WO2017064848A1 - Electric power conversion device and power conditioner using same - Google Patents

Electric power conversion device and power conditioner using sameDownload PDFInfo

- Publication number

- WO2017064848A1 WO2017064848A1PCT/JP2016/004484JP2016004484WWO2017064848A1WO 2017064848 A1WO2017064848 A1WO 2017064848A1JP 2016004484 WJP2016004484 WJP 2016004484WWO 2017064848 A1WO2017064848 A1WO 2017064848A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- switching element

- point

- output

- connection point

- capacitor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Ceased

Links

Images

Classifications

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M7/00—Conversion of AC power input into DC power output; Conversion of DC power input into AC power output

- H02M7/42—Conversion of DC power input into AC power output without possibility of reversal

- H02M7/44—Conversion of DC power input into AC power output without possibility of reversal by static converters

- H02M7/48—Conversion of DC power input into AC power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M7/00—Conversion of AC power input into DC power output; Conversion of DC power input into AC power output

- H02M7/42—Conversion of DC power input into AC power output without possibility of reversal

- H02M7/44—Conversion of DC power input into AC power output without possibility of reversal by static converters

- H02M7/48—Conversion of DC power input into AC power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M7/483—Converters with outputs that each can have more than two voltages levels

Definitions

- the present inventionrelates to a power conversion device and a power conditioner using the same.

- Patent Documents 1 and 2disclose a power converter that generates an AC output converted from a DC voltage source into a plurality of voltage levels (“Multi-level power converter” in Patent Document 1 and “Converter Circuit” in Patent Document 2). Is disclosed.

- the power conversion deviceis a 5-level inverter that outputs a 5-level voltage, and includes two DC capacitors, two flying capacitors, and 10 switching elements. ing.

- the voltage of each DC capacitorbecomes E / 2 and the voltage of each flying capacitor becomes E / 4.

- the switching elementBy controlling the switching element, a five-level voltage is output.

- Japanese Patent Laying-Open No. 2014-64431paragraphs [0002] to [0006], FIGS. 16 and 17

- Japanese Patent No. 4369425Japanese Patent No. 4369425

- the present inventionhas been made in view of the above reasons, and an object thereof is to provide a power conversion device capable of further improving the power conversion efficiency and a power conditioner using the power conversion device.

- a power conversion deviceincludes a first conversion circuit and a second conversion circuit, and includes a first bidirectional switch, a second bidirectional switch, and first to fourth protection diodes. It has more.

- the first conversion circuit and the second conversion circuitare electrically in parallel between a first input point on the high potential side of the DC power supply and a second input point on the low potential side of the DC power supply. It is connected.

- the first conversion circuitincludes first to fourth switching elements and a first capacitor.

- the first to fourth switching elementsinclude a first switching element, a second switching element, and a third switching element from the first input point side between the first input point and the second input point. In this order, the fourth switching elements are electrically connected in series.

- the first capacitoris electrically connected in parallel with a series circuit of the second switching element and the third switching element.

- the first conversion circuituses a connection point between the second switching element and the third switching element as a first output point.

- the second conversion circuitincludes fifth to eighth switching elements and a second capacitor.

- the fifth to eighth switching elementsinclude a fifth switching element, a sixth switching element, and a seventh switching element from the first input point side between the first input point and the second input point. In this order, the eighth switching elements are electrically connected in series.

- the second capacitoris electrically connected in parallel with a series circuit of the sixth switching element and the seventh switching element.

- the second conversion circuituses a connection point between the sixth switching element and the seventh switching element as a second output point.

- the first bidirectional switchis a connection point between a first connection point, which is a connection point between the first switching element and the second switching element, and a connection point between the seventh switching element and the eighth switching element.

- the second connection pointis electrically connected.

- the second bidirectional switchis a connection point of a third connection point that is a connection point of the third switching element and the fourth switching element, and a connection point of the fifth switching element and the sixth switching element. It is electrically connected to the fourth connection point.

- the first protection diodeis electrically connected in parallel with a series circuit of the first switching element and the second switching element between the first input point and the first output point, A current flowing from the first output point to the first input point is passed.

- the second protection diodeis electrically connected in parallel with a series circuit of the third switching element and the fourth switching element between the second input point and the first output point, A current flowing from the second input point to the first output point is passed.

- the third protection diodeis electrically connected in parallel with a series circuit of the fifth switching element and the sixth switching element between the first input point and the second output point, A current flowing from the second output point to the first input point is passed.

- the fourth protection diodeis electrically connected in parallel with a series circuit of the seventh switching element and the eighth switching element between the second input point and the second output point. A current flowing from the second input point to the second output point is passed.

- the power converteris configured to generate an output voltage between the first output point and the second output point.

- a power conditionerincludes the power conversion device described above and a disconnector electrically connected between the first output point and the second output point and a system power supply.

- FIG. 1is a circuit diagram illustrating a configuration of a power conversion device according to an embodiment.

- FIG. 2Ais an explanatory diagram of a first mode of the power conversion device according to the embodiment

- FIG. 2Bis an explanatory diagram of a second mode of the power conversion device according to the embodiment.

- FIG. 3Ais an explanatory diagram of a third mode of the power conversion device according to the embodiment

- FIG. 3Bis an explanatory diagram of a fourth mode of the power conversion device according to the embodiment.

- 4Ais an explanatory diagram of a fifth mode of the power conversion device according to the embodiment

- FIG. 4Bis an explanatory diagram of a sixth mode of the power conversion device according to the embodiment.

- FIG. 2Ais an explanatory diagram of a first mode of the power conversion device according to the embodiment

- FIG. 2Bis an explanatory diagram of a second mode of the power conversion device according to the embodiment.

- FIG. 3Ais an explanatory diagram of a third mode of the power

- FIG. 5Ais an explanatory diagram of a seventh mode of the power conversion device according to the embodiment

- FIG. 5Bis an explanatory diagram of an eighth mode of the power conversion device according to the embodiment

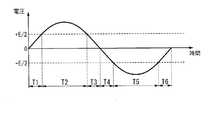

- FIG. 6is a waveform diagram of an output voltage of the power conversion device according to the embodiment.

- FIG. 7is a schematic diagram illustrating a configuration of a power conditioner according to the embodiment.

- FIG. 8is a waveform diagram showing the relationship between the output voltage and the output current of the power converter according to the embodiment.

- 9Ais an explanatory diagram of a dead time between the first and second modes of the power conversion device according to the embodiment

- FIG. 9Bis an explanatory diagram of a dead time between the first and third modes of the power conversion device according to the embodiment. is there.

- FIG. 10Ais an explanatory diagram of a dead time between the second and fourth modes of the power conversion device according to the embodiment

- FIG. 10Bis an explanatory diagram of a dead time between the third and fourth modes of the power conversion device according to the embodiment. is there.

- FIG. 11Ais an explanatory diagram of a dead time between the first and third modes of the power converter of the comparative example

- FIG. 11Bis an explanatory diagram of a third mode of the power converter of the comparative example.

- 12Ais an explanatory diagram of a dead time between the first and second modes of the power conversion device according to the embodiment

- FIG. 12Bis an explanatory diagram of a dead time between the first and third modes of the power conversion device according to the embodiment. is there.

- FIG. 11Ais an explanatory diagram of a dead time between the first and third modes of the power converter of the comparative example

- FIG. 12Bis an explanatory diagram of a dead time between the first and third modes of the power conversion device according to the

- FIG. 13Ais an explanatory diagram of a dead time between the second and fourth modes of the power conversion device according to the embodiment

- FIG. 13Bis an explanatory diagram of a dead time between the third and fourth modes of the power conversion device according to the embodiment. is there.

- the following embodimentsrelate to a power converter and a power conditioner using the power converter, and more particularly to a power converter that converts power from a DC power source and a power conditioner using the power converter.

- the power conversion device 1includes a first conversion circuit 11 and a second conversion circuit 12, and includes a first bidirectional switch 13 and a second bidirectional circuit. And a switch 14.

- the power conversion device 1further includes first to fourth protection diodes D101 to D104.

- the first conversion circuit 11 and the second conversion circuit 12are electrically connected between a first input point 101 on the high potential side of the DC power supply 100 and a second input point 102 on the low potential side of the DC power supply 100. Connected in parallel.

- the first conversion circuit 11includes first to fourth switching elements Q1 to Q4 and a first capacitor C1.

- the first conversion circuit 11sets a connection point between the second switching element Q ⁇ b> 2 and the third switching element Q ⁇ b> 3 as the first output point 103.

- the first to fourth switching elements Q1 to Q4are electrically connected in series between the first input point 101 and the second input point 102.

- the first to fourth switching elements Q1 to Q4are arranged in the order of the first switching element Q1, the second switching element Q2, the third switching element Q3, and the fourth switching element Q4 from the first input point 101 side. Connected in series.

- the first capacitor C1is electrically connected in parallel with the series circuit of the second switching element Q2 and the third switching element Q3.

- the second conversion circuit 12has fifth to eighth switching elements Q5 to Q8 and a second capacitor C2.

- the second conversion circuit 12sets a connection point between the sixth switching element Q6 and the seventh switching element Q7 as the second output point 104.

- the fifth to eighth switching elements Q5 to Q8are electrically connected in series between the first input point 101 and the second input point 102.

- the fifth to eighth switching elements Q5 to Q8are arranged in the order of the fifth switching element Q5, the sixth switching element Q6, the seventh switching element Q7, and the eighth switching element Q8 from the first input point 101 side. Connected in series.

- the second capacitor C2is electrically connected in parallel with the series circuit of the sixth switching element Q6 and the seventh switching element Q7.

- the first bidirectional switch 13is a connection point between a first connection point 201 that is a connection point between the first switching element Q1 and the second switching element Q2, and a connection point between the seventh switching element Q7 and the eighth switching element Q8. It is electrically connected to a certain second connection point 202.

- the second bidirectional switch 14is a connection point between the third switching element Q3 and the fourth switching element Q4, the third connection point 203 and the fifth switching element Q5 and the sixth switching element Q6. It is electrically connected to a certain fourth connection point 204.

- the first protection diode D101is electrically connected in parallel with the series circuit of the first switching element Q1 and the second switching element Q2 between the first input point 101 and the first output point 103. .

- the first protection diode D101allows a current flowing from the first output point 103 to the first input point 101 to pass therethrough.

- the second protection diode D102is electrically connected in parallel with the series circuit of the third switching element Q3 and the fourth switching element Q4 between the second input point 102 and the first output point 103. .

- the second protection diode D102allows a current flowing from the second input point 102 to the first output point 103 to pass therethrough.

- the third protection diode D103is electrically connected in parallel with the series circuit of the fifth switching element Q5 and the sixth switching element Q6 between the first input point 101 and the second output point 104. .

- the third protection diode D103allows a current flowing from the second output point 104 to the first input point 101 to pass therethrough.

- the fourth protection diode D104is electrically connected in parallel with the series circuit of the seventh switching element Q7 and the eighth switching element Q8 between the second input point 102 and the second output point 104. .

- the fourth protection diode D104allows a current flowing from the second input point 102 to the second output point 104 to pass therethrough.

- the power converter 1is configured to generate an output voltage between the first output point 103 and the second output point 104.

- the power conditioner 20is a residential power conditioner that is used by being electrically connected to a photovoltaic power generation device serving as the DC power source 100 is exemplified.

- the use of the power conditioner 20is illustrated. It is not intended to limit.

- the power conditioner 20may be used by being electrically connected to a DC power source 100 other than a solar power generation device, such as a household fuel cell or a power storage device.

- the power conditioner 20may be used in a non-residential such as a store, a factory, or an office.

- the power converter 1is not intended to limit the application to the power conditioner 20, and the power converter 1 may be used other than the power conditioner 20.

- the power converter 1 of the present embodimentis electrically connected to a DC power source 100 as shown in FIG.

- the power converter 1is connected to the DC power source 100 via a connection box.

- the power conversion device 1 of this embodimentincludes a conversion circuit 10 and a control unit 6. Further, the power conversion device 1 further includes a filter circuit 5.

- the conversion circuit 10includes a first conversion circuit 11, a second conversion circuit 12, a first bidirectional switch 13, a second bidirectional switch 14, and first to fourth protection diodes D101 to D104.

- the first input point 101 and the second input point 102correspond to a pair of input terminals in the power conversion device 1.

- a DC power source 100is electrically connected between the pair of input terminals (the first input point 101 and the second input point 102).

- the first output point 103 of the first conversion circuit 11 and the second output point 104 of the second conversion circuit 12are electrically connected to the third output point 105 and the fourth output point 106 through the filter circuit 5, respectively.

- the third output point 105 and the fourth output point 106correspond to a pair of output terminals in the power conversion device 1.

- the output voltage of the power converter 1is an AC voltage

- the third output point 105 and the fourth output point 106are electrically connected to the system power source (commercial power system) 7.

- a load 8 that operates by receiving supply of AC poweris electrically connected to the third output point 105 and the fourth output point 106.

- the pair of output terminals of the power conversion device 1are connected to the load 8 and the system power supply 7 by being electrically connected to an interconnection breaker provided in the distribution board. That is, the power conversion device 1 converts the DC power input from the DC power source 100 into AC power, and the AC power is transferred from the pair of output terminals (the third output point 105 and the fourth output point 106) to the load 8 and the system. Output to power supply 7.

- the system power supply 7is a single-phase three-wire system having a U-phase and a W-phase, but is not limited to this example, and the system power supply 7 may be a single-phase two-wire system.

- the power conversion apparatus 1uses the input terminal on the high potential (positive electrode) side of the DC power supply 100 among the pair of input terminals connected to the DC power supply 100 as the first input point 101, and the low potential (negative electrode) of the DC power supply 100.

- the input terminal on the sideis the second input point 102. Therefore, a DC voltage output from the DC power supply 100 is applied as an input voltage between the first input point 101 and the second input point 102.

- the input terminal (second input point 102) on the low potential side of the DC power supply 100is the circuit ground of the power converter 1, and the potential thereof is 0 [V]. Then, using the output voltage E [V] of the DC power supply 100, the potential of the first input point 101 is represented by E [V].

- the first conversion circuit 11includes the first to fourth switching elements Q1 to Q4 connected in series between the first input point 101 and the second input point 102, and the first capacitor C1. is doing.

- a depletion type n-channel MOSFETMetal-Oxide-Semiconductor-Field-Effect-Transistor

- each of the first to fourth switching elements Q1-Q4is used here as each of the first to fourth switching elements Q1-Q4.

- the drain of the first switching element Q1is electrically connected to the first input point 101.

- the drain of the second switching element Q2is electrically connected to the source of the first switching element Q1.

- the drain of the third switching element Q3is electrically connected to the source of the second switching element Q2.

- the drain of the fourth switching element Q4is electrically connected to the source of the third switching element Q3. Further, the source of the fourth switching element Q 4 is electrically connected to the second input point 102.

- connection point between the source of the second switching element Q 2 and the drain of the third switching element Q 3corresponds to the first output point 103. Further, the connection point between the source of the first switching element Q1 and the drain of the second switching element Q2 corresponds to the first connection point 201, and the source of the third switching element Q3 and the drain of the fourth switching element Q4. The connection point to corresponds to the third connection point 203.

- first capacitor C1One end of the first capacitor C1 is electrically connected to the drain (first connection point 201) of the second switching element Q2, and the other end is electrically connected to the source (third connection point 203) of the third switching element Q3. Connected.

- the first capacitor C1has one end electrically connected to the first input point 101 via the first switching element Q1 and the other end connected to the second input point 102 via the fourth switching element Q4. Electrically connected.

- the second conversion circuit 12includes the fifth to eighth switching elements Q5 to Q8 connected in series between the first input point 101 and the second input point 102, and the second capacitor C2. is doing.

- the second conversion circuit 12has basically the same configuration as the first conversion circuit 11, and the fifth to eighth switching elements Q5 to Q8 are replaced with the first to fourth switching elements Q1 to Q4, respectively.

- the second capacitor C2corresponds to the first capacitor C1.

- a depletion type n-channel MOSFETis used in the same manner as each of the first to fourth switching elements Q1 to Q4.

- the drain of the fifth switching element Q5is electrically connected to the first input point 101.

- the drain of the sixth switching element Q6is electrically connected to the source of the fifth switching element Q5.

- the drain of the seventh switching element Q7is electrically connected to the source of the sixth switching element Q6.

- the drain of the eighth switching element Q8is electrically connected to the source of the seventh switching element Q7. Further, the source of the eighth switching element Q8 is electrically connected to the second input point 102.

- connection point between the source of the sixth switching element Q6 and the drain of the seventh switching element Q7corresponds to the second output point 104. Further, the connection point between the source of the fifth switching element Q5 and the drain of the sixth switching element Q6 corresponds to the fourth connection point 204, and the source of the seventh switching element Q7 and the drain of the eighth switching element Q8.

- the connection pointis equivalent to the second connection point 202.

- the second capacitor C2has one end electrically connected to the drain (fourth connection point 204) of the sixth switching element Q6 and the other end electrically connected to the source (second connection point 202) of the seventh switching element Q7. Connected. In other words, the second capacitor C2 has one end electrically connected to the first input point 101 via the fifth switching element Q5 and the other end connected to the second input point 102 via the eighth switching element Q8. Electrically connected.

- the circuit constant (capacitance) of the second capacitor C2 and the circuit constant (capacitance) of the first capacitor C1are the same value.

- the first to eighth switching elements Q1 to Q8are connected to the first to eighth diodes D1 to D8 in a one-to-one manner and in antiparallel.

- These first to eighth diodes D1 to D8are parasitic diodes of the first to eighth switching elements Q1 to Q8, respectively. That is, the parasitic diode of the first switching element Q1 constitutes the first diode D1, and similarly, the parasitic diodes of the second, third,... Switching elements Q2, Q3,. D3...

- the first diode D1is connected in such a direction that the drain side of the first switching element Q1 is a cathode and the source side is an anode.

- the first conversion circuit 11 and the second conversion circuit 12 configured as described aboveare electrically connected in parallel between the first input point 101 and the second input point 102. That is, the first conversion circuit 11 and the second conversion circuit 12 are connected in parallel between both ends of the DC power supply 100.

- the first bidirectional switch 13is electrically connected between the first connection point 201 and the second connection point 202. That is, the first connection point 201 of the first conversion circuit 11 is electrically connected to the second connection point 202 of the second conversion circuit 12 via the first bidirectional switch 13.

- the first bidirectional switch 13includes a ninth switching element Q9 and a tenth switching element Q10 electrically connected in series between the first connection point 201 and the second connection point 202. have.

- the ninth switching element Q9 and the tenth switching element Q10are connected in the order of the ninth switching element Q9 and the tenth switching element Q10 from the first connection point 201 side.

- each of the ninth and tenth switching elements Q9 and Q10is a depletion type n-channel MOSFET, like each of the first to eighth switching elements Q1 to Q8.

- the source of the ninth switching element Q9is connected to the first connection point 201, and the drain of the ninth switching element Q9 is connected to the drain of the tenth switching element Q10.

- the source of the tenth switching element Q ⁇ b> 10is connected to the second connection point 202.

- the ninth switching element Q9 and the tenth switching element Q10are connected in anti-series between the first connection point 201 and the second connection point 202 so that the drains are connected to each other. .

- the second bidirectional switch 14is electrically connected between the third connection point 203 and the fourth connection point 204. That is, the third connection point 203 of the first conversion circuit 11 is electrically connected to the fourth connection point 204 of the second conversion circuit 12 via the second bidirectional switch 14.

- the second bidirectional switch 14includes the twelfth switching element Q12 and the eleventh switching element Q11 electrically connected in series between the third connection point 203 and the fourth connection point 204. have.

- the eleventh switching element Q11 and the twelfth switching element Q12are connected in order of the twelfth switching element Q12 and the eleventh switching element Q11 from the third connection point 203 side.

- each of the eleventh and twelfth switching elements Q11 and Q12is a depletion type n-channel MOSFET, similar to each of the first to eighth switching elements Q1 to Q8.

- the source of the eleventh switching element Q11is connected to the fourth connection point 204, and the drain of the eleventh switching element Q11 is connected to the drain of the twelfth switching element Q12.

- the source of the twelfth switching element Q12is connected to the third connection point 203.

- the eleventh switching element Q11 and the twelfth switching element Q12are connected in anti-series between the third connection point 203 and the fourth connection point 204 so that the drains are connected to each other. .

- ninth to twelfth diodes D9 to D12are connected in antiparallel to the ninth to twelfth switching elements Q9 to Q12, respectively.

- the ninth to twelfth diodes D9 to D12are parasitic diodes of the ninth to twelfth switching elements Q9 to Q12, respectively. That is, the parasitic diode of the ninth switching element Q9 forms a ninth diode D9, and similarly, the parasitic diodes of the tenth, eleventh and twelfth switching elements Q10, Q11 and Q12 are the tenth, eleventh and twelfth parasitic diodes, respectively.

- Diodes D10, D11, and D12are configured.

- the ninth diode D9is connected in such a direction that the drain side of the ninth switching element Q9 is a cathode and the source side is an anode.

- the first bidirectional switch 13is configured to be able to switch between an operation state including an all-off state and an all-on state.

- the all-off state of the first bidirectional switch 13is a state in which a bidirectional current is interrupted between the first connection point 201 and the second connection point 202.

- the all-on state of the first bidirectional switch 13is a state in which bidirectional current passes between the first connection point 201 and the second connection point 202.

- the second bidirectional switch 14is configured to be able to switch the operation state including the all-off state and the all-on state.

- the all-off state of the second bidirectional switch 14is a state in which bidirectional current is interrupted between the third connection point 203 and the fourth connection point 204.

- the all-on state of the second bidirectional switch 14is a state in which bidirectional current passes between the third connection point 203 and the fourth connection point 204.

- the operating state of the first bidirectional switch 13blocks the current flowing from the second connection point 202 to the first connection point 201, and from the first connection point 201 to the second connection point 202. It further includes a half-on state for passing a flowing current.

- the operating state of the second bidirectional switch 14is a half-on state that interrupts the current flowing from the third connection point 203 to the fourth connection point 204 and passes the current flowing from the fourth connection point 204 to the third connection point 203. It further includes a state.

- bidirectional currentcan pass between the first connection point 201 and the second connection point 202 by setting the first bidirectional switch 13 to the all-on state. Can create a unique state.

- the power converter device 1 of this embodimentcan pass a bidirectional

- the first bidirectional switch 13is turned off when the ninth and tenth switching elements Q9 and Q10 are both off, and the ninth and tenth switching elements Q9 and Q10 are both on. All are turned on. Further, in the first bidirectional switch 13, when the tenth switching element Q10 is on and the ninth switching element Q9 is off, the direction of the current is limited to one direction by the ninth diode D9. Semi-on state.

- the second bidirectional switch 14is fully turned off when the eleventh and twelfth switching elements Q11 and Q12 are both off, and the eleventh and twelfth switching elements Q11 and Q12 are both on. All are turned on. Furthermore, in the second bidirectional switch 14, when the twelfth switching element Q12 is on and the eleventh switching element Q11 is off, the direction of the current is limited to one direction by the eleventh diode D11. Semi-on state.

- the bidirectional switch in the present embodiment(each of the first bidirectional switch 13 and the second bidirectional switch 14) has three operation states consisting of a full-off state, a full-on state, and a half-on state. Can be switched.

- the first bidirectional switch 13is electrically connected between the positive terminal of the first capacitor C1 and the negative terminal of the second capacitor C2.

- the second bidirectional switch 14is electrically connected between the negative terminal of the first capacitor C1 and the positive terminal of the second capacitor C2.

- the first capacitor C1 of the first conversion circuit 11 and the second capacitor C2 of the second conversion circuit 12are connected in a crossed manner via the first bidirectional switch 13 and the second bidirectional switch 14. Has been.

- the first protection diode D101 and the second protection diode D102are electrically connected in parallel with the first conversion circuit 11 between the first input point 101 and the second input point 102.

- the first protection diode D101 and the second protection diode D102are connected in order of the first protection diode D101 and the second protection diode D102 from the first input point 101 side.

- the cathode of the first protection diode D101is connected to the first input point 101

- the anode of the first protection diode D101is connected to the cathode of the second protection diode D102.

- the anode of the second protection diode D102is connected to the second input point 102.

- a connection point between the first protection diode D101 and the second protection diode D102is connected to the first output point 103.

- the first protection diode D101is electrically connected to the series circuit of the first switching element Q1 and the second switching element Q2 so as to pass a current flowing from the first output point 103 to the first input point 101.

- the second protection diode D102is electrically in parallel with the series circuit of the third switching element Q3 and the fourth switching element Q4 so as to pass the current flowing from the second input point 102 to the first output point 103. It is connected.

- the third protection diode D103 and the fourth protection diode D104are electrically connected in parallel with the second conversion circuit 12 between the first input point 101 and the second input point 102.

- the third protection diode D103 and the fourth protection diode D104are connected in order of the third protection diode D103 and the fourth protection diode D104 from the first input point 101 side.

- the cathode of the third protection diode D103is connected to the first input point 101

- the anode of the third protection diode D103is connected to the cathode of the fourth protection diode D104.

- the anode of the fourth protection diode D104is connected to the second input point.

- a connection point between the third protection diode D 103 and the fourth protection diode D 104is connected to the second output point 104.

- the third protection diode D103is electrically connected to the series circuit of the fifth switching element Q5 and the sixth switching element Q6 so as to pass the current flowing from the second output point 104 to the first input point 101. Connected in parallel.

- the fourth protection diode D104is electrically in parallel with the series circuit of the seventh switching element Q7 and the eighth switching element Q8 so as to pass the current flowing from the second input point 102 to the second output point 104. It is connected.

- the fast recovery diodeis a diode having a recovery characteristic (reverse recovery characteristic) superior to a general rectifying diode.

- the recovery characteristichere is a characteristic of the diode when the bias applied to the diode is changed from the forward bias to the reverse bias, and the reverse recovery current (Irr), the reverse recovery time (trr), or the reverse recovery charge. (Qrr) or the like.

- the reverse recovery currentis a current that flows through the diode in the reverse direction (from the cathode to the anode) when the bias changes from the forward bias to the reverse bias.

- the reverse recovery timeis the time required for the diode to turn off when the bias changes from the forward bias to the reverse bias, that is, the time required for the current flowing through the diode (reverse current) to reach a predetermined value.

- the reverse recovery chargeis a time integral value of the reverse recovery current. The smaller the (or shorter) reverse recovery current, reverse recovery time, and reverse recovery charge, the better the recovery characteristics.

- each of the first, fourth, fifth, and eighth switching elements Q1, Q4, Q5, and Q8is required to have a particularly high breakdown voltage and a low on-resistance. Therefore, in this embodiment, a trench gate type MOSFET is used for each of the first, fourth, fifth, and eighth switching elements Q1, Q4, Q5, and Q8.

- a trench gate type MOSFETis used for each of the first, fourth, fifth, and eighth switching elements Q1, Q4, Q5, and Q8.

- the recovery characteristic of the parasitic diodeis worse than that of a general MOSFET. That is, the recovery characteristics of the first, fourth, fifth, and eighth diodes D1, D4, D5, and D8 are relatively poor.

- each of the first to fourth protection diodes D101 to D104has at least a better recovery characteristic than each of the first, fourth, fifth, and eighth diodes D1, D4, D5, and D8.

- each of the first to fourth protection diodes D101 to D104is about 1/10 to 1 / 100th of each of the first, fourth, fifth, and eighth diodes D1, D4, D5, and D8. It is. Further, in the present embodiment, each of the first to fourth protection diodes D101 to D104 has better recovery characteristics than each of the second, third, sixth, and seventh diodes D2, D3, D6, and D7.

- the gates of the first to eighth switching elements Q1 to Q8 and the ninth to twelfth switching elements Q9 to Q12are electrically connected to the control unit 6.

- the control unit 6can individually switch on / off the first to fourth switching elements Q1 to Q4, and thereby controls the first conversion circuit 11.

- the control unit 6can individually switch on / off the fifth to eighth switching elements Q5 to Q8, thereby controlling the second conversion circuit 12.

- the controller 6can individually switch on / off the ninth and tenth switching elements Q9 and Q10, and thereby controls the first bidirectional switch 13.

- the controller 6can individually switch on / off the eleventh and twelfth switching elements Q11 and Q12, and thereby controls the second bidirectional switch 14.

- the control unit 6may be provided for each of the first conversion circuit 11, the second conversion circuit 12, the first bidirectional switch 13, and the second bidirectional switch 14.

- control unit 6includes a drive circuit 61 that supplies drive signals to the first to twelfth switching elements Q1 to Q12, a microcomputer 62 that supplies signals to the drive circuit 61, and a detection circuit 63.

- drive circuit 61that supplies drive signals to the first to twelfth switching elements Q1 to Q12

- microcomputer 62that supplies signals to the drive circuit 61

- the drive circuit 61is configured to drive (control) each element by giving a drive signal to each control terminal (gate) of each of the first to twelfth switching elements Q1 to Q12.

- the microcomputer 62is configured to control the drive circuit 61 by giving a PWM (Pulse Width Modulation) signal to the drive circuit 61. That is, the control unit 6 individually controls the first to twelfth switching elements Q1 to Q12 by a drive signal generated by the drive circuit 61 in response to an instruction from the microcomputer 62.

- the detection circuit 63is configured to detect the magnitude of the voltage across the first capacitor C1 and the voltage across the second capacitor C2. The operation of the control unit 6 using the detection result of the detection circuit 63 will be described later.

- the drive circuit 61also has a function as a short-circuit prevention circuit that prevents two or more switching elements from being simultaneously turned on to prevent a short-circuit current from flowing. That is, when switching elements of a specific combination are simultaneously turned on, for example, the first input point 101 and the second input point 102 may be short-circuited, and the current from the DC power supply 100 may flow as a short-circuit current to the switching element. There is. Therefore, it is preferable that the drive circuit 61 is configured such that such specific combination of switching elements does not turn on at the same time.

- the drive circuit 61is specified by forcibly dropping the drive signal to the L level (Low Level) when the drive signals input to the gates of the switching elements of the specific combination simultaneously become the H level (High Level).

- the switching elements of the combinationare configured so as not to be turned on simultaneously.

- the filter circuit 5has a pair of inductors L1 and L2 and a third capacitor C3.

- One inductor L ⁇ b> 1is electrically connected between the first output point 103 and the third output point 105.

- the other inductor L 2is electrically connected between the second output point 104 and the fourth output point 106.

- the inductors L1 and L2are electrically connected between at least one of the first output point 103 and the second output point 104 and the output terminal (the third output point 105 and the fourth output point 106). Any one of the inductors L1 and L2 may be omitted. That is, the inductor L1 is only electrically connected between the first output point 103 and the third output point 105, or the inductor L2 is electrically connected between the second output point 104 and the fourth output point 106. It may be only connected to.

- the third capacitor C3is electrically connected between the third output point 105 and the fourth output point 106.

- the filter circuit 5is a series circuit of an inductor L1, a third capacitor C3, and an inductor L2, which are electrically connected between the first output point 103 and the second output point 104.

- the basic operation of the power conversion device 1is the operation of the power conversion device 1 after the start-up period has elapsed.

- the starting period hereis a period from when the supply of power from the DC power supply 100 is started until both the first capacitor C1 and the second capacitor C2 are charged to the reference voltage. That is, the operation of the power conversion device 1 from a state where both the first capacitor C1 and the second capacitor C2 are charged to the reference voltage is defined as a basic operation of the power conversion device 1.

- the reference voltage for the first capacitor C1is a voltage that is 1/4 of the applied voltage applied from the DC power supply 100 between the first input point 101 and the second input point 102.

- the reference voltage for the second capacitor C ⁇ b> 2is a voltage that is 1 ⁇ 4 of the applied voltage applied between the first input point 101 and the second input point 102 from the DC power supply 100.

- the output voltage of the DC power supply 100is E [V]

- the potential of the first input point 101is E [V]

- the potential of the second input point 102is 0 [V].

- the voltage across each of the first capacitor C1 and the second capacitor C2 charged to the reference voltageis E / 4 [V].

- the potential difference between the first output point 103 and the second output point 104that is, the voltage generated between the first output point 103 and the second output point 104 will be described as the output voltage V2 of the power converter 1.

- the output voltage V2 generated between the first output point 103 and the second output point 104is also referred to as “second output voltage V2”.

- the output voltage V1 generated between the points 106is equal to the output voltage of the system power supply 7.

- the potential difference between the first output point 103 and the third output point 105 and the potential difference between the second output point 104 and the fourth output point 106are absorbed by the filter circuit 5.

- the output voltage V1 generated between the third output point 105 and the fourth output point 106is also referred to as “first output voltage V1”.

- the operation mode of the power conversion device 1includes the first to eighth modes.

- the power conversion device 1converts the DC voltage (E [V]) applied between the first input point 101 and the second input point 102 into an AC voltage, and the first output point 103 and the first input point 103 An output voltage V2 is generated between the two output points 104.

- E [V]DC voltage

- V2an output voltage

- the first to twelfth switching elements Q1 to Q12are assumed to be in the “off” state when the on / off state is not mentioned.

- control unit 6controls each of the first to twelfth switching elements Q1 to Q12 according to the following two conditions.

- the first conditionis that a one-to-one pair is set between the first to fourth switching elements Q1 to Q4 of the first conversion circuit 11 and the fifth to eighth switching elements Q5 to Q8 of the second conversion circuit 12. On / off is switched for each pair.

- the first and eighth switching elements Q1, Q8are paired

- the second, seventh switching elements Q2, Q7are paired

- the third, sixth switching elements Q3, Q6are paired

- the fourth, fifth Switching elements Q4 and Q5form a pair.

- the second conditionis that the second switching element Q2 and the third switching element Q3 are not simultaneously turned on or off. Further, in the first to fourth modes, the first switching element Q1 and the eleventh switching element Q11 are used. In the fifth to eighth modes, the fourth switching element Q4 and the ninth switching element Q9 are set. Are not simultaneously turned on or off. The condition that the two conditions are not turned off at the same time is applied except for the dead time described in “(2.4.2) Dead time”.

- the first and second switching elements Q1 and Q2, the seventh and eighth switching elements Q7 and Q8, and the twelfth switching element Q12are on. . That is, the second bidirectional switch 14 is in a half-on state.

- the first input point 101is electrically connected to the first output point 103 via the first switching element Q1 and the second switching element Q2.

- the second input point 102is electrically connected to the second output point 104 via the eighth switching element Q8 and the seventh switching element Q7.

- switching elementsdiodes

- there are four elementsi.e., first, second, seventh, and eighth switching elements Q1, Q2, Q7, and Q8, and the twelfth switching element Q12. There is no current flowing through.

- the first output point 103is at the same potential (E [V]) as the first input point 101

- the potential of the third output point 105becomes a potential obtained by subtracting the voltage across the inductor L1 from the potential of the first output point 103, and the potential of the fourth output point 106 becomes the potential of the second output point 104 to the inductor.

- the potentialis the sum of the voltages at both ends of L2.

- the first and third switching elements Q1 and Q3, the sixth and eighth switching elements Q6 and Q8, and the twelfth switching element Q12are turned on. is there. That is, the second bidirectional switch 14 is in a half-on state.

- the first input point 101is electrically connected to the first output point 103 via the first switching element Q1, the first capacitor C1, and the third switching element Q3. Is done.

- the second input point 102is electrically connected to the second output point 104 via the eighth switching element Q8, the second capacitor C2, and the sixth switching element Q6.

- switching elementsdiodes

- the semiconductor elementsswitching elements, diodes

- the potential of the third output point 105becomes a potential obtained by subtracting the voltage across the inductor L1 from the potential of the first output point 103, and the potential of the fourth output point 106 becomes the potential of the second output point 104 to the inductor.

- the potentialis the sum of the voltages at both ends of L2.

- the second switching element Q2, the seventh switching element Q7, and the eleventh and twelfth switching elements Q11 and Q12are in an on state, respectively. That is, the second bidirectional switch 14 is in an all-on state.

- the second output point 104passes through the seventh switching element Q7, the second capacitor C2, the eleventh switching element Q11, the twelfth switching element Q12, the first capacitor C1, and the second switching element Q2. And electrically connected to the first output point 103.

- the semiconductor elementsswitching elements, diodes

- the third switching element Q3, the sixth switching element Q6, and the eleventh and twelfth switching elements Q11 and Q12are in an ON state. That is, the second bidirectional switch 14 is in an all-on state. In this state, the second output point 104 is electrically connected to the first output point 103 via the sixth switching element Q6, the eleventh switching element Q11, the twelfth switching element Q12, and the third switching element Q3. Connected to. At this time, among the semiconductor elements (switching elements, diodes), there are a total of four elements, ie, third, sixth, eleventh, and twelfth switching elements Q3, Q6, Q11, and Q12.

- the potential at the first output point 103is the same as that at the second output point 104. Therefore, the output voltage V2 of the power conversion device 1 generated between the first output point 103 and the second output point 104 is 0 [V]. Further, at this time, the potential of the third output point 105 becomes a potential obtained by subtracting the voltage across the inductor L1 from the potential of the first output point 103, and the potential of the fourth output point 106 becomes the potential of the second output point 104 to the inductor. The potential is the sum of the voltages at both ends of L2. In this state, since the second bidirectional switch 14 is fully on, the conversion circuit 10 can cause a bidirectional current to flow between the first output point 103 and the second output point 104. it can.

- the power conversion device 1switches the operation between the first conversion circuit 11 and the second conversion circuit 12 on the basis of the first to fourth modes, and

- the bi-directional switch 13 and the second bi-directional switch 14perform operations that are interchanged. That is, in the fifth to eighth modes and the first to fourth modes, the operation of the conversion circuit 10 is performed by both the first conversion circuit 11 and the first bidirectional switch 13 and the second conversion circuit 12 and the second mode.

- the direction switch 14is replaced with a symmetrical operation.

- the operation of the conversion circuit 10is symmetrical to the fourth mode. Therefore, in the fifth mode, the second switching element Q2, the seventh switching element Q7, and the ninth and tenth switching elements Q9 and Q10 are in the ON state. That is, the first bidirectional switch 13 is fully turned on. In this state, as shown in FIG. 4A, the first output point 103 passes through the second switching element Q2, the ninth switching element Q9, the tenth switching element Q10, and the seventh switching element Q7. The two output points 104 are electrically connected. At this time, among the semiconductor elements (switching elements, diodes), there are a total of four elements, ie, the second, seventh, ninth, and tenth switching elements Q2, Q7, Q9, and Q10.

- the potential at the first output point 103is the same as that at the second output point 104. Therefore, the output voltage V2 of the power conversion device 1 generated between the first output point 103 and the second output point 104 is 0 [V]. Further, at this time, the potential at the third output point 105 is a potential obtained by adding the voltage across the inductor L1 to the potential at the first output point 103, and the potential at the fourth output point 106 is changed from the potential at the second output point 104 to the inductor. The potential is obtained by subtracting the voltage across L2. In this state, since the first bidirectional switch 13 is fully on, the conversion circuit 10 can cause a bidirectional current to flow between the first output point 103 and the second output point 104. it can.

- the operation of the conversion circuit 10is symmetric to the third mode. Therefore, in the sixth mode, the third switching element Q3, the sixth switching element Q6, and the ninth and tenth switching elements Q9 and Q10 are in the ON state. That is, the first bidirectional switch 13 is fully turned on. In this state, the first output point 103 includes the third switching element Q3, the first capacitor C1, the ninth switching element Q9, the tenth switching element Q10, the second capacitor C2, and the sixth switching element Q6. And is electrically connected to the second output point 104. At this time, among the semiconductor elements (switching elements, diodes), there are a total of four elements, that is, third, sixth, ninth, and tenth switching elements Q3, Q6, Q9, and Q10.

- the operation of the conversion circuit 10is symmetric to the second mode. Therefore, in the seventh mode, the second and fourth switching elements Q2 and Q4, the fifth and seventh switching elements Q5 and Q7, and the tenth switching element Q10 are in an ON state. That is, the first bidirectional switch 13 is in a half-on state. In this state, as shown in FIG. 5A, the first input point 101 is electrically connected to the second output point 104 via the fifth switching element Q5, the second capacitor C2, and the seventh switching element Q7. Is done. The second input point 102 is electrically connected to the first output point 103 via the fourth switching element Q4, the first capacitor C1, and the second switching element Q2.

- switching elementsdiodes

- the potential at the third output point 105is a potential obtained by adding the voltage across the inductor L1 to the potential at the first output point 103, and the potential at the fourth output point 106 is changed from the potential at the second output point 104 to the inductor.

- the potentialis obtained by subtracting the voltage across L2.

- the operation of the conversion circuit 10is symmetrical to the first mode. Therefore, in the eighth mode, the third and fourth switching elements Q3 and Q4, the fifth and sixth switching elements Q5 and Q6, and the tenth switching element Q10 are in an ON state. That is, the first bidirectional switch 13 is in a half-on state. In this state, as shown in FIG. 5B, the first input point 101 is electrically connected to the second output point 104 via the fifth switching element Q5 and the sixth switching element Q6. The second input point 102 is electrically connected to the first output point 103 via the fourth switching element Q4 and the third switching element Q3.

- switching elementsdiodes

- the first output point 103has the same potential (0 [V]) as the second input point 102

- the potential at the third output point 105is a potential obtained by adding the voltage across the inductor L1 to the potential at the first output point 103, and the potential at the fourth output point 106 is changed from the potential at the second output point 104 to the inductor. The potential is obtained by subtracting the voltage across L2.

- the power conversion device 1changes the output voltage V2 generated between the first output point 103 and the second output point 104 in a plurality of stages by switching the first to eighth modes.

- the first conversion circuit 11uses the first capacitor C1 as a flying capacitor and switches each of the first to fourth, ninth to twelfth switching elements Q1 to Q4 and Q9 to Q12 on / off.

- the potential at the first output point 103is switched.

- the first capacitor C1is charged in the second and seventh modes and discharged in the third and sixth modes.

- the first capacitor C1is in the basic operation.

- the voltage across one capacitor C1can be regarded as substantially constant (E / 4 [V]).

- the second conversion circuit 12uses the second capacitor C2 as a flying capacitor, and switches the potential of the second output point 104 by switching each of the fifth to twelfth switching elements Q5 to Q12 on / off.

- the second capacitor C2is charged in the second and seventh modes and discharged in the third and sixth modes. If the first to eighth modes are switched at a relatively high frequency, the second capacitor C2 is charged in the basic operation.

- the voltage across the two capacitors C2can be regarded as substantially constant (E / 4 [V]).

- control unit 6charges and discharges the capacitor by switching a pair of modes in which the output voltage V2 is the same and the directions of the currents flowing through the capacitors (the first capacitor C1 and the second capacitor C2) are reversed. And switching.

- the control unit 6switches the second mode and the third mode as a pair of modes so that the capacitor (the first capacitor C1 and second capacitor C2) are switched between charging and discharging.

- the control unit 6switches the seventh mode and the sixth mode as a pair of modes, so that the capacitors (first capacitor C1 and Switching between charging and discharging of the second capacitor C2).

- the second mode and the seventh modeare hereinafter referred to as “charging mode”. Call. Since each of the first capacitor C1 and the second capacitor C2 is discharged in the third and sixth modes in principle, the third mode and the sixth mode are also referred to as “discharge modes” below.

- the control unit 6outputs a “charge command” when selecting the charge mode, and outputs a “discharge command” when selecting the discharge mode.

- the control unit 6when the output voltage V2 is set to E / 2 [V], the control unit 6 outputs a charge command when charging the capacitors (the first capacitor C1 and the second capacitor C2), and is in the charging mode. 2 mode is selected.

- the controller 6When the output voltage V2 is set to E / 2 [V], the controller 6 outputs a discharge command when discharging the capacitors (the first capacitor C1 and the second capacitor C2), and the third mode is the discharge mode. Select a mode.

- the control unit 6when charging the capacitors (first capacitor C1 and second capacitor C2) when the output voltage V2 is set to ⁇ E / 2 [V], the control unit 6 outputs a charging command and performs charging in the charging mode. A certain seventh mode is selected. When the output voltage V2 is set to -E / 2 [V], the control unit 6 outputs a discharge command when discharging the capacitors (the first capacitor C1 and the second capacitor C2), and is in the discharge mode. Select the mode.

- the control unit 6switches between the charging mode and the discharging mode in which the output voltage V2 is the same and the direction of the current flowing through the capacitor is reversed as a pair of modes, thereby charging and discharging the capacitor.

- the capacitoris charged in the charge mode and the capacitor is discharged in the discharge mode because the forward current described in the column “(2.4.1) Forward current and reverse current” is applied to the conversion circuit 10. Limited to flowing conditions.

- the reverse current described in the column “(2.4.1) Forward current and reverse current”flows through the conversion circuit 10

- the capacitoris discharged in the charge mode and the capacitor is charged in the discharge mode. The This point will be described later.

- the descriptionwill be made assuming that the current flowing through the conversion circuit 10 is a forward current unless otherwise specified.

- the power conversion apparatus 1outputs the voltage having the first output point 103 as the high potential side and the second output point 104 as the low potential side as the output voltage V2. Will do.

- the power conversion apparatus 1converts the output voltage V2 generated between the first output point 103 and the second output point 104 to E [V] (first mode), E / Switching is performed in three stages of 2 [V] (second and third modes) and 0 [V] (fourth mode).

- the power conversion device 1sets the output voltage V2 generated between the first output point 103 and the second output point 104 to 0 [V] (fifth mode), ⁇ E / Switching is performed in three stages: 2 [V] (sixth and seventh modes) and -E [V] (eighth mode).

- the power conversion device 1switches the output mode V2 to E [V], E / 2 [V], 0 [V], -E / 2 [V] by switching the first to eighth modes. ] And -E [V].

- the power conversion apparatus 1generates the first output voltage V1 that is an AC voltage between the third output point 105 and the fourth output point 106 by appropriately switching the five-stage second output voltage V2.

- the output voltage V1is equal to the output voltage of the system power supply 7, and has a sinusoidal waveform as shown in FIG.

- the horizontal axisrepresents the time axis and the vertical axis represents the voltage value.

- the power converter 1Switches between the first to fourth modes.

- the power converter 1switches between 8 modes.

- Table 1summarizes the first to eighth modes described above.

- control unit 6switches on / off each of the first to twelfth switching elements Q1 to Q12 by the PWM signal to realize the first to eighth modes.

- the control unit 6performs the operation of switching the second to fourth modes. repeat.

- the controller 6balances the discharge and charge of the first capacitor C1 and the second capacitor C2 by adjusting the time length in the second mode and the third mode.

- the control unit 6repeats the operation of switching the first to third modes.

- the controller 6balances the discharge and charge of the first capacitor C1 and the second capacitor C2 by adjusting the time length in the second mode and the third mode.

- control unit 6repeats the operation of switching the fifth to seventh modes during the periods T4 and T6 in which the output voltage V1 varies in the range of 0 [V] to ⁇ E / 2 [V].

- the control unit 6balances the discharge and charging of the first capacitor C1 and the second capacitor C2 by adjusting the time length in the sixth mode and the seventh mode.

- the control unit 6repeats the operation of switching the sixth to eighth modes.

- the control unit 6balances the discharge and charging of the first capacitor C1 and the second capacitor C2 by adjusting the time length in the sixth mode and the seventh mode.

- the control unit 6switches the first to eighth modes described above while changing the duty ratio of the PWM signal, so that the waveform of the output voltage V1 approximates a sine wave.

- the output voltage V2 generated between the output point 103 and the second output point 104is controlled.

- the power conversion device 1changes the output voltage V2 generated between the first output point 103 and the second output point 104 in five steps by the control unit 6 to thereby generate a sinusoidal AC voltage (output voltage V1). ) Occurs between the third output point 105 and the fourth output point 106.

- the fourth mode and the fifth modeare both modes in which the output voltage V2 is 0 [V] and do not contribute to the discharging and charging of the first capacitor C1 and the second capacitor C2. For this reason, it is conceivable to omit either the fourth mode or the fifth mode, but the power conversion device 1 is configured as the fourth mode in consideration of the positive / negative balance of the output voltage V1. By dividing the fifth mode, the switching loss can be reduced and the efficiency is improved.

- the number of elements through which a current flows(hereinafter referred to as “the number of passing elements”) among the semiconductor elements (switching elements, diodes) In this mode, it is “4” or less.

- the number of passing elementsis “ 4 ".

- the number of passing elements in the third to sixth modesis “3”.

- the control unit 6determines whether to charge or discharge the first capacitor C1 and the second capacitor C2 according to the detection result of the detection circuit 63.

- the detection circuit 63is included in the control unit 6, and the detection result of the detection circuit 63 is output to the microcomputer 62.

- the detection circuit 63individually detects the voltage across the first capacitor C1 and the voltage across the second capacitor C2, and outputs an average value Vc of these two voltages to the microcomputer 62 as a detection result.

- the microcomputer 62is configured to select whether to charge or discharge the capacitor according to the detection result of the detection circuit 63.

- the control unit 6repeats the operation of switching the first to fourth modes.

- the microcomputer 62determines whether to select the second mode (charge mode) or the third mode (discharge mode) according to the detection result of the detection circuit 63. To decide. That is, the microcomputer 62 compares the detection result (average value Vc) of the detection circuit 63 with the target voltage, and either the second mode (charge mode) or the third mode (discharge mode) is determined according to the comparison result. Select.

- the microcomputer 62selects the third mode, which is the discharge mode, if the detection result of the detection circuit 63 is greater than the target voltage, and the charge mode, if the detection result of the detection circuit 63 is smaller than the target voltage. 2 mode is selected.

- the target voltageis the same value as the reference voltage (E / 4 [V]).

- the control unit 6repeats the operation of switching the fifth to eighth modes.

- the microcomputer 62determines whether to select the sixth mode (discharge mode) or the seventh mode (charge mode) according to the detection result of the detection circuit 63. To decide. That is, the microcomputer 62 compares the detection result (average value Vc) of the detection circuit 63 with the target voltage (E / 4 [V]), and the seventh mode (charging mode) and the sixth mode are compared according to the comparison result. (Discharge mode) is selected.

- the microcomputer 62selects the sixth mode that is the discharge mode if the detection result of the detection circuit 63 is larger than the target voltage, and the charge mode if the detection result of the detection circuit 63 is smaller than the target voltage. 7 mode is selected.

- control unit 6switches between charging and discharging of the capacitors (the first capacitor C1 and the second capacitor C2) at a predetermined switching cycle.

- the switching periodhere is set in accordance with, for example, the period of the PWM signal.

- the power conditioner 20includes the power conversion device 1 and the disconnector 9.

- the disconnector 9is electrically connected between the first output point 103 (see FIG. 1) and the second output point 104 (see FIG. 1) and the system power supply 7.

- the disconnector 9is electrically connected between the third output point 105 and the fourth output point 106 and the system power supply 7.

- the resolver 9is connected to the first output point 103 and the second output point 104 via the filter circuit 5 (see FIG. 1).

- the disconnector 9may be located between the first output point 103 and the second output point 104 and the system power supply 7, and is required to be directly connected to the first output point 103 and the second output point 104. Instead, it may be connected to the subsequent stage of the filter circuit 5 as in this embodiment.

- the circuit breaker 9is electrically connected between the first contact point 91 electrically connected between the third output point 105 and the system power supply 7, and between the fourth output point 106 and the system power supply 7. And a second contact portion 92 connected to the.

- the circuit breaker 9only needs to be electrically connected between at least one of the third output point 105 and the fourth output point 106 and the system power supply 7, and the first contact portion 91 and the second contact portion are required. Any of 92 may be omitted.

- the power conditioner 20performs grid connection operation in a steady state, converts DC power input from the DC power supply 100 into AC power by the power converter 1, and outputs the AC power to the system power supply 7 and the load 8. Although detailed description is omitted, the power conditioner 20 performs a self-sustained operation in which the disconnector 9 is opened and AC power is output in a state disconnected from the system power supply 7 in the event of an abnormality such as a power failure of the system power supply 7. It is configured as follows.

- the first converter circuit 11 and the second converter circuit 12can be electrically disconnected from the system power supply 7 by opening the disconnector 9 (disconnecting). Therefore, the power conditioner 20 opens the disconnector 9 during the start-up period after the power is turned on and before the power converter 1 starts the basic operation described above, so that the first output point 103 and the second output point are opened.

- a current path including the filter circuit 5can be formed between the terminal 104 and the terminal 104.

- the current pathis a current path including the inductor L1, the third capacitor C3, and the inductor L2 constituting the filter circuit 5.

- the power conversion device 1uses the current path as a charging path, so that even if the third output point 105 and the fourth output point 106 are electrically insulated, the first capacitor C1 and the second capacitor C2 can be charged.

- the power conversion device 1can charge the first capacitor C1 and the second capacitor C2 even if the third output point 105 and the fourth output point 106 are not connected to the system power supply 7. In other words, the power conversion device 1 operates in a steady state even when no load is connected between the pair of output terminals (the third output point 105 and the fourth output point 106) (no load state). Necessary capacitors (first capacitor C1 and second capacitor C2) can be charged.

- the steady operation hereis an operation of the power conversion device 1 after the start-up period has elapsed, that is, after each of the first capacitor C1 and the second capacitor C2 is charged to the reference voltage (E / 4 [V]). Therefore, it is synonymous with the basic operation described above.

- the power converter 1 of the present embodimenthas the second bidirectional switch 14 in the third and fourth modes.

- the first bidirectional switch 13is in the fully on state. That is, in any of the first to eighth modes, the element through which a current flows among the semiconductor elements (switching elements, diodes) is any one of the first to twelfth switching elements Q1 to Q12, and the diode (first to eighth modes). No current flows through the twelve diodes D1 to D12). Therefore, the power conversion device 1 can pass a bidirectional current between the first output point 103 and the second output point 104 in any of the first to eighth modes.

- the current flowing through the conversion circuit 10 in the direction indicated by the thick arrow in FIGS. 2A, 2B, 3A, 3B, 4A, 4B, 5A, and 5Bis referred to as “forward current” and is opposite to the forward current.

- the current flowing through the conversion circuit 10is referred to as “reverse current”. That is, in the first to fourth modes in which the output voltage V1 varies in the range of 0 [V] to E [V], the current from the first output point 103 to the third output point 105 is the forward current. In the fifth to eighth modes in which the output voltage V1 varies in the range of 0 [V] to -E [V], the current from the second output point 104 to the fourth output point 106 is the forward current.

- the power conversion device 1is configured so that the conversion circuit 10 supports bidirectional current, so that the output current I1 that flows between the third output point 105 and the fourth output point 106, the third output point 105, A phase difference can be set between the output voltage V ⁇ b> 1 generated between the fourth output points 106. If there is a phase difference between the output current I1 and the output voltage V1, as shown in FIG. 8, the output current I1 is different from the output voltage V1 (for example, the output voltage V1 is positive and the output current I1 is negative). A period will arise.

- V1shows the first output voltage V1 generated between the third output point 105 and the fourth output point 106 and the output current I1 flowing through the third output point 105 or the fourth output point 106 with the horizontal axis as the time axis. Is shown.

- the output current I1is delayed with respect to the output voltage V1

- the output current I1 and the output voltage V1have different signs in the periods T11 and T13

- V1has the same sign.

- the current flowing in the conversion circuit 10is a forward current, but the period T11 in which the output current I1 and the output voltage V1 have different signs. , T13, the current flowing through the conversion circuit 10 is a reverse current. Therefore, when the power converter 1 sets a phase difference between the output current I1 and the output voltage V1, the conversion circuit 10 needs to support bidirectional current as in the present embodiment.

- the power conversion device 1when the power conversion device 1 is used for the power conditioner 20 (see FIG. 7) for the solar power generation device, the power conversion device is used for the purpose of detecting the isolated operation and suppressing the voltage rise of the system power supply 7. 1 may set a phase difference between the output current I1 and the output voltage V1. Moreover, when the power converter 1 is used for the power conditioner for the power storage device, the power converter 1 is supplied with power by setting a phase difference between the output current I1 and the output voltage V1. And switching between charging and discharging of the power storage device. The power converter 1 of this embodiment can respond to such a use because the conversion circuit 10 supports bidirectional current.

- the first capacitor C1 and the first capacitor C1 and the second capacitor C2depend on whether the current flowing through the first capacitor C1 and the second capacitor C2 is forward current or reverse current.

- the charging and discharging of the second capacitor C2may be interchanged. That is, when forward current flows through the conversion circuit 10, the first capacitor C1 and the second capacitor C2 are charged in the second and seventh modes and discharged in the third and sixth modes, as a rule.

- the first capacitor C1 and the second capacitor C2are discharged in the second and seventh modes and charged in the third and sixth modes. Will be.

- Dead timeWhen switching between the first to eighth modes, the power converter 1 turns off all of the specific combination of switching elements so that the specific combination of switching elements does not turn on at the same time. There is a dead time. That is, in the power conversion device 1, the first to eighth modes are switched after a period (dead time) in which the ON / OFF state of the switching element is different from any of the first to eighth modes.

- operationmovement of the power converter device 1 in a dead time is demonstrated with reference to FIG. 9A, 9B, 10A, 10B.

- a thick line arrowrepresents a current path

- a switching element with a dotted circlerepresents an on-state element.

- the second, third, sixth, and seventh switching elements Q2, Q3, Q6 , Q7are all set to a dead time. That is, only the first, eighth, and twelfth switching elements Q1, Q8, and Q12 are turned on during the dead time when switching between the first mode and the second mode. In this state, the return currents of the inductors L1 and L2 flow through the sixth diode D6, the second capacitor C2, the eighth switching element Q8, the first switching element Q1, the first capacitor C1, and the third diode D3. .

- the first, eighth, and eleventh switching elements Q1, Q8, and Q11are all.

- the return currents of the inductors L1 and L2pass through the seventh switching element Q7, the second capacitor C2, the eleventh diode D11, the twelfth switching element Q12, the first capacitor C1, and the second switching element Q2. Flowing.

- the first, eighth, and eleventh switching elements Q1, Q8, and Q11are all.

- the return currents of the inductors L1 and L2flow through the sixth switching element Q6, the eleventh diode D11, the twelfth switching element Q12, and the third switching element Q3.

- the second, third, sixth and seventh switching elements Q2, Q3, Q6. , Q7are all set to a dead time. That is, only the eleventh and twelfth switching elements Q11 and Q12 are turned on in the dead time when switching between the third mode and the fourth mode. In this state, the return currents of the inductors L1 and L2 flow through the sixth diode D6, the eleventh switching element Q11, the twelfth switching element Q12, and the third diode D3.

- the dead time when the first to fourth modes are switchedhas been described, but the same dead time is set when the fifth to eighth modes are switched.