USRE48845E1 - Video decoding system supporting multiple standards - Google Patents

Video decoding system supporting multiple standardsDownload PDFInfo

- Publication number

- USRE48845E1 USRE48845E1US16/103,107US201816103107AUSRE48845EUS RE48845 E1USRE48845 E1US RE48845E1US 201816103107 AUS201816103107 AUS 201816103107AUS RE48845 EUSRE48845 EUS RE48845E

- Authority

- US

- United States

- Prior art keywords

- decoding

- media data

- format

- function

- encoding

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime, expires

Links

Images

Classifications

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3861—Recovery, e.g. branch miss-prediction, exception handling

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3877—Concurrent instruction execution, e.g. pipeline or look ahead using a slave processor, e.g. coprocessor

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/10—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding

- H04N19/102—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding characterised by the element, parameter or selection affected or controlled by the adaptive coding

- H04N19/12—Selection from among a plurality of transforms or standards, e.g. selection between discrete cosine transform [DCT] and sub-band transform or selection between H.263 and H.264

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/10—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding

- H04N19/102—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding characterised by the element, parameter or selection affected or controlled by the adaptive coding

- H04N19/12—Selection from among a plurality of transforms or standards, e.g. selection between discrete cosine transform [DCT] and sub-band transform or selection between H.263 and H.264

- H04N19/122—Selection of transform size, e.g. 8x8 or 2x4x8 DCT; Selection of sub-band transforms of varying structure or type

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/10—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding

- H04N19/102—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding characterised by the element, parameter or selection affected or controlled by the adaptive coding

- H04N19/129—Scanning of coding units, e.g. zig-zag scan of transform coefficients or flexible macroblock ordering [FMO]

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/10—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding

- H04N19/134—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding characterised by the element, parameter or criterion affecting or controlling the adaptive coding

- H04N19/157—Assigned coding mode, i.e. the coding mode being predefined or preselected to be further used for selection of another element or parameter

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/10—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding

- H04N19/169—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding characterised by the coding unit, i.e. the structural portion or semantic portion of the video signal being the object or the subject of the adaptive coding

- H04N19/17—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding characterised by the coding unit, i.e. the structural portion or semantic portion of the video signal being the object or the subject of the adaptive coding the unit being an image region, e.g. an object

- H04N19/176—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding characterised by the coding unit, i.e. the structural portion or semantic portion of the video signal being the object or the subject of the adaptive coding the unit being an image region, e.g. an object the region being a block, e.g. a macroblock

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/42—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals characterised by implementation details or hardware specially adapted for video compression or decompression, e.g. dedicated software implementation

- H04N19/423—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals characterised by implementation details or hardware specially adapted for video compression or decompression, e.g. dedicated software implementation characterised by memory arrangements

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/44—Decoders specially adapted therefor, e.g. video decoders which are asymmetric with respect to the encoder

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/60—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using transform coding

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/60—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using transform coding

- H04N19/61—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using transform coding in combination with predictive coding

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/60—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using transform coding

- H04N19/625—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using transform coding using discrete cosine transform [DCT]

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/70—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals characterised by syntax aspects related to video coding, e.g. related to compression standards

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/80—Details of filtering operations specially adapted for video compression, e.g. for pixel interpolation

- H04N19/82—Details of filtering operations specially adapted for video compression, e.g. for pixel interpolation involving filtering within a prediction loop

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/90—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using coding techniques not provided for in groups H04N19/10-H04N19/85, e.g. fractals

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/90—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using coding techniques not provided for in groups H04N19/10-H04N19/85, e.g. fractals

- H04N19/91—Entropy coding, e.g. variable length coding [VLC] or arithmetic coding

Definitions

- the present inventionrelates generally to video decoding systems, and more particularly to a video decoding system supporting multiple standards.

- Digital video decodersdecode compressed digital data that represent video images in order to reconstruct the video images.

- a relatively wide variety of encoding /decoding algorithms and encoding/decoding standardspresently exist, and many additional algorithms and standards are sure to be developed in the future.

- the various algorithms and standardsproduce compressed video bit streams of a variety of formats.

- Some existing public format standardsinclude MPEG -1, MPEG-2 (SD/HD), MPEG-4, H.263, H.263+ and H.26LIJVT.

- private standardshave been developed by Microsoft Corporation (Windows Media), RealNetworks, Inc., Apple Computer, Inc. (QuickTime), and others. It would be desirable to have a multi-format decoding system that can accommodate a variety of encoded bit stream formats, including existing and future standards, and to do so in a cost-effective manner.

- a highly optimized hardware architecturecan be created to address a specific video decoding standard, but this kind of solution is typically limited to a single format.

- a fully software based solutionis often flexible enough to handle any encoding format, but such solutions tend not to have adequate performance for real time operation with complex algorithms, and also the cost tends to be too high for high volume consumer products.

- a common software based solutionis to use a general-purpose processor running in a personal computer, or to use a similar processor in a slightly different system.

- the general-purpose processorincludes special instructions to accelerate digital signal processor (DSP) operations such as multiply-accumulate (MAC); these extensions are intimately tied to the particular internal processor architecture.

- DSPdigital signal processor

- MACmultiply-accumulate

- an Intel Pentium processorincludes an MMX instruction set extension. Such a solution is limited in performance, despite very high clock rates, and does not lend itself to creating mass market, commercially attractive systems.

- VLIWVery Long Instruction Word

- the processorsare difficult to program when compared to a general-purpose processor.

- the DSP and VLIW architecturesare intended for high performance, they still tend not to have enough performance for the present purpose of real time decoding of complex video algorithms.

- special processing acceleratorsare tightly coupled to the instruction pipeline and are part of the core of the main processor.

- One aspect of the present inventionis directed to a digital media decoding system having a processor and a hardware accelerator.

- the processoris adapted to control a decoding process.

- the hardware acceleratoris coupled to the processor and performs a decoding function on a digital media data stream.

- the acceleratoris configurable to perform the decoding function according to a plurality of decoding methods.

- Another aspect of the present inventionis directed to a method of decoding a digital media data stream.

- a first decoding functionis performed on an i th data element of the data stream with a first decoding accelerator.

- a second decoding functionis performed on the i th data element with a second decoding accelerator, while the first decoding function is performed on an i+1 st data element in the data stream with the first decoding accelerator.

- Another aspect of the present inventionis directed to a method of decoding a digital video data stream.

- entropy decodingis performed on an i th data element of the data stream.

- inverse quantizationis performed on a product of the entropy decoding of the i th data element, while entropy decoding is performed on an i+1 st data element in the data stream.

- Still another aspect of the present inventionis directed to a method of decoding a digital media data stream.

- media data of a first encoding/decoding formatis received.

- At least one external decoding functionis configured based on the first encoding/decoding format.

- Media data of the first encoding/decoding formatis decoded using the at least one external decoding function.

- Media data of a second encoding/decoding formatis received.

- the at least one external decoding functionis configured based on the second encoding/decoding format.

- media data of the second encoding/decoding formatis decoded using the at least one external decoding function.

- FIG. 1is a functional block diagram of a digital media system in which the present invention may be illustratively employed.

- FIG. 2is a functional block diagram demonstrating a video decode data flow according to an illustrative embodiment of the present invention.

- FIG. 3is a high-level functional block diagram of a digital video decoding system according to an illustrative embodiment of the present invention.

- FIG. 4ais a functional block diagram of a digital video decoding system according to an illustrative embodiment of the present invention.

- FIG. 4bis a functional block diagram of a motion compensation filter engine according to an illustrative embodiment of the present invention.

- FIG. 5is a block diagram depicting a clocking scheme for a decoding system according to an illustrative embodiment of the present invention.

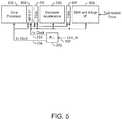

- FIG. 6is a chart representing a decoding pipeline according to an illustrative embodiment of the present invention.

- FIG. 7is a flowchart representing a macroblock decoding loop according to an illustrative embodiment of the present invention.

- FIG. 8is a flowchart representing a method of decoding a digital video data stream containing more than one video data format, according to an illustrative embodiment of the present invention.

- FIG. 1is a functional block diagram of a digital media system in which the present invention may be illustratively employed. It will be noted, however, that the present invention can be employed in systems of widely varying architectures and widely varying designs.

- the digital media system of FIG. 1includes transport processor 102 , audio decoder 104 , direct memory access (DMA) controller 106 , system memory controller 108 , system memory 110 , host CPU interface 112 , host CPU 114 , digital video decoder 116 , display feeder 118 , display engine 120 , graphics engine 122 , display encoders 124 and analog video decoder 126 .

- the transport processor 102receives and processes a digital media data stream.

- the transport processor 102provides the audio portion of the data stream to the audio decoder 104 and provides the video portion of the data stream to the digital video decoder 116 .

- the audio and video datais stored in main memory 110 prior to being provided to the audio decoder 104 and the digital video decoder 116 .

- the audio decoder 104receives the audio data stream and produces a decoded audio signal.

- DMA controller 106controls data transfer amongst main memory 110 and memory units contained in elements such as the audio decoder 104 and the digital video decoder 116 .

- the system memory controller 108controls data transfer to and from system memory 110 .

- system memory 110is a dynamic random access memory (DRAM) unit.

- the digital video decoder 116receives the video data stream, decodes the video data and provides the decoded data to the display engine 120 via the display feeder 118 .

- DRAMdynamic random access memory

- the analog video decoder 126digitizes and decodes an analog video signal (NTSC or PAL) and provides the decoded data to the display engine 120 .

- the graphics engine 122processes graphics data in the data stream and provides the processed graphics data to the display engine 120 .

- the display engine 120prepares decoded video and graphics data for display and provides the data to display encoders 124 , which provide an encoded video signal to a display device.

- FIG. 2is a functional block diagram demonstrating a video decode data flow according to an illustrative embodiment of the present invention.

- Transport streamsare parsed by the transport processor 102 and written to main memory 110 along with access index tables.

- the video decoder 116retrieves the compressed video data for decoding, and the resulting decoded frames are written back to main memory 110 .

- Decoded framesare accessed by the display feeder interface 118 of the video decoder for proper display by a display unit.

- two video streamsare shown flowing to the display engine 120 , suggesting that, in an illustrative embodiment, the architecture allows multiple display streams by means of multiple display feeders.

- aspects of the present inventionrelate to the architecture of digital video decoder 116 .

- a moderately capable general purpose CPU with widely available development toolsis used to decode a variety of coded streams using hardware accelerators designed as integral parts of the decoding process.

- the most widely-used compressed video formatsfall into a general class of DCT-based, variable-length coded, block-motion-compensated compression algorithms.

- these types of algorithmsencompass a wide class of international, public and private standards, including MPEG-1, MPEG-2 (SD/HD), MPEG-4, H.263, H.263-F, H.26LINT, Microsoft Corp, Real Networks, QuickTime, and others. Fundamental functions exist that are common to most or all of these formats.

- Such functionsinclude, for example, programmable variable-length decoding (VLD), arithmetic decoding (AC), inverse quantization (IQ), inverse discrete cosine transform (IDCT), pixel filtering (PF), motion compensation (MC), and deblocking/de-ringing (loop filtering or post-processing).

- VLDprogrammable variable-length decoding

- ACarithmetic decoding

- IQinverse quantization

- IDCTinverse discrete cosine transform

- PFpixel filtering

- MCmotion compensation

- deblocking/de-ringingloop filtering or post-processing

- these hardware modulesare provided with sufficient flexibility or programmability enabling a decoding system that decodes a variety of standards efficiently and flexibly.

- the decoding system of the present inventionemploys high-level granularity acceleration with internal programmability or configurability to achieve the requirements above by implementation of very fundamental processing structures that can be configured dynamically by the core decoder processor.

- MACmultiply-accumulate

- the decompression algorithmhas to be implemented with firmware that uses individual low-level instructions (such as MAC) to implement a high-level function, and each instruction runs on the core processor.

- the firmwareconfigures each hardware accelerator, which in turn represent high-level functions (such as motion compensation) that run (using a well-defined specification of input data) without intervention from the main core processor. Therefore, each hardware accelerator runs in parallel according to a processing pipeline dictated by the firmware in the core processor. Upon completion of the high-level functions, each accelerator notifies the main core processor, which in turn decides what the next processing pipeline step should be.

- high-level functionssuch as motion compensation

- the software controltypically consists of a simple pipeline that orchestrates decoding by issuing commands to each hardware accelerator module for each pipeline stage, and a status reporting mechanism that makes sure that all modules have completed their pipeline tasks before issuing the start of the next pipeline stage.

- FIG. 3is a high-level functional block diagram of a digital video decoding system 300 according to an illustrative embodiment of the present invention.

- the digital video decoding system 300 of FIG. 3can illustratively be employed to implement the digital video decoder 116 of FIGS. 1 and 2 .

- the core processor 302is the central control unit of the decoding system 300 .

- the core processor 302prepares the data for decoding.

- the core processor 302also orchestrates the macroblock (MB) processing pipeline for all modules and fetches the required data from main memory via the bridge 304 .

- the core processor 302also handles some data processing tasks.

- MBmacroblock

- Picture level processingincluding sequence headers, GOP headers, picture headers, time stamps, macroblock-level information except the block coefficients, and buffer management, are performed directly and sequentially by the core processor 302 , without using the accelerators 304 , 306 , 308 , 309 , 310 , 312 and 314 other than the PVLD 306 (which accelerates general bitstream parsing). Picture level processing does not overlap with slice level/macroblock decoding in this embodiment.

- Programmable variable length decoder (PVLD) 306inverse quantizer 308 , inverse transform module 309 , pixel filter 310 , motion compensation module 312 and loop/post filter 314 are hardware accelerators that accelerate special decoding tasks that would otherwise be bottlenecks for real-time video decoding if these tasks were handled by the core processor 302 alone.

- Each hardware module 306 , 308 , 309 , 310 , 312 and 314is internally configurable or programmable to allow changes according to various processing algorithms.

- modules 308 and 309are implemented in the form of a transform engine 307 that handles all functionality, but which is conceptually equivalent to the union of 308 and 309 .

- modules 310 and 312are implemented in the form of a filter engine 311 which consists of an internal SIMD (single instruction multiple data) processor and a general purpose controller to interface to the rest of the system, but which is conceptually equivalent to the union of 310 and 312 .

- module 314is implemented in the form of another filter engine similar to 311 which consists of an internal SIMD (single instruction multiple data) processor and a general purpose controller to interface to the rest of the system, but which is conceptually equivalent to 314 .

- module 314is implemented in the form of the same filter engine 311 that can also implement the equivalent function of the combination of 310 and 311 .

- each hardware module 306 , 308 , 309 , 310 , 312 and 314performs its task after being so instructed by the core processor 302 .

- each hardware moduleincludes a status register that indicates whether the module has completed its assigned tasks.

- the ore processor 302polls the status register to determine whether the hardware module has completed its task.

- the hardware acceleratorsshare a status register.

- the PVLD engine 306performs variable-length code (VLD) decoding of the block DCT coefficients. It also helps the core processor 302 to decode the header information in the compressed bitstream.

- VLDvariable-length code

- the PVLD module 306is designed as a coprocessor to the core processor 302 , while the rest of the modules 308 , 309 , 310 , 312 and 314 are designed as hardware accelerators.

- the PVLD module 306includes two variable length decoders. Each of the two programmable variable-length decoders can be hardwired to efficiently perform decoding according to a particular video compression standard, such as MPEG2 HD.

- One of themcan be optionally set as a programmable VLD engine, with a code RAM to hold VLC tables for media coding formats other than MPEG2.

- the two VLD enginesare controlled independently by the core processor 302 , and either one or both of them will be employed at any given time, depending on the application.

- the IQ engine 308performs run-level pair decoding, inverse scan and quantization.

- the inverse transform engine 309performs IDCT operations or other inverse transform operations like the Integer Transform of the H.26x standards.

- the IQ module 308 and the inverse transform module 309are part of a common hardware module and use a similar interface to the core processor 302 .

- the pixel filter 310performs pixel filtering and interpolation.

- the motion compensation module 312performs motion compensation.

- the pixel filter 310 and motion compensation module 312are shown as one module in the diagram to emphasize a certain degree of direct cooperation between them.

- the PF module 310 and the MC module 312are part of a common programmable module 311 designated as a filter engine capable of performing internal SIMD instructions to process data in parallel with an internal control processor.

- the filter module 314performs the de-blocking operation common in many low bit-rate coding standards.

- the filter modulecomprises a loop filter that performs de-blocking within the decoding loop.

- the filter modulecomprises a post filter that performs de-blocking outside the decoding loop.

- the filter modulecomprises a de-ringing filter, which may function as either a loop filter or a post filter, depending on the standard of the video being processed.

- the filter module 314includes both a loop filter and a post filter.

- the filter module 314is implemented using the same filter engine 311 implementation as for 310 and 312 , except that module 311 is programmed to produce deblocked or deringed data as the case may be.

- the bridge module 304arbitrates and moves picture data between decoder memory 316 and main memory.

- the bridge interface 304includes an internal bus network that includes arbiters and a direct memory access (DMA) engine.

- the bridge 304serves as an interface to the system buses.

- the display feeder module 318reads decoded frames from main memory and manages the horizontal scaling and displaying of picture data.

- the display feeder 318interfaces directly to a display module.

- the display feeder 318converts from 420 to 422 color space.

- the display feeder 318includes multiple feeder interfaces, each including its own independent color space converter and horizontal scaler. The display feeder 318 handles its own memory requests via the bridge module 304 .

- Decoder memory 316is used to store macroblock data and other time-critical data used during the decode process.

- Each hardware block 306 , 308 , 309 , 310 , 312 , 314accesses decoder memory 316 to either read the data to be processed or write processed data back. In an illustrative embodiment of the present invention, all currently used data is stored in decoder memory 316 to minimize accesses to main memory.

- Each hardware module 306 , 308 , 309 , 310 , 312 , 314is assigned one or more buffers in decoder memory 316 for data processing. Each module accesses the data in decoder memory 316 as the macro blocks are processed through the system.

- decoder memory 316also includes parameter buffers that are adapted to hold parameters that are needed by the hardware modules to do their job at a later macroblock pipeline stage.

- the buffer addressesare passed to the hardware modules by the core processor 302 .

- decoder memory 316is a static random access memory (SRAM) unit.

- FIG. 4ais a functional block diagram of digital video decoding system 300 according to an illustrative embodiment of the present invention.

- elements that are common to FIG. 3are given like reference numbers.

- various elementsare grouped together to illustrate a particular embodiment where 308 and 309 form part of a transform engine 307 , 310 and 312 form part of a filter engine 311 that is a programmable module that implements the functionality of PF and MC, 313 and 315 form part of another filter engine 314 which is another instance of the same programmable module except that it is programmed to implement the functionality of a loop filter 313 and a post filter 315 .

- FIG. 4ashows, phase-locked loop (PLL) element 320 , internal data bus 322 , register bus 324 and separate loop and post filters 313 and 315 embodied in a filter engine module 314 which implements the functionality of 313 and 315 .

- PLLphase-locked loop

- the core processor 302is the master of the decoding system 300 . It controls the data flow of decoding processing. All video decode processing, except where otherwise noted, is performed in the core processor.

- the PVLD 306 , IQ 308 , inverse transform 309 , PF 310 and MC 312 , and filter 314are hardware accelerators to help the core processor achieve the required performance.

- the core processor 302is a MIPS processor, such as a MIPS32 implementation, for example.

- the core processor 302incorporates a D cache and an I cache. The cache sizes are chosen to ensure that time critical operations are not impacted by cache misses. For example, instructions for macroblock-level processing of MPEG-2 video runs from cache.

- time-critical code and dataalso reside in cache.

- the determination of exactly which functions are stored in cacheinvolves a trade-off between cache size, main memory access time, and the degree of certainty of the firmware implementation for the various algorithms.

- the cache behavior with proprietary algorithmsdepends in part in the specific software design. In an illustrative embodiment, the cache sizes are 16 kB for instructions and 4 kB for data. These can be readily expanded if necessary.

- the core processor 302interprets the decoded bits for the appropriate headers and decides and coordinates the actions of the hardware blocks 306 , 308 , 309 , 310 , 312 and 314 . Specifically, all macroblock header information, from the macroblock address increment (MBAinc) to motion vectors (MV s) and to the cbp pattern in the case of MPEG2 decoding, for example, is derived by the core processor 302 . The core processor 302 stores related information in a particular format or data structure (determined by the hardware module specifications) in the appropriate buffers in the decoder memory 316 .

- the quantization scaleis passed to the buffer the IQ engine 308 ; macroblock type, motion type and pixel precision are stored in the parameter buffer for the pixel filter engine 310 .

- the core processorkeeps track of certain information in order to maintain the correct pipeline, and it may store some such information in its D cache, some in main system memory and some in the decoder memory 316 , as required by the specific algorithm being performed. For example, for some standards, motion vectors of the macroblock are kept as the predictors for future motion vector derivation.

- the programmable variable length decoder 306performs decoding of variable length codes (VLC) in the compressed bit stream to extract values, such as DCT coefficients, from the compressed data stream.

- VLCvariable length codes

- Different coding formatsgenerally have their own unique VLC tables.

- the PVLD 306is completely configurable in terms of the VLC tables it can process.

- the PVLD 306can accommodate a dynamically changing set of VLC tables, for example they may change on a macroblock-to-macroblock basis.

- the PVLD 306includes a register that the core processor can program to guide the PVLD 306 to search for the VLC table of the appropriate encoding/decoding algorithm.

- the PVLD 306decodes variable length codes in as little as one clock, depending on the specific code table in use and the specific code being decoded.

- the PVLD 306is designed to support the worst-case requirement for VLD operation with MPEG-2 HDTV (MP@HL), while retaining its full programmability.

- the PVLD 306includes a code table random access memory (RAM) for fastest performance. Code tables such a MPEG-2 video can fit entirely within the code RAM. Some formats, such as proprietary formats, may require larger code tables that do not fit entirely within the code RAM in the PVLD 306 . For such cases, the PVLD 306 can make use of both the decoder memory 316 and the main memory as needed. Performance of VLC decoding is reduced somewhat when codes are searched in video memory 316 and main memory.

- the most common codesare typically stored in the PVLD code RAM, the next most common codes are stored in decoder memory, and the least common codes are stored in main memory. Also, such codes are stored in decoder memory 316 and main memory such that even when extended look-ups in decoder memory 316 and main memory are required, the most commonly occurring codes are found more quickly. This allows the overall performance to remain exceptionally high.

- the PVLD 306is architected as a coprocessor of the core processor 302 . That is, it can operate on a single-command basis where the core processor issues a command (via a coprocessor instruction) and waits (via a Move From Coprocessor instruction) until it is executed by the PVLD 306 , without polling to determine completion of the command. This increases performance when a large number of VLC codes are parsed under software control. Additionally, the PVLD 306 can operate on a block-command basis where the core processor 302 commands the PVLD 306 to decode a complete block of VLC codes, such as DCT coefficients, and the core processor 302 continues to perform other tasks in parallel. In this case, the core processor 302 verifies the completion of the block operation by checking a status bit in the PVLD 306 . The PVLD produces results (tokens) that are stored in decoder memory 316 .

- the PVLD 306checks for invalid codes and recovers gracefully from them. Invalid codes may occur in the coded bit stream for a variety of reasons, including errors in the video encoding, errors in transmission, and improper discontinuities in the stream.

- the inverse quantizer module 308performs run-level code (RLC) decoding, inverse scanning (also called zig-zag scanning), inverse quantization and mismatch control.

- the coefficients, such as DCT coefficients, extracted by the PVLD 306are processed by the inverse quantizer 308 to bring the coefficients from the quantized domain to the DCT domain.

- the IQ module 308obtains its input data (run-level values) from the decoder memory 316 , as the result of the PVLD module 306 decoding operation.

- the IQ module 308obtains its input data directly from the PVLD 306 .

- This alternative embodimentis illustratively employed in conjunction with encoding/decoding algorithms that are relatively more involved, such as MPEG-2 HD decoding, for best performance.

- the run-length, value and end-of-block codes read by the IQ module 308are compatible with the format created by the PVLD module when it decodes blocks of coefficient VLCs, and this format is not dependent on the specific video coding format being decoded.

- the IQ 308 and inverse transform 309 modulesform part of a tightly coupled module labeled transform engine 307 . This embodiment has the advantage of providing fast communication between modules 308 and 309 by virtue of being implemented in the same hardware block.

- the scan pattern of the IQ module 308is programmable in order to be compatible with any required pattern.

- the quantization formatis also programmable, and mismatch control supports a variety of methods, including those specified in MPEG-2 and MPEG-4.

- the IQ module 308can accommodate block sizes of 16 ⁇ 16, 8 ⁇ 8, 8 ⁇ 4, 4 ⁇ 8 and 4 ⁇ 4.

- the IQ module 308includes one or more registers that are used to program the scan pattern, quantization matrix and mismatch control method. These registers are programmed by the core processor 302 to dictate the mode of operation of the IQ module.

- the IQ module 306is designed in such a way that the core processor 302 can intervene at any point in the process, in case a particular decoding algorithm requires software processing of some aspect of the algorithmic steps performed by the IQ module 308 . For example, there may be cases where an unknown algorithm could require a different form of rounding; this can be performed in the core processor 302 .

- the IQ module 308has specific support for AC prediction as specified in MPEG-4 Advanced Simple Profile. In an exemplary embodiment, the IQ module 308 also has specific support for the inverse quantization functions of the ISO-ITU NT (Joint Video Team) standard under development.

- the inverse transform module 309performs the inverse transform to convert the coefficients produced by the IQ module 308 from the frequency domain to the spatial domain.

- the primary transform supportedis the IDCT, as specified in MPEG-2, MPEG-4, IEEE, and several other standards.

- the coefficientsare programmable, and it can support alternative related transforms, such as the “linear” transform in H.26L (also known as JVT), which is not quite the same as IDCT.

- the inverse transform module 309supports a plurality of matrix sizes, including 8 ⁇ 8, 4 ⁇ 8, 8 ⁇ 4 and 4 ⁇ 4 blocks.

- the inverse transform module 309includes a register that is used to program the matrix size. This register is programmed by the core processor 302 according to the appropriate matrix size for the encoding/decoding format of the data stream being decoded.

- the coefficient input to the inverse transform module 309is read from decoder memory 316 , where it was placed after inverse quantization by the IQ module 308 .

- the transform resultis written back to decoder memory 316 .

- the inverse transform module 309uses the same memory location in decoder memory 316 for both its input and output, allowing a savings in on-chip memory usage.

- the coefficients produced by the IQ moduleare provided directly to the inverse transform module 309 , without first depositing them in decoder memory 316 .

- the IQ module 308 and inverse transform module 309use a common interface directly between them for this purpose.

- the transfer of coefficients from the IQ module 308 to the inverse transform module 309can be either direct or via decoder memory 316 .

- the transferis direct in order to save time and improve performance.

- the functionality of the PF 310 and MC 312are implemented by means of a filter engine (FE) 311 .

- the FEis the combination of an 8-way SIMD processor 2002 and a 32-bit RISC processor 2004 , illustrated in FIG. 4b . Both processors operate at the same clock frequency.

- the SIMD engine 2002is architected to be very efficient as a coprocessor to the RISC processor (internal MIPS) 2004 , performing specialized filtering and decision-making tasks.

- the SIMD 2002includes: a split X-memory 2006 (allowing simultaneous operations), a Y-memory, a Z-register input with byte shift capability, 16 bit per element inputs, and no branch or jump functions.

- the SIMD processor 2002has hardware for three-level looping, and it has a hardware function call and return mechanism for use as a coprocessor. All of these help to improve performance and minimize the area.

- the RISC processor 2004controls the operations of the FE 311 . Its functions include the control of the data flow and scheduling tasks. It also takes care of part of the decision-making functions.

- the FE 311operates like the other modules on a macro block basis under the control of the mum core processor 302 .

- the pixel filter 310performs pixel filtering and interpolation as part of the motion compensation process.

- Motion compensationuses a small piece of an image from a previous frame to predict a piece of the current image; typically the reference image segment is in a different location within the reference frame. Rather than recreate the image anew from scratch, the previous image is used and the appropriate region of the image moved to the proper location within the frame; this may represent the image accurately, or more generally there may still be a need for coding the residual difference between this prediction and the actual current image.

- the new locationis indicated by motion vectors that denote the spatial displacement in the frame with respect to the reference frame.

- the pixel filter 310performs the interpolation necessary when a reference block is translated (motion-compensated) by a vector that cannot be represented by an integer number of whole-pixel locations. For example, a hypothetical motion vector may indicate to move a particular block 10.5 pixels to the right and 0.25 pixels down for the motion-compensated prediction.

- the motion vectorsare decoded by the PVLD 3D6 in a previous processing pipeline stage and are further processed in the core processor 302 before being passed to the pixel filter, typically via the decoder memory 316 .

- the pixel filter 310gets the motion information as vectors and not just bits from the bitstream.

- the reference block data that is used by the motion compensation processis read by the pixel filter 310 from the decoder memory 316 , the required data having been moved to decoder memory 316 from system memory 110 ; alternatively the pixel filter obtains the reference block data from system memory 110 .

- the pixel filterobtains the processed motion vectors from decode memory 316 .

- the pixel data that results from motion compensation of a given macroblockis stored in memory after decoding of said macroblock is complete.

- the decoded macroblock datais written to decoder memory 316 and then transferred to system memory 110 ; alternatively, the decoded macro block data may be written directly to system memory 110 . If and when that decoded macroblock data is needed for additional motion compensation of another macroblock, the pixel filter 310 retrieves the reference macroblock pixel information from memory, as above, and again the reconstructed macroblock pixel information is written to memory, as above.

- the pixel filter 310supports a variety of filter algorithms, including 1 ⁇ 2 pixel and 1 ⁇ 4 pixel interpolations in either or both of the horizontal and vertical axes; each of these can have many various definitions, and the pixel filter can be configured or programmed to support a wide variety of filters, thereby supporting a wide range of video formats, including proprietary formats.

- the PF modulecan process block sizes of 4, 8 or 16 pixels per dimension (horizontal and vertical), or even other sizes if needed.

- the pixel filter 310is also programmable to support different interpolation algorithms with different numbers of filter taps, such as 2, 4, or 6 taps per filter, per dimension.

- the pixel filter 309includes one or more registers that are used to program the filter algorithm and the block size. These registers are programmed by the core processor 302 according to the motion compensation technique employed with the encoding/decoding format of the data stream being decoded.

- the pixel filteris implemented using the filter engine (FE) architecture, which is programmable to support any of a wide variety of filter algorithms. As such, in either type of embodiment, it supports a very wide variety of motion compensation schemes.

- FEfilter engine

- the motion compensation module 312reconstructs the macroblock being decoded by performing the addition of the decoded difference (or residual or “error”) pixel information from the inverse transform module 309 to the pixel prediction data from the output of the pixel filter 310 .

- the motion compensation module 312is programmable to support a wide variety of block sizes, including 16 ⁇ 16, 16 ⁇ 8, 8 ⁇ 16, 8 ⁇ 8, 8 ⁇ 4, 4 ⁇ 8 and 4 ⁇ 4.

- the motion compensation module 312is also programmable to support different transform block types, such as field-type and frame-type transform blocks.

- the motion compensation module 312is further programmable to support different matrix formats.

- MC module 312supports all the intra and inter prediction modes in the H.26L/JVT proposed standard.

- the motion compensation module 312includes one or more registers that are configurable to select the block size and format. These registers are programmed by the core processor 302 according to the motion compensation technique employed with the encoding/decoding format of the data stream being decoded.

- the motion compensation moduleis a function of a filter engine (FE) that is serving as the pixel filter and motion compensation modules, and it is programmable to perform any of the motion compensation functions and variations that are required by the format being decoded.

- FEfilter engine

- the loop filter 313 and post filter 315perform de-blocking filter operations.

- the loop filter 313 and post filter 315are combined in one filter module 314 , as shown in FIG. 3 .

- the filter module 314in an illustrative embodiment is the same processing structure as described for 311 , except that it is programmed to perform the functionality of 313 and 315 .

- Some decoding algorithmsemploy a loop filter and others employ a post filter. Therefore, the filter module 314 (or loop filter 313 and post filter 315 independently) is programmable to turn on either the loop filter 313 or the post filter 315 or both.

- the filter module 314(or loop filter 313 and post filter 315 ) has a register that controls whether a loop filter or post filter scheme is employed.

- the core processor 302programs the filter module register(s) according to the bit-stream semantics.

- the loop filter 313 and post filter 315each have programmable coefficients and thresholds for performing a variety of de-blocking algorithms in either the horizontal or vertical directions. Deblocking is required in some low bit-rate algorithms. De-blocking is not required in MPEG-2. However, in one embodiment of the present invention, de-blocking is used to advantage with MPEG-2 at low bit rates.

- the input data to the loop filter 313 and post filter 315comes from decoder memory 316 , the input pixel data having been transferred from system memory 110 as appropriate, typically at the direction of the core processor 302 .

- This dataincludes pixel and block/macroblock parameter data generated by other modules in the decoding system 300 .

- the output data from the loop filter 313 and post filter 315is written into decoder memory 316 .

- the core processor 302then causes the processed data to be put in its correct location in system memory 110 .

- the core processor 302can program operational parameters into loop filter 313 and post filter 315 registers at any time. In an illustrative embodiment, all parameter registers are double buffered.

- the loop filter 313 and post filter 315obtain input pixel data from system memory 110 , and the results may be written to system memory 110 .

- the loop filter 313 and post filter 315are both programmable to operate according to any of a plurality of different encoding/decoding algorithms.

- the loop filter 313 and post filter 315can be programmed similarly to one another. The difference is where in the processing pipeline each filter 313 , 315 does its work.

- the loop filter 313processes data within the reconstruction loop and the results of the filter are used in the actual reconstruction of the data.

- the post filter 315processes data that has already been reconstructed and is fully decoded in the two-dimensional picture domain.

- the coefficients, thresholds and other parameters employed by the loop filter 313 and the post filter 315are programmed by the core processor 302 according to the de-blocking technique employed with the encoding/decoding format of the data stream being decoded.

- the core processor 302 , bridge 304 , PVLD 306 , IQ 308 , inverse transform module 309 , pixel filter 310 , motion compensation module 312 , loop filter 313 and post filter 315have access to decoder memory 316 via the internal bus 322 or via equivalent functionality in the bridge 304 .

- the PVLD 306 , IQ 308 , inverse transform module 309 , pixel filter 310 , motion compensation module 312 , loop filter 313 and post filter 315use the decoder memory 316 as the source and destination memory for their normal operation.

- the PL VD 306uses the system memory 110 as the source of its data in normal operation.

- the pixel filter 310 and motion compensation module 312use the decoder memory 316 as the source for residual pixel information and they use system memory 110 as the source for reference pixel data and as the destination for reconstructed pixel data.

- the loop filter 313 and post processor 315use system memory 110 as the source and destination for pixel data in normal operation.

- the CPUhas access to decoder memory 316 , and the DMA engine 304 can transfer data between decoder memory 316 and the main system memory 110 .

- the arbiter for decoder memory 316is in the bridge module 304 .

- decoder memory 316is a static random access memory (SRAM) unit.

- the bridge module 304performs several functions.

- the bridge module 304includes an interconnection network to connect all the other modules of the MVP as shown schematically as internal bus 322 and register bus 324 . It is the bridge between the various modules of decoding system 300 and the system memory. It is the bridge between the register bus 324 , the core processor 302 , and the main chip-level register bus. It also includes a DMA engine to service the memories within the decoder system 300 , including decoder memory 316 and local memory units within individual modules such as PVLD 306 .

- the bridge moduleillustratively includes an asynchronous interface capability and it supports different clock rates in the decoding system 300 and the main memory bus, with either clock frequency being greater than the other.

- the bridge module 304implements a consistent interface to all of the modules of the decoding system 300 where practical.

- Logical register bus 324connects all the modules and serves the purpose of accessing control and status registers by the main core processor 302 . Coordination of processing by the main core processor 302 is accomplished by a combination of accessing memory, control and status registers for all modules.

- the display feeder 318 modulereads decoded pictures (frames or fields, as appropriate) from main memory in their native decoded format (4:2:0, for example), converts the video into 4:2:2 format, and performs horizontal scaling using a polyphase filter.

- the coefficients, scale factor, and the number of active phases of the polyphase filterare programmable.

- the display feeder 318includes one or more registers that are used to program these parameters. These registers are programmed by the core processor 302 according to the desired display format.

- the polyphase filteris an 8 tap, 11 phase filter.

- the outputis illustratively standard 4:2:2 format YCrCb video, in the native color space of the coded video (for example, ITU-T 709-2 or ITU-T 601-B color space), and with a horizontal size that ranges, for example, from 160 to 1920 pixels.

- the horizontal scalercorrects for coded picture sizes that differ from the display size, and it also provides the ability to scale the video to arbitrary smaller or larger sizes, for use in conjunction with subsequent 2-dimensional scaling where required for displaying video in a window, for example.

- the display feeder 318is adapted to supply two video scan lines concurrently, in which case the horizontal scaler in the feeder 318 is adapted to scale two lines concurrently, using identical parameters.

- FIG. 5is a block diagram depicting a clocking scheme for decoding system 300 according to an illustrative embodiment of the present invention.

- Hardware accelerators block 330includes PVLD 306 , IQ 308 , inverse transform module 309 , pixel filter 310 , motion compensation module 312 and filter engine 314 .

- the core processor 302runs at twice the frequency of the other processing modules.

- hardware accelerator block 330includes PVLD 306 , IQ 308 , and inverse transform module 309 , while one instance of the filter engine module 311 implements pixel filter 310 and motion compensation 312 , and yet another instance of the filter module 314 implements loop filter 313 and post filter 315 , noting that FE 311 and FE 314 receive both 243 MHz and 121.5 MHz clocks.

- the core processorruns at 243 MHz and the individual modules at half this rate, i.e., 121.5 MHz.

- the system clock signal (CLK_IN) 332is used as input to the phase locked loop element (PLL) 320 , which is a closed-loop feedback control system that locks to a particular phase of the system clock to produce a stable signal with little jitter.

- the PLL element 320generates a IX clock (targeting, e.g., 121.5 MHz) for the hardware accelerators 330 , bridge 304 and the core processor bus interface 303 , while generating a 2X clock (targeting, e.g., 243 MHz) for the core processor 302 and the core processor bus interface 303 .

- picture level processingfrom the sequence level down to the slice level, including the sequence headers, picture headers, time stamps, and buffer management, are performed directly and sequentially by the core processor 302 .

- the PVLD 306assists the core processor when a bit-field in a header is to be decoded.

- Picture level processingdoes not overlap with macroblock level decoding.

- the macroblock level decodingis the main video decoding process. It occurs within a direct execution loop.

- hardware blocks PVLD 306 , IQ 308 , inverse transform module 309 , pixel filter 310 , motion compensation module 312 (and, depending on which decoding algorithm is being executed, possibly loop filter 313 )are all involved in the decoding loop.

- the core processor 302controls the loop by polling the status of each of the hardware blocks involved.

- Still another aspect of the present inventionis directed to a method of decoding a digital media data stream.

- media data of a first encoding/decoding formatis received.

- At least one external decoding functionsuch as variable-length decoding or inverse quantization, e.g., is configured based on the first encoding/decoding format.

- Media data of the first encoding/decoding formatis decoded using the at least one external decoding function.

- Media data of a second encoding/decoding, formatis received.

- the at least one external decoding functionis configured based on the second encoding/decoding format.

- media data of the second encoding/decoding formatis decoded using the at least one external decoding function.

- the actions of the various hardware blocksare arranged in an execution pipeline comprising a plurality of stages.

- stagecan refer to all of the decoding functions performed during a given time slot, or it can refer to a functional step, or group of functional steps, in the decoding process.

- the pipeline schemeaims to achieve maximum throughput in defined worst case decoding scenarios. Pursuant to this objective, it is important to utilize the core processor efficiently.

- FIG. 6is a chart representing a decoding pipeline according to an illustrative embodiment of the present invention. The number of decoding functions in the pipeline may vary depending on the target applications. Due to the selection of hardware elements that comprise the pipeline, the pipeline architecture of the present invention can accommodate, at least, substantially any existing or future compression algorithms that fall into the general class of block-oriented algorithms.

- the rows of FIG. 6represent the decoding functions performed as part of the pipeline according to an exemplary embodiment.

- Variable length decoding 600is performed by PVLD 306 .

- Run length/inverse scan/IQ/mismatch 602are functions performed by IQ module 308 .

- Inverse transform operations 604are performed by the inverse transform module 309 .

- Pixel filter reference fetch 606 and pixel filter reconstruction 608are performed by pixel filter 310 .

- Motion compensation reconstruction 610is performed by motion compensation module 312 .

- the columns of FIG. 6represent the pipeline stages.

- the designations MB i , MB i+2 , etc.represent the i th macroblock in a data stream, the i+1 st macroblock in the data stream, the i+2 nd macroblock, and so on.

- the pipeline schemesupports one pipeline stage per module, wherein any hardware module that depends on the result of another module is arranged in a following MB pipeline stage. In an illustrative embodiment, the pipeline scheme

- variable length decoding 600is performed on MBi.

- Exploded view 620 of the variable length decoding function 600demonstrates how functions are divided between the core processor 302 and the PVLD 306 during this stage, according to one embodiment of the present invention. Exploded view 620 shows that during stage x 612 , the core processor 302 decodes the macmblock header of MB i . The PVLD 306 assists the core processor 302 in the decoding of macroblock headers.

- the core processor 302also reconstructs the motion vectors of MB i , calculates the address of the pixel filter reference fetch for MB i , performs pipeline flow control and checks the status of IQ module 308 , inverse transform module 309 , pixel filter 310 and motion compensator 312 during stage x 612 .

- the hardware blocksoperate concurrently with the core processor 302 while decoding a series of macroblocks.

- the core processor 302controls the pipeline, initiates the decoding of each macroblock, and controls the operation of each of the hardware accelerators.

- the core processor firmwarechecks the status of each of the hardware blocks to determine completion of previously assigned tasks and checks the buffer availability before advancing the pipeline. Each block will then process the corresponding next macroblock.

- the PVLD 306also decodes the macro block coefficients of Mbi during stage x.

- Block coefficient VLC decodingis not started until the core processor 302 decodes the whole macro block header. Note that the functions listed in exploded view 620 are performed during each stage of the pipeline of FIG. 6 , even though, for simplicity's sake, they are only exploded out with respect to stage x 612 .

- the inverse quantizer 308works on MB i (function 602 ) while variable length decoding 600 is performed on the next macroblock, MB i+1 .

- the data that the inverse quantizer 308 works onare the quantized transform coefficients of MB i extracted from the data stream by the PVLD 306 during stage x 612 .

- the pixel filter reference datais fetched for MB i (function 606 ) using the pixel filter reference fetch address calculated by the core processor 302 during stage x 612 .

- the inverse transform module 309performs inverse transform operations 604 on the MB i transform coefficients that were output by the inverse quantizer 308 during stage x+1.

- the pixel filter 310performs pixel filtering 608 for MB i using the pixel filter reference data fetched in stage x+1 614 and the motion vectors reconstructed by the core processor 302 in stage x 612 .

- the inverse quantizer 308works on MB i+1 (function 602 ), the pixel filter reference data is fetched for MB i+1 (function 606 ), and variable length decoding 600 is performed on MB i+2 .

- the motion compensation module 312performs motion compensation reconstruction 610 on MB i using decoded difference pixel information produced by the inverse transform module 309 (function 604 ) and pixel prediction data produced by the pixel filter 310 (function 608 ) in stage x+2 616 .

- the inverse transform module 309performs inverse transform operations 604 on MB i+h the pixel filter 310 performs pixel filtering 608 for MB i+1 , the inverse quantizer 308 works on MBi+2 (function 602 ), the pixel filter reference data is fetched for MB i+2 (function 606 ), and variable length decoding 600 is performed on MB i+3 .

- the pipeline of FIG. 6shows just four pipeline stages, in an illustrative embodiment of the present invention, the pipeline includes as many stages as is needed to decode a complete incoming data stream.

- the functions of two or more hardware modulesare combined into one pipeline stage and the macroblock data is processed by all the modules in that stage sequentially.

- inverse transform operations for a given macroblockare performed during the same pipeline stage as IQ operations.

- the inverse transform module 309waits idle until the inverse quantizer 308 finishes and the inverse quantizer 308 becomes idle when the inverse transform operations start.

- This embodimentwill have a longer processing time for the “packed” pipeline stage, and therefore such embodiments may have lower throughput.

- the benefits of the packed stage embodimentinclude fewer pipeline stages, fewer buffers and possibly simpler control for the pipeline.

- the above-described macroblock-level pipelineadvances stage-by-stage.

- the pipelineadvances after all the tasks in the current stage are completed.

- the time elapsed in one macroblock pipeline stagewill be referred to herein as the macroblock (MB) time.

- the MB timeis not a constant and varies from stage to stage according to various factors, such as the amount of processing time required by a given acceleration module to complete processing of a given block of data in a given stage. It depends on the encoded bitstream characteristics and is determined by the bottleneck module, which is the one that finishes last in that stage. Any module, including the core processor 302 itself, could be the bottleneck from stage to stage and it is not pre-determined at the beginning of each stage.

- each moduleincluding the core processor 302 , has a defined and predetermined task or group of tasks to complete.

- the macroblock time for each moduleis substantially constant for a given decoding standard. Therefore, in an illustrative embodiment of the present invention, the hardware acceleration pipeline is optimized by hardware balancing each module in the pipeline according to the compression format of the data stream.

- the main video decoding operationsoccur within a direct execution loop that also includes polling of the accelerator functions.

- the coprocessor/acceleratorsoperate concurrently with the core processor while decoding a series of macro blocks.

- the core processor 302controls the pipeline, initiates the decoding of each macro block, and controls the operation of each of the accelerators.

- the core processoralso does a lot of actual decoding, as described in previous paragraphs.

- firmwarechecks the status of each of the accelerators to determine completion of previously assigned tasks. In the event that the firmware gets to this point before an accelerator module has completed its required tasks, the firmware polls for completion.

- the core processor 302is interrupted by the coprocessor or hardware accelerators when an exceptional occurrence is detected, such as an error in the processing task.

- the coprocessor or hardware acceleratorsinterrupt the core processor when they complete their assigned tasks.

- Each hardware module 306 , 308 , 309 , 310 , 312 , 313 , 315is independently controllable by the core processor 302 .

- the core processor 302drives a hardware module by issuing a certain start command after checking the module's status. In one embodiment, the core processor 302 issues the start command by setting up a register in the hardware module.

- FIG. 7is a flowchart representing a macroblock decoding loop according to an illustrative embodiment of the present invention.

- FIG. 7depicts the decoding of one video picture, starting at the macro block level.

- the loop of macroblock level decoding pipeline controlis fully synchronous.

- the core processor 302retrieves a macroblock to be decoded from system memory 110 .

- the core processorstarts all the hardware modules for which input data is available. The criteria for starting all modules depends on an exemplary pipeline control mechanism illustrated in FIG. 6 .

- the core processor 302decodes the macroblock header with the help of the PVLD 306 .

- the core processor 302commands the PVLD 306 for block coefficient decoding.

- the core processor 302calculates motion vectors and memory addresses, such as the pixel filter reference fetch address, controls buffer rotation and performs other housekeeping tasks.

- the core processor 302checks to see whether the acceleration modules have completed their respective tasks.

- decision box 760if all of the acceleration modules have completed their respective tasks, control passes to decision box 770 . If, at decision box 760 , one or more of the acceleration modules have not finished their tasks, the core processor 302 continues polling the acceleration modules until they have all completed their tasks, as shown by step 750 and decision box 760 .

- the processis complete. If the picture is not decoded, the core processor 302 retrieves the next macroblock and the process continues as shown by step 700 . In an illustrative embodiment of the present invention, when the current picture has been decoded, the incoming macroblock data of the next picture in the video sequence is decoded according to the process of FIG. 7 .

- the core processor 302interprets the bits decoded (with the help of the PVLD 306 ) for the appropriate headers and sets up and coordinates the actions of the hardware modules. More specifically, all header information, from the sequence level down to the macroblock level, is requested by the core processor 302 .

- the core processor 302also controls and coordinates the actions of each hardware module.

- the core processorconfigures the hardware modules to operate in accordance with the encoding/decoding format of the data stream being decoded by providing operating parameters to the hardware modules.

- the parametersinclude but are not limited to (using MPEG2 as an example) the cbp (coded block pattern) used by the PVLD 306 to control the decoding of the transform block coefficients, the quantization scale used by the IQ module 308 to perform inverse quantization, motion vectors used by the pixel filter 309 and motion compensation module 310 to reconstruct the macroblocks, and the working buffer address(es) in decoder memory 316 .

- Each hardware module 306 , 308 , 309 , 310 , 312 , 313 , 315performs the specific processing as instructed by the core processor 302 and sets up its status properly in a status register as the task is being executed and when it is done.

- Each of the moduleshas or shares a status register that is polled by the core processor to determine the module's status.

- each moduleissues an interrupt signal to the core processor so that in addition to polling the status registers, the core processor can be informed asynchronously of exceptional events like errors in the bitstream.

- Each hardware moduleis assigned a set of macroblock buffers in decoder memory 316 for processing purposes.

- each hardware modulesignals the busy/available status of the working buffer(s) associated with it so that the core processor 302 can properly coordinate the processing pipeline.

- the hardware accelerator modules 306 , 308 , 309 , 319 , 312 , 313 , 314 , 315generally do not communicate with each other directly.

- the acceleratorswork on assigned areas of decoder memory 316 and produce results that are written back to decoder memory 316 , in some cases to the same area of decoder memory 316 as the input to the accelerator, or results are written back to main memory.

- the acceleratorswhen the incoming bitstream is of a format that includes a relatively large amount of data, or of a relatively complex encoding/decoding format, the accelerators in some cases may bypass the decoder memory 316 and pass data between themselves directly.

- modules 310 , 312 and 313 , 315are implemented in a programmable SIMD/RISC filter engine module ( 311 and 314 respectively) that allows execution of a wide range of decoding algorithms, even ones that have not yet been specified in by any standards body.

- Software representing all other video decoding tasksis compiled to run directly on the core processor.

- FIG. 8is a flowchart representing a method of decoding a digital video data stream or set of streams containing more than one video data format, according to an illustrative embodiment of the present invention.

- step 800video data of a first encoding/decoding format is received.

- At step 810at least one external decoding function, such as variable-length decoding or inverse quantization: is configured based on the first encoding/decoding format.

- video data of the first encoding/decoding formatis decoded using the at least one external decoding function.

- a full picture, or a least a full rowis processed before changing formats and before changing streams.

- video data of a second encoding/decoding formatis received.

- at least one external decoding functionis configured based on the second encoding/decoding format.

- video data of the second encoding/decoding formatis decoded using the at least one external decoding function.

- the at least one decoding functionis performed by one or more of hardware accelerators 306 , 308 , 309 , 310 , 312 , 313 , 314 and 315 .

- the hardware acceleratorsare programmed or configured by the core processor 302 to operate according to the appropriate encoding/decoding format. As is described above with respect to the individual hardware accelerators of FIGS. 3 and 4 , in one illustrative embodiment the programming for different decoding formats is done through register read/write.

- the core processorprograms registers in each module to modify the operational behavior of the module.

- some or all of the hardware acceleratorscomprise programmable processors which are configured to operate according to different encoding/decoding formats by changing the software executed by those processors, in addition to programming registers as appropriate to the design.

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Software Systems (AREA)

- Theoretical Computer Science (AREA)

- Discrete Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- Compression Or Coding Systems Of Tv Signals (AREA)

Abstract

Description

This application is a reissue of U.S. patent application Ser. No. 13/608,221 filed Sep. 10, 2012 (now U.S. Pat. No. 9,417,883) entitled, “Video Decoding System Supporting Multiple Standards,” which is a divisional application of and claims priority to U.S. patent application Ser. No. 10/114,798, filed on Apr. 1, 2002, having the title “VIDEO DECODING SYSTEM SUPPORTING MULTIPLE STANDARDS,” and issued as U.S. Pat. No. 8,284,844 on Oct. 9, 2012, which is incorporated by reference herein as if expressly set forth in its entirety.

The present invention relates generally to video decoding systems, and more particularly to a video decoding system supporting multiple standards.

Digital video decoders decode compressed digital data that represent video images in order to reconstruct the video images. A relatively wide variety of encoding /decoding algorithms and encoding/decoding standards presently exist, and many additional algorithms and standards are sure to be developed in the future. The various algorithms and standards produce compressed video bit streams of a variety of formats. Some existing public format standards include MPEG -1, MPEG-2 (SD/HD), MPEG-4, H.263, H.263+ and H.26LIJVT. Also, private standards have been developed by Microsoft Corporation (Windows Media), RealNetworks, Inc., Apple Computer, Inc. (QuickTime), and others. It would be desirable to have a multi-format decoding system that can accommodate a variety of encoded bit stream formats, including existing and future standards, and to do so in a cost-effective manner.

A highly optimized hardware architecture can be created to address a specific video decoding standard, but this kind of solution is typically limited to a single format. On the other hand, a fully software based solution is often flexible enough to handle any encoding format, but such solutions tend not to have adequate performance for real time operation with complex algorithms, and also the cost tends to be too high for high volume consumer products. Currently a common software based solution is to use a general-purpose processor running in a personal computer, or to use a similar processor in a slightly different system. Sometimes the general-purpose processor includes special instructions to accelerate digital signal processor (DSP) operations such as multiply-accumulate (MAC); these extensions are intimately tied to the particular internal processor architecture. For example, in one existing implementation, an Intel Pentium processor includes an MMX instruction set extension. Such a solution is limited in performance, despite very high clock rates, and does not lend itself to creating mass market, commercially attractive systems.

Others in the industry have addressed the problem of accommodating different encoding/decocting algorithms by designing special purpose DSPs in a variety of architectures. Some companies have implemented Very Long Instruction Word (VLIW) architectures more suitable to video processing and able to process several instructions in parallel. In. these cases, the processors are difficult to program when compared to a general-purpose processor. Despite the fact that the DSP and VLIW architectures are intended for high performance, they still tend not to have enough performance for the present purpose of real time decoding of complex video algorithms. In special cases, where the processors are dedicated for decoding compressed video, special processing accelerators are tightly coupled to the instruction pipeline and are part of the core of the main processor.

Yet others in the industry have addressed the problem of accommodating different encoding/decoding algorithms by simply providing, multiple instances of hardware, each dedicated to a single algorithm. This solution is inefficient and is not cost-effective.

Further limitations and disadvantages of conventional and traditional approaches will become apparent to one of skill in the art through comparison of such systems with the present invention as set forth in the remainder of the present application with reference to the drawings.

One aspect of the present invention is directed to a digital media decoding system having a processor and a hardware accelerator. The processor is adapted to control a decoding process. The hardware accelerator is coupled to the processor and performs a decoding function on a digital media data stream. The accelerator is configurable to perform the decoding function according to a plurality of decoding methods.