US7902679B2 - Structure and manufacturing method of a chip scale package with low fabrication cost, fine pitch and high reliability solder bump - Google Patents

Structure and manufacturing method of a chip scale package with low fabrication cost, fine pitch and high reliability solder bumpDownload PDFInfo

- Publication number

- US7902679B2 US7902679B2US11/981,138US98113807AUS7902679B2US 7902679 B2US7902679 B2US 7902679B2US 98113807 AUS98113807 AUS 98113807AUS 7902679 B2US7902679 B2US 7902679B2

- Authority

- US

- United States

- Prior art keywords

- layer

- solder

- substrate

- metal

- contact point

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49811—Additional leads joined to the metallisation on the insulating substrate, e.g. pins, bumps, wires, flat leads

- H01L23/49816—Spherical bumps on the substrate for external connection, e.g. ball grid arrays [BGA]

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/02—Bonding areas ; Manufacturing methods related thereto

- H01L24/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L24/06—Structure, shape, material or disposition of the bonding areas prior to the connecting process of a plurality of bonding areas

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L24/17—Structure, shape, material or disposition of the bump connectors after the connecting process of a plurality of bump connectors

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/0401—Bonding areas specifically adapted for bump connectors, e.g. under bump metallisation [UBM]

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/04042—Bonding areas specifically adapted for wire connectors, e.g. wirebond pads

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0556—Disposition

- H01L2224/05571—Disposition the external layer being disposed in a recess of the surface

- H01L2224/05572—Disposition the external layer being disposed in a recess of the surface the external layer extending out of an opening

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/06—Structure, shape, material or disposition of the bonding areas prior to the connecting process of a plurality of bonding areas

- H01L2224/061—Disposition

- H01L2224/0612—Layout

- H01L2224/0613—Square or rectangular array

- H01L2224/06134—Square or rectangular array covering only portions of the surface to be connected

- H01L2224/06136—Covering only the central area of the surface to be connected, i.e. central arrangements

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13005—Structure

- H01L2224/13007—Bump connector smaller than the underlying bonding area, e.g. than the under bump metallisation [UBM]

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/1301—Shape

- H01L2224/13016—Shape in side view

- H01L2224/13017—Shape in side view being non uniform along the bump connector

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/1302—Disposition

- H01L2224/13023—Disposition the whole bump connector protruding from the surface

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13075—Plural core members

- H01L2224/1308—Plural core members being stacked

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13075—Plural core members

- H01L2224/1308—Plural core members being stacked

- H01L2224/13083—Three-layer arrangements

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

- H01L2224/131—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

- H01L2224/131—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/13138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/13147—Copper [Cu] as principal constituent

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

- H01L2224/131—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/13138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/13155—Nickel [Ni] as principal constituent

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L24/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00013—Fully indexed content

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01005—Boron [B]

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01013—Aluminum [Al]

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01014—Silicon [Si]

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01015—Phosphorus [P]

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01018—Argon [Ar]

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01022—Titanium [Ti]

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01042—Molybdenum [Mo]

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/0105—Tin [Sn]

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01073—Tantalum [Ta]

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01074—Tungsten [W]

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01075—Rhenium [Re]

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01078—Platinum [Pt]

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01082—Lead [Pb]

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/013—Alloys

- H01L2924/014—Solder alloys

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/049—Nitrides composed of metals from groups of the periodic table

- H01L2924/0494—4th Group

- H01L2924/04941—TiN

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1204—Optical Diode

- H01L2924/12044—OLED

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/30105—Capacitance

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/35—Mechanical effects

- H01L2924/351—Thermal stress

Definitions

- the inventionrelates to the fabrication of integrated circuit devices, and more particularly, to a method and package for packaging semiconductor devices.

- BGABall Grid Array

- CGAColumn Grid Array

- BGABall Grid Array

- BGAis an array of solder balls placed on a chip carrier. The balls contact a printed circuit board in an array configuration where, after reheat, the balls connect the chip to the printed circuit board.

- BGA'sare known with 40, 50 and 60 mil spacings.

- Flip-chip technologyfabricates bumps (typically Pb/Sn solders) on aluminum pads on a semiconductor device.

- the bumpsare interconnected directly to the package media, which are usually ceramic or plastic based.

- the flip-chipis bonded face down to the package medium through the shortest paths.

- Chip-On-Board (COB) techniquesare used to attach semiconductor die to a printed circuit board; these techniques include the technical disciplines of flip chip attachment, wirebonding, and tape automated bonding (TAB).

- Flip chip attachmentconsists of attaching a flip chip to a printed circuit board or to another substrate.

- a flip chipis a semiconductor chip that has a pattern or arrays of terminals that are spaced around an active surface area of the flip chip, allowing for face down mounting of the flip chip to a substrate.

- the flip chip active surfacehas one of the following electrical connectors: BGA (wherein an array of minute solder balls is created on the surface of the flip chip that attaches to the substrate); Slightly Larger than Integrated Circuit Carrier (SLICC) (which is similar to the BGA but has a smaller solder ball pitch and diameter than the BGA); a Pin Grid Array (PGA) (wherein an array of small pins extends substantially perpendicularly from the attachment surface of a flip chip, such that the pins conform to a specific arrangement on a printed circuit board or other substrate for attachment thereto).

- BGAwherein an array of minute solder balls is created on the surface of the flip chip that attaches to the substrate

- SLICCSlightly Larger than Integrated Circuit Carrier

- PGAPin Grid Array

- the solder or other conductive ball arrangement on the flip chipmust be a mirror image of the connecting bond pads on the printed circuit board so that precise connection can be made.

- Bond padsare generally used to wire device elements and to provide exposed contact regions of the die. These contact regions are suitable for wiring the die to components that are external to the die.

- An exampleis where a bond wire is attached to a bond pad of a semiconductor die at one end and to a portion of a Printed Circuit Board at the other end of the wire.

- the artis constantly striving to achieve improvements in the creation of bond pads that simplify the manufacturing process while enhancing bond pad reliability.

- bonds padsMaterials that are typically used for bond pads include metallic materials, such as tungsten and aluminum, while heavily doped polysilicon can also be used for contacting material.

- the bond padis formed on the top surface of the semiconductor device whereby the electrically conducting material is frequently embedded in an insulating layer of dielectric.

- polysiliconcan be doped with an n-type dopant for contacting N-regions while it can be doped with p-type dopant for contacting P-regions. This approach of doping avoids inter-diffusion of the dopants and dopant migration. It is clear that low contact resistance for the bond pad area is required while concerns of avoidance of moisture or chemical solvent absorption, thin film adhesion characteristics, delamination and cracking play an important part in the creation of bond pads.

- the conventional processing sequence that is used to create an aluminum bond padstarts with a semiconductor surface, typically the surface of a silicon single crystalline substrate.

- a layer of Intra Metal Dielectric (IMD)is deposited over the surface, a layer of metal, typically aluminum, is deposited over the surface of the layer of IMD.

- the layer of metalis patterned and etched typically using a layer of photoresist and conventional methods of photolithography and etching.

- a layer of passivationis deposited over the layer of IMD.

- An opening that aligns with the bond padis created in the layer of passivation, again using methods of photolithography and etching.

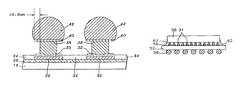

- FIGS. 1 through 4show an example of one of the methods that is used to create an interconnect bump.

- a semiconductor surface 10has been provided with a metal contact pad 14 ; the semiconductor surface 10 is protected with a layer 12 of passivation.

- An opening 19has been created in the layer 12 of passivation; the surface of the metal contact pad 14 is exposed through this opening 19 .

- a dielectric layer 16is deposited over the surface of the layer 12 of passivation.

- the layer 16 of dielectricis patterned and etched, creating an opening 21 in the layer 16 of dielectric that aligns with the metal pad 14 and that partially exposes the surface of the metal pad 14 .

- a layer 18 of metalis created over the layer 16 of dielectric; layer 18 of metal is in contact with the surface of the metal pad 14 inside opening 21 .

- the region of layer 18 of metal that is above the metal pad 14will, at a later point in the processing, form a pedestal over which the interconnect bump will be formed.

- This pedestalcan be further extended in a vertical direction by the deposition and patterning of one or more additional layers that may contain a photoresist or a dielectric material; these additional layers are not shown in FIG. 2 .

- These layersessentially have the shape of layer 16 and are removed during one of the final processing steps that is applied for the formation of the interconnect bump.

- a layer of photoresist(not shown) is deposited, patterned and etched, creating an opening that aligns with the contact pad 14 .

- a layer 20 of metalsuch as copper or nickel, shown in FIG. 3 , that forms an integral part of the pedestal of the to be created interconnect bump, is next electroplated in the opening created in the layer of photoresist and on the surface of the layer 18 of metal, whereby the layer 18 serves as the lower electrode during the plating process.

- Layer 20 in prior art applicationshas a thickness of between about 1 and 10 ⁇ m with a typical value of about 5 ⁇ m.

- the final layer 22 of solderis electroplated on the surface of layer 20 .

- the patterned layer of photoresistis then removed.

- the layer 18 of metalis next etched, as in FIG. 4 , leaving in place only the pedestal for the interconnect bump. During this etch process the deposited layers 20 and 22 serve as a mask. If, as indicated above, additional layers of dielectric or photoresist have been deposited for the further shaping of pedestal 18 in FIG. 2 , these layers are also removed at this time.

- solder paste or flux(not shown) is now applied to the layer 22 of solder, and the solder 22 is melted in a reflow surface typically under a nitrogen atmosphere, creating the spherically shaped interconnect bump 22 that is shown in FIG. 4 .

- BLM layersare successive and overlying layers of chrome, copper and gold, whereby the chrome is used to enhance adhesion with an underlying aluminum contact pad, the copper layer serves to prevent diffusion of solder materials into underlying layers, while the gold layer serves to prevent oxidation of the surface of the copper layer.

- the BLM layeris layer 18 of FIGS. 2 through 4 .

- Increased device densitybrings with it increased closeness of components and elements that are part of the created semiconductor devices. This increased closeness is expressed as a reduction in the spacing or “pitch” between elements of a semiconductor device.

- State-of-the-art technologyuses solder bumps having a pitch of about 200 ⁇ m, which imposes a limitation on further increasing device density.

- the limitation in further reducing the pitch of solder bumpsis imposed by concerns of reliability, which impose a relatively large ball size for the solder bump. This relatively large solder ball restricts further reducing the solder ball pitch.

- solder bumpsare used as interconnections between I/O bond pads and a substrate or printed circuit board.

- a large solder ballbrings with it high standoff since a solder ball with high standoff has better thermal performance (CTE mismatching is easier to avoid resulting in reduced thermal stress on the solder balls).

- Large solder ballsare therefore required in order to maintain interconnect reliability.

- Low-alpha solderis applied to avoid soft error (electrical or functional errors) from occurring, thereby eliminating the potential for inadvertent memory discharge and incorrect setting of the voltage (1 or 0).

- the inventionaddresses concerns of creating a BGA type package whereby the pitch of the solder ball or solder bump of the device interconnect is in the range of 200 ⁇ m or less.

- the conventional, state-of-the-art solder processruns into limitations for such a fine interconnect pad pitch, the invention provides a method and a package for attaching devices having very small ball pitch to an interconnect medium such as a Printed Circuit Board.

- a principal objective of the inventionis to provide a method of creating a fine-pitch solder bump.

- Another objective of the inventionis to provide a method of creating smaller solder bumps, further allowing for the creation of fine-pitched solder bumps.

- Another objective of the inventionis to provide a cost-effective method to create a fine-pitch solder bump of high reliability, due to the increased height of the solder bump. This objective is based on the belief that solder bump reliability improves proportionally to the square of the distance between the solder ball and the underlying substrate.

- Another objective of the inventionis to provide a cost-effective way of creating a solder bump. This cost-effective way is realized by using standard solder material and therewith eliminating the need for expensive “low- ⁇ solder”.

- Another objective of the inventionis to provide a cost-effective method of creating a fine-pitch solder bump by reducing the alpha-effect on memory products.

- Another objective of the inventionis to provide a method of creating solder bumps which allows an easy method of cleaning flux after the process of creating the solder bump has been completed.

- Another objective of the inventionis to provide a method of creating solder bumps which allows easy application of underfill.

- Another objective of the inventionis to provide a method for applying fine pitch solder bumps directly to the I/O pads of a semiconductor device, without a redistribution interface, and bonding the semiconductor device directly to a Ball Grid Array substrate using the flip-chip bonding approach.

- Another objective of the inventionis to provide a method for shortening the interconnection between a semiconductor device and the substrate on which the device is mounted, thus improving the electrical performance of the device.

- Yet another objective of the inventionis to eliminate conventional methods of re-distribution of device I/O interconnect, thereby making packaging of the device more cost-effective and eliminating performance degradation.

- a still further objective of the inventionis to improve chip accessibility during testing of the device, thus eliminating the need for special test fixtures.

- a still further objective of the inventionis to improve performance and device reliability of BGA packages that are used for the mounting of semiconductor devices having small-pitch I/O interconnect bumps.

- a still further objective of the inventionis to perform Chip Scale Packaging (CSP) without re-distribution, including for various pad designs such as peripheral or central pad designs.

- CSPChip Scale Packaging

- a still further objective of the inventionis to provide a method of mounting small-pitch semiconductor devices in such a manner that flux removal and the dispensing of device encapsulants is improved.

- a new method and packageis provided for the mounting of semiconductor devices that have been provided with small-pitch Input/Output interconnect bumps.

- Fine pitch solder bumpsconsisting of pillar metal and a solder bump, are applied directly to the I/O pads of the semiconductor device, the device is then flip-chip bonded to a substrate. Dummy bumps may be provided for cases where the I/O pads of the device are arranged such that additional mechanical support for the device is required.

- FIGS. 1 through 4show a prior art method of creating a solder bump overlying a point of electrical contact, as follows:

- FIG. 1shows a cross section of a semiconductor surface on the surface of which a contact pad has been created; the semiconductor surface is covered with a patterned layer of passivation.

- FIG. 2shows the cross section of FIG. 1 after a patterned layer of dielectric and a layer of metal have been created on the semiconductor surface.

- FIG. 3shows a cross section of FIG. 2 after a layer of bump metal and solder compound have been selectively deposited.

- FIG. 4show a cross section after excessive layers have been removed from the semiconductor surface and, after the solder has been reflowed, forming the interconnect bump.

- FIG. 5shows a cross section of the BGA package of the invention; the semiconductor device is encapsulated in a molding compound.

- FIG. 6shows a cross section of the BGA package of the invention

- FIGS. 7 through 16address the invention, as follows:

- FIG. 7shows a cross section of a semiconductor surface, a layer of dielectric has been deposited, metal pads have been created, a layer of passivation has been deposited and patterned, and a layer of barrier material has been deposited.

- FIG. 8shows a cross section after a patterned layer of photoresist has been created over the structure of FIG. 7 .

- FIG. 9shows a cross section after pillar metal has been created aligned with the metal pads and under bump metal has been deposited over the surface of the pillar metal.

- FIG. 10shows a cross section after solder metal has been plated over the under bump metal.

- FIG. 11shows a cross section after the patterned layer of photoresist has been removed from the surface.

- FIG. 12shows a cross section after the diameter of the pillar metal has been reduced.

- FIG. 13shows a cross section after the barrier layer has been etched using isotropic etching, creating a first profile.

- FIG. 14shows a cross section after the barrier layer has been etched using anisotropic etching or RIE, creating a second profile.

- FIG. 15shows a cross-section of a completed first solder bump of the present invention.

- FIG. 16shows a cross-section of a completed second solder bump of the present invention.

- FIG. 17shows a cross section of the BGA package of the invention; the semiconductor device is encapsulated in a molding compound.

- FIG. 18shows a cross section of the BGA package of the invention. Underfill is provided to the semiconductor device.

- FIG. 19shows a top view of an array type I/O pad configuration of a semiconductor device.

- FIG. 20shows a top view of a peripheral type I/O pad configuration of a semiconductor device.

- FIG. 21shows a top view of a center type I/O pad configuration of a semiconductor device.

- FIG. 22shows a top view of a center type I/O pad configuration of a semiconductor device; dummy solder bumps have been provided in support of the semiconductor device.

- FIG. 23shows a top view of the substrate with exposed I/O contact pads; this exposure is accomplished by not depositing the solder mask in close proximity to the contact pads of the semiconductor device.

- FIG. 24shows a cross section of the substrate of FIG. 23 .

- FIG. 25shows a top view of a prior art substrate with exposed I/O contact pads; the solder mask is in close proximity to the contact pads of the semiconductor device.

- FIG. 26shows a cross section of the substrate of FIG. 25 .

- FIGS. 27 a through 27 fshow examples of applications of the invention.

- FIGS. 28 a and 28 bdemonstrate how the invention leads to the ability to reduce the pitch between I/O pads.

- the above stated objective of improving chip accessibility during testing of the device, thus eliminating the need for special test fixtures,can further be highlighted as follows.

- the disclosed method of the inventionusing Chip Scale Packaging (CSP), can control the cost of testing CSP devices by keeping the same body size of the chip and by using the same size substrate.

- the chipmay have different body sizes, which imposes the requirement of different size test fixtures.

- CSP packagescan control the cost of testing CSP devices by keeping the same body size of the chip and by using the same size substrate.

- the chipmay have different body sizes, which imposes the requirement of different size test fixtures.

- additional and varying device sizesare expected to be used. This would result in ever increasing costs for back-end testing of the devices in a production environment.

- the inventionprovides a method where these additional back-end testing costs can be avoided.

- FIG. 5there is shown a cross section of a typical flip chip package with the semiconductor device being encapsulated in a molding compound.

- the Integrated Circuit (IC) device 10enters the process as a separate unit with the contact points (balls 16 ) attached to the bottom of the chip 10 .

- the IC 10is placed on the surface of a BGA substrate 12 , an (optional) interconnect substrate 14 has been provided for additional routing of the electrical network to which device 10 is attached.

- the balls 18 that are connected to the lower surface of the substrate 12make contact with surrounding circuitry (not shown).

- the paths of electrical interconnect of device 10 as shown in cross section in FIG. 5are as follows: contact bumps (points of I/O interconnect, not shown in FIG.

- BGA substrate 12may further have been provided with one or more layers of interconnect metal, all of the interfaces (the interconnect substrate 12 and the optional redistribution lines provided in BGA substrate 12 ) result in interconnecting balls 16 with balls 18 .

- Balls 18are the contact points that connect the package that is shown in cross section in FIG. 5 to surrounding circuitry.

- FIG. 5shows contact balls 16 for the establishment of contacts between device 10 and the underlying substrate 12

- some prior art applicationsstill used wire bond connections (not shown in FIG. 5 ), this in order to achieve optimum electrical performance of the device package.

- layer 19which may be provided over the surface of semiconductor device 10 facing the substrate 12 .

- This re-distribution layerprovides interconnect lines over the surface of device 10 and is required in prior art applications if solder bumps are required on current pad layout for wire bonding purposes.

- the main purpose of the redistribution layeris to enlarge the pitch of solder bump interconnects if the bond pads are originally designed for wire bonding applications. It will be clear from later explanations that the invention removes the need for the redistribution layer.

- FIG. 6shows a cross section of a conventional BGA package whereby the semiconductor device 10 is provided with underfill 22 , no molding compound ( 20 , FIG. 5 ) has been provided in the package that is shown in cross section in FIG. 6 .

- All the other statements that relate to the electrical interconnection of the device 10 of FIG. 6are identical to the statements that have been made in the description provided for the package of FIG. 5 .

- the sides of the underfill 22are sloping such that the physical contact between the underfill 22 and the substrate 12 is extended beyond the dimensions of the bottom surface of the chip 10 . This is a normal phenomenon with liquid underfill, which enhances the mechanical strength between the substrate 12 and the IC chip 10 .

- FIG. 15there is shown a cross section of a first solder bump that has been created in accordance with the above referenced related application.

- the elements that are shown in FIG. 15 that form part of the solder bump of the related applicationare the following:

- the cross section that is shown in FIG. 16is similar to the cross section of FIG. 15 with the exception of layer 35 , which is an anisotropically etched layer of barrier metal (etched after the solder bump 42 has been created) which, due to the nature of the anisotropic etch, protrudes from the pillar metal 38 as shown in the cross section of FIG. 16 .

- layer 35is an anisotropically etched layer of barrier metal (etched after the solder bump 42 has been created) which, due to the nature of the anisotropic etch, protrudes from the pillar metal 38 as shown in the cross section of FIG. 16 .

- solder bumpthat allows easy cleaning of flux after the process of flip chip assembly and before the process of underfill and encapsulation

- FIGS. 7 through 16provide details of the process of the invention which leads to the solder bumps that have been shown in cross section in FIGS. 5 and 6 .

- FIG. 7shows a cross section of substrate 10 on the surface, wherein he following elements are highlighted:

- dielectric material for layer 30can be used any of the typically applied dielectrics such as silicon dioxide (doped or undoped), silicon oxynitride, parylene or polyimide, spin-on-glass, plasma oxide or LPCVD oxide.

- the material that is used for the deposition of layer 30 of dielectric of the inventionis not limited to the materials indicated above but can include any of the commonly used dielectrics in the art.

- metal contact pads 32can use conventional methods of metal rf sputtering at a temperature between about 100 and 400 degrees C. and a pressure between about 1 and 100 mTorr using as source, for instance, aluminum-copper material (for the creation of aluminum contact pads) at a flow rate of between about 10 and 400 sccm to a thickness between about 4000 and 11000 Angstroms. After a layer of metal has been deposited, the layer must be patterned and etched to create the aluminum contact pads 32 . This patterning and etching uses conventional methods of photolithography and patterning and etching.

- a deposited layer of AICucan be etched using Cl 2 /Ar as an etchant at a temperature between 50 and 200 degrees C., an etchant flow rate of about 20 sccm for the Cl 2 and 1000 sccm for the Ar, a pressure between about 50 mTorr and 10 Torr, a time of the etch between 30 and 200 seconds.

- insulating layerssuch as silicon oxide and oxygen-containing polymers, are deposited using Chemical Vapor Deposition (CVD) technique over the surface of various layers of conducting lines in a semiconductor device or substrate to separate the conductive interconnect lines from each other.

- the insulating layerscan also be deposited over patterned layers of interconnecting lines; electrical contact between successive layers of interconnecting lines is established with metal vias created in the insulating layers.

- Electrical contact to the chipis typically established by means of bonding pads or contact pads that form electrical interfaces with patterned levels of interconnecting metal lines. Signal lines and power/ground lines can be connected to the bonding pads or contact pads.

- the bonding pads or contact padsare passivated and electrically insulated by the deposition of a passivation layer over the surface of the bonding pads.

- a passivation layercan contain silicon oxide/silicon nitride (SiO 2 /Si 3 N 4 ) deposited by CVD.

- the passivation layeris patterned and etched to create openings in the passivation layer for the bonding pads or contact pads after which a second and relatively thick passivation layer can be deposited for further insulation and protection of the surface of the chips from moisture and other contaminants and from mechanical damage during assembling of the chips.

- the passivation layercan contain silicon oxide/silicon nitride (SiO 2 /Si 3 N 4 ) deposited by CVD, or a passivation layer can be a layer of photosensitive polyimide or can comprise titanium nitride.

- a passivation layercan be a layer of photosensitive polyimide or can comprise titanium nitride.

- Another material often used for a passivation layeris phosphorous doped silicon dioxide that is typically deposited over a final layer of aluminum interconnect using a Low Temperature CVD process.

- photosensitive polyimidehas frequently been used for the creation of passivation layers. Conventional polyimides have a number of attractive characteristics for their application in a semiconductor device structure which have been highlighted above.

- Photosensitive polyimideshave these same characteristics but can, in addition, be patterned like a photoresist mask and can, after patterning and etching, remain on the surface on which it has been deposited to serve as a passivation layer.

- a precursor layeris first deposited by, for example, conventional photoresist spin coating.

- the precursoris, after a low temperature pre-bake, exposed using, for example, a step and repeat projection aligner and Ultra Violet (UV) light as a light source.

- UVUltra Violet

- the portions of the precursor that have been exposed in this mannerare cross-linked, thereby leaving unexposed regions (that are not cross-linked) over the bonding pads.

- the unexposed polyimide precursor layeris dissolved, thereby providing openings over the bonding pads.

- a final step of thermal curingleaves a permanent high quality passivation layer of polyimide over the substrate.

- the preferred material of the invention for the deposition of layer 34 of passivationis Plasma Enhanced silicon nitride (PE Si 3 N 4 ), deposited using PECVD technology at a temperature between about 350 and 450 degrees C. with a pressure of between about 2.0 and 2.8 Torr for the duration between about 8 and 12 seconds.

- Layer 32 of PE Si 3 N 4can be deposited to a thickness between about 200 and 800 Angstroms.

- Layer 34 of PE Si 3 N 4is next patterned and etched to create openings in the layer 34 that overlay and align with the underlying contact pads 32 .

- the etching of layer 34 of passivationcan use Ar/CF 4 as an etchant at a temperature of between about 120 and 160 degrees C. and a pressure of between about 0.30 and 0.40 Torr for a time of between about 33 and 39 seconds using a dry etch process.

- the etching of layer 34 of passivationcan also use He/NF 3 as an etchant at a temperature of between about 80 and 100 degrees C. and a pressure of between about 1.20 and 1.30 Torr for a time of between about 20 and 30 seconds using a dry etch process.

- Barrier layerssuch as layer 36 are typically used to prevent diffusion of an interconnect metal into surrounding layers of dielectric and silicon.

- Some of the considerations that apply in selecting a material for the barrier layerbecome apparent by using copper for interconnect metal as an example. Although copper has a relatively low cost and low resistivity, it has a relatively large diffusion coefficient into silicon dioxide and silicon and is therefore not typically used as an interconnect metal. Copper from an interconnect may diffuse into the silicon dioxide layer causing the dielectric to be conductive and decreasing the dielectric strength of the silicon dioxide layer. Copper interconnects should be encapsulated by at least one diffusion barrier to prevent diffusion into the silicon dioxide layer.

- Silicon nitrideis a diffusion barrier to copper, but the prior art teaches that the interconnects should not lie on a silicon nitride layer because it has a high dielectric constant compared with silicon dioxide. The high dielectric constant causes a desired increase in capacitance between the interconnect and the substrate.

- a typical diffusion barrier layermay contain silicon nitride, phosphosilicate glass (PSG), silicon oxynitride, aluminum, aluminum oxide (Al x O y ), tantalum, Ti/TiN or Ti/W, nionbium, or molybdenum and is more preferably formed from TiN.

- the barrier layercan also be used to improve the adhesion of the subsequent overlying tungsten layer.

- a barrier layeris preferably between about 500 and 2000 Angstroms thick and more preferably about 300 Angstroms thick and can be deposited using rf sputtering.

- a seed layer(not shown in FIG. 7 ) can be blanket deposited over the surface of the wafer.

- any of the conventional metallic seed materialscan be used.

- the metallic seed layercan be deposited using a sputter chamber or an Ion Metal Plasma (IMP) chamber at a temperature of between about 0 and 300 degrees C. and a pressure of between about 1 and 100 mTorr, using (for instance) copper or a copper alloy as the source (as highlighted above) at a flow rate of between about 10 and 400 sccm and using argon as an ambient gas.

- IMPIon Metal Plasma

- FIG. 8shows a cross section of the substrate after a layer 37 of photoresist has been deposited over the surface of the barrier layer 36 .

- the layer 37 of photoresisthas been patterned and etched, creating openings 31 in the layer 37 of photoresist. Openings 31 partially expose the surface of the barrier layer 36 .

- Layer 37 of photoresistis typically applied to a thickness of between about 100 and 200 ⁇ m but more preferably to a thickness of about 150 ⁇ m.

- Layer 37 of photoresistis typically applied to a thickness of between about 100 and 200 ⁇ m but more preferably to a thickness of about 150 ⁇ m.

- the methods used for the deposition and development of the layer 37 of photoresistuses conventional methods of photolithography.

- Photolithographyis a common approach wherein patterned layers are formed by spinning on a layer of photoresist, projecting light through a photomask with the desired pattern onto the photoresist to expose the photoresist to the pattern, developing the photoresist, washing off the undeveloped photoresist, and plasma etching to clean out the areas where the photoresist has been washed away.

- the exposed resistmay be rendered soluble (positive working) and washed away, or insoluble (negative working) and form the pattern.

- the deposited layer 37 of photoresistcan, prior to patterning and etching, be cured or pre-baked further hardening the surface of the layer 37 of photoresist.

- Layer 37 of photoresistcan be etched by applying O 2 plasma and then wet stripping by using H 2 SO 4 , H 2 O 2 and NH 4 OH solution.

- Sulfuric acid (H 2 SO 4 ) and mixtures of H 2 SO 4 with other oxidizing agents such as hydrogen peroxide (H 2 O 2 )are widely used in stripping photoresist after the photoresist has been stripped by other means.

- Wafers to be strippedcan be immersed in the mixture at a temperature between about 100 degrees C. and about 150 degrees C. for 5 to 10 minutes and then subjected to a thorough cleaning with deionized water and dried by dry nitrogen.

- Inorganic resist strippers, such as the sulfuric acid mixturesare very effective in the residual free removal of highly postbaked resist. They are more effective than organic strippers and the longer the immersion time, the cleaner and more residue free wafer surface can be obtained.

- the photoresist layer 37can also be partially removed using plasma oxygen ashing and careful wet clean.

- the oxygen plasma ashingis heating the photoresist in a highly oxidized environment, such as an oxygen plasma, thereby converting the photoresist to an easily removed ash.

- the oxygen plasma ashingcan be followed by a native oxide dip for 90 seconds in a 200:1 diluted solution of hydrofluoric acid.

- FIG. 9shows a cross section of the substrate 10 after a layer 38 of pillar metal has been deposited (electroplated) over the surface of the layer 36 of barrier material and bounded by openings 31 that have been created in the layer 37 of photoresist.

- layers 40 of under bump metalhave been deposited using deposition methods such as electroplating.

- Layer 36preferably comprises titanium or copper and is preferably deposited to a thickness of between about 500 and 2000 Angstroms and more preferably to a thickness of about 1000 Angstroms.

- Layer 38preferably comprises copper and is preferred to be applied to a thickness of between about 10 and 100 ⁇ m but more preferably to a thickness of about 50 ⁇ m.

- Layer 40preferably comprises nickel and is preferred to be applied to a thickness of between about 1 and 10 ⁇ m but more preferably to a thickness of about 4 ⁇ m.

- FIG. 10shows a cross section where the process of the invention has further electroplated layers 42 of solder metal over the surface of layers 40 of under bump metal (UBM) and bounded by the openings 31 that have been created in the layer 37 of photoresist.

- UBMunder bump metal

- Layer 40 of UBMtypically of nickel and of a thickness between about 1 and 10 ⁇ m, is electroplated over the layer 38 of pillar metal.

- the layer 42 of bump metal(typically solder) is electroplated in contact with the layer 40 of UBM to a thickness of between about 30 and 100 ⁇ m but more preferably to a thickness of about 50 ⁇ m.

- the layers 38 , 40 and 42 of electroplated metalare centered in the opening 31 that has been created in the layer 37 of photoresist.

- the patterned layer 37 of photoresisthas been removed from above the surface of the barrier layer 36 .

- the previously highlighted methods and processing conditions for the removal of a layer of photoresistcan be applied for the purpose of the removal of layer 37 that is shown in cross section in FIG. 11 .

- the inventionfurther proceeds with the partial etching of the pillar metal 38 , as shown in cross section in FIG. 12 , using methods of wet chemical etching or an isotropic dry etch, selective to the pillar metal material. It is clear that, by adjusting the etching parameters, of which the time of etch is most beneficial, the diameter of the pillar metal 38 can be reduced by almost any desired amount.

- the limitation that is imposed on the extent to which the diameter of the pillar metal 38 is reducedis not imposed by the wet etching process but by concerns of metal bump reliability and functionality. Too small a remaining diameter of the pillar metal 38 will affect the robustness of the solder bumps while this may also have the effect of increasing the resistance of the metal bump.

- the final two processing steps of the invention, before the solder metal is reflowed,are shown in the cross section of FIGS. 13 and 14 and affect the etching of the exposed surface of the barrier layer 36 .

- isotropic etchingthe exposed barrier layer is completely removed as is shown in FIG. 13 .

- anisotropic etchingin FIG. 14 , the etching of the barrier layer is partially impeded by the presence of the columns 42 of solder metal.

- the undercut shape of pillar 38will prevent wetting of pillar 38 and the UBM layer 40 during subsequent solder reflow. It is also believed that exposure to air will oxidize the sidewalls of pillar 38 and UBM layer 40 and therefore prevent wetting of these surfaces during subsequent solder reflow.

- the sidewalls of pillar 38 and UBM layer 40may be further oxidized by, for example, a thermal oxidation below reflow temperature of about 240 degrees C. such as heating in oxygen ambient at about 125 degrees C.

- FIGS. 15 and 16show the final cross section of the solder bump of the invention after the solder metal has been reflowed.

- FIG. 15corresponds to FIG. 13 while FIG. 16 corresponds to FIG. 14 , this relating to the etch in the barrier layer 36 that has been explained using FIGS. 13 and 14 .

- the etched layer 36 of barrier material that is shown in cross section in FIG. 15corresponds to the etched layer of barrier material that is shown in FIG. 13 .

- FIGS. 16 and 14show the same correspondence exists between FIGS. 16 and 14 .

- FIG. 17there is shown a cross section of the BGA package of the invention whereby the semiconductor device has been encapsulated in a molding compound.

- the elements that are highlighted in the cross section of FIG. 5are the following:

- the columns 54 of pillar metaltypically have a height of between about 10 and 100 ⁇ m and more preferably about 50 ⁇ m.

- FIG. 18The cross section that is shown in FIG. 18 is identical to the cross section of FIG. 17 with the exception of the underfill 62 which is used instead of the molding compound 60 of FIG. 17 .

- the creation of the pillar metal 54 and the solder bump 56starts using the I/O contact pads of device 50 (not shown in FIGS. 17 , 18 ) as the contact pads; that is the I/O contact pads of device 50 take the place of the contact pad 32 of FIGS. 15 and 16 in the creation of the pillar metal 54 and the solder bump 56 .

- the process of creating the pillar metal 54 and the solder bump 56therefore is as follows:

- FIG. 19there is shown a top view of an array type arrangement of I/O contact points 66 that form the contact points of device 50 .

- This top view of the array type contact points 66is shown as one example of where the process of creating pillar metal and solder bumps can be applied.

- FIGS. 20 and 21show two more examples of arrangements of I/O contact pads that are provided on the surface of device 50 , where the process of the invention can be applied.

- FIG. 20shows a peripheral I/O pad design 68 while

- FIG. 21shows a center type pad design 70 .

- peripheral I/O pad designthat is shown in FIG. 20 provides evenly distributed mechanical support for device 50 , this is not the case for the center pad design that is shown in FIG. 21 .

- additional mechanical supportcan be provided to device 50 ; this is shown in top view in FIG. 22 .

- the elements highlighted as 70 in FIG. 22are the solder bumps that have been created on the I/O contact pads of device 50 ; elements 72 are dummy solder bumps that can be provided in order to lend mechanical support to device 50 .

- the symmetry of the dummy bumps 72 as shown in FIG. 22makes clear that device 50 is, with the dummy bumps 72 , adequately and symmetrically supported.

- solder fluxIn mounting semiconductor devices on the surface of a BGA substrate, it is important from a manufacturing point of view that solder flux, after the process of solder flow has been completed, can be readily removed. This requires easy access to the surface areas of the BGA substrate where solder flux has been able to accumulate.

- the device interconnectsConsisting of pillar metal and solder bumps

- the flux that has accumulated in the gap between the semiconductor die and the substratemust be cleaned.

- solder masknot across the entire surface of the substrate (blank deposition) but to leave open the surface areas of the substrate that are immediately adjacent to the I/O interconnects (of pillar metal and solder bumps).

- This designwill create a channel though which the cleaning solution can flow easily. This is highlighted in the top view of FIGS. 23 and 24 , where is shown:

- FIGS. 25 and 26show how prior art procedures and conventions are applied to affect flux removal and encapsulant application.

- the metal pads 74are typically surrounded by the solder mask 78 , even for small pitch I/O pad designs.

- the solder maskis determined by the type of contact pad design ( FIGS. 19 through 21 ), whereby the contact pads 74 require about 60 ⁇ m clearance for reasons of proper alignment registration. This results in the substrate design rule being more critical, allowing for less error and smaller tolerance in the design parameters.

- the height of the solder mask 78is generally about 10 ⁇ m larger than the height of the contact pad 74 , further forming an obstacle in applying molding compound or in removing flux after the solder process has been completed.

- FIGS. 27 a through 27 fshow examples of applications of the invention, as follows:

- FIG. 27 ashows the application of a solder mask over the surface that has previously been shown in FIG. 19 , the solder mask has been indicated with cross-hatched regions 90 , the regions where no solder mask is present have been highlighted with 91 .

- FIGS. 27 b and 27 crelate to the previous FIG. 20 , the solder mask has been highlighted as regions 90 while the regions where no solder mask is present have been highlighted with 91 .

- the design that is shown in FIG. 27 cis considered a “partial” peripheral type I/O pad configuration of a semiconductor device since I/O pads 68 are only provided along two opposing sides of the semiconductor device 50 .

- FIGS. 27 b and 27 ccan further be provided with supporting dummy solder bumps in the regions of the solder mask 90 , these supporting solder bumps have not been shown in FIGS. 27 b and 27 c.

- FIG. 27 dshows the design that has previously been shown in FIG. 21

- FIG. 27 eshows a design that is similar to the design of FIG. 27 d with the exception that the contact points 70 have now been provided in two columns. It is clear from these two drawings that channels have been created in the solder mask that are in line with and include the contact pads. These channels allow for easy flow of cleaning fluid and therefore allow for easy removal of solder flux after the process of chip encapsulation and solder flow has been completed.

- FIG. 27 frelates to the previously shown FIG. 22 , the above observation relating to the creation of a channel through the solder flux and the therefrom following easy flow of cleaning fluid equally applies to the design that is shown in FIG. 27 f.

- FIGS. 28 a and 28 bdemonstrate how the invention leads to the ability to reduce the pitch between I/O pads.

- FIG. 28 ashows how in prior art applications the solder mask 90 is provided, further shown in FIG. 28 a are:

- the required clearanceis needed by the solder mask and requires that extra space is required between the circumference 95 of the contact pad and the circumference 94 of the opening created in the solder mask.

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Wire Bonding (AREA)

Abstract

Description

- 10, a semiconductor surface such as the surface of a substrate

- 30, a layer of dielectric that has been deposited over the

semiconductor surface 10 - 32, contact pads that have been created on the surface of the

layer 30 of dielectric - 34, a patterned layer of passivation that has been deposited over the surface of the

layer 30 of dielectric; openings have been created in thelayer 34 of passivation, partially exposing the surface ofcontact pads 32 - 36, an isotropically etched layer of barrier metal; this layer of barrier metal has been isotropically etched; that is, the barrier metal has been completely removed from the surface of the

layer 34 of passivation except where the barrier metal is covered by the overlying pillar metal (38) of the solder bump - 38, the pillar metal of the solder bump

- 40, a layer of under bump metal created overlying the

pillar metal 38 of the solder bump, wherein the distance between an edge of the under bump metal layer and an edge of the metal pillar of the solder bump is greater than 0.2 microns - 42, the solder metal.

- 10, a silicon substrate over the surface of which

metal contact pads 32 have been created - 30, a layer of dielectric that has been deposited over the surface of

substrate 10 - 32, the metal contact pads, typically comprising aluminum, created over the surface of the

layer 30 of dielectric - 34, a layer of passivation that has been deposited over the surface of the

layer 30 of dielectric. Openings have been created in thelayer 34 of passivation that align with themetal contact pads 32, partially exposing the surface of thecontact pads 32 - 36, a layer of barrier metal that has been created over the surface of

layer 34 of passivation, including the openings that have been created in thelayer 34 of passivation, contacting theunderlying contact pads 32.

- 10, a silicon substrate over the surface of which

- prior to and in preparation for the invention, a semiconductor surface is provided, a layer of dielectric has been deposited over the semiconductor surface, a contact pad has been provided on the layer of dielectric, the contact pad has an exposed surface, a layer of passivation has been deposited over a semiconductor surface including the surface of said contact pad, and the layer of passivation has been patterned and etched, creating an opening in the layer of passivation, partially exposing the surface of the contact pad, the opening in the layer of passivation is centered with respect to the contact pad

- the invention starts with a barrier layer deposited over the surface of the layer of passivation, making contact with the contact pad through the opening created in the layer of passivation

- a layer of photoresist is deposited over the surface of the barrier layer

- the layer of photoresist is patterned and etched, creating an opening through the layer of photoresist, wherein the opening in the layer of photoresist aligns with and is centered with respect to the contact pad

- in sequence are deposited, bounded by the opening created in the layer of photoresist, a layer of pillar metal, a layer of under bump metal and a layer of solder metal

- the patterned layer of photoresist is removed from the surface of the barrier layer

- the layer of pillar metal is etched, reducing the diameter of the pillar metal

- the barrier layer is etched, using either isotropic or anisotropic etching

- the solder metal is reflowed.

- ball height is a very important reliability concern; in order to prevent thermal mismatch between overlying layers of a package (such as a semiconductor device and an underlying printed circuit board and the like) it is important to increase the distance between overlying elements; the invention provides this ability

- a larger solder ball (for better thermal or reliability performance) results in increased pitch; this is contrary to state of the art design requirements

- if small solder balls are used without providing height, it is very difficult to underfill the small gaps

- the solder is, using the invention, relatively far removed from the semiconductor device which means that the application of low-alpha solder is not required (alpha-particles create soft errors in memory products; lead is known to emit alpha-particles when lead decays)

- for the pillar metal a metal needs to be selected that has good conductivity and good ductility, such as copper. This is in order to provide improved thermal performance by counteracting thermal stress

- the height of the pillar of the solder bump of the invention is important and should be between about 10 to 100 μm in order to achieve objectives of high stand-off

- the metal that is used for the under bump metal layer is important in that this metal must have good adhesion with the overlying solder during solder reflow while this metal must not solve too fast and in so doing form a barrier to the solder; in addition, the UBM metal when exposed to air can form a layer of protective oxide thus preventing solder wetting to the pillar metal around the perimeter of the UBM metal during the reflow process; nickel is therefore preferred for the UBM metal

- 50, a semiconductor device that is mounted in the package of the invention shown in cross section in

FIG. 17 - 52, the (BGA) substrate on the surface of which

device 50 is mounted - 54, the pillar metal of the interface between the

device 50 and theBGA substrate 52, similar topillar metal 38 ofFIGS. 15 and 16 - 56, the solder bump of the interface between the

device 50 and theBGA substrate 52, similar tosolder bump 42 ofFIGS. 15 and 16 - 58, the contact balls that are used to interconnect the package of the invention with surrounding circuitry

- 60, molding compound into which the

device 50 is embedded for protection against the environment.

- 50, a semiconductor device that is mounted in the package of the invention shown in cross section in

- a layer of dielectric is deposited over the active surface of

device 50; the active surface ofdevice 50 is the surface in which I/O contact points have been provided; this surface will face theBGA substrate 52 after mounting of thedevice 50 onBGA substrate 52 - openings are created in the layer of dielectric, exposing the I/O contact pads of

device 50; this brings the process of the invention to the point of the related application where contact pads32 (FIGS. 15 ,16) have been created on the surface of thelayer 30 of dielectric - a layer of passivation is deposited over the surface of the layer of dielectric, similar to

layer 34,FIGS. 15 ,16 - openings are created in the layer of passivation, partially exposing the surface of the device I/O contact pads

- a barrier layer is deposited over the surface of the layer of passivation, identical to

layer 36,FIGS. 15 ,16 - the

pillar metal 54 of the solder bump is formed, identical tolayer 38,FIGS. 15 ,16 - the layer of under bump (not shown in

FIGS. 17 ,18) is created overlying the pillar metal, identical tolayer 40,FIGS. 15 ,16 - the