US7105889B2 - Selective implementation of barrier layers to achieve threshold voltage control in CMOS device fabrication with high k dielectrics - Google Patents

Selective implementation of barrier layers to achieve threshold voltage control in CMOS device fabrication with high k dielectricsDownload PDFInfo

- Publication number

- US7105889B2 US7105889B2US10/863,830US86383004AUS7105889B2US 7105889 B2US7105889 B2US 7105889B2US 86383004 AUS86383004 AUS 86383004AUS 7105889 B2US7105889 B2US 7105889B2

- Authority

- US

- United States

- Prior art keywords

- gate

- insulating interlayer

- cmos structure

- dielectric

- gate conductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime, expires

Links

- 239000003989dielectric materialSubstances0.000titledescription7

- 238000004519manufacturing processMethods0.000titledescription3

- 230000004888barrier functionEffects0.000title1

- 239000011229interlayerSubstances0.000claimsabstractdescription119

- 239000000758substrateSubstances0.000claimsabstractdescription51

- 239000004065semiconductorSubstances0.000claimsabstractdescription42

- BPQQTUXANYXVAA-UHFFFAOYSA-NOrthosilicateChemical compound[O-][Si]([O-])([O-])[O-]BPQQTUXANYXVAA-UHFFFAOYSA-N0.000claimsabstractdescription22

- 229910052735hafniumInorganic materials0.000claimsabstractdescription21

- VBJZVLUMGGDVMO-UHFFFAOYSA-Nhafnium atomChemical compound[Hf]VBJZVLUMGGDVMO-UHFFFAOYSA-N0.000claimsabstractdescription18

- CJNBYAVZURUTKZ-UHFFFAOYSA-Nhafnium(IV) oxideInorganic materialsO=[Hf]=OCJNBYAVZURUTKZ-UHFFFAOYSA-N0.000claimsabstractdescription12

- 229910017105AlOxNyInorganic materials0.000claimsabstractdescription7

- CEPICIBPGDWCRU-UHFFFAOYSA-N[Si].[Hf]Chemical compound[Si].[Hf]CEPICIBPGDWCRU-UHFFFAOYSA-N0.000claimsabstractdescription6

- 239000004020conductorSubstances0.000claimsdescription62

- VYPSYNLAJGMNEJ-UHFFFAOYSA-NSilicium dioxideChemical compoundO=[Si]=OVYPSYNLAJGMNEJ-UHFFFAOYSA-N0.000claimsdescription49

- PMHQVHHXPFUNSP-UHFFFAOYSA-Mcopper(1+);methylsulfanylmethane;bromideChemical compoundBr[Cu].CSCPMHQVHHXPFUNSP-UHFFFAOYSA-M0.000claimsdescription41

- 239000000463materialSubstances0.000claimsdescription35

- 229910052710siliconInorganic materials0.000claimsdescription29

- XUIMIQQOPSSXEZ-UHFFFAOYSA-NSiliconChemical compound[Si]XUIMIQQOPSSXEZ-UHFFFAOYSA-N0.000claimsdescription24

- 239000010703siliconSubstances0.000claimsdescription24

- 239000000377silicon dioxideSubstances0.000claimsdescription23

- 229910052681coesiteInorganic materials0.000claimsdescription21

- 229910052906cristobaliteInorganic materials0.000claimsdescription21

- 229910021420polycrystalline siliconInorganic materials0.000claimsdescription21

- 229910052682stishoviteInorganic materials0.000claimsdescription21

- 229910052905tridymiteInorganic materials0.000claimsdescription21

- 229910052751metalInorganic materials0.000claimsdescription19

- 239000002184metalSubstances0.000claimsdescription19

- 150000004767nitridesChemical class0.000claimsdescription16

- 229920005591polysiliconPolymers0.000claimsdescription16

- QVGXLLKOCUKJST-UHFFFAOYSA-Natomic oxygenChemical compound[O]QVGXLLKOCUKJST-UHFFFAOYSA-N0.000claimsdescription12

- 229910052760oxygenInorganic materials0.000claimsdescription12

- 239000001301oxygenSubstances0.000claimsdescription12

- 229910000577Silicon-germaniumInorganic materials0.000claimsdescription9

- 229910052782aluminiumInorganic materials0.000claimsdescription9

- 229910052796boronInorganic materials0.000claimsdescription8

- ZOXJGFHDIHLPTG-UHFFFAOYSA-NBoronChemical compound[B]ZOXJGFHDIHLPTG-UHFFFAOYSA-N0.000claimsdescription7

- 239000012212insulatorSubstances0.000claimsdescription7

- 229910021332silicideInorganic materials0.000claimsdescription7

- 229910003811SiGeCInorganic materials0.000claimsdescription6

- 229910044991metal oxideInorganic materials0.000claimsdescription6

- 150000004706metal oxidesChemical class0.000claimsdescription6

- PIGFYZPCRLYGLF-UHFFFAOYSA-NAluminum nitrideChemical compound[Al]#NPIGFYZPCRLYGLF-UHFFFAOYSA-N0.000claimsdescription5

- XAGFODPZIPBFFR-UHFFFAOYSA-NaluminiumChemical compound[Al]XAGFODPZIPBFFR-UHFFFAOYSA-N0.000claimsdescription5

- 230000000295complement effectEffects0.000claimsdescription5

- 150000001875compoundsChemical class0.000claimsdescription5

- 229910052733galliumInorganic materials0.000claimsdescription5

- 229910052732germaniumInorganic materials0.000claimsdescription5

- 229910052738indiumInorganic materials0.000claimsdescription5

- 229910052698phosphorusInorganic materials0.000claimsdescription5

- PZNSFCLAULLKQX-UHFFFAOYSA-NBoron nitrideChemical compoundN#BPZNSFCLAULLKQX-UHFFFAOYSA-N0.000claimsdescription4

- GYHNNYVSQQEPJS-UHFFFAOYSA-NGalliumChemical compound[Ga]GYHNNYVSQQEPJS-UHFFFAOYSA-N0.000claimsdescription4

- JMASRVWKEDWRBT-UHFFFAOYSA-NGallium nitrideChemical compound[Ga]#NJMASRVWKEDWRBT-UHFFFAOYSA-N0.000claimsdescription4

- OAICVXFJPJFONN-UHFFFAOYSA-NPhosphorusChemical compound[P]OAICVXFJPJFONN-UHFFFAOYSA-N0.000claimsdescription4

- GWEVSGVZZGPLCZ-UHFFFAOYSA-NTitan oxideChemical compoundO=[Ti]=OGWEVSGVZZGPLCZ-UHFFFAOYSA-N0.000claimsdescription4

- MCMNRKCIXSYSNV-UHFFFAOYSA-NZirconium dioxideChemical compoundO=[Zr]=OMCMNRKCIXSYSNV-UHFFFAOYSA-N0.000claimsdescription4

- NWAIGJYBQQYSPW-UHFFFAOYSA-NazanylidyneindiganeChemical compound[In]#NNWAIGJYBQQYSPW-UHFFFAOYSA-N0.000claimsdescription4

- APFVFJFRJDLVQX-UHFFFAOYSA-Nindium atomChemical compound[In]APFVFJFRJDLVQX-UHFFFAOYSA-N0.000claimsdescription4

- 239000011574phosphorusSubstances0.000claimsdescription4

- 229910010271silicon carbideInorganic materials0.000claimsdescription4

- 229910000673Indium arsenideInorganic materials0.000claimsdescription3

- 239000007789gasSubstances0.000claimsdescription3

- RPQDHPTXJYYUPQ-UHFFFAOYSA-Nindium arsenideChemical compound[In]#[As]RPQDHPTXJYYUPQ-UHFFFAOYSA-N0.000claimsdescription3

- 229910052741iridiumInorganic materials0.000claimsdescription3

- 229910003465moissaniteInorganic materials0.000claimsdescription3

- 229910052750molybdenumInorganic materials0.000claimsdescription3

- 229910052759nickelInorganic materials0.000claimsdescription3

- 229910052758niobiumInorganic materials0.000claimsdescription3

- 229910052702rheniumInorganic materials0.000claimsdescription3

- 150000004760silicatesChemical class0.000claimsdescription3

- 229910052715tantalumInorganic materials0.000claimsdescription3

- 229910052721tungstenInorganic materials0.000claimsdescription3

- 229910002244LaAlO3Inorganic materials0.000claimsdescription2

- 229910002370SrTiO3Inorganic materials0.000claimsdescription2

- PNEYBMLMFCGWSK-UHFFFAOYSA-Naluminium oxideInorganic materials[O-2].[O-2].[O-2].[Al+3].[Al+3]PNEYBMLMFCGWSK-UHFFFAOYSA-N0.000claimsdescription2

- 229910052593corundumInorganic materials0.000claimsdescription2

- MRELNEQAGSRDBK-UHFFFAOYSA-Nlanthanum oxideInorganic materials[O-2].[O-2].[O-2].[La+3].[La+3]MRELNEQAGSRDBK-UHFFFAOYSA-N0.000claimsdescription2

- KTUFCUMIWABKDW-UHFFFAOYSA-Noxo(oxolanthaniooxy)lanthanumChemical compoundO=[La]O[La]=OKTUFCUMIWABKDW-UHFFFAOYSA-N0.000claimsdescription2

- 229910001845yogo sapphireInorganic materials0.000claimsdescription2

- RUDFQVOCFDJEEF-UHFFFAOYSA-Nyttrium(III) oxideInorganic materials[O-2].[O-2].[O-2].[Y+3].[Y+3]RUDFQVOCFDJEEF-UHFFFAOYSA-N0.000claimsdescription2

- 238000000034methodMethods0.000abstractdescription37

- -1H2O2 peroxideChemical class0.000abstractdescription4

- 239000010410layerSubstances0.000description69

- 238000005530etchingMethods0.000description22

- 238000005229chemical vapour depositionMethods0.000description21

- IJGRMHOSHXDMSA-UHFFFAOYSA-NAtomic nitrogenChemical compoundN#NIJGRMHOSHXDMSA-UHFFFAOYSA-N0.000description19

- 238000000151depositionMethods0.000description18

- 230000008021depositionEffects0.000description16

- 239000003990capacitorSubstances0.000description14

- 239000002019doping agentSubstances0.000description13

- 229920002120photoresistant polymerPolymers0.000description13

- 229910004129HfSiOInorganic materials0.000description12

- 238000002955isolationMethods0.000description12

- 125000006850spacer groupChemical group0.000description11

- 238000001704evaporationMethods0.000description9

- 238000005137deposition processMethods0.000description7

- 239000007943implantSubstances0.000description7

- 229910052757nitrogenInorganic materials0.000description7

- 239000000243solutionSubstances0.000description7

- 230000015572biosynthetic processEffects0.000description6

- 238000009792diffusion processMethods0.000description6

- 230000008020evaporationEffects0.000description6

- 230000003993interactionEffects0.000description6

- 230000003647oxidationEffects0.000description6

- 238000007254oxidation reactionMethods0.000description6

- 238000000623plasma-assisted chemical vapour depositionMethods0.000description6

- 238000012545processingMethods0.000description6

- 229910052814silicon oxideInorganic materials0.000description6

- 238000012360testing methodMethods0.000description6

- 238000000137annealingMethods0.000description5

- 238000000231atomic layer depositionMethods0.000description5

- 238000005516engineering processMethods0.000description5

- 239000011810insulating materialSubstances0.000description5

- 239000000203mixtureSubstances0.000description5

- 150000002978peroxidesChemical class0.000description5

- 238000000026X-ray photoelectron spectrumMethods0.000description4

- 238000000277atomic layer chemical vapour depositionMethods0.000description4

- 230000000694effectsEffects0.000description4

- FVBUAEGBCNSCDD-UHFFFAOYSA-Nsilicide(4-)Chemical compound[Si-4]FVBUAEGBCNSCDD-UHFFFAOYSA-N0.000description4

- 238000004544sputter depositionMethods0.000description4

- 230000000087stabilizing effectEffects0.000description4

- 238000000224chemical solution depositionMethods0.000description3

- 238000001312dry etchingMethods0.000description3

- 230000005669field effectEffects0.000description3

- 238000010348incorporationMethods0.000description3

- 238000005468ion implantationMethods0.000description3

- 238000001459lithographyMethods0.000description3

- 238000002161passivationMethods0.000description3

- 238000005240physical vapour depositionMethods0.000description3

- 238000001020plasma etchingMethods0.000description3

- 238000007747platingMethods0.000description3

- 238000000926separation methodMethods0.000description3

- 239000000126substanceSubstances0.000description3

- KRHYYFGTRYWZRS-UHFFFAOYSA-NFluoraneChemical compoundFKRHYYFGTRYWZRS-UHFFFAOYSA-N0.000description2

- NBIIXXVUZAFLBC-UHFFFAOYSA-NPhosphoric acidChemical compoundOP(O)(O)=ONBIIXXVUZAFLBC-UHFFFAOYSA-N0.000description2

- QAOWNCQODCNURD-UHFFFAOYSA-NSulfuric acidChemical compoundOS(O)(=O)=OQAOWNCQODCNURD-UHFFFAOYSA-N0.000description2

- 238000009825accumulationMethods0.000description2

- 230000004913activationEffects0.000description2

- 230000002411adverseEffects0.000description2

- 229910021417amorphous siliconInorganic materials0.000description2

- 238000003486chemical etchingMethods0.000description2

- 239000011248coating agentSubstances0.000description2

- 238000000576coating methodMethods0.000description2

- 239000013078crystalSubstances0.000description2

- 230000000593degrading effectEffects0.000description2

- 239000008367deionised waterSubstances0.000description2

- 230000002939deleterious effectEffects0.000description2

- 238000010494dissociation reactionMethods0.000description2

- 230000005593dissociationsEffects0.000description2

- 229910000449hafnium oxideInorganic materials0.000description2

- WIHZLLGSGQNAGK-UHFFFAOYSA-Nhafnium(4+);oxygen(2-)Chemical compound[O-2].[O-2].[Hf+4]WIHZLLGSGQNAGK-UHFFFAOYSA-N0.000description2

- 150000002500ionsChemical class0.000description2

- 229910052914metal silicateInorganic materials0.000description2

- 150000007522mineralic acidsChemical class0.000description2

- 230000007935neutral effectEffects0.000description2

- 239000007800oxidant agentSubstances0.000description2

- 230000005855radiationEffects0.000description2

- 235000012239silicon dioxideNutrition0.000description2

- 235000012431wafersNutrition0.000description2

- XTEGARKTQYYJKE-UHFFFAOYSA-MChlorateChemical class[O-]Cl(=O)=OXTEGARKTQYYJKE-UHFFFAOYSA-M0.000description1

- 229910001218Gallium arsenideInorganic materials0.000description1

- 239000003929acidic solutionSubstances0.000description1

- 229910045601alloyInorganic materials0.000description1

- 239000000956alloySubstances0.000description1

- 229910000147aluminium phosphateInorganic materials0.000description1

- 229910052787antimonyInorganic materials0.000description1

- 229910052785arsenicInorganic materials0.000description1

- 125000004429atomChemical group0.000description1

- 229910052797bismuthInorganic materials0.000description1

- YZYDPPZYDIRSJT-UHFFFAOYSA-Kboron phosphateChemical compound[B+3].[O-]P([O-])([O-])=OYZYDPPZYDIRSJT-UHFFFAOYSA-K0.000description1

- 229910000149boron phosphateInorganic materials0.000description1

- 238000006243chemical reactionMethods0.000description1

- QBWCMBCROVPCKQ-UHFFFAOYSA-Nchlorous acidChemical classOCl=OQBWCMBCROVPCKQ-UHFFFAOYSA-N0.000description1

- 238000000354decomposition reactionMethods0.000description1

- 229910021641deionized waterInorganic materials0.000description1

- 238000000280densificationMethods0.000description1

- 238000000572ellipsometryMethods0.000description1

- 238000011049fillingMethods0.000description1

- 125000005843halogen groupChemical group0.000description1

- WQYVRQLZKVEZGA-UHFFFAOYSA-NhypochloriteChemical classCl[O-]WQYVRQLZKVEZGA-UHFFFAOYSA-N0.000description1

- 230000003116impacting effectEffects0.000description1

- 238000002513implantationMethods0.000description1

- 238000011065in-situ storageMethods0.000description1

- 238000010884ion-beam techniqueMethods0.000description1

- 238000000608laser ablationMethods0.000description1

- 238000005259measurementMethods0.000description1

- 150000002739metalsChemical class0.000description1

- 150000002823nitratesChemical class0.000description1

- 150000002826nitritesChemical class0.000description1

- VLTRZXGMWDSKGL-UHFFFAOYSA-Nperchloric acidChemical classOCl(=O)(=O)=OVLTRZXGMWDSKGL-UHFFFAOYSA-N0.000description1

- JRKICGRDRMAZLK-UHFFFAOYSA-Lpersulfate groupChemical groupS(=O)(=O)([O-])OOS(=O)(=O)[O-]JRKICGRDRMAZLK-UHFFFAOYSA-L0.000description1

- 238000000206photolithographyMethods0.000description1

- 239000002243precursorSubstances0.000description1

- 238000004321preservationMethods0.000description1

- 238000005546reactive sputteringMethods0.000description1

- 239000005368silicate glassSubstances0.000description1

- LIVNPJMFVYWSIS-UHFFFAOYSA-Nsilicon monoxideChemical class[Si-]#[O+]LIVNPJMFVYWSIS-UHFFFAOYSA-N0.000description1

- 238000010561standard procedureMethods0.000description1

- 238000001771vacuum depositionMethods0.000description1

- XLYOFNOQVPJJNP-UHFFFAOYSA-NwaterChemical compoundOXLYOFNOQVPJJNP-UHFFFAOYSA-N0.000description1

Images

Classifications

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F30/00—Individual radiation-sensitive semiconductor devices in which radiation controls the flow of current through the devices, e.g. photodetectors

- H10F30/20—Individual radiation-sensitive semiconductor devices in which radiation controls the flow of current through the devices, e.g. photodetectors the devices having potential barriers, e.g. phototransistors

- H10F30/21—Individual radiation-sensitive semiconductor devices in which radiation controls the flow of current through the devices, e.g. photodetectors the devices having potential barriers, e.g. phototransistors the devices being sensitive to infrared, visible or ultraviolet radiation

- H10F30/28—Individual radiation-sensitive semiconductor devices in which radiation controls the flow of current through the devices, e.g. photodetectors the devices having potential barriers, e.g. phototransistors the devices being sensitive to infrared, visible or ultraviolet radiation the devices being characterised by field-effect operation, e.g. junction field-effect phototransistors

- H10F30/2823—Individual radiation-sensitive semiconductor devices in which radiation controls the flow of current through the devices, e.g. photodetectors the devices having potential barriers, e.g. phototransistors the devices being sensitive to infrared, visible or ultraviolet radiation the devices being characterised by field-effect operation, e.g. junction field-effect phototransistors the devices being conductor-insulator-semiconductor devices, e.g. diodes or charge-coupled devices [CCD]

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/60—Electrodes characterised by their materials

- H10D64/66—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes

- H10D64/68—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator

- H10D64/681—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator having a compositional variation, e.g. multilayered

- H10D64/685—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator having a compositional variation, e.g. multilayered being perpendicular to the channel plane

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/28008—Making conductor-insulator-semiconductor electrodes

- H01L21/28017—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon

- H01L21/28026—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon characterised by the conductor

- H01L21/28079—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon characterised by the conductor the final conductor layer next to the insulator being a single metal, e.g. Ta, W, Mo, Al

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/28008—Making conductor-insulator-semiconductor electrodes

- H01L21/28017—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon

- H01L21/28026—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon characterised by the conductor

- H01L21/28088—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon characterised by the conductor the final conductor layer next to the insulator being a composite, e.g. TiN

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/60—Electrodes characterised by their materials

- H10D64/66—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes

- H10D64/665—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes the conductor comprising a layer of elemental metal contacting the insulator, e.g. tungsten or molybdenum

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/60—Electrodes characterised by their materials

- H10D64/66—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes

- H10D64/667—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes the conductor comprising a layer of alloy material, compound material or organic material contacting the insulator, e.g. TiN workfunction layers

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/60—Electrodes characterised by their materials

- H10D64/66—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes

- H10D64/68—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator

- H10D64/691—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator comprising metallic compounds, e.g. metal oxides or metal silicates

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0165—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs the components including complementary IGFETs, e.g. CMOS devices

- H10D84/0181—Manufacturing their gate insulating layers

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/02—Manufacture or treatment characterised by using material-based technologies

- H10D84/03—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology

- H10D84/038—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology using silicon technology, e.g. SiGe

Definitions

- the present inventiongenerally relates to a semiconductor device, and more particularly to a complementary metal oxide semiconductor (CMOS) structure having nFET and pFET device regions, which incorporates an insulating interlayer between a gate conductor and a high k gate dielectric in at least one pFET device of the pFET device region without incorporating the insulating interlayer into the nFET device region, wherein the insulating interlayer stabilizes the threshold voltage V t and flatband voltage V fb of the pFET devices without substantially impacting the threshold voltage V t and flatband voltage V fb of the devices within the nFET device region.

- CMOScomplementary metal oxide semiconductor

- CMOScomplementary metal oxide semiconductor

- p-type field effect transistorsuse a boron (or other acceptor) doped p-type polysilicon layer as a gate conductor that is deposited on top of a silicon dioxide or silicon oxynitride gate oxide layer. The gate voltage is applied through this polysilicon layer to create an inversion channel in the n-type silicon underneath the gate oxide layer.

- FIG. 1shows the approximate band alignment across a poly-Si/gate oxide gate stack in a typical pFET at zero gate bias.

- E c , E v and E fare the conduction band edge, valence band edge and the Fermi level in the silicon, respectively.

- the poly-Si/gate oxide/n-type silicon stackforms a capacitor that swings into inversion at around 0 V and into accumulation around +1 V (depending on the substrate doping).

- the threshold voltage V twhich can be interpreted as the voltage at which the inversion starts occurring, is therefore approximately 0 V and the flatband voltage V fb , which is the voltage just beyond which the capacitor starts to swing into accumulation, is approximately +1 V.

- the exact values of the threshold V t and flatband voltages V fbhave a dependence on the doping level in the silicon substrate, and can be varied somewhat by choosing an appropriate substrate doping level.

- silicon dioxide or silicon oxynitride dielectricswill be replaced with a gate material that has a higher dielectric constant.

- These materialsare known as “high k” materials with the term “high k” denoting an insulating material whose dielectric constant is greater than 4.0, preferably greater than about 7.0.

- the dielectric constants mentioned hereinare relative to a vacuum unless otherwise specified.

- hafnium oxide, hafnium silicate, or hafnium silicon oxynitridemay be the most suitable replacement candidates for conventional gate dielectrics due to their excellent thermal stability at high temperatures.

- This threshold voltage V t shiftis believed to be a consequence of an intimate interaction between the Hf-based gate oxide layer and the polysilicon layer.

- One model(See, for example, C. Hobbs, et al., ibid.) speculates that such an interaction causes an increase in the density of states in the silicon band gap at the polysilicon-gate oxide interface, leading to “Fermi level pinning”.

- the threshold voltage V ttherefore is not in the “right” place, i.e., it is too high for a useable CMOS (complementary metal oxide semiconductor) technology.

- FIG. 2depicts the capacitance v.

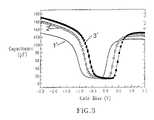

- FIG. 3depicts capacitance v.

- an nFET devicecomprising a 2.5 nm thick SiO 2 dielectric layer (control), as indicated by reference number 1 ′; an nFET device comprising a 3.0 nm HfSiO high k dielectric atop a 1.0 nm SiO 2 dielectric layer, as indicated by reference number 2 ′; and an nFET device comprising an AlN insulating interlayer atop a 3.0 nm HfSiO high k dielectric atop a 1.0 nm SiO 2 dielectric layer, as indicated by reference number 3 ′.

- the positive shift in the threshold voltage V t due to the incorporation of the AlN insulating interlayer within the nFET deviceis an equally unfavorable characteristic as the original negative shift in the threshold voltage V t of the pFET device, without the AlN insulating interlayer.

- Prior methods to remove the AlN insulating layer from the nFET device region, without destroying the underlying nFET device region surface or removing the AlN insulating layer from the pFET device region,are not known.

- Prior etchantssuch as KOH or dry reactive etching techniques are undesirable due to their deleterious impact on the underlying high k dielectric.

- an insulating interlayere.g. AlN

- the present inventionadvantageously stabilizes the threshold voltage V t and flatband voltage V fb in pFET devices by providing an insulating interlayer between the high k dielectric and the gate conductor, wherein the insulating interlayer prevents interaction between the high k gate dielectric and the gate conductor by spatial separation.

- the threshold V t and flatband voltage V fb shift attributed to the incorporation of the insulating interlayer in the nFET devicesis stabilized by removing the insulating interlayer from the nFET devices, without etching the nFET devices or removing the insulating interlayer from the pFET device region.

- the inventive method for providing a CMOS structure having high k dielectric pFET and nFET devicescomprises the steps of:

- dielectric stackatop said semiconducting substrate including said first device region and said second device region, said dielectric stack comprising an insulating interlayer atop a high k dielectric;

- the first device regionis the area in which nFET devices are formed, while the second device region is the area in which pFET devices are formed.

- the insulating interlayer employed in the present inventionis any insulating material that is capable of preventing interaction between the high k gate dielectric and the gate conductor by spatial separation. Moreover, the insulating interlayer employed in the present invention has a sufficiently high dielectric constant (on the order of about 4.0 or greater) such that there is a minimal decrease in gate capacitance (due to series capacitance effect) with its addition.

- the insulating interlayer of the present inventionis substantially non-reactive with the underlying high k gate dielectric; therefore it does not react with the high k gate dielectric forming a silicide.

- the insulating interlayer of the present inventionis also non-reactive with the above lying gate conductor.

- inventive insulating interlayeris that it is chemically stable so that silicon cannot reduce it.

- inventive insulating interlayershould not be an n-type dopant to silicon. Rather, the inventive insulating interlayer can be either a p-type dopant or a neutral dopant so that device performance is not adversely affected.

- the insulating interlayer employed in the present inventionshould be a refractory compound that is able to withstand high temperatures (of approximately 1000° C., typical of standard CMOS processing).

- Insulating materials that fit the above mentioned criteria and are thus employed as the insulating interlayer of the present inventioninclude any insulating metal nitride, i.e., metal nitride containing material, that may optional include oxygen therein.

- insulating interlayersinclude, but are not limited to: aluminum nitride (AlN), aluminum oxynitride (AlO x N y ), boron nitride (BN), boron oxynitride (BO x N y ), gallium nitride (GaN), gallium oxynitride (GaON), indium nitride (InN), indium oxynitride (InON) and combinations thereof.

- AlNaluminum nitride

- AlO x N yaluminum oxynitride

- BNboron nitride

- BO x N yboron nitride

- GaNgallium nitride

- the insulating interlayeris a thin interlayer located between the high k gate dielectric and the gate conductor. Typically, the insulating interlayer has a thickness in the range from about 1 to about 25 ⁇ , with a thickness from about 2 to about 15 ⁇ being more typical.

- the insulating interlayeris formed by deposition or thermal growing. The deposition comprises plating, sputtering, atomic layer chemical vapor deposition (ALCVD) or metal organic chemical vapor deposition (MOCVD).

- the high k dielectriccomprises any dielectric material having a dielectric constant greater than 4.0, preferably being greater than 7.0.

- the high k dielectriccomprises HfO 2 , hafnium silicate or hafnium silicon oxynitride.

- the high k dielectricis formed by deposition or thermal growing. Thermal growing may comprise oxidation, nitridation, and/or oxynitridation. Deposition may comprise chemical vapor deposition (CVD), plasma-enhanced CVD (PECVD), metal organic chemical vapor deposition (MOCVD), high-density chemical vapor deposition (HDCVD), plating, sputtering, evaporation and/or chemical solution deposition.

- CVDchemical vapor deposition

- PECVDplasma-enhanced CVD

- MOCVDmetal organic chemical vapor deposition

- HDCVDhigh-density chemical vapor deposition

- Removing the insulating interlayer from the first device region, without removing the insulating interlayer from the second device regioncan include forming a block mask atop the second device region, wherein the first device region is exposed; and etching the insulating interlayer from the first device region.

- the insulating interlayermay be etched by an etch chemistry that removes the insulating interlayer without substantially etching the block mask positioned in the second device region and the portion of the high k dielectric positioned underlying the insulating interlayer in the first device region.

- CMOS structureprovided by the above method.

- the present inventionprovides a CMOS structure comprising:

- a semiconductor substratehaving a first device region and a second device region

- said first device regioncomprising at least one first gate stack comprising a first high k gate dielectric and a first gate conductor

- said second device regioncomprising at least one second gate stack comprising a second high k dielectric, an insulating interlayer atop said high k gate, and a second gate conductor atop said insulating layer, wherein said insulating interlayer is capable of stabilizing said second device regions threshold voltage and flatband voltage without shifting said first device regions threshold voltage and flatband voltage.

- the quantities E c and E vdenote the conduction and the valence band edge, respectively, in the silicon substrate and in the polysilicon gate.

- E fdenotes the Fermi level position (dotted line) in the silicon substrate and in the polysilicon gate at zero gate bias.

- FIG. 2is a graph showing the capacitance-voltage curves for three types of pFET devices.

- the capacitance voltage curvesinclude a plot for a pFET comprising a AlN threshold insulating interlayer on a 3 nm HfSiO high k dielectric on a 1 nm SiO 2 dielectric layer; a pFET comprising a 3 nm HfSiO high k dielectric on a 1 nm SiO 2 dielectric layer; and a pFET comprising a 2.5 nm thick SiO 2 dielectric layer.

- FIG. 3is a graph showing the capacitance-voltage curves for three types of nFET devices.

- the capacitance voltage curvesinclude a plot for an nFET comprising a AlN threshold insulating interlayer on a 3 nm HfSiO high k dielectric on a 1 nm SiO 2 dielectric layer; an nFET comprising a 3 nm HfSiO high k dielectric on a 1 nm SiO 2 dielectric layer; and an nFET comprising a 2.5 nm thick SiO 2 dielectric layer.

- FIG. 4is a pictorial representation (through a cross sectional view) of the inventive CMOS structure that includes a pFET device region having a threshold voltage V t stabilizing insulating interlayer between a high k gate dielectric and a poly-Si gate conductor and an nFET device region from which the insulating interlayer has been removed using the selective etch process of the present invention.

- FIGS. 5–8are pictorial representations (through a cross sectional views) of the process steps for the inventive method, which provides the CMOS structure depicted in FIG. 4 .

- FIG. 9is a plot showing capacitance voltage characteristics of the inventive CMOS structure, in which the insulating interlayer has been removed from the nFET device.

- FIG. 10is an XPS spectra depicting AlN content following the inventive selective etch process.

- the present inventionwhich provides a CMOS structure having an insulating interlayer (e.g., AlN interlayer) between a high k gate dielectric and a gate conductor of at least one pFET device, without incorporating the insulating interlayer into the nFET devices, wherein the positioning of the insulating interlayer stabilizes the threshold voltage V t and flatband voltage V fb for both pFET and nFET devices, and a method of fabricating the same will now be described in greater detail.

- insulating interlayerdenotes a metal-nitride containing interlayer which can include metal nitride and metal oxynitride materials.

- FIG. 4is a pictorial representation (through a cross sectional view) showing the CMOS structure 10 of the present invention.

- the CMOS structure 10includes a semiconductor substrate 12 having a pFET device region 15 and an nFET device region 25 separated by an isolation region 30 .

- the drawingsshow the presence of only two field effect transistors (FETs) on one substrate 12 , multiple FETs are also within the scope of the present invention.

- the pFET device region 15comprises at least one pFET having p-type source/drain regions 13 .

- Each of the pFETscomprises a gate region 18 having a gate conductor 24 atop an insulating interlayer 22 atop a high k dielectric 20 .

- At least one set of sidewall spacers 6are positioned abutting the gate conductor 24 .

- the nFET device region 25comprises at least one nFET having n-type source/drain regions 14 .

- Each of the nFETsfurther comprises a gate region 18 , including a gate conductor 24 atop a high k dielectric 20 , in which the gate conductor 24 is abutted by at least one set of sidewall spacers 6 .

- the insulating interlayer 22is positioned to stabilize the threshold voltage V t and flatband voltage V fb in pFET devices, without shifting the threshold voltage V t and flatband voltage V fb of the nFET devices, thereby providing a solution to the fabrication of CMOS transistors with the appropriate threshold and flatband voltages.

- the insulating interlayer 22 employed in the present inventionhas at least one of the following characteristics: (i) it is capable of preventing interaction between the high k gate dielectric 20 and the gate conductor 24 by spatial separation; (ii) it has a sufficiently high dielectric constant (on the order of about 4.0 or greater) such that there is a minimal decrease in gate capacitance (due to series capacitance effect) because of its addition; (iii) it may dissociate, at least partially, to provide a supply of p-type dopants in the near interfacial layer to ensure p-type behavior of near interfacial Si-containing material of the gate conductor 24 in the pFET device region 15 ; (iv) it can prevent outdiffusion of atoms from the high k gate dielectric 20 to the gate conductor 24 ; and (v) it can prevent oxidation under the gate conductor 24 .

- Examples of insulating interlayers 22include aluminum nitride (AlN), aluminum oxynitride (AlO x N y ), boron nitride (BN), boron oxynitride (BO x N y ), gallium nitride (GaN), gallium oxynitride (GaON), indium nitride (InN), indium oxynitride (InON) and combinations thereof.

- the insulating interlayer 22is AlN.

- blanket layers of high k dielectric 20 and insulating interlayer 22are formed on a surface of a semiconductor substrate 12 .

- the high k dielectric 20is located between the insulating interlayer 22 and the semiconductor substrate 12 .

- the semiconductor substrate 12 employed in the present inventioncomprises any semiconducting material including, but not limited to: Si, Ge, SiGe, SiC, SiGeC, Ga, GaAs, InAs, InP and all other III/V or II/VI compound semiconductors.

- Semiconductor substrate 12may also comprise an organic semiconductor or a layered semiconductor such as Si/SiGe, a silicon-on-insulator (SOI) or a SiGe-on-insulator (SGOI).

- SOIsilicon-on-insulator

- SGOISiGe-on-insulator

- the semiconductor substrate 12may be doped, undoped or contain doped and undoped regions therein.

- the semiconductor substrate 12may also include a first doped (n- or p-) region, and a second doped (n- or p-) region.

- n- or p-first doped

- n- or p-second doped

- the first doped region and the second doped regionmay be the same, or they may have different conductivities and/or doping concentrations. These doped regions are known as “wells”.

- the isolation region 30is then typically formed into the semiconductor substrate 12 .

- the isolation region 30may be a trench isolation region or a field oxide isolation region.

- the trench isolation regionis formed utilizing a conventional trench isolation process well known to those skilled in the art. For example, lithography, etching and filling of the trench with a trench dielectric may be used in forming the trench isolation region.

- a linermay be formed in the trench prior to trench fill, a densification step may be performed after the trench fill and a planarization process may follow the trench fill as well.

- the field oxidemay be formed utilizing a so-called local oxidation of silicon process.

- the at least one isolation regionprovides isolation between neighboring gate regions, typically required when the neighboring gates have opposite conductivities.

- the neighboring gate regionscan have the same conductivity (i.e., both n- or p-type), or alternatively they can have different conductivities (i.e., one n-type and the other p-type).

- a high k gate dielectric 20is formed on a surface of the structure.

- the high k gate dielectric 20can be formed by a thermal growth process such as, for example, oxidation, nitridation or oxynitridation.

- the high k gate dielectric 20can be formed by a deposition process such as, for example, chemical vapor deposition (CVD), plasma-assisted CVD, metalorganic chemical vapor deposition (MOCVD), atomic layer deposition (ALD), evaporation, reactive sputtering, chemical solution deposition and other like deposition processes.

- the high k gate dielectric 20may also be formed utilizing any combination of the above processes.

- the high k gate dielectric 20is comprised of an insulating material having a dielectric constant of greater than about 4.0, preferably greater than 7.0.

- the high k gate dielectric 20 employed in the present inventionincludes, but is not limited to: oxide, nitride, oxynitride and/or silicate including metal silicates and nitrided metal silicates.

- it is preferred that the gate dielectric 20is comprised of an oxide such as, for example, HfO 2 , ZrO 2 , Al 2 O 3 , TiO 2 , La 2 O 3 , SrTiO 3 , LaAlO 3 , Y 2 O 3 and mixtures thereof.

- Highly preferred examples of high k dielectrics 20include HfO 2 , hafnium silicate and hafnium silicon oxynitride.

- the physical thickness of the high k gate dielectric 20may vary, but typically, the high k gate dielectric 20 has a thickness from about 0.5 to about 10 nm, with a thickness from about 0.5 to about 3 nm being more typical. It may be deposited above a thin (on the order of about 0.1 to about 1.5 nm) layer of silicon oxide or silicon oxynitride that is first deposited on the substrate.

- the high k dielectricmay be selectively deposited on portions of the substrate using block masks as known within the skill of the art.

- a first portion of the substratemay be processed to provide a first high k dielectric for a first device type, such as an nFET, and a second portion of the substrate may be processed to provide a second high k dielectric for a second device type, such as a pFET.

- insulating interlayer 22is formed atop the blanket layer of high k gate dielectric 20 .

- the insulating interlayer 22 of the present inventionis a chemical interlayer that prevents interaction between the high k gate dielectric 20 and the subsequently formed gate conductor 24 .

- the insulating interlayer 22 of the present inventionis substantially non-reactive (there may be slight or partial decomposition, such as when its acts as a dopant source) with the underlying high k dielectric 20 ; therefore it does not react with the high k dielectric 20 to form a silicide.

- Another characteristic feature of the inventive insulating interlayer 22is that silicon cannot reduce the inventive insulating interlayer 22 .

- the inventive interlayer 22should be either a p-type dopant or a neutral dopant so that device performance is not adversely affected.

- the p-type dopantsdoes not dissociate into the portion of the device in which nFET devices are subsequently formed.

- the insulating interlayer 22 employed in the present inventionshould be a refractory compound that is able to withstand high temperatures (of approximately 1000° C., typical of standard CMOS processing).

- Insulating materials that fit the above-mentioned criteria and are thus employed as the insulating interlayer 22 of the present inventioninclude any insulating metal nitride that may optional include oxygen therein.

- insulating interlayersinclude, but are not limited to: aluminum nitride (AlN), aluminum oxynitride (AlO x N y ), boron nitride (BN), boron oxynitride (BO x N y ), gallium nitride (GaN), gallium oxynitride (GaON), indium nitride (InN), indium oxynitride (InON) and combinations thereof

- the insulating interlayer 22is AlN or AlO x N y .

- the insulating interlayer 22is a thin layer that typically has a thickness from about 1 to about 25 ⁇ , with a thickness from about 2 to about 15 ⁇ being more typical.

- the insulating interlayer 22can be formed by various deposition processes such as, for example, chemical vapor deposition (CVD), plasma-assisted CVD, atomic layer deposition (ALD) using aluminum and nitrogen-based precursors, physical vapor deposition or molecular beam deposition where the metal is evaporated along with a beam or ambient of atomic or molecular nitrogen (that may be optionally an excited species) and optionally oxygen, metalorganic chemical vapor deposition (MOCVD), atomic layer deposition, sputtering, and the like.

- the insulating interlayer 22can be formed by thermal nitridation or oxynitridation of a previously deposited insulating metal layer.

- the oxynitride of the metalmay be created by first depositing the metal nitride, followed by partial oxidation in a suitable oxygen environment to create and oxynitride.

- One preferred method of forming the interlayer insulating layer 22is by evaporating, under a high vacuum, Al from a standard Al effusion cell that is resistively heated, and using a nitrogen, or oxygen and nitrogen beams from commercial radio frequency (RF) atomic nitrogen or nitrogen and oxygen sources.

- RFradio frequency

- a nitrogen, or oxygen and nitrogen beamsfrom commercial radio frequency (RF) atomic nitrogen or nitrogen and oxygen sources.

- RFradio frequency

- a nitrogen, or oxygen and nitrogen beamsfrom commercial radio frequency (RF) atomic nitrogen or nitrogen and oxygen sources.

- RFradio frequency

- the effusion celltypically has a temperature from about 1000° C.–1200° C. during the evaporation process.

- the evaporation processis typically performed using a RF source having a power from about 200–450 W and a flow rate from about 1–3 sccm. These numbers can also be widely varied from the stated bounds without problems.

- the substrate temperatureis typically kept between 150° C. to 650° C. during deposition. Again, the deposition temperature can also be varied outside the stated ranges.

- Base vacuum chamber pressureis typically about 5 ⁇ 10 ⁇ 10 to 2 ⁇ 10 ⁇ 9 torr.

- the insulating interlayer 22 formed in the present inventionis a continuous and uniform layer that is present atop the high k gate dielectric 20 .

- continuousit is meant that the insulating interlayer 22 contains no substantial breaks and/or voids therein; by “uniform” it is meant that the insulating interlayer 22 has nearly the same, as deposited, thickness across the structure.

- the insulating interlayer 22may be amorphous meaning that it can lack a specific crystal structure.

- the insulating interlayer 22may exist in other phases besides amorphous depending on the material used as well as the technique that is used in forming the same.

- a block mask 50is formed protecting the portion of the substrate 12 in which pFETs are subsequently formed. This portion of the substrate is hereafter referred to as the pFET device region 15 .

- the exposed portion of the substrate that is not protected by the block maskis subsequently processed to provide nFET devices and is hereafter referred to as the nFET device region 25 .

- the block mask 50may comprise conventional soft and/or hardmask materials and can be formed using deposition, photolithography and etching.

- the block mask 50comprises a photoresist.

- a photoresist block mask 50can be produced by applying a photoresist layer to the substrate 12 surface, exposing the photoresist layer to a pattern of radiation, and then developing the pattern into the photoresist layer utilizing conventional resist developer.

- the block mask 50can be a hardmask material.

- Hardmask materialsinclude dielectrics systems that may be deposited by chemical vapor deposition (CVD) and related methods.

- the hardmask compositionincludes silicon oxides, silicon carbides, silicon nitrides, silicon carbonitrides, etc.

- Spin-on dielectricsmay also be utilized as a hardmask material including but not limited to: silsequioxanes, siloxanes, and boron phosphate silicate glass (BPSG).

- BPSGboron phosphate silicate glass

- a block mask 50 comprising hardmask materialmay be formed by blanket depositing a layer of hardmask material; providing a patterned photoresist atop the layer of hardmask material; and then etching the layer of hardmask material to provide a block mask 50 protecting the pFET device region 15 , in which etching comprises an etch chemistry having a high selectivity to the patterned photoresist and the surface of the nFET device region 25 .

- the exposed portion of the insulating interlayer 22is removed from the nFET device region 25 using a highly selective etch process.

- This highly selective etchpreferably comprises an etch chemistry which removes the exposed portion of the insulating interlayer 22 from the nFET device region 25 , without substantially etching the underlying high k dielectric 20 or the block mask 50 that protects the pFET device region 15 .

- a wet etchremoves the insulating interlayer 22 from the nFET device region 25 , without etching the underlying high k dielectric 20 or the block mask 50 .

- this etch chemistryremoves the AlN insulating interlayer 22 , without substantially etching an underlying hafnium silicate high k dielectric 20 .

- Prior etch methodscannot selectively remove AlN without etching the underlying high k dielectric 20 .

- wet etchantssuch as KOH

- dry etch techniquessuch as RIE

- the wet etch chemistrycomprises a solution of HCl and peroxide, the preferred concentration being 3:1 HCl:H 2 O 2 .

- HCl/peroxide solutionsit is proposed that other inorganic acids and oxidizing agents can produce the same results so long as the etch chemistry does not attack the high k dielectric 20 .

- the oxidizing agentsmay include peroxides, nitrates, nitrites, perchlorates, chlorates, chlorites, hypochlorites, dichromates, permanganates, persulfates or combinations thereof.

- the inorganic acidscan include sulfuric acid, phosphoric acid or combinations thereof. Etch rate may be impacted by the pH of the etch chemistry.

- the pH of the etch chemistrymay range from about 1 to about 8, preferably ranging from about 2 to about 6, most preferably being about 2.8.

- the etch compositioncan be mixed during an exothermic reaction.

- the wet etchmay be conducted in an oxygen-containing environments and may be conducted at room temperature or at an elevated temperature. Preferably, the etch temperature is 15° C. to 80° C.

- the block mask 50is removed using a chemical strip and the substrate 12 is rinsed with deionized water and dried in a N 2 ambient.

- the gate conductor 24may comprise any conductive material known by those skilled in the art.

- the gate conductor materialcan comprise polysilicon but may also be comprised of SiGe, SiGeC, metal silicides, metallic nitrides, metals (for example W, Ir, Re, Ru, Ti, Ta, Hf, Mo, Nb, Ni, Al), or a combination of the above.

- the at least one gate conductormay be deposited using chemical vapor deposition (CVD), plasma-enhanced chemical vapor deposition (PECVD), high-density chemical vapor deposition (HDCVD), plating, sputtering, evaporation or chemical solution deposition.

- CVDchemical vapor deposition

- PECVDplasma-enhanced chemical vapor deposition

- HDCVDhigh-density chemical vapor deposition

- platingsputtering, evaporation or chemical solution deposition.

- the gate conductor 24 formed in the pFET device region 15 and the nFET device region 25may be the same or a different material.

- block masksmay be utilized to selectively process the gate conductor 24 materials in the pFET device region 15 and the nFET device region 25 .

- a blanket layer of a Si-containing materialis formed on the insulating interlayer 22 in the pFET device region 15 and on the high k dielectric 20 in the nFET device region 25 utilizing a known deposition process including, but not limited to: physical vapor deposition, CVD or evaporation.

- the Si-containing material used in forming the gate conductor 24includes Si or a SiGe alloy layer in single crystal, polycrystalline or amorphous form. Combinations of the aforementioned Si-containing materials are also contemplated herein.

- the blanket layer of Si-containing materialmay be doped or undoped. If doped, an in-situ doping deposition process may be employed in forming the same.

- a doped Si-containing layercan be formed by deposition, ion implantation and annealing.

- the doping of the Si-containing layerwill shift the workfunction of the gate conductor 24 formed.

- dopant ionsinclude As, P, B, Sb, Bi, In, Al, Ga, or mixtures thereof, preferably being P.

- the thickness, i.e., height, of the Si-containing layer deposited at this point of the present inventionmay vary depending on the deposition process employed.

- the Si-containing layerhas a vertical thickness from about 20 to about 180 nm, with a thickness from about 40 to about 150 nm being more typical.

- a dielectric cap layer(not shown) can be formed atop the blanket layer of gate conductor material utilizing a deposition process such as, for example, physical vapor deposition or chemical vapor deposition.

- the dielectric cap layermay be an oxide, nitride, oxynitride or any combination thereof.

- the thickness, i.e., height, of the dielectric cap layeris from about 20 to about 180 nm, with a thickness from about 30 to about 140 nm being more typical.

- the dielectric cap (if present), the blanket gate conductor layer, and optionally the insulating interlayer 22 and the high k gate dielectric 20 in the pFET device region 15 and the high k gate dielectric in the nFET device region 25are then patterned by lithography and etching so as to provide at least one patterned gate stack 18 in the nFET and pFET device regions 15 , 25 .

- the gate stacks 18may have the same dimension, i.e., length, or they can have variable dimensions to improve device performance.

- Each patterned gate stack 18 at this point of the present inventionincludes at least the gate conductor 24 .

- the lithography stepincludes applying a photoresist to the upper surface of the blanket layered structure, exposing the photoresist to a desired pattern of radiation and developing the exposed photoresist utilizing a conventional resist developer.

- the pattern in the photoresistis then transferred to the structure utilizing one or more dry etching steps.

- the patterned photoresistmay be removed after the pattern has been transferred into one of the layers of the blanket layered structure. In other embodiments, the patterned photoresist is removed after etching has been completed.

- Suitable dry etching processesthat can be used in the present invention in forming the patterned gate stacks include, but are not limited to: reactive ion etching, ion beam etching, plasma etching or laser ablation.

- the dry etching process employedis typically, but not always, selective to the underlying high k dielectric 20 in the nFET device region 25 and the insulating interlayer 22 in the pFET device region 15 . Therefore this etching step does not typically remove the exposed portions of the insulating interlayer 22 and the high k dielectric 20 . In some embodiments, this etching step may however be used to remove portions of the high k dielectric 20 and the insulating interlayer 22 that are not protected by the gate conductor 24 that were previously etched.

- At least one set of spacers 6is typically, but not always, formed on exposed sidewalls of each patterned gate stack 18 .

- the at least one set of spacers 6is comprised of an insulator such as an oxide, nitride, oxynitride and/or any combination thereof.

- the at least one set of spacers 6is formed by deposition and etching.

- the width of the at least one spacer 6must be sufficiently wide such that the source and drain silicide contacts (to be subsequently formed) do not encroach underneath the edges of the gate stack.

- the source/drain silicidedoes not encroach underneath the edges of the gate stack when the at least one spacer has a width, as measured at the bottom, from about 20 to about 80 nm.

- the gate stack 18can also be passivated at this point of the present invention by subjecting the same to a thermal oxidation, nitridation or oxynitridation process.

- the passivation stepforms a thin layer of passivating material about the gate stack. This step may be used instead or in conjunction with the previous step of spacer formation. When used with the spacer formation step, spacer formation occurs after the gate stack passivation process.

- Source/drain diffusion regions 13 , 14are then formed into the substrate.

- the source/drain diffusion regions 13 , 14are formed utilizing ion implantation and an annealing step.

- P-type source/drain diffusion regions 13are formed within the pFET device region 15 and n-type source/drain diffusion regions 14 are formed within the nFET device region 25 .

- the annealing stepserves to activate the dopants that were implanted by the previous implant step.

- the conditions for the ion implantation and annealingare well known to those skilled in the art.

- the source/drain diffusion regions 13 , 14may also include extension implant regions, which are formed prior to source/drain implantation using a conventional extension implant having the same dopant type as the corresponding source/drain diffusion regions.

- the extension implantmay be followed by an activation anneal, or alternatively the dopants implanted during the extension implant and the source/drain implant can be activated using the same activation anneal cycle. Halo implants are also contemplated herein.

- the exposed portion of the high k dielectric 20is removed from the nFET device region 25 and the exposed portions of the insulating interlayer 22 and the high k dielectric 20 are removed from the pFET device region 25 utilizing a highly selective chemical etching process.

- This etching stepstops on an upper surface of the semiconductor substrate 12 .

- any chemical etchantmay be used in removing the exposed portions of the high k dielectric 20 and the insulating interlayer 22 , in one embodiment dilute hydrofluoric acid (DHF) is used.

- DHFdilute hydrofluoric acid

- CMOS structure of the present inventionis one in which the high k gate dielectric 20 is comprised of HfO 2 , hafnium silicate or hafnium silicon oxynitride and the insulating interlayer 22 is comprised of AlN, which optionally may include some oxygen therein.

- the particularly preferred structureare also contemplated herein and should not be excluded.

- CMOS processingsuch as formation of silicided contacts (source/drain and gate) as well as formation of BEOL (back-end-of-the-line) interconnect levels with metal interconnects can be formed utilizing processing steps that are well known to those skilled in the art.

- CMOS structurein which the inventive insulating interlayer 22 positioned only within pFET devices and removed from nFET devices.

- a Hf oxide or silicate layer(high k dielectric) was grown on a silicon substrate that was pre-patterned with an isolation region separating an nFET device region from a pFET device region.

- the Hf oxide and silicatewere deposited using metal organic chemical vapor deposition (MOCVD) and atomic layer chemical vapor deposition (ALCVD).

- MOCVDmetal organic chemical vapor deposition

- ACVDatomic layer chemical vapor deposition

- the thicknesses of the Hf oxide and silicate layerswere in the range of about 2 nm to about 4 nm and for the silicates, the composition was approximately Hf x Si y O 4 with y/(x+y) being approximately 0.2–0.3.

- These oxideswere deposited on an n-type silicon wafer having 0.3 nm to 1.2 nm thick silicon oxide or silicon oxynitride coating. The presence of this silicon oxide or silicon oxynitride coating is optional.

- the waferswere loaded in an ultra-high vacuum deposition chamber for aluminum nitride deposition (insulating interlayer).

- Aluminum nitridewas deposited by evaporating Al from a standard Al effusion cell that is resistively heated, and using a nitrogen beam from a commercial radio frequency atomic nitrogen source.

- the effusion cellhad a temperature of 1000° C.–1200° C. during operation.

- the atomic nitrogen sourcewas operated in the range of 200–450 W and a nitrogen flow rate of 1–3 sccm.

- the substrate temperaturewas kept between 150° C. to 650° C. during deposition.

- Base vacuum chamber pressurewas about 5 ⁇ 10 ⁇ 10 to 2 ⁇ 10 ⁇ 9 torr. During AlN deposition the pressure rose to the 1 ⁇ 10 ⁇ 5 torr range.

- the AlN layerswere deposited to a thicknesses ranging from about 0.5 nm to about 2.0 nm.

- the substrateswere then taken out and etched in a HCl:H 2 O 2 peroxide solution to remove the AlN layers, with no external heat supplied.

- the concentrations of this etchant solutioncomprised greater than 1 part HCl and greater than 1.5 parts H 2 O 2 , wherein an acidic solution was provided.

- the preferred concentrationcomprises 3:1 HCl:H 2 O 2 . It is noted that the pH resulting from the choice of concentration as described-above will impact the etch rate.

- the substrateswere rinsed with de-ionized water and dried in a N 2 ambient to provide a substrate having a Hf oxide surface.

- amorphous silicon layer(gate conductor layer) was then deposited atop the substrate surface to a thickness of approximately 150 nm thick using chemical vapor deposition using standard procedures.

- the amorphous silicon layerwas then ion implanted with phosphorus and the dopants activated by annealing at approximately 950° C. to approximately 1000° C., again following standard semiconductor processing procedures. In some cases, forming gas anneals were performed for SiO 2 /Si(100) interface state passivation.

- NMOS test capacitorswere then formed from these above structures using chemical vapor deposition and etching to define pad shapes on the order of about 20 ⁇ 20 square microns.

- the NMOS test capacitor structureswere etched using the above-described method to remove the AlN layer to provide a structure comprising a phosphorus doped polysilicon layer; a layer of Hf silicate or HfO 2 having a thickness ranging from about 2 nm to about 4 nm; and an SiO 2 or SiON layer having a thickness ranging from about 0.3 nm to about 1.2 nm; and a silicon (100) substrate.

- Capacitance-voltage curves for nMOS test capacitors with Hf silicate or HfO 2 as the gate dielectric and having an AlN layer deposited thereon and then removed by the selective etch of the present inventionare indicated by reference number 55 .

- Capacitance-voltage curves for the control capacitorsare indicated by reference number 60 .

- the flatband voltage V fb in the capacitance voltage curves for the capacitorsis equivalent to threshold voltage V t in transistors.

- comparison of the flatband voltage V fb of the test capacitors to the control capacitorsindicates that the flatband voltage V fb of the test capacitors was within 70 mV of the control capacitors. Therefore, since AlN can be removed from the surface of the test capacitors without substantially degrading the device's flatband voltage V fb ; the etch chemistries of the present invention can advantageously remove AlN without etching the underlying Hf silicate or HfO 2 high k dielectric or disadvantageously effecting the electrical properties of the Hf silicate or HfO 2 high k dielectric.

- an XPS spectrais provided of a blanket AlN film etched from a hafnium silicate surface by an etch chemistry comprising a HCl:H 2 O 2 solution in 3:1 ratio for 15 minutes.

- the XPS spectra of the HCl/peroxide etched surfaceis indicated by reference number 75 and the XPS surface of an AlN control surface is indicated by reference number 80 .

- the Al 2P peak detected from the AlN control surfaceis not present in the AlN film which was etched from the hafnium surface by the HCl/peroxide solution.

- the selectivity to hafnium silicatewas confirmed using the ellipsometry measurements, which showed no change in the thickness of the hafnium silicate film.

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Composite Materials (AREA)

- Chemical & Material Sciences (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Weting (AREA)

- Thin Film Transistor (AREA)

Abstract

Description

Claims (26)

Priority Applications (12)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/863,830US7105889B2 (en) | 2004-06-04 | 2004-06-04 | Selective implementation of barrier layers to achieve threshold voltage control in CMOS device fabrication with high k dielectrics |

| US10/957,342US7479683B2 (en) | 2004-06-04 | 2004-10-01 | Selective implementation of barrier layers to achieve threshold voltage control in CMOS device fabrication with high-k dielectrics |

| KR1020067025229AKR100951227B1 (en) | 2004-06-04 | 2005-03-30 | Selective Implementation of Barrier Layers for Controlling Threshold Voltages in CMOS Devices with High-K dielectrics |

| JP2007515066AJP4711444B2 (en) | 2004-06-04 | 2005-03-30 | Method for forming complementary metal oxide semiconductor (CMOS) structures with improved threshold voltage and flat band voltage stability (barrier layer to achieve threshold voltage control in CMOS device formation with high-k dielectrics) Selective implementation) |

| CN2005800161892ACN101427386B (en) | 2004-06-04 | 2005-03-30 | Selective implementation of barrier layers for threshold voltage control in CMOS device fabrication with high-k dielectrics |

| EP05732384.2AEP1766691B1 (en) | 2004-06-04 | 2005-03-30 | Selective implementation of barrier layers to achieve threshold voltage control in cmos device fabrication with high k dielectrics |

| PCT/US2005/010825WO2005122286A2 (en) | 2004-06-04 | 2005-03-30 | Selective implementation of barrier layers to achieve threshold voltage control in cmos device fabrication with high k dielectrics |

| TW094118832ATWI380378B (en) | 2004-06-04 | 2005-06-06 | Selective implementation of barrier layers to achieve threshold voltage control in cmos device fabrication with high-k dielectrics |

| US11/500,254US7452767B2 (en) | 2004-06-04 | 2006-08-07 | Selective implementation of barrier layers to achieve threshold voltage control in CMOS device fabrication with high k dielectrics |

| US12/211,530US7745278B2 (en) | 2004-06-04 | 2008-09-16 | Selective implementation of barrier layers to achieve threshold voltage control in CMOS device fabrication with high K dielectrics |

| US12/355,368US7928514B2 (en) | 2004-06-04 | 2009-01-16 | Selective implementation of barrier layers to achieve threshold voltage control in CMOS device fabrication with high-k dielectrics |

| US13/047,172US8193051B2 (en) | 2004-06-04 | 2011-03-14 | Selective implementation of barrier layers to achieve threshold voltage control in CMOS device fabrication with high-k dielectrics |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/863,830US7105889B2 (en) | 2004-06-04 | 2004-06-04 | Selective implementation of barrier layers to achieve threshold voltage control in CMOS device fabrication with high k dielectrics |

Related Child Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| US10/957,342Continuation-In-PartUS7479683B2 (en) | 2004-06-04 | 2004-10-01 | Selective implementation of barrier layers to achieve threshold voltage control in CMOS device fabrication with high-k dielectrics |

| US11/500,254DivisionUS7452767B2 (en) | 2004-06-04 | 2006-08-07 | Selective implementation of barrier layers to achieve threshold voltage control in CMOS device fabrication with high k dielectrics |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| US20050269634A1 US20050269634A1 (en) | 2005-12-08 |

| US7105889B2true US7105889B2 (en) | 2006-09-12 |

Family

ID=35446743

Family Applications (6)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| US10/863,830Expired - LifetimeUS7105889B2 (en) | 2004-06-04 | 2004-06-04 | Selective implementation of barrier layers to achieve threshold voltage control in CMOS device fabrication with high k dielectrics |

| US10/957,342Expired - Fee RelatedUS7479683B2 (en) | 2004-06-04 | 2004-10-01 | Selective implementation of barrier layers to achieve threshold voltage control in CMOS device fabrication with high-k dielectrics |

| US11/500,254Expired - LifetimeUS7452767B2 (en) | 2004-06-04 | 2006-08-07 | Selective implementation of barrier layers to achieve threshold voltage control in CMOS device fabrication with high k dielectrics |

| US12/211,530Expired - LifetimeUS7745278B2 (en) | 2004-06-04 | 2008-09-16 | Selective implementation of barrier layers to achieve threshold voltage control in CMOS device fabrication with high K dielectrics |

| US12/355,368Expired - LifetimeUS7928514B2 (en) | 2004-06-04 | 2009-01-16 | Selective implementation of barrier layers to achieve threshold voltage control in CMOS device fabrication with high-k dielectrics |

| US13/047,172Expired - LifetimeUS8193051B2 (en) | 2004-06-04 | 2011-03-14 | Selective implementation of barrier layers to achieve threshold voltage control in CMOS device fabrication with high-k dielectrics |

Family Applications After (5)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| US10/957,342Expired - Fee RelatedUS7479683B2 (en) | 2004-06-04 | 2004-10-01 | Selective implementation of barrier layers to achieve threshold voltage control in CMOS device fabrication with high-k dielectrics |

| US11/500,254Expired - LifetimeUS7452767B2 (en) | 2004-06-04 | 2006-08-07 | Selective implementation of barrier layers to achieve threshold voltage control in CMOS device fabrication with high k dielectrics |

| US12/211,530Expired - LifetimeUS7745278B2 (en) | 2004-06-04 | 2008-09-16 | Selective implementation of barrier layers to achieve threshold voltage control in CMOS device fabrication with high K dielectrics |

| US12/355,368Expired - LifetimeUS7928514B2 (en) | 2004-06-04 | 2009-01-16 | Selective implementation of barrier layers to achieve threshold voltage control in CMOS device fabrication with high-k dielectrics |

| US13/047,172Expired - LifetimeUS8193051B2 (en) | 2004-06-04 | 2011-03-14 | Selective implementation of barrier layers to achieve threshold voltage control in CMOS device fabrication with high-k dielectrics |

Country Status (7)

| Country | Link |

|---|---|

| US (6) | US7105889B2 (en) |

| EP (1) | EP1766691B1 (en) |

| JP (1) | JP4711444B2 (en) |

| KR (1) | KR100951227B1 (en) |

| CN (1) | CN101427386B (en) |

| TW (1) | TWI380378B (en) |

| WO (1) | WO2005122286A2 (en) |

Cited By (39)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20060030096A1 (en)* | 2004-08-06 | 2006-02-09 | Weimer Ronald A | Methods of enabling polysilicon gate electrodes for high-k gate dieletrics |

| US20060060929A1 (en)* | 2004-08-30 | 2006-03-23 | Gyoung-Ho Buh | Semiconductor transistors having surface insulation layers and methods of fabricating such transistors |

| US20060102968A1 (en)* | 2004-11-15 | 2006-05-18 | International Business Machines Corporation | Nitrogen-containing field effect transistor gate stack containing a threshold voltage control layer formed via deposition of a metal oxide |

| US20060228904A1 (en)* | 2005-04-07 | 2006-10-12 | Texas Instruments Incorporated | Protection of silicon from phosphoric acid using thick chemical oxide |

| WO2007050312A2 (en) | 2005-10-26 | 2007-05-03 | International Business Machines Corporation | Low threshold voltage semiconductor device with dual threshold voltage control means |

| US20070187774A1 (en)* | 2005-07-14 | 2007-08-16 | Matthias Goldbach | Manufacturing method for an integrated semiconductor structure and corresponding integrated semiconductor structure |

| US20070210354A1 (en)* | 2006-03-10 | 2007-09-13 | Renesas Technology Corp. | Semiconductor device and semiconductor device manufacturing method |

| US20070298560A1 (en)* | 2005-02-14 | 2007-12-27 | Kabushiki Kaisha Toshiba | Semiconductor Device |

| US20080038924A1 (en)* | 2006-08-08 | 2008-02-14 | Willy Rachmady | Highly-selective metal etchants |

| US20080264898A1 (en)* | 2007-04-27 | 2008-10-30 | International Business Machines Corporation | SELECTIVE ETCH OF TiW FOR CAPTURE PAD FORMATION |

| US20080274598A1 (en)* | 2007-03-19 | 2008-11-06 | Texas Instruments Inc. | Doped WGe to form dual metal gates |

| US20080318404A1 (en)* | 2004-09-13 | 2008-12-25 | Kabushiki Kaisha Toshiba | Semiconductor device and method for manufacturing the same |

| US20090108366A1 (en)* | 2007-10-30 | 2009-04-30 | Tze-Chiang Chen | Structure And Method To Fabricate Metal Gate High-K Devices |