US6504201B1 - Memory cell having a vertical transistor with buried source/drain and dual gates - Google Patents

Memory cell having a vertical transistor with buried source/drain and dual gatesDownload PDFInfo

- Publication number

- US6504201B1 US6504201B1US09/651,199US65119900AUS6504201B1US 6504201 B1US6504201 B1US 6504201B1US 65119900 AUS65119900 AUS 65119900AUS 6504201 B1US6504201 B1US 6504201B1

- Authority

- US

- United States

- Prior art keywords

- pillar

- source

- pillars

- word line

- substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/05—Making the transistor

- H10B12/053—Making the transistor the transistor being at least partially in a trench in the substrate

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/48—Data lines or contacts therefor

- H10B12/488—Word lines

Definitions

- the present inventionrelates generally to integrated circuits, and particularly, but not by way of limitation, to a dynamic random access memory (DRAM) having a memory cell with a vertical access transistor with buried dual gates, and having buried bit and word lines.

- DRAMdynamic random access memory

- DRAMsdynamic random access memories

- a DRAM memory celltypically includes an access field-effect transistor (FET) and a storage capacitor.

- FETaccess field-effect transistor

- the access FETallows the transfer of data charges to and from the storage capacitor during reading and writing operations.

- the data charges on the storage capacitorare periodically refreshed during a refresh operation.

- Memory densityis typically limited by a minimum lithographic feature size (F) that is imposed by lithographic processes used during fabrication.

- Flithographic feature size

- DRAMsdynamic random access memories

- Flithographic feature size

- DRAMsdynamic random access memories

- Increasing the data storage capacity of semiconductor memoriesrequires a reduction in the size of the access FET and storage capacitor of each memory cell.

- other factorssuch as subthreshold leakage currents and alpha-particle induced soft errors, require that larger storage capacitors be used.

- the present inventionprovides an integrated circuit including a pillar of semiconductor material that extends outwardly from a working surface of a substrate.

- the pillarhas a number of sides.

- a transistoris formed having a body region and first and second source/drain regions within the pillar.

- the transistorincludes first and second gates that are each associated with a side of the pillar.

- the inventionalso provides a memory device including an array of memory cells.

- Each cellincludes a transistor.

- Each transistorincludes a semiconductor pillar forming body and first and second source/drain regions.

- the transistoralso includes first and second gates disposed adjacent to opposing sides of the pillar.

- the memory devicealso includes a plurality of substantially parallel first word lines. Each first word line is disposed orthogonally to the bit lines in a trench between columns of the memory cells. Each first word line allows addressing of first gates of the transistors of the memory cells that are adjacent to the trench in which the first word line is disposed.

- the memory devicealso includes a plurality of substantially parallel second word lines. The second word lines are interdigitated with the first word lines.

- Each second word lineis disposed orthogonally to the bit lines in a trench between columns of the memory cells. Each second word line allows addressing of second gates of the transistors of the memory cells that are adjacent to the trench in which the second word line is disposed.

- a plurality of bit linesis provided, proximal to the substrate. The bit lines interconnect ones of the first source/drain regions of ones of the memory cells.

- the pillarsextend outwardly from an insulating portion of the substrate. In another embodiment, the pillars extend outwardly from a semiconductor portion of the substrate.

- the inventionalso provides a method of fabricating an integrated circuit.

- a substrateis provided, and a plurality of bit lines are formed on the substrate.

- a plurality of access transistorsare formed on each of the bit lines.

- Each access transistorincludes a first source/drain region shared by at least a portion of the bit line.

- Each access transistoralso includes a body region and second source/drain region formed vertically on the first source/drain region.

- a plurality of isolation trenchesare formed in the substrate, orthogonal to the bit lines. Each trench is located between access transistors on the orthogonal bit lines.

- a first word lineis formed in a first one of the trenches.

- the first word linecontrols conduction between first and second source/drain regions of access transistors that are adjacent to a first side of the first trench.

- a second word lineis formed in a second one of the trenches. The second word line controls conduction between first and second source/drain regions of access transistors that are adjacent to a first side of the second trench.

- the first word linealso controls conduction between first and second source/drain regions of access transistors that are adjacent to a second side of the first trench.

- the second word linealso controls conduction between first and second source/drain regions of access transistors that are adjacent to a second side of the second trench.

- first word lineis formed in the first trench, for controlling conduction between first and second source/drain regions of access transistors that are adjacent to a second side of the first trench.

- a second word lineis formed in the second trench, for controlling conduction between first and second source/drain regions of access transistors that are adjacent to a second side of the second trench.

- the inventionprovides high density integrated circuit structures and fabrication methods, such as for DRAM memory cell arrays and other semiconductor devices.

- Each memory cellcan be fabricated in a surface area that is approximately 4 F 2 , where F is a minimum lithographic feature size.

- Fis a minimum lithographic feature size.

- a common first word lineis shared by all of the access FETs that are located along both sides of the trench in which the first word line is located.

- a common second word lineis shared by all of the access FETs that are located along both sides of the trench in which the second word line is located.

- split word linesare provided in either or both trenches. The split word lines provide separate addressing of gate regions of access FETs on opposite sides of the trench.

- Each of the unitary and split word line embodimentscan be fabricated on a bulk semiconductor substrate, or on a semiconductor-on-insulator (SOI) substrate that results from using an SOI starting material, or by forming SOI regions during fabrication.

- SOI embodimentsprovide greater immunity to alpha-particle induced soft errors, allowing the use of smaller storage capacitors.

- FIG. 1is a schematic representation illustrating generally one embodiment of a semiconductor memory according to the invention.

- FIG. 2is a perspective view illustrating generally one embodiment of a portion of a memory according to the present invention.

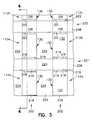

- FIG. 3is a plan view illustrating generally memory cells according to one embodiment of the invention as viewed from above the structures formed on the substrate.

- FIG. 4is a cross-sectional view taken along the cut line 4 — 4 of FIG. 3 .

- FIGS. 5A-Kdescribe generally various processing techniques of one embodiment of a method of fabricating memory cells according to the invention.

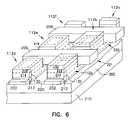

- FIG. 6is a perspective view illustrating generally another embodiment of a portion of a memory according to the present invention having a semiconductor-on-insulator (SOI) substrate.

- SOIsemiconductor-on-insulator

- FIGS. 7A-Cillustrate generally, by way of example, additional steps used to form SOI bars according to one embodiment of the invention.

- FIG. 8is a perspective view illustrating-generally another embodiment of a portion of a memory according to the present invention in which split gates are formed.

- FIG. 9is a plan view illustrating generally memory cells according to a split gate embodiment of the invention as viewed from above the structures formed on the substrate.

- FIG. 10is a cross-sectional view taken along the cut line 10 — 10 of FIG. 9 .

- FIG. 11is a perspective view illustrating generally another embodiment of a portion of a memory according to the present invention including split gates and a bulk semiconductor substrate.

- FIG. 12is a cross-sectional view taken along the cut line 12 — 12 of FIG. 11 .

- wafer and substrateare interchangeably used to refer generally to any structure on which integrated circuits are formed, and also to such structures during various stages of integrated circuit fabrication. Both terms include doped and undoped semiconductors, epitaxial layers of a semiconductor on a supporting semiconductor or insulating material, combinations of such layers, as well as other such structures that are known in the art.

- doped and undoped semiconductorsinclude doped and undoped semiconductors, epitaxial layers of a semiconductor on a supporting semiconductor or insulating material, combinations of such layers, as well as other such structures that are known in the art.

- FIG. 1is a schematic representation illustrating generally one embodiment of an integrated circuit 100 , such as a semiconductor memory device, incorporating an array of memory cells provided by the invention.

- circuit 100illustrates, by way of example but not by way of limitation, a dynamic random access memory (DRAM), but the invention also comprises other integrated circuits including any other semiconductor memory devices.

- circuit 100includes memory cell arrays 110 , such as 110 A and 110 B. Each array 110 includes M rows and N columns of memory cells 112 .

- each memory cellincludes a transfer device, such as n-channel cell access field-effect transistor (FET) 130 or any other transistor or switching device having more than one control terminal inputs. More particularly, access FET 130 includes first and second gate terminals for controlling conduction between its first and second source/drain terminals.

- FETfield-effect transistor

- Access FET 130is coupled at a second source/drain terminal to a storage node of a storage capacitor 132 .

- the other terminal of storage capacitor 132is coupled to a reference voltage such as a ground voltage VSS.

- Each of the M rowsincludes one of word lines WL 0 , WL 1 . . . WLm ⁇ 1, WLm coupled to the first gate terminals of access FETs 130 or to one of the control terminals of an equivalent switching device.

- Each of the M rowsalso includes one of word lines R 1 , R 2 , . . . , Rm ⁇ 1, Rm coupled to the second gate terminals of access FETs 130 in memory cells 112 .

- word lineincludes any interconnection line between gate terminals of access FETs 130 , or the control terminals of equivalent switching devices.

- Each of the N columnsincludes one of bit lines BL 0 , BL 1 . . . BLn ⁇ 1, BLn.

- Bit lines BL 0 -BLnare used to write to and read data from memory cells 112 .

- Word lines WL 0 -WLm and R 1 -Rmare used to activate access FETs 130 to access a particular row of memory cells 112 that is to be written or read.

- Addressing circuitryis also included.

- address buffer 114controls column decoders 118 , which also include sense amplifiers and input/output circuitry that is coupled to bit lines BL 0 -BLn.

- Address buffer 114also controls row decoders 116 .

- Row decoders 116 and column decoders 118selectably access memory cells 112 in response to address signals that are provided on address lines 120 during read and write operations.

- the address signalsare typically provided by an external controller such as a microprocessor or other memory controller.

- Each of memory cells 112has a substantially identical structure, and accordingly, only one memory cell 112 structure is described herein.

- circuit 100receives an address of a particular memory cell 112 at address buffer 114 .

- Address buffer 114identifies one of the word lines WL 0 -WLm of the particular memory cell 112 to row decoder 116 .

- Row decoder 116selectively activates the particular word line WL 0 -WLm to activate access FETs 130 of each memory cell 112 that is connected to the selected word line WL 0 -WLm.

- Column decoder 118selects the one of bit lines BL 0 -BLn of the particularly addressed memory cell 112 .

- data received by input/output circuitryis coupled to the one of bit lines BL 0 -BLn and through the access FET 130 to charge or discharge the storage capacitor 132 of the selected memory cell 112 to represent binary data.

- data stored in the selected memory cell 112is coupled to the one of bit lines BL 0 -BLn, amplified, and a corresponding voltage level is provided to the input/output circuits.

- each of the first and second gates of access FET 130is capable of controlling the conduction between its first and second source/drain terminals, as described below.

- parallel switching functionalitycan be effected between the first and second source/drain terminals of access FET 130 by independently operating the particular ones of word lines WL 0 -WLm and corresponding ones of word lines R 0 -Rm.

- word line WL 0 and word line R 0both of which are coupled to the same row of memory cells 112

- independently controlled inversion channelscan be formed in each corresponding access FET 130 by respective first and second gates for allowing conduction between the first and second source/drain regions.

- each of the first and second gates of access FET 130is capable of controlling the conduction between its first and second source/drain terminals, but the first and second gates of particular access FETs 130 are synchronously activated, rather than independently operated.

- first and second gates of particular access FETs 130are synchronously activated, rather than independently operated.

- word line WL 0 and word line R 0both of which are coupled to the same row of memory cells 112

- synchronously activated inversion channelscan be formed in each corresponding access FET 130 by respective first and second gates for allowing conduction between the first and second source/drain regions.

- synchronous activation and deactivation of the first and second gatesallows better control over the potential distributions in the access FET 130 when it is in a conductive state. Synchronous activation and deactivation can be used to obtain well-controlled fully depleted operating characteristics of access FET 130 .

- different activation voltagescan be applied to the first and second gates of the access FET 130 .

- different voltagescan be provided to synchronously activated word lines WL 0 and R 0 , thereby providing different activation voltages to the first and second gates of the access FET 130 to obtain particular desired operating characteristics.

- different deactivation voltagescan be applied to the first and second gates of the access FET 130 .

- different deactivation voltagescan be provided to synchronously deactivated word lines WL 0 and R 0 and corresponding first and second gates of access FETs 130 , in order to obtain particular desired operating characteristics.

- different activation and deactivation voltagescan be applied to independently operated word lines such as WL 0 and R 0 .

- FIG. 2is a perspective view illustrating generally one-embodiment of a portion of a memory according to the present invention.

- FIG. 2illustrates portions of six memory cells 112 a-f , including portions of vertically oriented access FETs 130 therein.

- Conductive segments of bit lines 202represent particular ones of bit lines BL 0 -BLn.

- Conductive segments of first word line 206represents any one of word lines WL 0 -WLm, which provide integrally formed first gates for access FETs 130 between which the particular first word line 206 is interposed.

- Conductive segments of second word line 208represents any one of word lines R 0 -Rm, which provide integrally formed second gates for access FETs 130 between which the particular second word line 208 is interposed.

- word lines WL 0 -WLm and R 0 -RMare alternatingly disposed (interdigitated) within the array 110 .

- the detailed description of memory cell 112 structurerefers only to memory cells 112 a-f , bit lines 202 , and respective first and second word lines 206 and 208 that are associated with memory cells 112 a-f . However, the following description similarly applies to all memory cells 112 and similar conductive lines in array 110 .

- vertically oriented access FETs 130are formed in semiconductor pillars that extend outwardly from an underlying substrate 210 .

- substrate 210includes bulk semiconductor starting material, semiconductor-on-insulator (SOI) starting material, or SOI material that is formed from a bulk semiconductor starting material during processing.

- SOIsemiconductor-on-insulator

- access FETs 130include an n+silicon layer formed on a bulk silicon substrate 210 to produce first source/drain regions 212 of access FETs 130 and integrally formed n++ conductively doped bit lines 202 defining a particular column of memory cells 112 .

- a p ⁇ silicon layeris formed on n+ first source/drain region 212 to form the body region 214 of access FET 130 , in which inversion channels may be capacitively generated at the sidewalls of the semiconductor pillar under the control of the first and second gates.

- a further n+ silicon layeris formed on p- body region 214 to produce second source/drain region 216 of access FET 130 :

- Storage capacitors 132are formed on the second/source drain regions 216 .

- Word lines WL 0 -WLm and R 0 -RMare alternatingly disposed (interdigitated) within the array 110 .

- first word line 206is interposed between semiconductor pillars of memory cell pairs 112 a-b and 112 d-e .

- Second word line 208is interposed between semiconductor pillars of memory cell pairs 112 b-c and 112 e-f .

- access FETs 130are formed on bit lines 202 in semiconductor pillars extending outwardly from substrate 210 and including body regions 214 , and first and second source drain regions 212 and 216 , respectively.

- bit lines 202contact bulk semiconductor substrate 210 .

- Isolation trenchesprovide isolation between access FETs 130 of adjacent memory cells 112 .

- Columns of memory cells 112are separated by a trench 220 that is subsequently filled with a suitable insulating material such as silicon dioxide.

- trench 220provides isolation between memory cells 112 a and 112 d and between memory cells 112 b and 112 e .

- Rows of memory cells 112are alternatingly separated by a trench 221 and 222 , each of which are separated from substrate 210 by an underlying insulating layer, described below, and separated from the body region 214 of access FETs 130 by a gate oxide, also described below.

- trench 221provides isolation between memory cells 112 a and 112 b and between memory cells 112 d and 112 e .

- trench 222provides isolation between memory cells 112 b and 112 c and memory cells 112 e and 112 f .

- Trenches 221 and 222extend substantially orthogonally to bit lines 202 .

- FIG. 3is a plan view illustrating generally memory cells 112 a-f as viewed from above the structures formed on substrate 210 .

- FIG. 3illustrates subsequently formed insulator such as oxide 224 , formed in trenches 220 to provide isolation between memory cells 112 .

- first word line 206is shared between first gates of access FETs 130 of memory cells 112 in adjacent rows, such as between memory cells 112 a-b and 112 d-e .

- First word line 206is also shared between first gates of other access FETs 130 that are in the same adjacent rows, but coupled to different bit lines 202 .

- First word line 206is located in-trench 221 that extends between the semiconductor pillars of memory cells 112 a and 112 b .

- First word line 206is separated by gate oxide 218 from the vertical sidewalls 219 of the semiconductor pillars on each side of trench 221 .

- Second word line 208is shared between second gates of access FETs 130 of memory cells 112 in adjacent rows, such as between memory cells 112 b-c and 112 e-f . Second word line 208 is also shared between second gates of other access FETs 130 that are in the same adjacent rows, but coupled to different bit lines 202 . Second word line 208 is located in trench 222 that extends between the semiconductor pillars of memory cells 112 b and 112 c . Second word line 208 is separated by gate oxide 218 from the vertical sidewalls 223 of the semiconductor pillars on each side of trench 222 .

- FIG. 4is a cross-sectional view taken along the cut line 4 — 4 of FIG. 3 .

- respective first and second word lines 206 and 208are buried below the active semiconductor surface 230 of the semiconductor pillar in the memory cells 112 .

- Active semiconductor surface 230represents an upper semiconductor portion of second source/drain region 216 .

- First and second word lines 206 and 208respectively, are isolated from adjacent semiconductor pillars by gate oxide 218 .

- First and second word lines 206 and 208respectively provide integrally formed first and second gate portions that are capacitively coupled to adjacent access FET 130 body regions 214 , such as for forming inversion channel regions therein.

- respective first and second word lines 206 and 208are formed of a refractory metal, such as tungsten or titanium.

- first and second word lines 206 and 208can be formed of n+ doped polysilicon.

- other suitable conductorscould also be used for first and second words lines 206 and 208 , respectively.

- Burying first and second word lines 206 and 208 below semiconductor surface 230provides additional space on the upper portion of memory cell 112 for formation of storage capacitors 132 .

- Increasing the area available for forming storage capacitor 132increases the possible obtainable capacitance value of storage capacitor 132 .

- storage capacitor 132is a stacked capacitor that is formed using any of the many capacitor structures and process sequences known in the art. Other techniques could also be used for implementing storage capacitor 132 .

- Contacts to the first and second word lines 206 and 208 , respectively,can be made outside of the memory array 110 .

- respective first and second word lines 206 and 208are shared between adjacent memory cells 112 .

- the row pitch of each cellmeasured from the centerline of first word line 206 to the centerline of second word line 208 , can be approximately 2 F, where F is a minimum lithographic feature size.

- Fcorresponds to the length and width presented by the surface of a minimum-sized semiconductor pillar in each memory cell 112 .

- the column pitch of each cell, measured between centerlines of bit lines 202can be approximately 2 F.

- the surface area of each memory cell 112can be approximately 4 F 2 .

- FIGS. 5A-Kdescribe generally various processing techniques of one embodiment of a method of fabricating memory cells 112 , such as shown in FIGS. 2-4, using bulk silicon processing techniques.

- a p-bulk silicon substrate 210 starting materialis used.

- An n++ and n+ silicon composite first source/drain layer 212is formed on substrate 210 , such as by ionimplantation, epitaxial growth, or a combination of such techniques.

- the more heavily conductively doped lower portion of the first/source drain layer 212also functions as the bit line 202 .

- the thickness of the n++ portion of first source/drain layer 212is that of the desired bit line 202 thickness, which can be approximately between 0.1 to 0.25 ⁇ m.

- the overall thickness of the first source/drain layer 212can be approximately between 0.2 to 0.5 ⁇ m.

- a body region layer 214 of p ⁇ siliconis formed, such as by epitaxial growth, to a thickness that can be about 0.4 ⁇ m.

- a second source/drain region layer 216 of n+ siliconis formed, such as by ion-implantation into body region layer 214 or by epitaxial growth on body region layer 214 , to a thickness that can be approximately between 0.2 and 0.5 ⁇ m.

- an SiO 2 thin pad oxide layer 512is formed on second source/drain region 216 , such as by chemical vapor deposition (CVD).

- pad oxide layer 512can be approximately 10 nm in thickness.

- a thin silicon nitride (Si 3 N 4 ) layer 514is formed on pad oxide layer 512 , such as by CVD.

- nitride layer 514 ofcan be approximately 100 nm in thickness.

- photoresistis applied and selectively exposed to provide a mask for the directional etching of trenches 220 , such as by reactive ion etching (RIE).

- RIEreactive ion etching

- the directional etchingresults in a plurality of column bars 516 containing the stack of nitride layer 514 , pad oxide layer 512 , second source/drain layer 216 , body region layer 214 , and first source/drain layer 212 .

- Trenches 220are etched to a depth that is sufficient to reach the surface 518 of substrate 210 , thereby providing separation between conductively doped bit lines 202 .

- Bars 516are oriented in the direction of bit lines 202 .

- bars 516have a surface line width of approximately one micron or less. The depth and width of each trench 220 can be approximately equal to the line width of bars 516 .

- Isolation material 224such as SiO 2 is deposited to fill the trenches 220 .

- the working surfaceis then planarized, such as by chemical mechanical polishing/planarization (CMP).

- FIG. 5Eillustrates the view of FIG. 5D after clockwise rotation by ninety degrees.

- a photoresist materialis applied and selectively exposed to provide a mask for the directional etching of trenches 221 and 222 , such as by reactive ion etching (RIE) of a plurality of row bars 532 that are disposed orthogonally to bit lines 202 .

- RIEreactive ion etching

- Forming trenches 221 and 222includes etching though stacked layers in the portions of bars 516 .

- Forming trenches 221 and 222also includes etching through the isolation material 224 disposed between bars 516 .

- trenches 221 and 222are etched through nitride layer 514 , pad oxide layer 512 , second source/drain layer 216 , body region layer 214 , and partially into first source/drain layer 212 .

- Trenches 221 and 222are etched into bars 516 to a depth of about 100 nm into first source/drain layer 212 , leaving intact an underlying bit line 202 portion of the first source/drain layer 212 .

- Trenches 221 and 222are also etched into the isolation material 224 between bars 516 .

- a nonselective dry etchis used to remove the isolation material 224 between bars 516 and also the pad oxide layer 512 , second source/drain layer 216 , body region layer 214 , and a portion of first source/drain layer 212 of bars 516 .

- the directional etching of trenches 221 and 222results in the formation of a plurality of row bars 532 that are orthogonal to column bars 516 .

- FIG. 5Fis a plan view illustrating generally the arrangement of parallel bars 516 , and trenches 220 interposed therebetween. Bars 532 are arranged orthogonally to bars 516 . Trenches 221 and 222 are interposed between ones of bars 532 . The resulting semiconductor pillars in the intersecting portions of bars 532 and 516 provide first and second source drain regions 212 and 216 , respectively, and body region 214 for access FETs 130 of memory cells 112 .

- a conformal silicon nitride layer 540is formed, such as by CVD.

- Nitride layer 540is directionally etched, such as by RIE, to leave resulting portions of nitride layer 540 only on sidewalls 219 of the bars 532 in trenches 221 and 222 .

- the thickness of nitride layer 540is about 20 mn.

- An oxide layer 542is formed, such as by thermal growth, at the base portions of trenches 221 and 222 . Oxide layer 542 insulates the underlying bit lines 202 from structures subsequently formed in trenches 221 and 222 . After forming oxide layer 542 , remaining portions of nitride layer 540 are removed.

- a gate oxide 218is formed on the exposed sidewalls 219 portions in trenches 221 and 222 of second source/drain region 216 , body region 214 , and first source/drain region 212 .

- gate oxide 218is a high-quality thin oxide layer that is thermally grown on the exposed sidewalls 219 of trenches 221 and 222 .

- a conductive layer 544is formed over the working surface of the wafer, including filling trenches 221 and 222 in which respective first and second word lines 206 and 208 will be formed.

- layer 544is formed by CVD of a refractory metal, such as tungsten.

- layer 544is formed by CVD of n+ polysilicon.

- first and second word lines 206 and 208are formed in respective trenches 221 and 222 .

- FIG. 5Killustrates one embodiment in which, an insulating layer 546 , such as SiO 2 , is formed on the working surface of the wafer, such as by CVD.

- the structure thus formedis then processed to fabricate a storage capacitor 132 on the working surface of the wafer, using known techniques, followed by conventional back end of line (BEOL) procedures.

- BEOLback end of line

- FIG. 6is a perspective view illustrating generally another embodiment of a portion of a memory according to the present invention, similar to that described with respect to FIG. 2 .

- SOI substrate 210 of FIG. 6is obtained using an SOI starting material.

- a bulk semiconductor starting materialis used, and an bars of SOI are formed during fabrication of circuit 100 , such that the semiconductor pillars, in which portions of access FETs 130 are formed, extend outwardly from an insulating portion 602 of substrate 210 .

- FIGS. 7A-Cillustrate generally, by way of example, additional steps used to form SOI bars during the fabrication steps described above with respect to FIGS. 5A-K, such that the semiconductor pillars, in which portions of access FETs 130 are formed, extend outwardly from an insulating portion 602 of substrate 210 , resulting in the structure illustrated in FIG. 6 .

- FIG. 7Athe processing steps described above with respect to FIGS. 5A-C are carried out, forming trenches 220 that are etched to a depth that is below the original surface 518 of substrate 210 , such as by approximately greater than or equal to 0.6 ⁇ m.

- a nitride layer 704is formed, such as by CVD.

- Nitride layer 704is directionally etched, such as by RIE, to remove nitride layer 704 from the base regions of trenches 220 . Portions of nitride layer 704 remain on the sidewall of trenches 220 to protect adjacent layers during subsequent etching and oxidation.

- an isotropic chemical etch of siliconis used to partially undercut bars 516 .

- hydrofluoric acid (HF) or a commercial etchant sold under the trade name CP 4a mixture of approximately 1 part (46% HF):1 part (CH 3 COOH):3 parts (HNO 3 )

- CP 4a mixture of approximately 1 part (46% HF):1 part (CH 3 COOH):3 parts (HNO 3 )

- the partial undercutting of bars 516 by isotropic etchingis timed to remove a volume of silicon that is sufficient to compensate for a subsequently formed volume of oxide, described below.

- the subsequent oxidation stepproduces a volume of oxide that is approximately twice that of the silicon consumed during oxidation.

- substrate 210is oxidized using a standard semiconductor processing furnace at a temperature of approximately 900 to 1,100 degrees Celsius.

- a wet oxidizing ambientis used in the furnace chamber to oxidize the exposed silicon regions in the lower portion of trenches 220 .

- Substrate 210is oxidized for a time period that is sufficient to form oxide insulating portion 602 that fully undercuts bars 516 .

- Insulating portion 602underlies both bars 516 and trenches 220 , and isolates the bit lines 202 and access FETs 130 formed on bit lines 202 from an underlying semiconductor portion of substrate 210 .

- Nitride layer 704is removed, and processing then continues as described above with respect to FIGS. 5D-K, resulting in the structure of FIG. 6 .

- bars 516are sufficiently narrow such that the oxidation step that undercuts bars 516 produces sufficient oxide to fill trenches 220 , resulting in a generally planar structure. This avoids the need for a separate step of depositing an oxide insulation material 224 described with respect to FIG. 5 D.

- the oxidation time perioddepends on the width of bars 516 and the effective width of bars 516 after the undercut etch step. Narrower bars 516 require shorter oxidation times. For example, for sub-0.25 micron technology, oxidation time is approximately 1 hour. In another embodiment, the etch step fully undercuts bars 516 before oxidation. This further reduces oxidation time.

- FIGS. 8-10illustrate generally another embodiment of a portion of a memory according to the present invention, similar to that described with respect to FIG. 6 .

- first and second word lines 206 and 208are each split into separate conductors.

- First word line 206is split into independently operable first word lines 206 a and 206 b , each disposed in trench 221 and electrically isolated from each other.

- Second word line 208is split into independently operable second word lines 208 a and 208 b , each disposed in trench 222 and electrically isolated from each other, such as by SiO 2 .

- First and second word lines 206 and 208can be formed of a refractory metal or n+ polysilicon or other suitable conductor, as described above.

- first word line 206 aextends in trench 221 adjacent to the vertical sidewalls 219 of the semiconductor pillars of in-line memory cells 112 a and 112 d , separated therefrom by gate oxide 218 .

- First word line 206 bextends in trench 221 adjacent to the vertical sidewalls 219 of the semiconductor pillars of in-line memory cells 112 b and 112 e , separated therefrom by gate oxide 218 .

- Second word line 208 aextends in trench 222 adjacent to the vertical sidewalls 219 of the semiconductor pillars of in-line memory cells 112 b and 112 e , separated therefrom by gate oxide 218 .

- Second word line 208 bextends in trench 222 adjacent to the vertical sidewalls 219 of the semiconductor pillars of in-line memory cells 112 c and 112 f.

- Operation of the access FET 130 of memory cell 112 bincludes operation of the first word line 206 b and second word line 208 a , as described above.

- a positive potentialis applied to either or both of first word line 206 b and second word line 208 a , as described above to turn on the access FET 130 of memory cell 112 b .

- first word line 206 bis not shared by the access FET 130 of memory cell 112 a , subthreshold leakage is not induced in the access FET 130 of memory cell 112 a during activation of first word line 206 b to operate the access FET 130 of memory cell 112 b .

- second word line 208 ais not shared by the access FET 130 of memory cell 112 c , subthreshold leakage in the access FET 130 of memory cell 112 c is not induced during activation of second word line 208 a to operate the access FET 130 of memory cell 112 b.

- split first word lines 206 a-b and split second word lines 208 a-bavoids the problem of sub-threshold conduction in access FETs 130 in one row while the memory cells 112 in the adjacent row are being addressed.

- Each memory cell 112is capable of being uniquely addressed by a combination of first word line 206 and second word line 208 voltages. These voltages need not appear on the first word line 206 and second word line 208 of adjacent rows of memory cells 112 .

- FIGS. 8-10can be fabricated by process steps similar to those described with respect to FIGS. 5A-C forming bars 516 separated by trenches 220 . This is followed by the process steps described with respect to FIGS. 7A-C follow, isolating bars 516 from an underlying semiconductor portion of substrate 210 by insulating portion 602 . This is followed by the process steps described with respect to FIGS. 5D-J forming a planar structure including a unitary conductor first word line 206 in first trench 221 and a unitary conductor second word line 208 in second trench 222 .

- Unitary conductor first word line 206 thus formedis split to form separate conductors 206 a-b .

- a refractory metal, n+ polysilicon, or other conductoris deposited as a conformal film that can have a thickness of less than or equal to approximately F/3, where F is the minimum feature size.

- the conformal filmis then directionally etched, thereby leaving resulting split conductor word lines 206 a-b adjacent to the vertical sidewall 219 , separated therefrom by gate oxide 218 .

- Second word line 208can be similarly split into separate conductors 208 a-b during the same deposition and directional etch steps.

- Splitting unitary conductor first and second word lines 206 and 208respectively, provides the resulting structures illustrated in FIGS. 8-10, but is not required to practice the invention. These steps can be omitted, such as to obtain the structures illustrated in FIGS. 2-4.

- FIGS. 11-12illustrate generally another embodiment of a portion of a memory according to the present invention, similar to that described with respect to FIGS. 8-10, but fabricating using a bulk silicon substrate 210 , as described with respect to FIGS. 2-4.

- the structures of FIGS. 11-12are fabricated by process steps similar to those described with respect to FIGS. 5A-C, forming bars 516 separated by trenches 220 .

- the process steps described with respect to FIGS. 7A-C followare omitted from this embodiment. Instead, this is followed by the process steps described with respect to FIGS. 5D-J forming a planar structure including a unitary conductor first word line 206 in first trench 221 and a unitary conductor second word line 208 in second trench 222 .

- the unitary conductor first and second word lines 206 and 208are then split as described above with respect to FIGS. 8-10.

- DRAMsdynamic random access memories

- the scope of the inventionincludes any other integrated circuit applications in which the above structures and fabrication methods are used.

- Each memory cellincludes a vertical access FET, formed on a bit line, and first and second gates integrally formed with respective first and second word lines that are buried in trenches that extend along opposite sides of the memory cell.

- Each memory cellcan be fabricated in a surface area that is approximately 4F 2 , where F is a minimum lithographic feature size.

- a common first word lineis shared by all of the access FETs that are located along both sides of the trench in which the first word line is located.

- a common second word lineis shared by all of the access FETs that are located along both sides of the trench in which the second word line is located.

- split word linesare provided in each trench, and the two split word lines provide separate addressing of gate regions of access FETs on opposite sides of the trench.

- Each of the unitary and split word line embodimentscan be fabricated on a bulk semiconductor substrate, or on a semiconductor-on-insulator (SOI) substrate that results from using an SOI starting material, or by forming SOI regions during fabrication.

- SOIsemiconductor-on-insulator

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Semiconductor Memories (AREA)

Abstract

Description

Claims (28)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/651,199US6504201B1 (en) | 1997-07-08 | 2000-08-30 | Memory cell having a vertical transistor with buried source/drain and dual gates |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US08/889,462US6150687A (en) | 1997-07-08 | 1997-07-08 | Memory cell having a vertical transistor with buried source/drain and dual gates |

| US09/651,199US6504201B1 (en) | 1997-07-08 | 2000-08-30 | Memory cell having a vertical transistor with buried source/drain and dual gates |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| US08/889,462ContinuationUS6150687A (en) | 1997-07-08 | 1997-07-08 | Memory cell having a vertical transistor with buried source/drain and dual gates |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| US6504201B1true US6504201B1 (en) | 2003-01-07 |

Family

ID=25395151

Family Applications (5)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| US08/889,462Expired - LifetimeUS6150687A (en) | 1997-07-08 | 1997-07-08 | Memory cell having a vertical transistor with buried source/drain and dual gates |

| US09/139,164Expired - Fee RelatedUS6350635B1 (en) | 1997-07-08 | 1998-08-24 | Memory cell having a vertical transistor with buried source/drain and dual gates |

| US09/596,266Expired - LifetimeUS6399979B1 (en) | 1997-07-08 | 2000-06-16 | Memory cell having a vertical transistor with buried source/drain and dual gates |

| US09/651,199Expired - LifetimeUS6504201B1 (en) | 1997-07-08 | 2000-08-30 | Memory cell having a vertical transistor with buried source/drain and dual gates |

| US10/162,942Expired - Fee RelatedUS6818937B2 (en) | 1997-07-08 | 2002-06-04 | Memory cell having a vertical transistor with buried source/drain and dual gates |

Family Applications Before (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| US08/889,462Expired - LifetimeUS6150687A (en) | 1997-07-08 | 1997-07-08 | Memory cell having a vertical transistor with buried source/drain and dual gates |

| US09/139,164Expired - Fee RelatedUS6350635B1 (en) | 1997-07-08 | 1998-08-24 | Memory cell having a vertical transistor with buried source/drain and dual gates |

| US09/596,266Expired - LifetimeUS6399979B1 (en) | 1997-07-08 | 2000-06-16 | Memory cell having a vertical transistor with buried source/drain and dual gates |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| US10/162,942Expired - Fee RelatedUS6818937B2 (en) | 1997-07-08 | 2002-06-04 | Memory cell having a vertical transistor with buried source/drain and dual gates |

Country Status (1)

| Country | Link |

|---|---|

| US (5) | US6150687A (en) |

Cited By (55)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6597203B2 (en) | 2001-03-14 | 2003-07-22 | Micron Technology, Inc. | CMOS gate array with vertical transistors |

| US20030227790A1 (en)* | 2002-06-06 | 2003-12-11 | Marr Ken W. | Temperature compensated T-RAM memory device and method |

| US20040042256A1 (en)* | 2002-08-29 | 2004-03-04 | Micron Technology, Inc. | Single transistor vertical memory gain cell |

| US20040041236A1 (en)* | 2002-08-29 | 2004-03-04 | Micron Technology, Inc. | Merged mos-bipolar capacitor memory cell |

| US20040041189A1 (en)* | 2002-08-29 | 2004-03-04 | Voshell Thomas W. | Random access memory device utilizing a vertically oriented select transistor |

| US20040052139A1 (en)* | 2002-06-21 | 2004-03-18 | Brown Kris K. | Memory cell and method for forming the same |

| US20040140509A1 (en)* | 2003-01-22 | 2004-07-22 | Ching-Yu Chang | Non-volatile memory and fabricating method thereof |

| US6804142B2 (en) | 2002-11-12 | 2004-10-12 | Micron Technology, Inc. | 6F2 3-transistor DRAM gain cell |

| US20050024936A1 (en)* | 2003-03-04 | 2005-02-03 | Micron Technology, Inc. | Vertical gain cell |

| US20050063233A1 (en)* | 2002-06-21 | 2005-03-24 | Brown Kris K. | Memory cell and method for forming the same |

| US20050073005A1 (en)* | 2003-10-07 | 2005-04-07 | International Business Machines Corporation | High-density split-gate finfet |

| US20060038259A1 (en)* | 2004-08-19 | 2006-02-23 | Patrick Thomas | Silicon pillars for vertical transistors |

| US20060043450A1 (en)* | 2004-09-02 | 2006-03-02 | Tang Sanh D | Vertical transistors |

| US20060113587A1 (en)* | 2004-11-30 | 2006-06-01 | Andreas Thies | Transistor array for semiconductor memory devices and method for fabricating a vertical channel transistor array |

| US20060160323A1 (en)* | 2005-01-14 | 2006-07-20 | Wells David H | Memory array buried digit line |

| US20060211194A1 (en)* | 2004-12-13 | 2006-09-21 | Haller Gordon A | Methods of reducing floating body effect |

| US7120046B1 (en) | 2005-05-13 | 2006-10-10 | Micron Technology, Inc. | Memory array with surrounding gate access transistors and capacitors with global and staggered local bit lines |

| US20060249776A1 (en)* | 2005-05-05 | 2006-11-09 | Manning H M | Memory cell, device, system and method for forming same |

| US20070018223A1 (en)* | 2005-07-25 | 2007-01-25 | Micron Technology Inc. | Dram including a vertical surround gate transistor |

| US20070018206A1 (en)* | 2005-07-06 | 2007-01-25 | Leonard Forbes | Surround gate access transistors with grown ultra-thin bodies |

| US20070048930A1 (en)* | 2005-09-01 | 2007-03-01 | Figura Thomas A | Peripheral gate stacks and recessed array gates |

| US20070045712A1 (en)* | 2005-09-01 | 2007-03-01 | Haller Gordon A | Memory cell layout and process flow |

| US20070045721A1 (en)* | 2005-08-29 | 2007-03-01 | Micron Technology, Inc. | Ultra-thin body vertical tunneling transistor |

| US20070051997A1 (en)* | 2005-08-31 | 2007-03-08 | Gordon Haller | Semiconductor memory device |

| US20070232007A1 (en)* | 2006-04-04 | 2007-10-04 | Micron Technology, Inc. | Nanowire transistor with surrounding gate |

| US20070228433A1 (en)* | 2006-04-04 | 2007-10-04 | Micron Technology, Inc. | DRAM with nanofin transistors |

| US20070228491A1 (en)* | 2006-04-04 | 2007-10-04 | Micron Technology, Inc. | Tunneling transistor with sublithographic channel |

| US20070231985A1 (en)* | 2006-04-04 | 2007-10-04 | Micron Technology, Inc. | Grown nanofin transistors |

| US20070231980A1 (en)* | 2006-04-04 | 2007-10-04 | Micron Technology, Inc. | Etched nanofin transistors |

| US7371627B1 (en) | 2005-05-13 | 2008-05-13 | Micron Technology, Inc. | Memory array with ultra-thin etched pillar surround gate access transistors and buried data/bit lines |

| US20080227255A1 (en)* | 2006-09-14 | 2008-09-18 | Micron Technology, Inc. | Methods of Forming Vertical Transistors |

| US7557032B2 (en) | 2005-09-01 | 2009-07-07 | Micron Technology, Inc. | Silicided recessed silicon |

| US20100090264A1 (en)* | 2008-10-10 | 2010-04-15 | Qimonda Ag | Interconnect structure for semiconductor devices |

| US20100176451A1 (en)* | 2009-01-09 | 2010-07-15 | Hoon Jeong | Semiconductor |

| US20110215391A1 (en)* | 2010-03-08 | 2011-09-08 | Elpida Memory, Inc. | Semiconductor device and method of manufacturing the same |

| US8274106B2 (en) | 2004-07-20 | 2012-09-25 | Micron Technology, Inc. | DRAM layout with vertical FETs and method of formation |

| US8329567B2 (en) | 2010-11-03 | 2012-12-11 | Micron Technology, Inc. | Methods of forming doped regions in semiconductor substrates |

| US8361856B2 (en) | 2010-11-01 | 2013-01-29 | Micron Technology, Inc. | Memory cells, arrays of memory cells, and methods of forming memory cells |

| US8362537B2 (en) | 2008-10-10 | 2013-01-29 | Qimonda Ag | Memory devices including semiconductor pillars |

| US8450175B2 (en) | 2011-02-22 | 2013-05-28 | Micron Technology, Inc. | Methods of forming a vertical transistor and at least a conductive line electrically coupled therewith |

| US8569831B2 (en) | 2011-05-27 | 2013-10-29 | Micron Technology, Inc. | Integrated circuit arrays and semiconductor constructions |

| US8878156B2 (en) | 2011-11-21 | 2014-11-04 | Avalanche Technology Inc. | Memory device having stitched arrays of 4 F2 memory cells |

| US20140346652A1 (en)* | 2013-05-24 | 2014-11-27 | Nanya Technology Corp. | Buried digitline (bdl) access device and memory array |

| US9006060B2 (en) | 2012-08-21 | 2015-04-14 | Micron Technology, Inc. | N-type field effect transistors, arrays comprising N-type vertically-oriented transistors, methods of forming an N-type field effect transistor, and methods of forming an array comprising vertically-oriented N-type transistors |

| US9029822B2 (en) | 2012-11-17 | 2015-05-12 | Avalanche Technology, Inc. | High density resistive memory having a vertical dual channel transistor |

| US9036391B2 (en) | 2012-03-06 | 2015-05-19 | Micron Technology, Inc. | Arrays of vertically-oriented transistors, memory arrays including vertically-oriented transistors, and memory cells |

| US9087897B1 (en) | 2014-01-31 | 2015-07-21 | International Business Machines Corporation | Semiconductor structures with pair(s) of vertical field effect transistors, each pair having a shared source/drain region and methods of forming the structures |

| US9111853B2 (en) | 2013-03-15 | 2015-08-18 | Micron Technology, Inc. | Methods of forming doped elements of semiconductor device structures |

| US9129896B2 (en)* | 2012-08-21 | 2015-09-08 | Micron Technology, Inc. | Arrays comprising vertically-oriented transistors, integrated circuitry comprising a conductive line buried in silicon-comprising semiconductor material, methods of forming a plurality of conductive lines buried in silicon-comprising semiconductor material, and methods of forming an array comprising vertically-oriented transistors |

| US9287271B2 (en) | 2011-08-23 | 2016-03-15 | Micron Technology, Inc. | Vertical transistor devices, memory arrays, and methods of forming vertical transistor devices |

| US9397094B2 (en) | 2014-09-25 | 2016-07-19 | International Business Machines Corporation | Semiconductor structure with an L-shaped bottom plate |

| US9478550B2 (en) | 2012-08-27 | 2016-10-25 | Micron Technology, Inc. | Arrays of vertically-oriented transistors, and memory arrays including vertically-oriented transistors |

| US10515801B2 (en) | 2007-06-04 | 2019-12-24 | Micron Technology, Inc. | Pitch multiplication using self-assembling materials |

| US11482277B2 (en) | 2020-11-04 | 2022-10-25 | Samsung Electronics Co., Ltd. | Integrated circuit device including a word line driving circuit |

| US12426237B2 (en) | 2022-06-23 | 2025-09-23 | Changxin Memory Technologies, Inc. | Semiconductor structure and method for forming same |

Families Citing this family (148)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6218237B1 (en) | 1996-01-03 | 2001-04-17 | Micron Technology, Inc. | Method of forming a capacitor |

| US6072209A (en) | 1997-07-08 | 2000-06-06 | Micro Technology, Inc. | Four F2 folded bit line DRAM cell structure having buried bit and word lines |

| US6150687A (en)* | 1997-07-08 | 2000-11-21 | Micron Technology, Inc. | Memory cell having a vertical transistor with buried source/drain and dual gates |

| US5907170A (en) | 1997-10-06 | 1999-05-25 | Micron Technology, Inc. | Circuit and method for an open bit line memory cell with a vertical transistor and trench plate trench capacitor |

| US6528837B2 (en) | 1997-10-06 | 2003-03-04 | Micron Technology, Inc. | Circuit and method for an open bit line memory cell with a vertical transistor and trench plate trench capacitor |

| US6066869A (en) | 1997-10-06 | 2000-05-23 | Micron Technology, Inc. | Circuit and method for a folded bit line memory cell with vertical transistor and trench capacitor |

| US6025225A (en) | 1998-01-22 | 2000-02-15 | Micron Technology, Inc. | Circuits with a trench capacitor having micro-roughened semiconductor surfaces and methods for forming the same |

| US6246083B1 (en) | 1998-02-24 | 2001-06-12 | Micron Technology, Inc. | Vertical gain cell and array for a dynamic random access memory |

| US6242775B1 (en) | 1998-02-24 | 2001-06-05 | Micron Technology, Inc. | Circuits and methods using vertical complementary transistors |

| US6097242A (en) | 1998-02-26 | 2000-08-01 | Micron Technology, Inc. | Threshold voltage compensation circuits for low voltage and low power CMOS integrated circuits |

| US5991225A (en) | 1998-02-27 | 1999-11-23 | Micron Technology, Inc. | Programmable memory address decode array with vertical transistors |

| US6124729A (en) | 1998-02-27 | 2000-09-26 | Micron Technology, Inc. | Field programmable logic arrays with vertical transistors |

| US6171891B1 (en)* | 1998-02-27 | 2001-01-09 | Taiwan Semiconductor Manufacturing Company | Method of manufacture of CMOS device using additional implant regions to enhance ESD performance |

| JPH11297856A (en) | 1998-04-16 | 1999-10-29 | Mitsubishi Electric Corp | Static semiconductor memory device |

| US6208164B1 (en) | 1998-08-04 | 2001-03-27 | Micron Technology, Inc. | Programmable logic array with vertical transistors |

| US6134175A (en) | 1998-08-04 | 2000-10-17 | Micron Technology, Inc. | Memory address decode array with vertical transistors |

| US6104068A (en)* | 1998-09-01 | 2000-08-15 | Micron Technology, Inc. | Structure and method for improved signal processing |

| US5977579A (en)* | 1998-12-03 | 1999-11-02 | Micron Technology, Inc. | Trench dram cell with vertical device and buried word lines |

| US7388289B1 (en)* | 1999-09-02 | 2008-06-17 | Micron Technology, Inc. | Local multilayered metallization |

| US6437389B1 (en)* | 2000-08-22 | 2002-08-20 | Micron Technology, Inc. | Vertical gate transistors in pass transistor programmable logic arrays |

| US6537870B1 (en)* | 2000-09-29 | 2003-03-25 | Infineon Technologies Ag | Method of forming an integrated circuit comprising a self aligned trench |

| US6472258B1 (en)* | 2000-11-13 | 2002-10-29 | International Business Machines Corporation | Double gate trench transistor |

| US6496034B2 (en) | 2001-02-09 | 2002-12-17 | Micron Technology, Inc. | Programmable logic arrays with ultra thin body transistors |

| US6424001B1 (en) | 2001-02-09 | 2002-07-23 | Micron Technology, Inc. | Flash memory with ultra thin vertical body transistors |

| US6377070B1 (en) | 2001-02-09 | 2002-04-23 | Micron Technology, Inc. | In-service programmable logic arrays with ultra thin vertical body transistors |

| US6448601B1 (en) | 2001-02-09 | 2002-09-10 | Micron Technology, Inc. | Memory address and decode circuits with ultra thin body transistors |

| US6566682B2 (en) | 2001-02-09 | 2003-05-20 | Micron Technology, Inc. | Programmable memory address and decode circuits with ultra thin vertical body transistors |

| US6559491B2 (en) | 2001-02-09 | 2003-05-06 | Micron Technology, Inc. | Folded bit line DRAM with ultra thin body transistors |

| US6531727B2 (en) | 2001-02-09 | 2003-03-11 | Micron Technology, Inc. | Open bit line DRAM with ultra thin body transistors |

| US6649476B2 (en) | 2001-02-15 | 2003-11-18 | Micron Technology, Inc. | Monotonic dynamic-static pseudo-NMOS logic circuit and method of forming a logic gate array |

| US6744094B2 (en)* | 2001-08-24 | 2004-06-01 | Micron Technology Inc. | Floating gate transistor with horizontal gate layers stacked next to vertical body |

| US8026161B2 (en) | 2001-08-30 | 2011-09-27 | Micron Technology, Inc. | Highly reliable amorphous high-K gate oxide ZrO2 |

| US7068544B2 (en) | 2001-08-30 | 2006-06-27 | Micron Technology, Inc. | Flash memory with low tunnel barrier interpoly insulators |

| US7067875B2 (en)* | 2001-09-20 | 2006-06-27 | Renesas Technology Corp. | Semiconductor integrated circuit device and its manufacturing method |

| WO2003036714A1 (en)* | 2001-10-24 | 2003-05-01 | Hitachi, Ltd D | Longitudinal misfet manufacturing method, longitudinal misfet, semiconductor storage device manufacturing method, and semiconductor storage device |

| US6800905B2 (en)* | 2001-12-14 | 2004-10-05 | International Business Machines Corporation | Implanted asymmetric doped polysilicon gate FinFET |

| US6953730B2 (en) | 2001-12-20 | 2005-10-11 | Micron Technology, Inc. | Low-temperature grown high quality ultra-thin CoTiO3 gate dielectrics |

| US20030151077A1 (en)* | 2002-02-13 | 2003-08-14 | Leo Mathew | Method of forming a vertical double gate semiconductor device and structure thereof |

| US6750487B2 (en)* | 2002-04-11 | 2004-06-15 | International Business Machines Corporation | Dual double gate transistor |

| US7589029B2 (en) | 2002-05-02 | 2009-09-15 | Micron Technology, Inc. | Atomic layer deposition and conversion |

| US7160577B2 (en) | 2002-05-02 | 2007-01-09 | Micron Technology, Inc. | Methods for atomic-layer deposition of aluminum oxides in integrated circuits |

| US6842369B2 (en) | 2002-05-07 | 2005-01-11 | Hewlett-Packard Development Company, L.P. | Intermesh memory device |

| US6970370B2 (en)* | 2002-06-21 | 2005-11-29 | Micron Technology, Inc. | Ferroelectric write once read only memory for archival storage |

| US7154140B2 (en) | 2002-06-21 | 2006-12-26 | Micron Technology, Inc. | Write once read only memory with large work function floating gates |

| US6996009B2 (en) | 2002-06-21 | 2006-02-07 | Micron Technology, Inc. | NOR flash memory cell with high storage density |

| US7193893B2 (en) | 2002-06-21 | 2007-03-20 | Micron Technology, Inc. | Write once read only memory employing floating gates |

| US6804136B2 (en)* | 2002-06-21 | 2004-10-12 | Micron Technology, Inc. | Write once read only memory employing charge trapping in insulators |

| CN100407427C (en) | 2002-06-21 | 2008-07-30 | 微米技术股份有限公司 | NROM memory element, memory array, related apparatus and method |

| US6888739B2 (en)* | 2002-06-21 | 2005-05-03 | Micron Technology Inc. | Nanocrystal write once read only memory for archival storage |

| US7221586B2 (en) | 2002-07-08 | 2007-05-22 | Micron Technology, Inc. | Memory utilizing oxide nanolaminates |

| US7847344B2 (en)* | 2002-07-08 | 2010-12-07 | Micron Technology, Inc. | Memory utilizing oxide-nitride nanolaminates |

| US7221017B2 (en) | 2002-07-08 | 2007-05-22 | Micron Technology, Inc. | Memory utilizing oxide-conductor nanolaminates |

| US7071043B2 (en)* | 2002-08-15 | 2006-07-04 | Micron Technology, Inc. | Methods of forming a field effect transistor having source/drain material over insulative material |

| US6794699B2 (en)* | 2002-08-29 | 2004-09-21 | Micron Technology Inc | Annular gate and technique for fabricating an annular gate |

| AU2003276212A1 (en)* | 2002-11-07 | 2004-06-07 | Ciba Specialty Chemicals Holding Inc. | Thickening agents comprising a crosslinked polymer powder |

| US7030436B2 (en)* | 2002-12-04 | 2006-04-18 | Micron Technology, Inc. | Embedded DRAM gain memory cell having MOS transistor body provided with a bi-polar transistor charge injecting means |

| US7339822B2 (en) | 2002-12-06 | 2008-03-04 | Sandisk Corporation | Current-limited latch |

| US7192892B2 (en) | 2003-03-04 | 2007-03-20 | Micron Technology, Inc. | Atomic layer deposited dielectric layers |

| US6967143B2 (en)* | 2003-04-30 | 2005-11-22 | Freescale Semiconductor, Inc. | Semiconductor fabrication process with asymmetrical conductive spacers |

| US7192876B2 (en)* | 2003-05-22 | 2007-03-20 | Freescale Semiconductor, Inc. | Transistor with independent gate structures |

| US6903967B2 (en)* | 2003-05-22 | 2005-06-07 | Freescale Semiconductor, Inc. | Memory with charge storage locations and adjacent gate structures |

| US7095075B2 (en) | 2003-07-01 | 2006-08-22 | Micron Technology, Inc. | Apparatus and method for split transistor memory having improved endurance |

| US7276754B2 (en)* | 2003-08-29 | 2007-10-02 | Micron Technology, Inc. | Annular gate and technique for fabricating an annular gate |

| US6844591B1 (en)* | 2003-09-17 | 2005-01-18 | Micron Technology, Inc. | Method of forming DRAM access transistors |

| US7098502B2 (en)* | 2003-11-10 | 2006-08-29 | Freescale Semiconductor, Inc. | Transistor having three electrically isolated electrodes and method of formation |

| US6831310B1 (en) | 2003-11-10 | 2004-12-14 | Freescale Semiconductor, Inc. | Integrated circuit having multiple memory types and method of formation |

| US6969656B2 (en)* | 2003-12-05 | 2005-11-29 | Freescale Semiconductor, Inc. | Method and circuit for multiplying signals with a transistor having more than one independent gate structure |

| US7050330B2 (en) | 2003-12-16 | 2006-05-23 | Micron Technology, Inc. | Multi-state NROM device |

| US7301804B2 (en) | 2003-12-16 | 2007-11-27 | Micro Technology, Inc. | NROM memory cell, memory array, related devices and methods |

| US7241654B2 (en) | 2003-12-17 | 2007-07-10 | Micron Technology, Inc. | Vertical NROM NAND flash memory array |

| US7148538B2 (en)* | 2003-12-17 | 2006-12-12 | Micron Technology, Inc. | Vertical NAND flash memory array |

| US7372091B2 (en)* | 2004-01-27 | 2008-05-13 | Micron Technology, Inc. | Selective epitaxy vertical integrated circuit components |

| US6878991B1 (en) | 2004-01-30 | 2005-04-12 | Micron Technology, Inc. | Vertical device 4F2 EEPROM memory |

| US7585731B2 (en)* | 2004-02-20 | 2009-09-08 | Renesas Technology Corp. | Semiconductor integrated circuit device and its manufacturing method |

| US7075146B2 (en) | 2004-02-24 | 2006-07-11 | Micron Technology, Inc. | 4F2 EEPROM NROM memory arrays with vertical devices |

| US7262089B2 (en)* | 2004-03-11 | 2007-08-28 | Micron Technology, Inc. | Methods of forming semiconductor structures |

| US7018876B2 (en)* | 2004-06-18 | 2006-03-28 | Freescale Semiconductor, Inc. | Transistor with vertical dielectric structure |

| US7271083B2 (en)* | 2004-07-22 | 2007-09-18 | Taiwan Semiconductor Manufacturing Company, Ltd. | One-transistor random access memory technology compatible with metal gate process |

| US7151294B2 (en)* | 2004-08-03 | 2006-12-19 | Micron Technology, Inc. | High density stepped, non-planar flash memory |

| US7081421B2 (en) | 2004-08-26 | 2006-07-25 | Micron Technology, Inc. | Lanthanide oxide dielectric layer |

| US7494939B2 (en) | 2004-08-31 | 2009-02-24 | Micron Technology, Inc. | Methods for forming a lanthanum-metal oxide dielectric layer |

| US7547945B2 (en) | 2004-09-01 | 2009-06-16 | Micron Technology, Inc. | Transistor devices, transistor structures and semiconductor constructions |

| US7457156B2 (en)* | 2004-09-02 | 2008-11-25 | Micron Technology, Inc. | NAND flash depletion cell structure |

| US7271052B1 (en) | 2004-09-02 | 2007-09-18 | Micron Technology, Inc. | Long retention time single transistor vertical memory gain cell |

| US7259415B1 (en) | 2004-09-02 | 2007-08-21 | Micron Technology, Inc. | Long retention time single transistor vertical memory gain cell |

| US7271433B1 (en) | 2004-09-02 | 2007-09-18 | Micron Technology, Inc. | High-density single transistor vertical memory gain cell |

| US7141838B1 (en)* | 2005-01-27 | 2006-11-28 | Spansion Llc | Buried word line memory integrated circuit system |

| US7326611B2 (en)* | 2005-02-03 | 2008-02-05 | Micron Technology, Inc. | DRAM arrays, vertical transistor structures and methods of forming transistor structures and DRAM arrays |

| US7374964B2 (en) | 2005-02-10 | 2008-05-20 | Micron Technology, Inc. | Atomic layer deposition of CeO2/Al2O3 films as gate dielectrics |

| US20060197140A1 (en)* | 2005-03-04 | 2006-09-07 | Freescale Semiconductor, Inc. | Vertical transistor NVM with body contact structure and method |

| US7244659B2 (en)* | 2005-03-10 | 2007-07-17 | Micron Technology, Inc. | Integrated circuits and methods of forming a field effect transistor |

| US7384849B2 (en)* | 2005-03-25 | 2008-06-10 | Micron Technology, Inc. | Methods of forming recessed access devices associated with semiconductor constructions |

| US7662729B2 (en) | 2005-04-28 | 2010-02-16 | Micron Technology, Inc. | Atomic layer deposition of a ruthenium layer to a lanthanide oxide dielectric layer |

| US7538389B2 (en) | 2005-06-08 | 2009-05-26 | Micron Technology, Inc. | Capacitorless DRAM on bulk silicon |

| US7679118B2 (en)* | 2005-06-13 | 2010-03-16 | Micron Technology, Inc. | Vertical transistor, memory cell, device, system and method of forming same |

| US7504685B2 (en)* | 2005-06-28 | 2009-03-17 | Micron Technology, Inc. | Oxide epitaxial isolation |

| KR100600044B1 (en)* | 2005-06-30 | 2006-07-13 | 주식회사 하이닉스반도체 | Method for manufacturing a semiconductor device having a recess gate |

| US7282401B2 (en) | 2005-07-08 | 2007-10-16 | Micron Technology, Inc. | Method and apparatus for a self-aligned recessed access device (RAD) transistor gate |

| US7927948B2 (en) | 2005-07-20 | 2011-04-19 | Micron Technology, Inc. | Devices with nanocrystals and methods of formation |

| US20070052012A1 (en)* | 2005-08-24 | 2007-03-08 | Micron Technology, Inc. | Vertical tunneling nano-wire transistor |

| US7867851B2 (en)* | 2005-08-30 | 2011-01-11 | Micron Technology, Inc. | Methods of forming field effect transistors on substrates |

| US8071476B2 (en) | 2005-08-31 | 2011-12-06 | Micron Technology, Inc. | Cobalt titanium oxide dielectric films |

| US7410910B2 (en) | 2005-08-31 | 2008-08-12 | Micron Technology, Inc. | Lanthanum aluminum oxynitride dielectric films |

| US7446372B2 (en)* | 2005-09-01 | 2008-11-04 | Micron Technology, Inc. | DRAM tunneling access transistor |

| US7867845B2 (en)* | 2005-09-01 | 2011-01-11 | Micron Technology, Inc. | Transistor gate forming methods and transistor structures |

| KR100673012B1 (en)* | 2005-09-02 | 2007-01-24 | 삼성전자주식회사 | A dynamic random access memory device having double gate type vertical channel transistors and a method of manufacturing the same |

| KR100697291B1 (en) | 2005-09-15 | 2007-03-20 | 삼성전자주식회사 | Nonvolatile Semiconductor Memory Device and Manufacturing Method Thereof |

| US7432122B2 (en)* | 2006-01-06 | 2008-10-07 | Freescale Semiconductor, Inc. | Electronic device and a process for forming the electronic device |

| US7700441B2 (en) | 2006-02-02 | 2010-04-20 | Micron Technology, Inc. | Methods of forming field effect transistors, methods of forming field effect transistor gates, methods of forming integrated circuitry comprising a transistor gate array and circuitry peripheral to the gate array, and methods of forming integrated circuitry comprising a transistor gate array including first gates and second grounded isolation gates |

| US7709402B2 (en) | 2006-02-16 | 2010-05-04 | Micron Technology, Inc. | Conductive layers for hafnium silicon oxynitride films |

| US8860174B2 (en)* | 2006-05-11 | 2014-10-14 | Micron Technology, Inc. | Recessed antifuse structures and methods of making the same |

| US20070262395A1 (en)* | 2006-05-11 | 2007-11-15 | Gibbons Jasper S | Memory cell access devices and methods of making the same |

| US8008144B2 (en) | 2006-05-11 | 2011-08-30 | Micron Technology, Inc. | Dual work function recessed access device and methods of forming |

| US7602001B2 (en) | 2006-07-17 | 2009-10-13 | Micron Technology, Inc. | Capacitorless one transistor DRAM cell, integrated circuitry comprising an array of capacitorless one transistor DRAM cells, and method of forming lines of capacitorless one transistor DRAM cells |

| US7772632B2 (en) | 2006-08-21 | 2010-08-10 | Micron Technology, Inc. | Memory arrays and methods of fabricating memory arrays |

| US7589995B2 (en) | 2006-09-07 | 2009-09-15 | Micron Technology, Inc. | One-transistor memory cell with bias gate |

| KR100881392B1 (en) | 2006-10-31 | 2009-02-05 | 주식회사 하이닉스반도체 | Semiconductor device with vertical transistor and manufacturing method thereof |

| US7872302B2 (en)* | 2007-01-15 | 2011-01-18 | Samsung Electronics Co., Ltd. | Semiconductor device having vertical transistor formed on an active pattern protruding from a substrate |

| US7800093B2 (en)* | 2007-02-01 | 2010-09-21 | Qimonda North America Corp. | Resistive memory including buried word lines |

| JP5460950B2 (en) | 2007-06-06 | 2014-04-02 | ピーエスフォー ルクスコ エスエイアールエル | Semiconductor device and manufacturing method thereof |

| US7759237B2 (en)* | 2007-06-28 | 2010-07-20 | Micron Technology, Inc. | Method of forming lutetium and lanthanum dielectric structures |

| JP5466816B2 (en)* | 2007-08-09 | 2014-04-09 | ピーエスフォー ルクスコ エスエイアールエル | Manufacturing method of vertical MOS transistor |

| US7943997B2 (en)* | 2008-04-17 | 2011-05-17 | International Business Machines Corporation | Fully-depleted low-body doping field effect transistor (FET) with reverse short channel effects (SCE) induced by self-aligned edge back-gate(s) |

| JP5701477B2 (en)* | 2008-09-18 | 2015-04-15 | マイクロンメモリジャパン株式会社 | Field effect transistor, memory cell, and method of manufacturing field effect transistor |

| KR101517390B1 (en)* | 2008-11-03 | 2015-05-04 | 삼성전자주식회사 | Vertical type semiconductor device and method for manufacturing the same |

| US7824986B2 (en) | 2008-11-05 | 2010-11-02 | Micron Technology, Inc. | Methods of forming a plurality of transistor gates, and methods of forming a plurality of transistor gates having at least two different work functions |

| KR101159900B1 (en)* | 2009-04-22 | 2012-06-25 | 에스케이하이닉스 주식회사 | Semiconductor device and method of fabricating the same |

| US8299519B2 (en)* | 2010-01-11 | 2012-10-30 | International Business Machines Corporation | Read transistor for single poly non-volatile memory using body contacted SOI device |

| US8467220B2 (en)* | 2010-01-14 | 2013-06-18 | Jai Hoon Sim | DRAM device and manufacturing method thereof |

| DE112011102837B4 (en)* | 2010-08-27 | 2021-03-11 | Semiconductor Energy Laboratory Co., Ltd. | Memory device and semiconductor device with double gate and oxide semiconductor |

| US8921899B2 (en) | 2010-11-19 | 2014-12-30 | Micron Technology, Inc. | Double gated 4F2 dram CHC cell and methods of fabricating the same |

| TWI415247B (en)* | 2010-12-15 | 2013-11-11 | Powerchip Technology Corp | Dynamic random access memory cell and array having vertical channel transistor |

| US9401436B2 (en) | 2011-05-05 | 2016-07-26 | Qualcomm Incorporated | Multiple control transcap variable capacitor |

| TWI499006B (en)* | 2011-10-07 | 2015-09-01 | Etron Technology Inc | Dynamic memory structure |

| KR101906946B1 (en) | 2011-12-02 | 2018-10-12 | 삼성전자주식회사 | High density semiconductor memory device |

| KR20130065264A (en)* | 2011-12-09 | 2013-06-19 | 에스케이하이닉스 주식회사 | Method for forming buried bitline, semiconductor device having buried bitline and fabricating the same |

| US9312257B2 (en) | 2012-02-29 | 2016-04-12 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| KR20130103942A (en) | 2012-03-12 | 2013-09-25 | 에스케이하이닉스 주식회사 | Semiconductor device having junctionless vertical gate transistor and method for manufacturing the same |

| US9281065B2 (en) | 2014-08-11 | 2016-03-08 | Empire Technology Development Llc | Low-power nonvolatile memory cells with select gates |

| US10388564B2 (en) | 2016-01-12 | 2019-08-20 | Micron Technology, Inc. | Method for fabricating a memory device having two contacts |

| SG10201701689UA (en) | 2016-03-18 | 2017-10-30 | Semiconductor Energy Lab | Semiconductor device, semiconductor wafer, and electronic device |

| US10002795B1 (en) | 2017-04-12 | 2018-06-19 | International Business Machines Corporation | Method and structure for forming vertical transistors with shared gates and separate gates |

| US10332874B2 (en) | 2017-05-03 | 2019-06-25 | International Business Machines Corporation | Indirect readout FET |

| US10522686B2 (en) | 2017-09-26 | 2019-12-31 | International Business Machines Corporation | Vertical thin film transistor |

| KR101950146B1 (en)* | 2018-08-23 | 2019-02-19 | 에스케이하이닉스 주식회사 | Semiconductor device having junctionless vertical gate transistor and method for manufacturing the same |

| US11107827B2 (en) | 2019-02-28 | 2021-08-31 | International Business Machines Corporation | Integration of split gate metal-oxide-nitride-oxide-semiconductor memory with vertical FET |

| CN112885832B (en)* | 2019-11-29 | 2024-07-16 | 长鑫存储技术有限公司 | Semiconductor structure and manufacturing method thereof |

| CN117337027A (en)* | 2022-06-23 | 2024-01-02 | 长鑫存储技术有限公司 | Semiconductor structures and methods of forming them |

Citations (124)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3931617A (en) | 1974-10-07 | 1976-01-06 | Signetics Corporation | Collector-up dynamic memory cell |

| US4020364A (en) | 1974-09-28 | 1977-04-26 | U.S. Philips Corporation | Resistance read amplifier |

| US4051354A (en) | 1975-07-03 | 1977-09-27 | Texas Instruments Incorporated | Fault-tolerant cell addressable array |

| US4252579A (en) | 1979-05-07 | 1981-02-24 | International Business Machines Corporation | Method for making single electrode U-MOSFET random access memory utilizing reactive ion etching and polycrystalline deposition |

| US4604162A (en) | 1983-06-13 | 1986-08-05 | Ncr Corporation | Formation and planarization of silicon-on-insulator structures |

| US4630088A (en) | 1984-09-11 | 1986-12-16 | Kabushiki Kaisha Toshiba | MOS dynamic ram |

| US4663831A (en) | 1985-10-08 | 1987-05-12 | Motorola, Inc. | Method of forming transistors with poly-sidewall contacts utilizing deposition of polycrystalline and insulating layers combined with selective etching and oxidation of said layers |

| US4673962A (en) | 1985-03-21 | 1987-06-16 | Texas Instruments Incorporated | Vertical DRAM cell and method |

| US4677589A (en) | 1985-07-26 | 1987-06-30 | Advanced Micro Devices, Inc. | Dynamic random access memory cell having a charge amplifier |

| US4701423A (en) | 1985-12-20 | 1987-10-20 | Ncr Corporation | Totally self-aligned CMOS process |

| US4716314A (en) | 1974-10-09 | 1987-12-29 | U.S. Philips Corporation | Integrated circuit |

| US4761768A (en) | 1985-03-04 | 1988-08-02 | Lattice Semiconductor Corporation | Programmable logic device |

| US4766569A (en) | 1985-03-04 | 1988-08-23 | Lattice Semiconductor Corporation | Programmable logic array |

| US4845537A (en) | 1986-12-01 | 1989-07-04 | Mitsubishi Denki Kabushiki Kaisha | Vertical type MOS transistor and method of formation thereof |

| US4906590A (en) | 1988-05-09 | 1990-03-06 | Mitsubishi Denki Kabushiki Kaisha | Method of forming a trench capacitor on a semiconductor substrate |

| US4920065A (en) | 1988-10-31 | 1990-04-24 | International Business Machines Corporation | Method of making ultra dense dram cells |

| US4929988A (en) | 1987-08-25 | 1990-05-29 | Kabushiki Kaisha Toshiba | Non-volatile semiconductor memory device and method of the manufacture thereof |

| US4949138A (en) | 1987-10-27 | 1990-08-14 | Texas Instruments Incorporated | Semiconductor integrated circuit device |

| US4958318A (en) | 1988-07-08 | 1990-09-18 | Eliyahou Harari | Sidewall capacitor DRAM cell |

| US4965651A (en) | 1973-02-01 | 1990-10-23 | U.S. Philips Corporation | CMOS logic array layout |

| US4987089A (en) | 1990-07-23 | 1991-01-22 | Micron Technology, Inc. | BiCMOS process and process for forming bipolar transistors on wafers also containing FETs |

| US5001526A (en) | 1987-11-10 | 1991-03-19 | Fujitsu Limited | Dram cell formed on an insulating layer having a buried semiconductor pillar structure and a manufacturing method thereof |

| US5006909A (en) | 1989-10-30 | 1991-04-09 | Motorola, Inc. | Dram with a vertical capacitor and transistor |

| US5010386A (en) | 1989-12-26 | 1991-04-23 | Texas Instruments Incorporated | Insulator separated vertical CMOS |

| US5017504A (en) | 1986-12-01 | 1991-05-21 | Mitsubishi Denki Kabushiki Kaisha | Vertical type MOS transistor and method of formation thereof |

| US5021355A (en) | 1989-05-22 | 1991-06-04 | International Business Machines Corporation | Method of fabricating cross-point lightly-doped drain-source trench transistor |

| US5028977A (en) | 1989-06-16 | 1991-07-02 | Massachusetts Institute Of Technology | Merged bipolar and insulated gate transistors |

| US5057896A (en) | 1988-05-28 | 1991-10-15 | Fujitsu Limited | Semiconductor device and method of producing same |

| US5072269A (en) | 1988-03-15 | 1991-12-10 | Kabushiki Kaisha Toshiba | Dynamic ram and method of manufacturing the same |

| US5083047A (en) | 1989-10-26 | 1992-01-21 | Kabushiki Kaisha Toshiba | Precharged-type logic circuit having dummy precharge line |

| US5087581A (en) | 1990-10-31 | 1992-02-11 | Texas Instruments Incorporated | Method of forming vertical FET device with low gate to source overlap capacitance |

| US5102817A (en) | 1985-03-21 | 1992-04-07 | Texas Instruments Incorporated | Vertical DRAM cell and method |