US20150214331A1 - Replacement metal gate including dielectric gate material - Google Patents

Replacement metal gate including dielectric gate materialDownload PDFInfo

- Publication number

- US20150214331A1 US20150214331A1US14/168,112US201414168112AUS2015214331A1US 20150214331 A1US20150214331 A1US 20150214331A1US 201414168112 AUS201414168112 AUS 201414168112AUS 2015214331 A1US2015214331 A1US 2015214331A1

- Authority

- US

- United States

- Prior art keywords

- layer

- dummy gate

- gate

- elements

- etch stop

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Abandoned

Links

- 239000000463materialSubstances0.000titleclaimsabstractdescription33

- 229910052751metalInorganic materials0.000titleclaimsdescription33

- 239000002184metalSubstances0.000titleclaimsdescription33

- 239000004065semiconductorSubstances0.000claimsabstractdescription74

- 125000006850spacer groupChemical group0.000claimsabstractdescription68

- 239000000758substrateSubstances0.000claimsabstractdescription35

- 230000015572biosynthetic processEffects0.000claimsabstractdescription24

- 239000003989dielectric materialSubstances0.000claimsabstractdescription14

- 238000004519manufacturing processMethods0.000claimsabstractdescription9

- 238000000034methodMethods0.000claimsdescription103

- 238000005530etchingMethods0.000claimsdescription37

- 229920002120photoresistant polymerPolymers0.000claimsdescription17

- VYPSYNLAJGMNEJ-UHFFFAOYSA-NSilicium dioxideChemical compoundO=[Si]=OVYPSYNLAJGMNEJ-UHFFFAOYSA-N0.000claimsdescription16

- 238000000059patterningMethods0.000claimsdescription15

- 238000000151depositionMethods0.000claimsdescription12

- 238000001020plasma etchingMethods0.000claimsdescription10

- 229910052580B4CInorganic materials0.000claimsdescription9

- IJGRMHOSHXDMSA-UHFFFAOYSA-NAtomic nitrogenChemical compoundN#NIJGRMHOSHXDMSA-UHFFFAOYSA-N0.000claimsdescription6

- INAHAJYZKVIDIZ-UHFFFAOYSA-Nboron carbideChemical compoundB12B3B4C32B41INAHAJYZKVIDIZ-UHFFFAOYSA-N0.000claimsdescription6

- OKTJSMMVPCPJKN-UHFFFAOYSA-NCarbonChemical compound[C]OKTJSMMVPCPJKN-UHFFFAOYSA-N0.000claimsdescription5

- 239000000377silicon dioxideSubstances0.000claimsdescription5

- 229910052799carbonInorganic materials0.000claimsdescription4

- CFOAUMXQOCBWNJ-UHFFFAOYSA-N[B].[Si]Chemical compound[B].[Si]CFOAUMXQOCBWNJ-UHFFFAOYSA-N0.000claimsdescription3

- 229910052757nitrogenInorganic materials0.000claimsdescription3

- 235000012239silicon dioxideNutrition0.000claimsdescription3

- 239000010410layerSubstances0.000claims54

- 239000012044organic layerSubstances0.000claims1

- 239000011800void materialSubstances0.000claims1

- 229910052814silicon oxideInorganic materials0.000description6

- 229910052581Si3N4Inorganic materials0.000description5

- 238000010586diagramMethods0.000description5

- 238000005429filling processMethods0.000description5

- HQVNEWCFYHHQES-UHFFFAOYSA-Nsilicon nitrideChemical compoundN12[Si]34N5[Si]62N3[Si]51N64HQVNEWCFYHHQES-UHFFFAOYSA-N0.000description5

- 239000006117anti-reflective coatingSubstances0.000description4

- 238000000231atomic layer depositionMethods0.000description4

- 238000005229chemical vapour depositionMethods0.000description4

- 230000008021depositionEffects0.000description4

- 239000010955niobiumSubstances0.000description4

- 229910021420polycrystalline siliconInorganic materials0.000description4

- 229920005591polysiliconPolymers0.000description4

- 239000010936titaniumSubstances0.000description4

- -1SiB:C(N))Chemical compound0.000description3

- XUIMIQQOPSSXEZ-UHFFFAOYSA-NSiliconChemical compound[Si]XUIMIQQOPSSXEZ-UHFFFAOYSA-N0.000description3

- 229910021417amorphous siliconInorganic materials0.000description3

- 238000012986modificationMethods0.000description3

- 230000004048modificationEffects0.000description3

- 229910052710siliconInorganic materials0.000description3

- 239000010703siliconSubstances0.000description3

- 238000001039wet etchingMethods0.000description3

- RTAQQCXQSZGOHL-UHFFFAOYSA-NTitaniumChemical compound[Ti]RTAQQCXQSZGOHL-UHFFFAOYSA-N0.000description2

- NRTOMJZYCJJWKI-UHFFFAOYSA-NTitanium nitrideChemical compound[Ti]#NNRTOMJZYCJJWKI-UHFFFAOYSA-N0.000description2

- 229910052782aluminiumInorganic materials0.000description2

- XAGFODPZIPBFFR-UHFFFAOYSA-NaluminiumChemical compound[Al]XAGFODPZIPBFFR-UHFFFAOYSA-N0.000description2

- IVHJCRXBQPGLOV-UHFFFAOYSA-NazanylidynetungstenChemical compound[W]#NIVHJCRXBQPGLOV-UHFFFAOYSA-N0.000description2

- 239000002019doping agentSubstances0.000description2

- 239000007769metal materialSubstances0.000description2

- 229910052758niobiumInorganic materials0.000description2

- GUCVJGMIXFAOAE-UHFFFAOYSA-Nniobium atomChemical compound[Nb]GUCVJGMIXFAOAE-UHFFFAOYSA-N0.000description2

- 230000003287optical effectEffects0.000description2

- 229910052702rheniumInorganic materials0.000description2

- WUAPFZMCVAUBPE-UHFFFAOYSA-Nrhenium atomChemical compound[Re]WUAPFZMCVAUBPE-UHFFFAOYSA-N0.000description2

- 239000000126substanceSubstances0.000description2

- 229910052715tantalumInorganic materials0.000description2

- GUVRBAGPIYLISA-UHFFFAOYSA-Ntantalum atomChemical compound[Ta]GUVRBAGPIYLISA-UHFFFAOYSA-N0.000description2

- MZLGASXMSKOWSE-UHFFFAOYSA-Ntantalum nitrideChemical compound[Ta]#NMZLGASXMSKOWSE-UHFFFAOYSA-N0.000description2

- 229910052719titaniumInorganic materials0.000description2

- WFKWXMTUELFFGS-UHFFFAOYSA-NtungstenChemical compound[W]WFKWXMTUELFFGS-UHFFFAOYSA-N0.000description2

- 229910052721tungstenInorganic materials0.000description2

- 239000010937tungstenSubstances0.000description2

- KRHYYFGTRYWZRS-UHFFFAOYSA-NFluoraneChemical compoundFKRHYYFGTRYWZRS-UHFFFAOYSA-N0.000description1

- OAICVXFJPJFONN-UHFFFAOYSA-NPhosphorusChemical compound[P]OAICVXFJPJFONN-UHFFFAOYSA-N0.000description1

- 229910003481amorphous carbonInorganic materials0.000description1

- 229910002090carbon oxideInorganic materials0.000description1

- 238000004140cleaningMethods0.000description1

- 238000001312dry etchingMethods0.000description1

- 229910052732germaniumInorganic materials0.000description1

- GNPVGFCGXDBREM-UHFFFAOYSA-Ngermanium atomChemical compound[Ge]GNPVGFCGXDBREM-UHFFFAOYSA-N0.000description1

- CJNBYAVZURUTKZ-UHFFFAOYSA-Nhafnium(iv) oxideChemical compoundO=[Hf]=OCJNBYAVZURUTKZ-UHFFFAOYSA-N0.000description1

- 238000001459lithographyMethods0.000description1

- 239000002070nanowireSubstances0.000description1

- 229910052698phosphorusInorganic materials0.000description1

- 239000011574phosphorusSubstances0.000description1

- 238000005389semiconductor device fabricationMethods0.000description1

- 239000002210silicon-based materialSubstances0.000description1

- 238000009966trimmingMethods0.000description1

Images

Classifications

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/01—Manufacture or treatment

- H10D64/017—Manufacture or treatment using dummy gates in processes wherein at least parts of the final gates are self-aligned to the dummy gates, i.e. replacement gate processes

- H01L29/66545—

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/02164—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material being a silicon oxide, e.g. SiO2

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/28008—Making conductor-insulator-semiconductor electrodes

- H01L21/28017—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon

- H01L21/28158—Making the insulator

- H01L21/28238—Making the insulator with sacrificial oxide

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/3065—Plasma etching; Reactive-ion etching

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/31051—Planarisation of the insulating layers

- H01L21/31053—Planarisation of the insulating layers involving a dielectric removal step

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31105—Etching inorganic layers

- H01L21/31111—Etching inorganic layers by chemical means

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31105—Etching inorganic layers

- H01L21/31111—Etching inorganic layers by chemical means

- H01L21/31116—Etching inorganic layers by chemical means by dry-etching

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31144—Etching the insulating layers by chemical or physical means using masks

- H01L21/823431—

- H01L21/823437—

- H01L21/823468—

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/0223—Manufacture or treatment of FETs having insulated gates [IGFET] having source and drain regions or source and drain extensions self-aligned to sides of the gate

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/024—Manufacture or treatment of FETs having insulated gates [IGFET] of fin field-effect transistors [FinFET]

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/62—Fin field-effect transistors [FinFET]

- H10D30/6211—Fin field-effect transistors [FinFET] having fin-shaped semiconductor bodies integral with the bulk semiconductor substrates

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/62—Fin field-effect transistors [FinFET]

- H10D30/6215—Fin field-effect transistors [FinFET] having multiple independently-addressable gate electrodes

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/62—Fin field-effect transistors [FinFET]

- H10D30/6219—Fin field-effect transistors [FinFET] characterised by the source or drain electrodes

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/01—Manufacture or treatment

- H10D64/021—Manufacture or treatment using multiple gate spacer layers, e.g. bilayered sidewall spacers

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/20—Electrodes characterised by their shapes, relative sizes or dispositions

- H10D64/23—Electrodes carrying the current to be rectified, amplified, oscillated or switched, e.g. sources, drains, anodes or cathodes

- H10D64/251—Source or drain electrodes for field-effect devices

- H10D64/258—Source or drain electrodes for field-effect devices characterised by the relative positions of the source or drain electrodes with respect to the gate electrode

- H10D64/259—Source or drain electrodes being self-aligned with the gate electrode and having bottom surfaces higher than the interface between the channel and the gate dielectric

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/60—Electrodes characterised by their materials

- H10D64/66—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes

- H10D64/667—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes the conductor comprising a layer of alloy material, compound material or organic material contacting the insulator, e.g. TiN workfunction layers

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/60—Electrodes characterised by their materials

- H10D64/66—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes

- H10D64/68—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/013—Manufacturing their source or drain regions, e.g. silicided source or drain regions

- H10D84/0133—Manufacturing common source or drain regions between multiple IGFETs

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0135—Manufacturing their gate conductors

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0147—Manufacturing their gate sidewall spacers

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0151—Manufacturing their isolation regions

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0158—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs the components including FinFETs

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/02—Manufacture or treatment characterised by using material-based technologies

- H10D84/03—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology

- H10D84/038—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology using silicon technology, e.g. SiGe

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/80—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs

- H10D84/82—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs of only field-effect components

- H10D84/83—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs of only field-effect components of only insulated-gate FETs [IGFET]

- H10D84/834—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs of only field-effect components of only insulated-gate FETs [IGFET] comprising FinFETs

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/01—Manufacture or treatment

- H10D86/011—Manufacture or treatment comprising FinFETs

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/201—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates the substrates comprising an insulating layer on a semiconductor body, e.g. SOI

- H10D86/215—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates the substrates comprising an insulating layer on a semiconductor body, e.g. SOI comprising FinFETs

Definitions

- the present inventionrelates to semiconductor device fabrication, and in particular, to a replacement metal gate process.

- a replacement metal gate (RMG) processi.e., a gate last process, has been traditionally used in semiconductor fabrications processes to form a semiconductor device including one or more gate elements 102 that wrap around on one or more semiconductor fins 104 .

- the gate elements 102typically extend in a direction perpendicular to the direction of the semiconductor fins 104 as illustrated in FIG. 1 .

- the RMG processutilizes a dummy gate element formed from amorphous silicon (a-Si) or polysilicon (PC), which is ultimately replaced with a metal gate element as understood by those ordinarily skilled in the art.

- the silicon material of the dummy gate elementmay be exposed when recessing the spacers formed on the sidewalls of the dummy gate element. Consequently, epitaxial material may be inadvertently grown on the exposed silicon of the dummy gate element which may result in a short between the epitaxially grown source/drain regions and the epitaxial material grown on the gate element.

- a method of fabricating a semiconductor devicecomprises forming at least one semiconductor fin on a semiconductor substrate.

- a plurality of gate formation layersis formed on an etch stop layer that is formed on one or more of the semiconductor fins.

- the plurality of gate formation layersinclude a dummy gate layer formed from a dielectric material.

- the plurality of gate formation layersis patterned to form a plurality of dummy gate elements on the etch stop layer. Each dummy gate element is formed from the dielectric material.

- a spacer layer formed on the dummy gate elementsis etched to form a spacer on each sidewall of dummy gate elements.

- a portion of the etch stop layer located between each dummy gate elementis etched to expose a portion the semiconductor fin.

- a semiconductor materialis epitaxially grown from the exposed portion of the semiconductor fin to form source/drain regions.

- a method of fabricating a semiconductor devicecomprises forming at least one semiconductor fin on a semiconductor substrate.

- the at least one semiconductor finincludes an etch stop layer formed on an upper surface thereof.

- the methodfurther comprises forming a plurality of dummy gate elements on the etch stop layer.

- Each dummy gate elementis formed from a dielectric material and has a hardmask gate cap formed on an upper surface thereof.

- the methodfurther comprises depositing a high-dielectric layer that conforms to an outer surface of each dummy gate element. A spacer layer is deposited on the high-dielectric layer.

- the methodfurther comprises performing a first etching process that etches the spacer layer to form a spacer on each sidewall of dummy gate elements and exposes an upper portion of the high-dielectric layer.

- the methodfurther comprises performing a second etching process that is different from the first etching process that selectively etches the upper portion of the high-dielectric layer to expose each hardmask gate cap.

- the methodfurther comprises removing the hardmask gate caps and the dummy gate elements to form a trench between a respective pair of spacers.

- the methodfurther comprises performing a third etching process after removing the dummy gates elements to remove a portion of the high-dielectric material from the sidewalls of the spacers such that a remaining portion of the high-dielectric material is interposed between the spacers and the etch stop layer.

- FIG. 1is an isometric view of a conventional array of semiconductor fins having gate elements formed thereon;

- FIG. 2Ais block diagram of a starting substrate including a plurality of gate formation layers formed on a semiconductor fin according to a first orientation extending along a Y-axis to define a length;

- FIG. 2Billustrates the starting substrate of FIG. 2A according to a second orientation showing the gate formation layers formed on a plurality of semiconductor fins and extending along an X-axis to define a width;

- FIG. 3Aillustrates the substrate of FIGS. 2A-2B according to the first orientation following patterning of a photoresist layer

- FIG. 3Billustrates the substrate of FIG. 3A according to the second orientation

- FIG. 4Aillustrates the substrate of FIGS. 3A-3B according to the first orientation following etching of an optical planar layer and hardmask layer to form individual hardmask gate caps;

- FIG. 4Billustrates the substrate of FIG. 4A according to the second orientation

- FIG. 5Aillustrates the substrate of FIGS. 4A-4B according to the first orientation after etching dummy gate layer according to the patterned hardmask layer to form individual dummy gate elements;

- FIG. 5Billustrates the substrate of FIG. 5A according to the second orientation

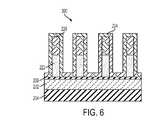

- FIG. 6illustrates the substrate of FIG. 5A following deposition of a conformal spacer layer on sidewalls of the dummy gates elements, gate caps, and on exposed surfaces of the etch stop layer located between each dummy gate element;

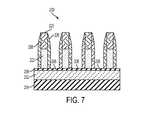

- FIG. 7illustrates the substrate of FIG. 6 following an etching process that partially etches the spacer layer formed on the dummy gate element and that removes the spacer layer formed on the etch stop layer;

- FIG. 8illustrates the substrate of FIG. 7 following a pre-clean process that removes a portion of the etch stop layer located between each dummy gate element to expose a portion of the underlying semiconductor fin;

- FIG. 9illustrates the substrate of FIG. 8 following an epitaxial growth process that grows an epitaxial material on the exposed portion of the semiconductor fin located between the dummy gate elements;

- FIG. 10illustrates the substrate of FIG. 9 following deposition of a block dielectric layer that fills the region between the dummy gate elements and that covers the gate caps;

- FIG. 11illustrates the substrate of FIG. 10 following a planarization process that recesses the block dielectric layer and a portion of the spacer layer to expose the dummy gate elements;

- FIG. 12illustrates the substrate of FIG. 11 following removal of the dummy gate elements to form respective gate trenches

- FIG. 13illustrates the substrate of FIG. 12 following a high-dielectric layer deposition and work function metal filling process that fills the trenches with a gate metal to form respective metal gate elements;

- FIG. 14illustrates another exemplary embodiment of the present disclosure where a conformal high-dielectric layer is deposited on sidewalls of the dummy gates elements, gate caps, and on exposed surfaces of the etch stop layer located between each dummy gate element, and a conformal spacer layer is formed on an upper surface of the high-dielectric layer;

- FIG. 15illustrates the substrate of FIG. 14 following an etching process that partially removes the spacer layer formed on the etch stop layer and that etches the spacer layer formed on the dummy gate element to expose an upper portion of the high-dielectric layer;

- FIG. 16illustrates the substrate of FIG. 15 following an etching process that removes an upper portion of the high-dielectric layer

- FIG. 17illustrates the substrate of FIG. 16 following a planarization process that recesses a block dielectric layer and gate caps to expose the dummy gate elements;

- FIG. 18illustrates the substrate of FIG. 17 following removal of the dummy gate elements to form respective gate trenches and to expose the high-dielectric layer formed on sidewalls of the trenches;

- FIG. 19illustrates the substrate of FIG. 18 following an etching process that removes the high-dielectric layer formed on sidewalls of the trenches.

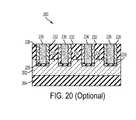

- FIG. 20illustrates the substrate of FIG. 19 following a high-dielectric layer deposition and work function metal filling process that fills the trenches with a gate metal to form respective metal gate elements.

- FIG. 21is a flow diagram illustrating a method of fabricating a semiconductor device according to an exemplary embodiment of the present disclosure.

- a starting semiconductor substrate 200 including a plurality of gate formation layers formed on one or more semiconductor fins 202is illustrated according to an exemplary embodiment of the present disclosure.

- the substrate 200extends along an X-axis to define a width and a Y-axis to define a length.

- the semiconductor fins 202may be formed on a buried oxide (BOX) layer 204 formed on the substrate 200 . It is appreciated, however, that the semiconductor fins 202 may be formed on a bulk semiconductor layer of the substrate 200 .

- An etch stop layer 206may be formed on an upper surface of the semiconductor fins 202 .

- the BOX layer and the etch stop layermay be formed from a dielectric material including, but not limited to, silicon oxide (SiO 2 ).

- a finFET semiconductor deviceis described going forward, it is appreciated that the inventive teachings described herein may be applied to various other semiconductor topologies including, but not limited to, a planar semiconductor device, and a nanowire semiconductor device.

- the gate formation layersare formed on an upper surface of the etch stop layer 206 formed on each semiconductor fin 202 .

- the plurality of gate formation layersinclude, for example, a dummy gate dielectric layer 208 , a gate hardmask layer 210 , an optical planar layer (OPL) 212 , an anti-reflective coating (ARC) layer 214 , and a photoresist layer 216 .

- OPLoptical planar layer

- ARCanti-reflective coating

- the ARC layer 214may be replaced with a silicon oxide layer.

- the dummy gate dielectric layer 208may be formed directly on an upper surface of the etch stop layer 206 , for example. Unlike a conventional replacement metal gate (RMG) process, the dummy gate dielectric layer 208 is formed from a dielectric material instead of amorphous silicon (Si) or polysilicon (PC).

- the dummy gate dielectric layer 208may be formed from various materials including, but not limited to, boron carbide (BC), a silicon boron carbide material that contains nitrogen (i.e., SiB:C(N)), carbon (C), compressed carbon, and SiO 2 . Therefore, at least one exemplary embodiment of the present disclosure may prevent inadvertent epitaxially growth on exposed portions of the dummy gate element (described below). Accordingly, shorting between epitaxially grown source-drain regions and the dummy gate element may be prevented.

- BCboron carbide

- SiB:C(N)silicon boron carbide material that contains nitrogen (i.e., SiB

- the gate hardmask layer 210is stacked on the dummy gate dielectric layer 208 and may be formed from various materials including, but not limited to, silicon nitride (SiN) and silicon dioxide (SiO 2 ).

- the OPL 212is stacked on the gate hardmask layer 210 to form a planarized upper surface.

- the OPL 212may be formed from an organic dielectric layer (ODL) material including, but not limited to, amorphous carbon, CHM701B, commercially available from Cheil Chemical Co., Ltd., HM8006 and HM8014, commercially available from JSR Corporation, and ODL-102, commercially available from ShinEtsu Chemical, Co., Ltd.

- ODLorganic dielectric layer

- the SiARC layer 214is stacked on the OPL 212 and may comprise Si, for example, to form a silicon-containing ARC (SiARC) layer as described going forward.

- the photoresist layer 216may be deposited according to a chemical vapor deposition (CVD) process or an atomic layer deposition (ALD) process as understood by those ordinarily skilled in the art.

- the photoresist layer 216is patterned to form one or more individual gate resist elements 218 .

- the gate resist elements 218ultimately determine the pattern of respective dummy gate elements to be formed on the substrate 200 as understood by those ordinarily skilled in the art.

- the stacked arrangement of the photoresist layer 216 , the SiARC layer 214 and the OPL 212may form a multilayer element (e.g., a trilateral element) such that a trilayer resist (TLR) patterning scheme may be performed that forms one or more dummy gate elements.

- TLRtrilayer resist

- the TLR pattering schemecomprises, for example, patterning the photoresist layer 216 using lithography and trimming, performing first a reactive ion etching (RIE) plasma process to etch through the SiARC layer 214 utilizing the patterned photoresist layer 216 (i.e., the gate resist elements 218 ) as a first pattern mask where a portion of the photoresist layer 216 is consumed during the during first etching, performing a second etching process to etch the ODL utilizing the patterned SiARC layer 214 as a second pattern mask where the photoresist layer 216 is completely consumed during the second etching, performing a third etching process to remove (e.g., burn-off) the SiARC layer 214 , performing a fourth etching process to etch the gate hardmask layer 210 utilizing the etched ODL as a third pattern mask where a portion of the gate hardmask layer 210 is removed during the third etching such that individual hardmask gate caps 2

- RIEreactive

- the dummy gate dielectric layer 208is patterned according to the patterned gate hardmask layer 210 (i.e., the hardmask gate caps 220 ) to form individual dummy gate elements 222 .

- the dummy gate dielectric layer 208may be etched using a reactive ion etching (RIE) process as understood by those ordinarily skilled in the art. Accordingly, one or more individual dummy gate elements 222 are formed that wrap around one or more semiconductor fins 202 .

- RIEreactive ion etching

- a conformal spacer layer 224is deposited on sidewalls of the dummy gates elements 222 , hardmask gate caps 220 , and on exposed surfaces of the etch stop layer 206 located between each dummy gate element 222 .

- the conformal spacer layer 224may be formed from, for example, silicon nitride (SiN).

- the spacer layer 224 formed on the dummy gate element 222is partially etched such that spacers 226 are formed on sidewalls of the dummy gate element 222 .

- Various etching processesmay be used to etch the spacer layer 224 including, but not limited to, RIE.

- a portion of the spacer layer 224 formed on the hardmask gate cap 220may also be removed such that the underlying gate cap 220 is exposed as further illustrated in FIG. 7 .

- a pre-clean processis performed that removes a portion of the etch stop layer 206 located between each dummy gate element 222 . Accordingly, a cavity 228 is formed between each dummy gate element 222 , which exposes a portion of the underlying semiconductor fin 202 .

- the pre-clean processmay be performed using a hydrogen fluoride (HF) based wet clean process, or a dry etching process that uses remote plasma that reacts with the etch stop layer 206 , while being selective to the spacers 226 .

- HFhydrogen fluoride

- an epitaxial growth processis performed that grows an epitaxial semiconductor material 230 on the exposed portion of the semiconductor fin 202 located between the dummy gate elements 222 .

- Well-known processes used to epitaxially grow an epitaxial semiconductor material 230including, but not limited to, silicon doped with germanium (Ge), carbon (C), and phosphorus (P), or any dopants desired to lower external resistance for forming a source/drain region.

- the epitaxial semiconductor material 230may be grown from a portion of the semiconductor fin 202 exposed by a respective cavity 228 and may extend therefrom to contact the sidewalls of a pair of opposing spacers 226 to form one or more source/drain regions.

- a contact dielectric layer 232is deposited on the hardmask gate caps 220 and in the voids between the dummy gate elements 222 .

- the contact dielectric layer 232may also contact one or more source/drain regions of one or more semiconductor fins 202 .

- Various methodsmay be used to deposit the contact dielectric layer 232 including, but not limited to, chemical vapor deposition (CVD) and atomic layer deposition (ALD).

- the contact dielectric layer 232may be formed from various materials including, but not limited to, SiO 2 .

- a planarization processis performed, which partially recesses the contact dielectric layer 232 and a portion of the spacer layer 224 to expose the dummy gate elements 222 .

- the planarization processmay stop on the upper surface of the dummy gate elements 222 such that the upper surface of the contact dielectric layer 232 is flush with the upper surfaces of the dummy gate elements 222 .

- the dummy gate elements 222are removed according to a replacement metal gate (RMG) process as understood by those ordinarily skilled in the art.

- the dummy gate elements 222may be removed using an RIE process or a wet etching process. Accordingly, gate trenches 234 that expose the underlying etch stop layer 206 of the semiconductor fin 202 are formed between a respective pair of spacers 226 .

- an anneal processmay be performed after removing the dummy gate elements 222 to activate the dopants of the source/drain regions. The anneal process may generate a temperature of approximately 900 degrees Celsius (C) or higher, for example.

- a metal filling processis performed that fills the trenches with a gate metal to form respective metal gate elements 236 .

- the gate metalmay include various metal materials including, but not limited to, tungsten (W), tantalum (Ta), titanium (Ti), Niobium (Nb), rhenium (Rh), aluminum (Al), tungsten nitride (WN), titanium nitride (TiN) and tantalum nitride (TaN).

- each metalmay contact a respective pair of spacers 226 and a respective etch stop layer 206 .

- one or more work function metal (WFM) layersmay be deposited in the trenches 234 and formed on the sidewalls of the spacers 226 before filling the trenches 234 with the metal gate material.

- the WFM layermay tune the threshold voltage of a resulting semiconductor device as understood by those ordinarily skilled in the art.

- FIGS. 14-20a process flow that interposes a high-dielectric constant layer 238 (i.e., a high-k layer 238 ) between the spacers 226 and the sidewalls of each dummy gate element 222 is illustrated according to an exemplary embodiment of the present disclosure.

- FIG. 14illustrates a conformal high-k layer 238 interposed between a conformal spacer layer 224 and the dummy gate elements 222 .

- the conformal high-k layer 238may first be deposited on sidewalls of the dummy gates elements 222 , hardmask gate caps 220 , and exposed surfaces of the etch stop layer 206 located between each dummy gate element 222 .

- the high-k layer 238may be formed from various high-k materials including, but not limited to, hafnium oxide (HfO 2 ).

- the conformal spacer layer 224may then be formed on an upper surface of the high-k layer 238 .

- the conformal spacer layer 224may be formed from, for example, SiN.

- an etching processis performed that partially removes the spacer layer 224 formed on the etch stop layer 206 and that etches the spacer layer 224 formed on the dummy gate element 222 . Accordingly, an upper portion of the high-k layer 238 is exposed.

- a second etching processsuch as a carina etch for example, is performed that removes the exposed upper portion of the high-k layer 238 .

- the carina etchis selective to the spacer layer 224 such that the high-k layer 238 is removed while the spacer layer 224 is maintained. Accordingly, an upper portion of the underlying hardmask gate cap 220 is exposed.

- a planarization process that partially recesses a contact dielectric layer 232is performed which exposes an upper portion of the dummy gate elements 222 .

- the contact dielectric layer 232is formed as previously discussed above.

- the planarization processmay stop on the upper surface of the dummy gate elements 222 such that the upper surface of the contact dielectric layer 232 is flush with the upper surfaces of the dummy gate elements 222 .

- the dummy gate elements 222are removed according to a replacement metal gate (RMG) process as understood by those ordinarily skilled in the art.

- RMGreplacement metal gate

- an RIE process or a wet etching processmay be used to remove the dummy gate elements 222 .

- gate trenches 234are formed that expose portions of the underlying etch stop layer 206 located between the remaining high-k layer 238 formed on sidewalls of the spacers 226 .

- an etching processis performed that removes portions of the high-k layer 238 from the sidewalls of the spacers 226 such that the length of each trench 234 increases.

- Various etchings processmay be used to remove the high-k layer 238 including, but not limited to, a carina etch.

- a portion of the high-k layer 238 ′may be maintained between the spacer 226 and the etch stop layer 206 , while the trench 234 exposes a portion of the etch stop layer 206 located between the spacers 226 .

- at least one exemplary embodiment of the present teachingsutilizes the high-k layer 238 as a gate oxide layer.

- the properties of the high-k layer 238may change during the dummy gate pull process to affect work function properties.

- the high-k layer 238may be best used as a sacrificial layer and may be omitted at FIG. 19 , and deposited as a high-k gate oxide layer before performing a metal filling process described below. Accordingly, process of removing portions of the high-k layer 238 from the sidewalls is optional and may be skipped at this stage of the exemplary process flow.

- the gate metalmay include various metal materials including, but not limited to, tungsten (W), tantalum (Ta), titanium (Ti), Niobium (Nb), rhenium (Rh), aluminum (Al), tungsten nitride (WN), titanium nitride (TiN) and tantalum nitride (TaN).

- the metal gate elements 236may contact the spacers 226 , the remaining high-k material, and the etch stop layer 206 .

- a high-k layer 238 for forming a gate oxide layermay be deposited in the trenches 234 before depositing the gate metal in the trenches 234 .

- FIG. 21is a flow diagram illustrating a method of fabricating a semiconductor device according to an exemplary embodiment of the present disclosure.

- the methodbegins at operation 2100 , and proceeds to operation 2102 where a plurality of gate formation layers are formed on one or more semiconductor fins.

- the semiconductor finsare formed on a semiconductor substrate as understood by those ordinarily skilled in the art.

- the plurality of gate formation layersare etched such that a one or more hardmask gate caps are patterned atop a dummy gate dielectric layer.

- a trilayer resist (TLR) patterning schememay be used to etch the gate formation layer, for example.

- TLRtrilayer resist

- the dummy gate dielectric layeris etched to form one or more dummy gate elements having a respective hardmask gate cap formed on an upper surface thereof.

- the pattern of the one or more gate elementsmay be based on a pattern of the one or more hardmask gate caps previously formed atop the dummy gate dielectric layer.

- a conformal spacer layeris deposited on sidewalls of the dummy gates elements, the gate caps, and on the exposed surfaces of the etch stop layer located between each dummy gate element.

- a conformal high-k layermay be deposited on sidewalls of the dummy gates elements, the gate caps, and on the exposed surfaces of the etch stop layer located between each dummy gate element.

- the conformal spacer layeris deposited on top of the high-k layer.

- the high-k layeris interposed between the dummy gate elements and the spacer layer.

- the spacer layer formed on the dummy gate elementis partially etched such that the spacers are formed on the sidewalls of the dummy gate element and a portion of the underlying gate cap is exposed.

- a pre-clean processis performed that removes a portion of the etch stop layer located between each dummy gate element. Accordingly, a portion of the underlying semiconductor fin located between each dummy gate element is exposed.

- an epitaxial materialis grown on the exposed portion of the semiconductor fin located between the dummy gate elements.

- a contact dielectric layeris deposited on the gate caps and in the voids between the dummy gate elements.

- a portion of contact dielectric layer and a portion of the spacersare recessed using, for example, a chemical mechanical planarization (CMP) process.

- CMPchemical mechanical planarization

- the planarization processmay stop on the upper surface of the dummy gate elements such that the upper surface of the contact dielectric layer is flush with the upper surfaces of the dummy gate elements.

- the dummy gate elementsare removed according to a replacement metal gate (RMG) process as understood by those ordinarily skilled in the art.

- RMGreplacement metal gate

- a wet etching process or RIE processmay be used to remove the dummy gate elements.

- gate trenches that expose the underlying etch stop layerare formed between a respective pair of spacers.

- the trenchesare filled with a metal gate material to form respective metal gate elements, and the method ends at operation 2124 .

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Power Engineering (AREA)

- Chemical & Material Sciences (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Inorganic Chemistry (AREA)

- Plasma & Fusion (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Electrodes Of Semiconductors (AREA)

Abstract

Description

- The present invention relates to semiconductor device fabrication, and in particular, to a replacement metal gate process.

- A replacement metal gate (RMG) process, i.e., a gate last process, has been traditionally used in semiconductor fabrications processes to form a semiconductor device including one or

more gate elements 102 that wrap around on one ormore semiconductor fins 104. Thegate elements 102 typically extend in a direction perpendicular to the direction of thesemiconductor fins 104 as illustrated inFIG. 1 . The RMG process utilizes a dummy gate element formed from amorphous silicon (a-Si) or polysilicon (PC), which is ultimately replaced with a metal gate element as understood by those ordinarily skilled in the art. However, the silicon material of the dummy gate element may be exposed when recessing the spacers formed on the sidewalls of the dummy gate element. Consequently, epitaxial material may be inadvertently grown on the exposed silicon of the dummy gate element which may result in a short between the epitaxially grown source/drain regions and the epitaxial material grown on the gate element. - According to at least one embodiment a method of fabricating a semiconductor device comprises forming at least one semiconductor fin on a semiconductor substrate. A plurality of gate formation layers is formed on an etch stop layer that is formed on one or more of the semiconductor fins. The plurality of gate formation layers include a dummy gate layer formed from a dielectric material. The plurality of gate formation layers is patterned to form a plurality of dummy gate elements on the etch stop layer. Each dummy gate element is formed from the dielectric material. A spacer layer formed on the dummy gate elements is etched to form a spacer on each sidewall of dummy gate elements. A portion of the etch stop layer located between each dummy gate element is etched to expose a portion the semiconductor fin. A semiconductor material is epitaxially grown from the exposed portion of the semiconductor fin to form source/drain regions.

- According to another exemplary embodiment, a method of fabricating a semiconductor device comprises forming at least one semiconductor fin on a semiconductor substrate. The at least one semiconductor fin includes an etch stop layer formed on an upper surface thereof. The method further comprises forming a plurality of dummy gate elements on the etch stop layer. Each dummy gate element is formed from a dielectric material and has a hardmask gate cap formed on an upper surface thereof. The method further comprises depositing a high-dielectric layer that conforms to an outer surface of each dummy gate element. A spacer layer is deposited on the high-dielectric layer. The method further comprises performing a first etching process that etches the spacer layer to form a spacer on each sidewall of dummy gate elements and exposes an upper portion of the high-dielectric layer. The method further comprises performing a second etching process that is different from the first etching process that selectively etches the upper portion of the high-dielectric layer to expose each hardmask gate cap. The method further comprises removing the hardmask gate caps and the dummy gate elements to form a trench between a respective pair of spacers. The method further comprises performing a third etching process after removing the dummy gates elements to remove a portion of the high-dielectric material from the sidewalls of the spacers such that a remaining portion of the high-dielectric material is interposed between the spacers and the etch stop layer.

- Additional features are realized through the techniques of the present invention. Other embodiments are described in detail herein and are considered a part of the claimed invention. For a better understanding of the invention with the features, refer to the description and to the drawings.

- The subject matter which is regarded as the invention is particularly pointed out and distinctly claimed in the claims at the conclusion of the specification. The forgoing features are apparent from the following detailed description taken in conjunction with the accompanying drawings in which:

FIG. 1 is an isometric view of a conventional array of semiconductor fins having gate elements formed thereon;FIG. 2A is block diagram of a starting substrate including a plurality of gate formation layers formed on a semiconductor fin according to a first orientation extending along a Y-axis to define a length;FIG. 2B illustrates the starting substrate ofFIG. 2A according to a second orientation showing the gate formation layers formed on a plurality of semiconductor fins and extending along an X-axis to define a width;FIG. 3A illustrates the substrate ofFIGS. 2A-2B according to the first orientation following patterning of a photoresist layer;FIG. 3B illustrates the substrate ofFIG. 3A according to the second orientation;FIG. 4A illustrates the substrate ofFIGS. 3A-3B according to the first orientation following etching of an optical planar layer and hardmask layer to form individual hardmask gate caps;FIG. 4B illustrates the substrate ofFIG. 4A according to the second orientation;FIG. 5A illustrates the substrate ofFIGS. 4A-4B according to the first orientation after etching dummy gate layer according to the patterned hardmask layer to form individual dummy gate elements;FIG. 5B illustrates the substrate ofFIG. 5A according to the second orientation;FIG. 6 illustrates the substrate ofFIG. 5A following deposition of a conformal spacer layer on sidewalls of the dummy gates elements, gate caps, and on exposed surfaces of the etch stop layer located between each dummy gate element;FIG. 7 illustrates the substrate ofFIG. 6 following an etching process that partially etches the spacer layer formed on the dummy gate element and that removes the spacer layer formed on the etch stop layer;FIG. 8 illustrates the substrate ofFIG. 7 following a pre-clean process that removes a portion of the etch stop layer located between each dummy gate element to expose a portion of the underlying semiconductor fin;FIG. 9 illustrates the substrate ofFIG. 8 following an epitaxial growth process that grows an epitaxial material on the exposed portion of the semiconductor fin located between the dummy gate elements;FIG. 10 illustrates the substrate ofFIG. 9 following deposition of a block dielectric layer that fills the region between the dummy gate elements and that covers the gate caps;FIG. 11 illustrates the substrate ofFIG. 10 following a planarization process that recesses the block dielectric layer and a portion of the spacer layer to expose the dummy gate elements;FIG. 12 illustrates the substrate ofFIG. 11 following removal of the dummy gate elements to form respective gate trenches;FIG. 13 illustrates the substrate ofFIG. 12 following a high-dielectric layer deposition and work function metal filling process that fills the trenches with a gate metal to form respective metal gate elements;FIG. 14 illustrates another exemplary embodiment of the present disclosure where a conformal high-dielectric layer is deposited on sidewalls of the dummy gates elements, gate caps, and on exposed surfaces of the etch stop layer located between each dummy gate element, and a conformal spacer layer is formed on an upper surface of the high-dielectric layer;FIG. 15 illustrates the substrate ofFIG. 14 following an etching process that partially removes the spacer layer formed on the etch stop layer and that etches the spacer layer formed on the dummy gate element to expose an upper portion of the high-dielectric layer;FIG. 16 illustrates the substrate ofFIG. 15 following an etching process that removes an upper portion of the high-dielectric layer;FIG. 17 illustrates the substrate ofFIG. 16 following a planarization process that recesses a block dielectric layer and gate caps to expose the dummy gate elements;FIG. 18 illustrates the substrate ofFIG. 17 following removal of the dummy gate elements to form respective gate trenches and to expose the high-dielectric layer formed on sidewalls of the trenches;FIG. 19 illustrates the substrate ofFIG. 18 following an etching process that removes the high-dielectric layer formed on sidewalls of the trenches; andFIG. 20 illustrates the substrate ofFIG. 19 following a high-dielectric layer deposition and work function metal filling process that fills the trenches with a gate metal to form respective metal gate elements.FIG. 21 is a flow diagram illustrating a method of fabricating a semiconductor device according to an exemplary embodiment of the present disclosure.- With reference now to

FIGS. 2A-2B , a startingsemiconductor substrate 200 including a plurality of gate formation layers formed on one ormore semiconductor fins 202 is illustrated according to an exemplary embodiment of the present disclosure. Thesubstrate 200 extends along an X-axis to define a width and a Y-axis to define a length. Thesemiconductor fins 202 may be formed on a buried oxide (BOX)layer 204 formed on thesubstrate 200. It is appreciated, however, that thesemiconductor fins 202 may be formed on a bulk semiconductor layer of thesubstrate 200. Anetch stop layer 206 may be formed on an upper surface of thesemiconductor fins 202. The BOX layer and the etch stop layer may be formed from a dielectric material including, but not limited to, silicon oxide (SiO2). Although a finFET semiconductor device is described going forward, it is appreciated that the inventive teachings described herein may be applied to various other semiconductor topologies including, but not limited to, a planar semiconductor device, and a nanowire semiconductor device. - The gate formation layers are formed on an upper surface of the

etch stop layer 206 formed on eachsemiconductor fin 202. The plurality of gate formation layers include, for example, a dummygate dielectric layer 208, agate hardmask layer 210, an optical planar layer (OPL)212, an anti-reflective coating (ARC)layer 214, and aphotoresist layer 216. Although not illustrated, TheARC layer 214 may be replaced with a silicon oxide layer. - The dummy

gate dielectric layer 208 may be formed directly on an upper surface of theetch stop layer 206, for example. Unlike a conventional replacement metal gate (RMG) process, the dummygate dielectric layer 208 is formed from a dielectric material instead of amorphous silicon (Si) or polysilicon (PC). The dummygate dielectric layer 208 may be formed from various materials including, but not limited to, boron carbide (BC), a silicon boron carbide material that contains nitrogen (i.e., SiB:C(N)), carbon (C), compressed carbon, and SiO2. Therefore, at least one exemplary embodiment of the present disclosure may prevent inadvertent epitaxially growth on exposed portions of the dummy gate element (described below). Accordingly, shorting between epitaxially grown source-drain regions and the dummy gate element may be prevented. - The

gate hardmask layer 210 is stacked on the dummygate dielectric layer 208 and may be formed from various materials including, but not limited to, silicon nitride (SiN) and silicon dioxide (SiO2). TheOPL 212 is stacked on thegate hardmask layer 210 to form a planarized upper surface. TheOPL 212 may be formed from an organic dielectric layer (ODL) material including, but not limited to, amorphous carbon, CHM701B, commercially available from Cheil Chemical Co., Ltd., HM8006 and HM8014, commercially available from JSR Corporation, and ODL-102, commercially available from ShinEtsu Chemical, Co., Ltd. - The

SiARC layer 214 is stacked on theOPL 212 and may comprise Si, for example, to form a silicon-containing ARC (SiARC) layer as described going forward. Thephotoresist layer 216 may be deposited according to a chemical vapor deposition (CVD) process or an atomic layer deposition (ALD) process as understood by those ordinarily skilled in the art. - Referring to

FIGS. 3A-3B , thephotoresist layer 216 is patterned to form one or more individual gate resistelements 218. The gate resistelements 218 ultimately determine the pattern of respective dummy gate elements to be formed on thesubstrate 200 as understood by those ordinarily skilled in the art. The stacked arrangement of thephotoresist layer 216, theSiARC layer 214 and theOPL 212 may form a multilayer element (e.g., a trilateral element) such that a trilayer resist (TLR) patterning scheme may be performed that forms one or more dummy gate elements. - According to at least embodiment, the TLR pattering scheme comprises, for example, patterning the

photoresist layer 216 using lithography and trimming, performing first a reactive ion etching (RIE) plasma process to etch through theSiARC layer 214 utilizing the patterned photoresist layer216 (i.e., the gate resist elements218) as a first pattern mask where a portion of thephotoresist layer 216 is consumed during the during first etching, performing a second etching process to etch the ODL utilizing the patternedSiARC layer 214 as a second pattern mask where thephotoresist layer 216 is completely consumed during the second etching, performing a third etching process to remove (e.g., burn-off) theSiARC layer 214, performing a fourth etching process to etch thegate hardmask layer 210 utilizing the etched ODL as a third pattern mask where a portion of thegate hardmask layer 210 is removed during the third etching such that individual hardmask gate caps220 are formed on the dummygate dielectric layer 208, and stripping the etched ODL using an RIE or wet cleaning process to form one or more individual hardmask gate caps220 on the dummygate dielectric layer 208 as illustrated inFIGS. 4A-4B . Accordingly, the pattern of thephotoresist layer 216 may be transferred to thegate hardmask layer 210 for ultimately forming the pattern of dummy gate elements as discussed in greater detail below - Referring to

FIGS. 5A-5B , the dummygate dielectric layer 208 is patterned according to the patterned gate hardmask layer210 (i.e., the hardmask gate caps220) to form individualdummy gate elements 222. The dummygate dielectric layer 208 may be etched using a reactive ion etching (RIE) process as understood by those ordinarily skilled in the art. Accordingly, one or more individualdummy gate elements 222 are formed that wrap around one ormore semiconductor fins 202. - Turning now to

FIG. 6 , aconformal spacer layer 224 is deposited on sidewalls of thedummy gates elements 222, hardmask gate caps220, and on exposed surfaces of theetch stop layer 206 located between eachdummy gate element 222. Theconformal spacer layer 224 may be formed from, for example, silicon nitride (SiN). - Referring to

FIG. 7 , thespacer layer 224 formed on thedummy gate element 222 is partially etched such thatspacers 226 are formed on sidewalls of thedummy gate element 222. Various etching processes may be used to etch thespacer layer 224 including, but not limited to, RIE. A portion of thespacer layer 224 formed on thehardmask gate cap 220 may also be removed such that theunderlying gate cap 220 is exposed as further illustrated inFIG. 7 . - Referring to

FIG. 8 , a pre-clean process is performed that removes a portion of theetch stop layer 206 located between eachdummy gate element 222. Accordingly, acavity 228 is formed between eachdummy gate element 222, which exposes a portion of theunderlying semiconductor fin 202. The pre-clean process may be performed using a hydrogen fluoride (HF) based wet clean process, or a dry etching process that uses remote plasma that reacts with theetch stop layer 206, while being selective to thespacers 226. - Turning now to

FIG. 9 , an epitaxial growth process is performed that grows anepitaxial semiconductor material 230 on the exposed portion of thesemiconductor fin 202 located between thedummy gate elements 222. Well-known processes used to epitaxially grow anepitaxial semiconductor material 230 including, but not limited to, silicon doped with germanium (Ge), carbon (C), and phosphorus (P), or any dopants desired to lower external resistance for forming a source/drain region. Theepitaxial semiconductor material 230 may be grown from a portion of thesemiconductor fin 202 exposed by arespective cavity 228 and may extend therefrom to contact the sidewalls of a pair of opposingspacers 226 to form one or more source/drain regions. - Referring to

FIG. 10 , acontact dielectric layer 232 is deposited on the hardmask gate caps220 and in the voids between thedummy gate elements 222. Thecontact dielectric layer 232 may also contact one or more source/drain regions of one ormore semiconductor fins 202. Various methods may be used to deposit thecontact dielectric layer 232 including, but not limited to, chemical vapor deposition (CVD) and atomic layer deposition (ALD). Thecontact dielectric layer 232 may be formed from various materials including, but not limited to, SiO2. - Referring now to

FIG. 11 , a planarization process is performed, which partially recesses thecontact dielectric layer 232 and a portion of thespacer layer 224 to expose thedummy gate elements 222. The planarization process may stop on the upper surface of thedummy gate elements 222 such that the upper surface of thecontact dielectric layer 232 is flush with the upper surfaces of thedummy gate elements 222. - Turning to

FIG. 12 , thedummy gate elements 222 are removed according to a replacement metal gate (RMG) process as understood by those ordinarily skilled in the art. For example, thedummy gate elements 222 may be removed using an RIE process or a wet etching process. Accordingly,gate trenches 234 that expose the underlyingetch stop layer 206 of thesemiconductor fin 202 are formed between a respective pair ofspacers 226. According to at least one embodiment, an anneal process may be performed after removing thedummy gate elements 222 to activate the dopants of the source/drain regions. The anneal process may generate a temperature of approximately 900 degrees Celsius (C) or higher, for example. - Referring to

FIG. 13 , a metal filling process is performed that fills the trenches with a gate metal to form respectivemetal gate elements 236. The gate metal may include various metal materials including, but not limited to, tungsten (W), tantalum (Ta), titanium (Ti), Niobium (Nb), rhenium (Rh), aluminum (Al), tungsten nitride (WN), titanium nitride (TiN) and tantalum nitride (TaN). According to this exemplary embodiment, each metal may contact a respective pair ofspacers 226 and a respectiveetch stop layer 206. In another embodiment, one or more work function metal (WFM) layers may be deposited in thetrenches 234 and formed on the sidewalls of thespacers 226 before filling thetrenches 234 with the metal gate material. The WFM layer may tune the threshold voltage of a resulting semiconductor device as understood by those ordinarily skilled in the art. - Turning now to

FIGS. 14-20 , a process flow that interposes a high-dielectric constant layer238 (i.e., a high-k layer238) between thespacers 226 and the sidewalls of eachdummy gate element 222 is illustrated according to an exemplary embodiment of the present disclosure. In this regard,FIG. 14 illustrates a conformal high-k layer 238 interposed between aconformal spacer layer 224 and thedummy gate elements 222. The conformal high-k layer 238 may first be deposited on sidewalls of thedummy gates elements 222, hardmask gate caps220, and exposed surfaces of theetch stop layer 206 located between eachdummy gate element 222. The high-k layer 238 may be formed from various high-k materials including, but not limited to, hafnium oxide (HfO2). Theconformal spacer layer 224 may then be formed on an upper surface of the high-k layer 238. Theconformal spacer layer 224 may be formed from, for example, SiN. - Referring to

FIG. 15 , an etching process is performed that partially removes thespacer layer 224 formed on theetch stop layer 206 and that etches thespacer layer 224 formed on thedummy gate element 222. Accordingly, an upper portion of the high-k layer 238 is exposed. - Referring to

FIG. 16 , a second etching process, such as a carina etch for example, is performed that removes the exposed upper portion of the high-k layer 238. The carina etch is selective to thespacer layer 224 such that the high-k layer 238 is removed while thespacer layer 224 is maintained. Accordingly, an upper portion of the underlyinghardmask gate cap 220 is exposed. - Referring to

FIG. 17 , a planarization process that partially recesses acontact dielectric layer 232 is performed which exposes an upper portion of thedummy gate elements 222. Thecontact dielectric layer 232 is formed as previously discussed above. The planarization process may stop on the upper surface of thedummy gate elements 222 such that the upper surface of thecontact dielectric layer 232 is flush with the upper surfaces of thedummy gate elements 222. - Referring now to

FIG. 18 , thedummy gate elements 222 are removed according to a replacement metal gate (RMG) process as understood by those ordinarily skilled in the art. For example, an RIE process or a wet etching process may be used to remove thedummy gate elements 222. Accordingly,gate trenches 234 are formed that expose portions of the underlyingetch stop layer 206 located between the remaining high-k layer 238 formed on sidewalls of thespacers 226. - Referring to