US20070245044A1 - System of interconnections for external functional blocks on a chip provided with a single configurable communication protocol - Google Patents

System of interconnections for external functional blocks on a chip provided with a single configurable communication protocolDownload PDFInfo

- Publication number

- US20070245044A1 US20070245044A1US11/482,175US48217506AUS2007245044A1US 20070245044 A1US20070245044 A1US 20070245044A1US 48217506 AUS48217506 AUS 48217506AUS 2007245044 A1US2007245044 A1US 2007245044A1

- Authority

- US

- United States

- Prior art keywords

- data

- interconnections

- response

- network

- read

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/66—Arrangements for connecting between networks having differing types of switching systems, e.g. gateways

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/40—Bus structure

- G06F13/4004—Coupling between buses

- G06F13/4022—Coupling between buses using switching circuits, e.g. switching matrix, connection or expansion network

Definitions

- the present inventionrelates to a system of interconnections for external functional blocks on a chip provided with a single configurable communication protocol.

- the cost of the wires in a system of interconnectionshas become dominant over the cost of the logic gates.

- assessing an interconnection network architecture on silicontakes into account the conditions of use of the wires and their cost effectiveness (quantity of information transported in relation to the cost).

- the integration of the functional blocksneeds to be more and more rapid.

- the system or network of interconnectionsmust be easy to implement.

- one object of the inventionis to propose a system of interconnections for external functional blocks on a chip provided with a single configurable communication protocol, that can easily be adapted according to the changing application-oriented requirements.

- a system of interconnections for external functional blocks on a chipprovided with a single configurable communication protocol.

- the systemcomprises two physically separate communication networks, a request network for transmitting request messages from an initiating block to a recipient block and a response network for transmitting response messages from a recipient block to an initiating block.

- the response messagesinclude additional information making said request and response networks able to respectively manage the request messages independently of the response messages.

- the request and response networksare capable of respectively managing the request messages independently of the response messages, they are autonomous.

- a response packetdoes not need to know the associated request, a change of size or frequency of the response packet is therefore possible without additional information and without saving the context between requests and responses within the system or network of interconnections.

- said protocolis organized in a plurality of independent layers.

- Said independent layerscomprise a transport layer defining the structure of a data packet, and a physical layer defining the signals interchanged at the interfaces of the elements of the system of interconnections. Address, data size and operation information is contained in the headers of the data packets.

- the rules that define the behaviour of a layerare independent of the way in which the preceding layer is implemented. This means it is easier to make optimizations on each layer, independently of the choices that might have been made on the other layers.

- said additional information of the response message data packetsincludes information representative of the operation carried out, and information representative of the size of the data associated with said operation carried out.

- the operationis a data read or a data write.

- the packets of the response message associated with said readinclude, at a predetermined position, said data that has been read.

- the packets of the response message associated with said readinclude information for aligning said data that has been read in relation to said memory space accessed.

- the interface between two elements of the system of interconnectionscomprises:

- the interface between two elements of the system of interconnectionsalso comprises signal generation means for favouring the transmission of some messages over others.

- the headers of the data packetsinclude an available space reserved for the use of the initiating blocks.

- the data packetsare of variable length, equal to a multiple of an elementary quantity of data.

- a system linkcan be programmed by the ratio between the quantity of data that it can transmit in each clock cycle and said elementary quantity of data.

- the linksinclude means of changing the clock frequency, and/or means of deleting data holes in the data packets in case of predictable hole ratios, and/or means of changing the serialization of the packets.

- the elements of the system of interconnectionsare configurable by software means via a separate network.

- said separate networkis able to operate at a low bit rate compared to the average bit rate in the system of interconnections.

- Another aspect of the inventionproposes generators of configurable IP blocks for constructing a system in a modular fashion as described previously, using standard interfaces.

- the generatorscomprise:

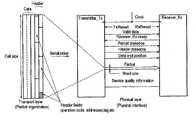

- FIG. 1illustrates the configurable protocol organized in a plurality of independent layers, according to one aspect of the invention.

- FIG. 2illustrates a system of interconnections for external functional blocks on a chip, according to one aspect of the invention.

- the protocolis defined on a number of independent layers, in this case on three layers: the physical layer, the transport layer and the transactional layer.

- the transport layeris used to control the interchange of data packets.

- a data packetis made up of an integer number of cells of equal size.

- a cellis an elementary quantity of data, the size of which is a parameter of the communication protocol.

- the size of the packet headeris one or two cells, depending on whether it is a response packet or a request packet.

- the header of a request data packetcontains the address of the recipient element in the network and the storage address in the addressing space of the recipient element, which does not need to be present in the header of the associated response data packet.

- the addressing space of the recipient elementcorresponds to a range of addresses that can be accessed, or at which a hardware device can be reached. These addresses can be physical or virtual.

- a data packet headeralways contains the address of the initiating element in the system or network of interconnections, and an information tag, used to identify the various data interchanges performed by one and the same initiating element.

- an initiating elementwhen it can communicate with several recipient elements, it needs to be able to identify the origin of the response data packets that it receives and it cannot therefore control the sequencing of the packets if they come from different recipient elements via different paths.

- each of these recipient elementsis assigned an identifier, or a tag, on a small number of bits.

- This tagis associated with the request data packet, and when the recipient element sends a corresponding response data packet, it attaches the corresponding tag to it.

- the transport layeris separated from the physical layer by placing in the header of a packet all the address and control information that concerns the packet, but not information concerning the manner in which it will physically be transported.

- the header of a packetcontains an operation code specifying the type of operation carried out or to be carried out (for example, read type or write type), the address of the initiating element in the network and a tag identifying the corresponding recipient element.

- the header of a data packetcan also contain, depending on the case, the address of the recipient element, the address corresponding to the operation carried out in the addressing domain of the recipient element, the length of the data, the transport control bits (corresponding, for example, to an exclusive or secured transaction), and any other information encoded on available bits reserved for the use of the initiating elements.

- the communication protocoldefines, for a data packet, the positioning of the various fields in the header of the data packet according to the operation codes.

- the separation of the request data packets and the response packets, with autonomous response packets,is performed by placing in the response data packet all the information needed to avoid saving contexts, in particular on changes of format on the data packets, in the elements that make up the network of interconnections.

- One way of ensuring the autonomy or independence of the response data packets with respect to the request data packetsis to have an operation code defining the transaction type (for example, read type or write type) and the associated quantity of data in the case of a read.

- a readit may be that information that is incomplete or unaligned in relation to the memory space accessed at the time of the read in the recipient element is accessed.

- the datais normally read in the format of the recipient element, and transmitted as such to the corresponding initiating element. Now, if the request requires a particular positioning of the data for the corresponding response, this positioning information must be determined from an associated response data packet.

- Any physical interfaceis independent of the message type, because, for the physical transport, all the cells or elementary data quantities are equivalent.

- the physical interfacemainly defines the nature of the signals in the links between the elements that make up the network of interconnections.

- the physical interfacecomprises the signals essential to the physical transport of the data during a clock cycle ( FIG. 1 ), such as:

- control information present in the header of a request data packetcan be analysed by the recipient element and retransmitted, modified or not, to the initiating element in the associated response data packet.

- the headers of the data packetsinclude an available space reserved for the use of the initiating blocks.

- the informationis encoded on the private bits of the reserved available space in the header of the request data packet.

- the private data bits that have been transmitted to itare used to separate the response and so terminate this set of transactions initiated by the initiating element.

- the cell sizeis fixed by the constraints on the data sizes rather than the constraints on the sizes of the data packet headers.

- the headertherefore normally includes a few unused bits, which can thus be exploited to advantageously replace context memories in the interfaces of the system of interconnections.

- the content of the packetdoes not depend on the manner in which it is transported.

- the request and response data packetsdo not need to have the same serializations, which are defined for each link in turn, by choosing the physical width of the link.

- the widths of the links and the clock timing frequencycan change, but the bit rates are adjusted to the slowest elements by the flow control.

- a FIFO type queueFor a change of frequency, a FIFO type queue is used, with two clocks, the size of which is sufficient never to needlessly lose cycles corresponding to the round-trip time of the flow control in the local loop, counted as a number of cycles of the slowest clock. A size of a few words is sufficient for such a queue.

- the size of the compaction queuecan be reduced using the size information present in the header of the data packets.

- the size of the queue and the latencycan be reduced by a factor of two.

- the paths between the initiating elements and the recipient elementsare partially shared in order to make best use of the wires.

- the system of interconnections 20comprises a request network 21 and a response network 22 that are physically separate.

- Message initiating elements 23 , 24 , 25 and 26can transmit request messages to recipient elements 27 , 28 , 29 , 30 and 31 via the request network 21 .

- the recipient elements 27 , 28 , 29 , 30 and 31can transmit response messages to the initiating elements 23 , 25 , 26 , which require a response on their-part, via the response networks 22 .

- the two networks 21 and 22have been represented side by side, and the message initiating elements 23 , 24 and 26 requiring a response to a request message sent to a recipient element 27 , 28 , 29 , 30 and 31 have been shown duplicated for greater clarity.

- the request network 21has two switches 32 , 33 and a demultiplexer 34 and four format converters 35 , 36 , 37 and 38 .

- the request network 21also comprises network interfaces 39 , 40 , 41 and 42 , respectively dedicated to the initiating elements 23 , 24 , 25 and 26 .

- the request network 21comprises network interfaces 43 , 44 , 45 , 46 and 47 , respectively dedicated to the recipient elements 27 , 28 , 29 , 30 and 31 .

- the response network 22comprises four switches 48 , 49 , 50 and 51 , one multiplexer 52 , and three format converters 53 , 54 and 55 . Furthermore, the response network 22 comprises network interfaces 56 , 57 , 58 , 59 and 60 , respectively dedicated to the recipient elements 27 , 28 , 29 , 30 and 31 , and network interfaces 61 , 62 and 63 , respectively dedicated to the initiating elements 23 , 25 and 26 , which require a response message after a request message has been sent.

- the request network 21comprises three subnetworks 64 , 65 and 66 , each having their own clock domain.

- the response network 22comprises three subnetworks 67 , 68 and 69 , each having their own clock domain.

- the subnetwork 64comprises the network interfaces 39 , 40 , 43 , 44 and 45 , the switch 32 and the format converters 35 and 36 .

- the network interfaces 39 and 40 , and the format converter 35can respectively transmit data packets, to the switch 32 , via the links 70 , 71 and 72 .

- the switch 32can transmit data packets to the network interfaces 43 , 44 and 45 , and to the format converter 36 , respectively via links 73 , 74 , 75 and 76 . Furthermore, the switch 32 can transmit data packets to another element via a link 77 .

- the subnetwork 65comprises the network interfaces 41 , 42 and 46 , the demultiplexer 34 , and the switch 33 .

- the network interface 41can transmit data packets to the demultiplexer 34 via a link 78 .

- the demultiplexer 34can transmit data packets to the format converters 35 and 37 , and to the switch 33 , respectively via links 79 , 80 and 81 .

- the network interface 42can transmit data packets to the switch 33 via a link 82 , and the format converter 36 via a link 82 a.

- the switch 33can transmit data packets to the network interface 46 and to the format converter 38 , respectively via links 83 and 84 .

- the subnetwork 66comprises the format converters 37 and 38 , and the network interface 47 .

- the format converters 37 and 38can respectively transmit data packets to the network interface 47 via links 85 and 86 .

- the subnetwork 67comprises the network interfaces 56 , 57 and 58 , the switches 48 , 49 and 50 , the format converters 53 and 54 and the network interface 61 .

- the network interfaces 57 and 58can transmit data packets to the switch 49 , respectively via links 87 and 88 .

- the network interface 56can transmit data packets to the switch 48 via a link 89 .

- the switch 48can also receive data packets from an element external to the response network 22 via a link 90 .

- the switches 48 and 49 , and the format converter 53can respectively transmit data packets to the switch 50 via links 91 , 92 and 93 .

- the switch 50can respectively transmit data packets to the network interface 61 and to the format converter 54 via links 94 and 95 .

- the subnetwork 68comprises the network interfaces 59 , 62 and 63 , the switch- 51 and the multiplexer 52 .

- the network interface 59 and the format converter 55can respectively transmit data packets to the switch 51 via links 96 and 97 .

- the switch 51can respectively transmit data packets to the format converter 53 , to the multiplexer 52 and to the network interface 63 via links 98 , 99 and 100 .

- the format converter 54can transmit data packets to the multiplexer 52 via a link 101 .

- the multiplexer 52can transmit data packets to the network interface 62 via a link 102 .

- the subnetwork 69comprises the network interface 60 and the format converter 55 , and a link 103 enabling the network interface 60 to transmit data packets to the format converter 55 .

- Serialization sdenotes the ratio of the width of the link (or word size) used to the size of the cell. For the subnetworks 64 and 67 , the serialization s is one, for the subnetworks 65 and 66 , the serialization s is two, and for the subnetworks 66 and 69 , the serialization s is four.

- the paths used for a transactioncan be followed from left to right.

- the initiating element(on the left) sends a request data packet which passes through the request network along a determined path to the recipient element.

- the latternormally returns a response data packet through the response network for the same initiating element (duplicated on the right of the figure).

- initiating elementssuch as memories with direct access, or DMA

- DMAdirect access

- the request and response networksare not symmetrical. Also, it is advantageous to be able to make independent optimizations of the request and response networks.

- Some elements that make up the network or system of interconnectionscan advantageously be configured by means of application software, by being able to program the values of software registers accessed by means of a network dedicated to this purpose.

- Each software registerhas its address in this dedicated network, which can be accessed by the request and response networks, with the presence, if necessary, of an interface between this dedicated network and the request and response networks.

- the separation of the routing in the networkallows a certain independence in the optimization of each link, which facilitates the design and implementation of a set of IP blocks, or intellectual property blocks, for the elements that make up the network of interconnections.

- IP blocksare configurable and can be assembled by simply joining up standard physical interfaces end to end to form a transport network. So, this “library” will contain at least the following elements:

- Each generatorcan, for example, produce descriptions in Verilog or VHDL language that can be synthesized by the standard CAD tools.

- These generatorsare coded in a language that enables the parameter space to be described easily in a structured manner.

- a generatorcan support lists of parameters, which can themselves be configured as in the case of the generator of switch IP blocks, for which it is possible to choose an arbitration type for each output, each type of arbiter having its own parameters.

Landscapes

- Engineering & Computer Science (AREA)

- General Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Signal Processing (AREA)

- Mathematical Physics (AREA)

- Computer Hardware Design (AREA)

- Computer Networks & Wireless Communication (AREA)

- General Physics & Mathematics (AREA)

- Data Exchanges In Wide-Area Networks (AREA)

- Communication Cables (AREA)

- Information Transfer Between Computers (AREA)

- Communication Control (AREA)

Abstract

Description

- The present invention relates to a system of interconnections for external functional blocks on a chip provided with a single configurable communication protocol.

- The ongoing trend in technology means that increasingly complex systems made up of numerous different functional blocks can be integrated. These functional blocks are developed by different teams using different methods and communication protocols, these functional blocks being called intellectual properties.

- It is therefore essential for these functional blocks to be able to intercommunicate, despite their different operating characteristics, such as the size of the data used and the frequencies used.

- Furthermore, since the communicating elements are becoming more and more numerous, the systems need to be flexible or adaptable enough to support this trend.

- Moreover, the cost of the wires in a system of interconnections has become dominant over the cost of the logic gates. Also, assessing an interconnection network architecture on silicon takes into account the conditions of use of the wires and their cost effectiveness (quantity of information transported in relation to the cost). Furthermore, since the time to market for new products is tending to shorten, the integration of the functional blocks needs to be more and more rapid. Also, the system or network of interconnections must be easy to implement.

- Solutions exist for interconnecting IP functional blocks in a system of interconnections on a semiconductor chip, and are mostly based on data buses. These networks lack the necessary flexibility for rapid adaptation to technological changes and for increasing the number of communicating elements.

- Such network architectures do not easily allow adaptation to the changing application-oriented requirements.

- Thus, one object of the invention is to propose a system of interconnections for external functional blocks on a chip provided with a single configurable communication protocol, that can easily be adapted according to the changing application-oriented requirements.

- Thus, according to one aspect of the invention, there is proposed a system of interconnections for external functional blocks on a chip provided with a single configurable communication protocol. The system comprises two physically separate communication networks, a request network for transmitting request messages from an initiating block to a recipient block and a response network for transmitting response messages from a recipient block to an initiating block. Furthermore, the response messages include additional information making said request and response networks able to respectively manage the request messages independently of the response messages.

- Since the request and response networks are capable of respectively managing the request messages independently of the response messages, they are autonomous. A response packet does not need to know the associated request, a change of size or frequency of the response packet is therefore possible without additional information and without saving the context between requests and responses within the system or network of interconnections.

- According to an embodiment, said protocol is organized in a plurality of independent layers. Said independent layers comprise a transport layer defining the structure of a data packet, and a physical layer defining the signals interchanged at the interfaces of the elements of the system of interconnections. Address, data size and operation information is contained in the headers of the data packets.

- Since the protocol is organized in separate layers, the rules that define the behaviour of a layer are independent of the way in which the preceding layer is implemented. This means it is easier to make optimizations on each layer, independently of the choices that might have been made on the other layers.

- Furthermore, this makes it possible to reduce the number of wires needed, by using the same wires to convey both the data of the packets, and data representative of address and control information.

- According to an embodiment, said additional information of the response message data packets includes information representative of the operation carried out, and information representative of the size of the data associated with said operation carried out.

- For example, the operation is a data read or a data write.

- According to an embodiment, following a read of data that is incomplete or unaligned in relation to the memory space accessed in said read, the packets of the response message associated with said read include, at a predetermined position, said data that has been read.

- According to an embodiment, following a read of data that is incomplete or unaligned in relation to the memory space accessed in said read, the packets of the response message associated with said read include information for aligning said data that has been read in relation to said memory space accessed.

- According to an embodiment, the interface between two elements of the system of interconnections comprises:

- means for receiving or transferring a clock timing signal,

- means for receiving or transferring signals for stopping or starting said elements independently,

- means of transferring flow control signals relating to the clock cycles,

- means of transferring data packet delimiting signals, and

- means of transferring signals of configurable size for transmitting the content of the data packets.

- According to an embodiment of the invention, the interface between two elements of the system of interconnections also comprises signal generation means for favouring the transmission of some messages over others.

- According to an embodiment, the headers of the data packets include an available space reserved for the use of the initiating blocks.

- According to an embodiment, the data packets are of variable length, equal to a multiple of an elementary quantity of data. A system link can be programmed by the ratio between the quantity of data that it can transmit in each clock cycle and said elementary quantity of data.

- According to an embodiment, the links include means of changing the clock frequency, and/or means of deleting data holes in the data packets in case of predictable hole ratios, and/or means of changing the serialization of the packets.

- According to an embodiment, the elements of the system of interconnections are configurable by software means via a separate network.

- For example, said separate network is able to operate at a low bit rate compared to the average bit rate in the system of interconnections.

- Another aspect of the invention proposes generators of configurable IP blocks for constructing a system in a modular fashion as described previously, using standard interfaces.

- According to an embodiment, the generators comprise:

- a generator of configurable protocol IP blocks,

- generators of network interface IP blocks between said configurable protocol and other communication protocols,

- generators of switch IP blocks,

- generators of IP blocks for changing clock, domain, compacting data packets, transporting packets over long distances, and programming ratios between the quantity of data that a link can transmit in each clock cycle and said elementary quantity of data, and

- generators of IP blocks of a separate network for configuring the elements of the system of interconnections.

- Other aims, features and advantages of the invention will become apparent from reading the description that follows, of a few by no means limiting examples, and with reference to the appended drawings, in which:

FIG. 1 illustrates the configurable protocol organized in a plurality of independent layers, according to one aspect of the invention; andFIG. 2 illustrates a system of interconnections for external functional blocks on a chip, according to one aspect of the invention.- As diagrammatically illustrated in

FIG. 1 , the protocol is defined on a number of independent layers, in this case on three layers: the physical layer, the transport layer and the transactional layer. - The transport layer is used to control the interchange of data packets. A data packet is made up of an integer number of cells of equal size.

- A cell is an elementary quantity of data, the size of which is a parameter of the communication protocol.

- The size of the packet header is one or two cells, depending on whether it is a response packet or a request packet. For example, the header of a request data packet contains the address of the recipient element in the network and the storage address in the addressing space of the recipient element, which does not need to be present in the header of the associated response data packet. The addressing space of the recipient element corresponds to a range of addresses that can be accessed, or at which a hardware device can be reached. These addresses can be physical or virtual.

- A data packet header always contains the address of the initiating element in the system or network of interconnections, and an information tag, used to identify the various data interchanges performed by one and the same initiating element.

- In practice, when an initiating element can communicate with several recipient elements, it needs to be able to identify the origin of the response data packets that it receives and it cannot therefore control the sequencing of the packets if they come from different recipient elements via different paths.

- Placing the address of the recipient element in the header of a response packet can be costly if there is a large number of recipient elements.

- However, since, at a given instant, the number of recipient elements corresponding with the initiating element is limited, each of these recipient elements is assigned an identifier, or a tag, on a small number of bits.

- This tag is associated with the request data packet, and when the recipient element sends a corresponding response data packet, it attaches the corresponding tag to it.

- The transport layer is separated from the physical layer by placing in the header of a packet all the address and control information that concerns the packet, but not information concerning the manner in which it will physically be transported.

- The header of a packet contains an operation code specifying the type of operation carried out or to be carried out (for example, read type or write type), the address of the initiating element in the network and a tag identifying the corresponding recipient element.

- The header of a data packet can also contain, depending on the case, the address of the recipient element, the address corresponding to the operation carried out in the addressing domain of the recipient element, the length of the data, the transport control bits (corresponding, for example, to an exclusive or secured transaction), and any other information encoded on available bits reserved for the use of the initiating elements.

- The communication protocol defines, for a data packet, the positioning of the various fields in the header of the data packet according to the operation codes.

- The separation of the request data packets and the response packets, with autonomous response packets, is performed by placing in the response data packet all the information needed to avoid saving contexts, in particular on changes of format on the data packets, in the elements that make up the network of interconnections.

- One way of ensuring the autonomy or independence of the response data packets with respect to the request data packets is to have an operation code defining the transaction type (for example, read type or write type) and the associated quantity of data in the case of a read.

- Furthermore, on a read, it may be that information that is incomplete or unaligned in relation to the memory space accessed at the time of the read in the recipient element is accessed.

- In practice, the data is normally read in the format of the recipient element, and transmitted as such to the corresponding initiating element. Now, if the request requires a particular positioning of the data for the corresponding response, this positioning information must be determined from an associated response data packet.

- It is, for example, possible to position the data that is read in a response data packet, at a predetermined position, and it is the initiating element that realigns the data on arrival by knowing the predetermined position.

- It is also possible to insert into the header of a response data packet information for aligning the data that is read relative to the memory space accessed.

- Any physical interface is independent of the message type, because, for the physical transport, all the cells or elementary data quantities are equivalent. The physical interface mainly defines the nature of the signals in the links between the elements that make up the network of interconnections.

- The physical interface comprises the signals essential to the physical transport of the data during a clock cycle (

FIG. 1 ), such as: - a clock timing signal;

- independent stop and restart signals for an element of the system of interconnections including at least one reset signal. These signals can include a power supply control signal and/or a signal for initializing flow control on the link;

- flow control signals relating to the clock cycles, for deleting the data packet storage queues at the nodes of the network, or for having holes in the data packets. These signals can also include a signal from the sender to the receiver of a data packet, representing data validity information, and a signal from the receiver to the sender of a data packet, comprising information representing the ability of the receiver to receive the data. A receiver that is not ready to receive data can block the sending of data by the sender;

- signals delimiting data packets;

- signals of configurable size for transferring data during a clock cycle, not necessarily corresponding to the size of a cell or elementary data quantity. The number of cells conveyed in each cycle, or word, defines the degree of these implementations of the data packet. The degrees of these implementations that are most practical are a quarter, a half, one, two or four cells conveyed in each clock cycle. The cell size depends on the parameters of the communication protocol;

- any signals linked to the service quality of a link or, in other words, signals for favouring the transmission of some messages over others, for favouring the passage of data packets considered priority.

- When necessary, the control information present in the header of a request data packet can be analysed by the recipient element and retransmitted, modified or not, to the initiating element in the associated response data packet.

- The headers of the data packets include an available space reserved for the use of the initiating blocks.

- For example, if a number of transactions of an initiating element are aggregated in a single request data packet at the network interface, instead of saving how the requests have been aggregated in a context queue, the information is encoded on the private bits of the reserved available space in the header of the request data packet.

- When the corresponding response data packet is received by the initiating element, the private data bits that have been transmitted to it are used to separate the response and so terminate this set of transactions initiated by the initiating element.

- Normally, the cell size is fixed by the constraints on the data sizes rather than the constraints on the sizes of the data packet headers. The header therefore normally includes a few unused bits, which can thus be exploited to advantageously replace context memories in the interfaces of the system of interconnections.

- The content of the packet does not depend on the manner in which it is transported. The request and response data packets do not need to have the same serializations, which are defined for each link in turn, by choosing the physical width of the link.

- On changes of format, the widths of the links and the clock timing frequency can change, but the bit rates are adjusted to the slowest elements by the flow control.

- For a change of frequency, a FIFO type queue is used, with two clocks, the size of which is sufficient never to needlessly lose cycles corresponding to the round-trip time of the flow control in the local loop, counted as a number of cycles of the slowest clock. A size of a few words is sufficient for such a queue.

- When the frequency or the size of the link is increased, data holes appear within the data packets, which can reduce the efficiency of certain recipient elements, such as a DRAM memory controller.

- These data holes can be eliminated using a FIFO type queue, which stores all of a data packet before transmitting it.

- However, this is costly in terms of implementation area, and in terms of latency, because, in this case, the queue needs to have a size equal to the maximum size of a data packet supported by the communication protocol.

- However, when the ratio of data holes in the data packet can be predicted, the size of the compaction queue can be reduced using the size information present in the header of the data packets.

- The use of this information and the knowledge of the ratio of data holes makes it possible to anticipate the sending of the data packet with no data hole, when this is possible, and without waiting for the end of the data packet.

- For example, if the bit rate is doubled, the size of the queue and the latency can be reduced by a factor of two.

- In a system of interconnections made up of point-to-point links, the paths between the initiating elements and the recipient elements are partially shared in order to make best use of the wires.

- There are therefore data flow convergence and redistribution points at the nodes of the network of interconnections, which are implemented by means of switches.

- When these nodes form routing cycles, there is a risk of deadlock in the network of interconnections by the appearance of a string of data packets that are mutually blocked. In such a deadlock situation, it is then necessary to reset all of the system.

- It is possible to guarantee, by construction, the elimination of this risk of deadlock, because, with the separation of the requests and the responses, to avoid such loops, it is enough to avoid the presence of such loops in the topology of each of the request and response networks.

- As illustrated in

FIG. 2 , the system ofinterconnections 20 comprises arequest network 21 and aresponse network 22 that are physically separate. - These two physically separate networks do not include common elements, and are represented separately for greater clarity, even if, in reality, these two networks intersect.

Message initiating elements recipient elements request network 21.- The

recipient elements elements - For greater clarity, the two

networks message initiating elements recipient element - The

request network 21 has twoswitches demultiplexer 34 and fourformat converters - The

request network 21 also comprises network interfaces39,40,41 and42, respectively dedicated to the initiatingelements - Furthermore, the

request network 21 comprises network interfaces43,44,45,46 and47, respectively dedicated to therecipient elements - The

response network 22 comprises fourswitches multiplexer 52, and threeformat converters 53,54 and55. Furthermore, theresponse network 22 comprises network interfaces56,57,58,59 and60, respectively dedicated to therecipient elements elements - The

request network 21 comprises threesubnetworks - The

response network 22 comprises threesubnetworks - The

subnetwork 64 comprises the network interfaces39,40,43,44 and45, theswitch 32 and theformat converters 35 and36. - The network interfaces39 and40, and the

format converter 35, can respectively transmit data packets, to theswitch 32, via thelinks - The

switch 32 can transmit data packets to the network interfaces43,44 and45, and to the format converter36, respectively vialinks switch 32 can transmit data packets to another element via alink 77. - The

subnetwork 65 comprises the network interfaces41,42 and46, thedemultiplexer 34, and theswitch 33. The network interface41 can transmit data packets to thedemultiplexer 34 via a link78. - The

demultiplexer 34 can transmit data packets to theformat converters switch 33, respectively vialinks switch 33 via alink 82, and the format converter36 via alink 82a. - The

switch 33 can transmit data packets to thenetwork interface 46 and to theformat converter 38, respectively vialinks 83 and84. - The

subnetwork 66 comprises theformat converters network interface 47. Theformat converters network interface 47 vialinks - The

subnetwork 67 comprises the network interfaces56,57 and58, theswitches format converters 53 and54 and thenetwork interface 61. - The network interfaces57 and58 can transmit data packets to the

switch 49, respectively vialinks 87 and88. Thenetwork interface 56 can transmit data packets to theswitch 48 via alink 89. - The

switch 48 can also receive data packets from an element external to theresponse network 22 via alink 90. - The

switches format converter 53 can respectively transmit data packets to theswitch 50 vialinks switch 50 can respectively transmit data packets to thenetwork interface 61 and to the format converter54 vialinks - The

subnetwork 68 comprises the network interfaces59,62 and63, the switch-51 and themultiplexer 52. - The network interface59 and the format converter55 can respectively transmit data packets to the

switch 51 vialinks 96 and97. - The

switch 51 can respectively transmit data packets to theformat converter 53, to themultiplexer 52 and to the network interface63 vialinks - The format converter54 can transmit data packets to the

multiplexer 52 via alink 101. - Furthermore, the

multiplexer 52 can transmit data packets to the network interface62 via a link102. - The

subnetwork 69 comprises thenetwork interface 60 and the format converter55, and a link103 enabling thenetwork interface 60 to transmit data packets to the format converter55. - Serialization s denotes the ratio of the width of the link (or word size) used to the size of the cell. For the

subnetworks subnetworks subnetworks - In

FIG. 2 , the paths used for a transaction can be followed from left to right. - The initiating element (on the left) sends a request data packet which passes through the request network along a determined path to the recipient element.

- The latter normally returns a response data packet through the response network for the same initiating element (duplicated on the right of the figure).

- However, some initiating elements, such as memories with direct access, or DMA, do not require a response from a recipient element, and are not duplicated on the right of

FIG. 2 , such as the initiatingelement 24. - The request and response networks are not symmetrical. Also, it is advantageous to be able to make independent optimizations of the request and response networks.

- Some elements that make up the network or system of interconnections can advantageously be configured by means of application software, by being able to program the values of software registers accessed by means of a network dedicated to this purpose.

- Such programming is mainly done on system initialization and supports very slow bit rates. Also, it is interesting to use, to this end, a very low cost network. Each software register has its address in this dedicated network, which can be accessed by the request and response networks, with the presence, if necessary, of an interface between this dedicated network and the request and response networks.

- Also, the separation of the routing in the network allows a certain independence in the optimization of each link, which facilitates the design and implementation of a set of IP blocks, or intellectual property blocks, for the elements that make up the network of interconnections.

- These IP blocks are configurable and can be assembled by simply joining up standard physical interfaces end to end to form a transport network. So, this “library” will contain at least the following elements:

- a utility for programming the communication protocol;

- a generator of IP blocks that can be configured for each type of network interface supported;

- a generator of IP blocks for configurable switches, including as parameters the number of inputs, the number of outputs, the types of routing tables, the layers of a pipeline architecture and the arbitration types;

- transport IP blocks for changing the frequency and the format of the links, for compacting the packets or for transporting the packets over long distances with or without pipeline; and

- means required to access the configuration registers via the low cost programming network, also called service network, to configure the IP blocks generated.

- Each generator can, for example, produce descriptions in Verilog or VHDL language that can be synthesized by the standard CAD tools.

- These generators are coded in a language that enables the parameter space to be described easily in a structured manner.

- For example, a generator can support lists of parameters, which can themselves be configured as in the case of the generator of switch IP blocks, for which it is possible to choose an arbitration type for each output, each type of arbiter having its own parameters.

Claims (15)

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| FR0603248AFR2900017B1 (en) | 2006-04-12 | 2006-04-12 | EXTERNAL CHIP FUNCTIONAL BLOCK INTERCONNECTION SYSTEM PROVIDED WITH A SINGLE COMMUNICATION PARAMETRABLE PROTOCOL |

| FR0603248 | 2006-04-12 | ||

| FRFR0603248 | 2006-04-12 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| US20070245044A1true US20070245044A1 (en) | 2007-10-18 |

| US8645557B2 US8645557B2 (en) | 2014-02-04 |

Family

ID=37697978

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| US11/482,175Active2028-12-21US8645557B2 (en) | 2006-04-12 | 2006-07-06 | System of interconnections for external functional blocks on a chip provided with a single configurable communication protocol |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8645557B2 (en) |

| EP (1) | EP1845456B1 (en) |

| AT (1) | ATE428143T1 (en) |

| DE (1) | DE602007000835D1 (en) |

| FR (1) | FR2900017B1 (en) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20100250784A1 (en)* | 2009-03-26 | 2010-09-30 | Terascale Supercomputing Inc. | Addressing Scheme and Message Routing for a Networked Device |

| US20100246581A1 (en)* | 2009-03-26 | 2010-09-30 | Terascale Supercomputing Inc. | Method and Apparatus for Packet Routing |

| US20100246437A1 (en)* | 2009-03-26 | 2010-09-30 | Terascale Supercomputing Inc. | Network Topology |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2921507B1 (en) | 2007-09-26 | 2011-04-15 | Arteris | ELECTRONIC MEMORY DEVICE |

| US12335048B2 (en) | 2021-09-16 | 2025-06-17 | Apple Inc. | Efficient communication in limited resource environments |

| US12245050B2 (en) | 2021-09-16 | 2025-03-04 | Apple Inc. | Canopy coverage determination for improved wireless connectivity |

Citations (58)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US2243851A (en)* | 1940-06-06 | 1941-06-03 | Bell Telephone Labor Inc | Wire line transmission |

| US5274782A (en)* | 1990-08-27 | 1993-12-28 | International Business Machines Corporation | Method and apparatus for dynamic detection and routing of non-uniform traffic in parallel buffered multistage interconnection networks |

| US5313649A (en)* | 1991-05-28 | 1994-05-17 | International Business Machines Corporation | Switch queue structure for one-network parallel processor systems |

| US5424590A (en)* | 1992-06-25 | 1995-06-13 | Fujitsu Limited | Delay time control circuit |

| US5453982A (en)* | 1994-08-29 | 1995-09-26 | Hewlett-Packard Company | Packet control procedure between a host processor and a peripheral unit |

| US5473761A (en)* | 1991-12-17 | 1995-12-05 | Dell Usa, L.P. | Controller for receiving transfer requests for noncontiguous sectors and reading those sectors as a continuous block by interspersing no operation requests between transfer requests |

| US5490253A (en)* | 1990-05-25 | 1996-02-06 | At&T Corp. | Multiprocessor system using odd/even data buses with a timeshared address bus |

| US5495197A (en)* | 1991-08-14 | 1996-02-27 | Advantest Corporation | Variable delay circuit |

| US5541932A (en)* | 1994-06-13 | 1996-07-30 | Xerox Corporation | Circuit for freezing the data in an interface buffer |

| US5541935A (en)* | 1995-05-26 | 1996-07-30 | National Semiconductor Corporation | Integrated circuit with test signal buses and test control circuits |

| US5604775A (en)* | 1994-09-29 | 1997-02-18 | Nec Corporation | Digital phase locked loop having coarse and fine stepsize variable delay lines |

| US5651002A (en)* | 1995-07-12 | 1997-07-22 | 3Com Corporation | Internetworking device with enhanced packet header translation and memory |

| US5764093A (en)* | 1981-11-28 | 1998-06-09 | Advantest Corporation | Variable delay circuit |

| US5784374A (en)* | 1996-02-06 | 1998-07-21 | Advanced Micro Devices, Inc. | Contention resolution system in ATM switch |

| US5844954A (en)* | 1993-02-17 | 1998-12-01 | Texas Instruments Incorporated | Fine resolution digital delay line with coarse and fine adjustment stages |

| US5931926A (en)* | 1995-07-07 | 1999-08-03 | Sun Microsystems, Inc. | Method and apparatus for dynamically calculating degrees of fullness of a synchronous FIFO |

| US6151316A (en)* | 1997-02-14 | 2000-11-21 | Advanced Micro Devices, Inc. | Apparatus and method for synthesizing management packets for transmission between a network switch and a host controller |

| US6211739B1 (en)* | 1997-06-03 | 2001-04-03 | Cypress Semiconductor Corp. | Microprocessor controlled frequency lock loop for use with an external periodic signal |

| US6260152B1 (en)* | 1998-07-30 | 2001-07-10 | Siemens Information And Communication Networks, Inc. | Method and apparatus for synchronizing data transfers in a logic circuit having plural clock domains |

| US6269433B1 (en)* | 1998-04-29 | 2001-07-31 | Compaq Computer Corporation | Memory controller using queue look-ahead to reduce memory latency |

| US6339553B1 (en)* | 1999-09-08 | 2002-01-15 | Mitsubishi Denki Kabushiki Kaisha | Clock generating circuit having additional delay line outside digital DLL loop and semiconductor memory device including the same |

| US6400720B1 (en)* | 1999-06-21 | 2002-06-04 | General Instrument Corporation | Method for transporting variable length and fixed length packets in a standard digital transmission frame |

| US20020087804A1 (en)* | 2000-12-29 | 2002-07-04 | Manoj Khare | Distributed mechanism for resolving cache coherence conflicts in a multi-node computer architecture |

| US20020085582A1 (en)* | 2000-12-28 | 2002-07-04 | Lg Electronics Inc. | System and method for processing multimedia packets for a network |

| US20020136235A1 (en)* | 2001-03-21 | 2002-09-26 | Mats Jarlstedt | Interconnection of signalling nodes |

| US20020196785A1 (en)* | 2001-06-25 | 2002-12-26 | Connor Patrick L. | Control of processing order for received network packets |

| US20030021281A1 (en)* | 2001-07-26 | 2003-01-30 | Kazuyasu Tanaka | Media converter and transmission system using the same |

| US6549047B2 (en)* | 1997-07-29 | 2003-04-15 | Fujitsu Limited | Variable delay circuit and semiconductor integrated circuit device |

| US6651148B2 (en)* | 2000-05-23 | 2003-11-18 | Canon Kabushiki Kaisha | High-speed memory controller for pipelining memory read transactions |

| US6661303B1 (en)* | 1999-11-30 | 2003-12-09 | International Business Machines Corporation | Cross talk suppression in a bidirectional bus |

| US20030227932A1 (en)* | 2002-06-10 | 2003-12-11 | Velio Communications, Inc. | Weighted fair share scheduler for large input-buffered high-speed cross-point packet/cell switches |

| US20040003181A1 (en)* | 2002-06-28 | 2004-01-01 | Cypher Robert E. | System with virtual address networks and split ownership and access right coherence mechanism |

| US20040017820A1 (en)* | 2002-07-29 | 2004-01-29 | Garinger Ned D. | On chip network |

| US6721309B1 (en)* | 1999-05-18 | 2004-04-13 | Alcatel | Method and apparatus for maintaining packet order integrity in parallel switching engine |

| US6738820B2 (en)* | 2000-08-23 | 2004-05-18 | Sony International (Europe) Gmbh | System using home gateway to analyze information received in an email message for controlling devices connected in a home network |

| US20040128413A1 (en)* | 2001-06-08 | 2004-07-01 | Tiberiu Chelcea | Low latency fifo circuits for mixed asynchronous and synchronous systems |

| US6759911B2 (en)* | 2001-11-19 | 2004-07-06 | Mcron Technology, Inc. | Delay-locked loop circuit and method using a ring oscillator and counter-based delay |

| US6778545B1 (en)* | 1998-09-24 | 2004-08-17 | Cisco Technology, Inc. | DSP voice buffersize negotiation between DSPs for voice packet end devices |

| US6812760B1 (en)* | 2003-07-02 | 2004-11-02 | Micron Technology, Inc. | System and method for comparison and compensation of delay variations between fine delay and coarse delay circuits |

| US20040266435A1 (en)* | 2002-10-04 | 2004-12-30 | De Jong Gjalt Gerrit | Access stratum manager |

| US6850842B2 (en)* | 2001-10-31 | 2005-02-01 | Samsung Electronics Co., Ltd. | Navigation system for providing real-time traffic information and traffic information processing method by the same |

| US6850542B2 (en)* | 2000-11-14 | 2005-02-01 | Broadcom Corporation | Linked network switch configuration |

| US20050025169A1 (en)* | 2003-07-22 | 2005-02-03 | Cesar Douady | Device and method for forwarding a message |

| US20050086412A1 (en)* | 2003-07-04 | 2005-04-21 | Cesar Douady | System and method for communicating between modules |

| US20050100014A1 (en)* | 2000-08-09 | 2005-05-12 | Microsoft Corporation | Fast dynamic measurement of bandwidth in a TCP network environment |

| US20050104644A1 (en)* | 2003-10-01 | 2005-05-19 | Luc Montperrus | Digital delay device, digital oscillator clock signal generator and memory interface |

| US6901074B1 (en)* | 1998-12-03 | 2005-05-31 | Secretary Of Agency Of Industrial Science And Technology | Communication method and communications system |

| US20050117589A1 (en)* | 2003-08-13 | 2005-06-02 | Cesar Douady | Method and device for managing priority during the transmission of a message |

| US20050141505A1 (en)* | 2003-11-13 | 2005-06-30 | Cesar Douady | System and method for transmitting a sequence of messages in an interconnection network |

| US6915361B2 (en)* | 2002-10-03 | 2005-07-05 | International Business Machines Corporation | Optimal buffered routing path constructions for single and multiple clock domains systems |

| US20050154843A1 (en)* | 2003-12-09 | 2005-07-14 | Cesar Douady | Method of managing a device for memorizing data organized in a queue, and associated device |

| US20050157717A1 (en)* | 2004-01-21 | 2005-07-21 | Cesar Douady | Method and system for transmitting messages in an interconnection network |

| US20050210325A1 (en)* | 2004-03-02 | 2005-09-22 | Cesar Douady | Method and device for switching between agents |

| US20060041889A1 (en)* | 2002-10-08 | 2006-02-23 | Koninklijke Philips Electronics N.V. | Integrated circuit and method for establishing transactions |

| US20060115088A1 (en)* | 2004-12-01 | 2006-06-01 | Valentine Matthew F | Method and apparatus for end-to-end clear transport protocol |

| US20070002634A1 (en)* | 2005-06-10 | 2007-01-04 | Luc Montperrus | System and method of transmitting data in an electronic circuit |

| US20070081414A1 (en)* | 2005-09-12 | 2007-04-12 | Cesar Douady | System and method of on-circuit asynchronous communication, between synchronous subcircuits |

| US20070110052A1 (en)* | 2005-11-16 | 2007-05-17 | Sophana Kok | System and method for the static routing of data packet streams in an interconnect network |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0388019A (en) | 1989-08-31 | 1991-04-12 | Toshiba Corp | data processing equipment |

| EP0752642B1 (en) | 1995-07-07 | 2001-09-26 | Sun Microsystems, Inc. | Method and apparatus for dynamically calculating degrees of fullness of a synchronous fifo |

| DE60130039T2 (en) | 2000-06-09 | 2008-05-15 | The Trustees Of Columbia University In The City Of New York | LOW-LOW FIFO CIRCUITS FOR MIXED ASYNCHRONOUS AND SYNCHRONOUS SYSTEMS |

| FR2814007B1 (en) | 2000-09-08 | 2003-01-31 | France Telecom | VOLTAGE CONTROL OSCILLATOR |

| US6886048B2 (en) | 2001-11-15 | 2005-04-26 | Hewlett-Packard Development Company, L.P. | Techniques for processing out-of-order requests in a processor-based system |

| US20040088472A1 (en) | 2002-10-31 | 2004-05-06 | Nystuen John M. | Multi-mode memory controller |

- 2006

- 2006-04-12FRFR0603248Apatent/FR2900017B1/ennot_activeExpired - Fee Related

- 2006-07-06USUS11/482,175patent/US8645557B2/enactiveActive

- 2007

- 2007-03-14EPEP07300863Apatent/EP1845456B1/ennot_activeNot-in-force

- 2007-03-14DEDE602007000835Tpatent/DE602007000835D1/ennot_activeExpired - Fee Related

- 2007-03-14ATAT07300863Tpatent/ATE428143T1/ennot_activeIP Right Cessation

Patent Citations (61)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US2243851A (en)* | 1940-06-06 | 1941-06-03 | Bell Telephone Labor Inc | Wire line transmission |

| US5764093A (en)* | 1981-11-28 | 1998-06-09 | Advantest Corporation | Variable delay circuit |

| US5490253A (en)* | 1990-05-25 | 1996-02-06 | At&T Corp. | Multiprocessor system using odd/even data buses with a timeshared address bus |

| US5274782A (en)* | 1990-08-27 | 1993-12-28 | International Business Machines Corporation | Method and apparatus for dynamic detection and routing of non-uniform traffic in parallel buffered multistage interconnection networks |

| US5313649A (en)* | 1991-05-28 | 1994-05-17 | International Business Machines Corporation | Switch queue structure for one-network parallel processor systems |

| US5495197A (en)* | 1991-08-14 | 1996-02-27 | Advantest Corporation | Variable delay circuit |

| US5473761A (en)* | 1991-12-17 | 1995-12-05 | Dell Usa, L.P. | Controller for receiving transfer requests for noncontiguous sectors and reading those sectors as a continuous block by interspersing no operation requests between transfer requests |

| US5424590A (en)* | 1992-06-25 | 1995-06-13 | Fujitsu Limited | Delay time control circuit |

| US5844954A (en)* | 1993-02-17 | 1998-12-01 | Texas Instruments Incorporated | Fine resolution digital delay line with coarse and fine adjustment stages |

| US5541932A (en)* | 1994-06-13 | 1996-07-30 | Xerox Corporation | Circuit for freezing the data in an interface buffer |

| US5453982A (en)* | 1994-08-29 | 1995-09-26 | Hewlett-Packard Company | Packet control procedure between a host processor and a peripheral unit |

| US5604775A (en)* | 1994-09-29 | 1997-02-18 | Nec Corporation | Digital phase locked loop having coarse and fine stepsize variable delay lines |

| US5541935A (en)* | 1995-05-26 | 1996-07-30 | National Semiconductor Corporation | Integrated circuit with test signal buses and test control circuits |

| US5931926A (en)* | 1995-07-07 | 1999-08-03 | Sun Microsystems, Inc. | Method and apparatus for dynamically calculating degrees of fullness of a synchronous FIFO |

| US5651002A (en)* | 1995-07-12 | 1997-07-22 | 3Com Corporation | Internetworking device with enhanced packet header translation and memory |

| US5784374A (en)* | 1996-02-06 | 1998-07-21 | Advanced Micro Devices, Inc. | Contention resolution system in ATM switch |

| US6151316A (en)* | 1997-02-14 | 2000-11-21 | Advanced Micro Devices, Inc. | Apparatus and method for synthesizing management packets for transmission between a network switch and a host controller |

| US6211739B1 (en)* | 1997-06-03 | 2001-04-03 | Cypress Semiconductor Corp. | Microprocessor controlled frequency lock loop for use with an external periodic signal |

| US6549047B2 (en)* | 1997-07-29 | 2003-04-15 | Fujitsu Limited | Variable delay circuit and semiconductor integrated circuit device |

| US6269433B1 (en)* | 1998-04-29 | 2001-07-31 | Compaq Computer Corporation | Memory controller using queue look-ahead to reduce memory latency |

| US6260152B1 (en)* | 1998-07-30 | 2001-07-10 | Siemens Information And Communication Networks, Inc. | Method and apparatus for synchronizing data transfers in a logic circuit having plural clock domains |

| US6778545B1 (en)* | 1998-09-24 | 2004-08-17 | Cisco Technology, Inc. | DSP voice buffersize negotiation between DSPs for voice packet end devices |

| US6901074B1 (en)* | 1998-12-03 | 2005-05-31 | Secretary Of Agency Of Industrial Science And Technology | Communication method and communications system |

| US6721309B1 (en)* | 1999-05-18 | 2004-04-13 | Alcatel | Method and apparatus for maintaining packet order integrity in parallel switching engine |

| US6400720B1 (en)* | 1999-06-21 | 2002-06-04 | General Instrument Corporation | Method for transporting variable length and fixed length packets in a standard digital transmission frame |

| US6339553B1 (en)* | 1999-09-08 | 2002-01-15 | Mitsubishi Denki Kabushiki Kaisha | Clock generating circuit having additional delay line outside digital DLL loop and semiconductor memory device including the same |

| US6661303B1 (en)* | 1999-11-30 | 2003-12-09 | International Business Machines Corporation | Cross talk suppression in a bidirectional bus |

| US6651148B2 (en)* | 2000-05-23 | 2003-11-18 | Canon Kabushiki Kaisha | High-speed memory controller for pipelining memory read transactions |

| US20050108420A1 (en)* | 2000-08-09 | 2005-05-19 | Microsoft Corporation | Fast dynamic measurement of bandwidth in a TCP network environment |

| US20050100014A1 (en)* | 2000-08-09 | 2005-05-12 | Microsoft Corporation | Fast dynamic measurement of bandwidth in a TCP network environment |

| US6738820B2 (en)* | 2000-08-23 | 2004-05-18 | Sony International (Europe) Gmbh | System using home gateway to analyze information received in an email message for controlling devices connected in a home network |

| US6850542B2 (en)* | 2000-11-14 | 2005-02-01 | Broadcom Corporation | Linked network switch configuration |

| US7050431B2 (en)* | 2000-11-14 | 2006-05-23 | Broadcom Corporation | Linked network switch configuration |

| US20020085582A1 (en)* | 2000-12-28 | 2002-07-04 | Lg Electronics Inc. | System and method for processing multimedia packets for a network |

| US20020087804A1 (en)* | 2000-12-29 | 2002-07-04 | Manoj Khare | Distributed mechanism for resolving cache coherence conflicts in a multi-node computer architecture |

| US20020136235A1 (en)* | 2001-03-21 | 2002-09-26 | Mats Jarlstedt | Interconnection of signalling nodes |

| US20040128413A1 (en)* | 2001-06-08 | 2004-07-01 | Tiberiu Chelcea | Low latency fifo circuits for mixed asynchronous and synchronous systems |

| US20020196785A1 (en)* | 2001-06-25 | 2002-12-26 | Connor Patrick L. | Control of processing order for received network packets |

| US20030021281A1 (en)* | 2001-07-26 | 2003-01-30 | Kazuyasu Tanaka | Media converter and transmission system using the same |

| US6850842B2 (en)* | 2001-10-31 | 2005-02-01 | Samsung Electronics Co., Ltd. | Navigation system for providing real-time traffic information and traffic information processing method by the same |

| US6759911B2 (en)* | 2001-11-19 | 2004-07-06 | Mcron Technology, Inc. | Delay-locked loop circuit and method using a ring oscillator and counter-based delay |

| US20030227932A1 (en)* | 2002-06-10 | 2003-12-11 | Velio Communications, Inc. | Weighted fair share scheduler for large input-buffered high-speed cross-point packet/cell switches |

| US20040003181A1 (en)* | 2002-06-28 | 2004-01-01 | Cypher Robert E. | System with virtual address networks and split ownership and access right coherence mechanism |

| US20040017820A1 (en)* | 2002-07-29 | 2004-01-29 | Garinger Ned D. | On chip network |

| US6915361B2 (en)* | 2002-10-03 | 2005-07-05 | International Business Machines Corporation | Optimal buffered routing path constructions for single and multiple clock domains systems |

| US20040266435A1 (en)* | 2002-10-04 | 2004-12-30 | De Jong Gjalt Gerrit | Access stratum manager |

| US20060041889A1 (en)* | 2002-10-08 | 2006-02-23 | Koninklijke Philips Electronics N.V. | Integrated circuit and method for establishing transactions |

| US6812760B1 (en)* | 2003-07-02 | 2004-11-02 | Micron Technology, Inc. | System and method for comparison and compensation of delay variations between fine delay and coarse delay circuits |

| US20050086412A1 (en)* | 2003-07-04 | 2005-04-21 | Cesar Douady | System and method for communicating between modules |

| US20050025169A1 (en)* | 2003-07-22 | 2005-02-03 | Cesar Douady | Device and method for forwarding a message |

| US20050117589A1 (en)* | 2003-08-13 | 2005-06-02 | Cesar Douady | Method and device for managing priority during the transmission of a message |

| US20050104644A1 (en)* | 2003-10-01 | 2005-05-19 | Luc Montperrus | Digital delay device, digital oscillator clock signal generator and memory interface |

| US7148728B2 (en)* | 2003-10-01 | 2006-12-12 | Arteris | Digital delay device, digital oscillator clock signal generator and memory interface |

| US20050141505A1 (en)* | 2003-11-13 | 2005-06-30 | Cesar Douady | System and method for transmitting a sequence of messages in an interconnection network |

| US20050154843A1 (en)* | 2003-12-09 | 2005-07-14 | Cesar Douady | Method of managing a device for memorizing data organized in a queue, and associated device |

| US20050157717A1 (en)* | 2004-01-21 | 2005-07-21 | Cesar Douady | Method and system for transmitting messages in an interconnection network |

| US20050210325A1 (en)* | 2004-03-02 | 2005-09-22 | Cesar Douady | Method and device for switching between agents |

| US20060115088A1 (en)* | 2004-12-01 | 2006-06-01 | Valentine Matthew F | Method and apparatus for end-to-end clear transport protocol |

| US20070002634A1 (en)* | 2005-06-10 | 2007-01-04 | Luc Montperrus | System and method of transmitting data in an electronic circuit |

| US20070081414A1 (en)* | 2005-09-12 | 2007-04-12 | Cesar Douady | System and method of on-circuit asynchronous communication, between synchronous subcircuits |

| US20070110052A1 (en)* | 2005-11-16 | 2007-05-17 | Sophana Kok | System and method for the static routing of data packet streams in an interconnect network |

Cited By (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20100250784A1 (en)* | 2009-03-26 | 2010-09-30 | Terascale Supercomputing Inc. | Addressing Scheme and Message Routing for a Networked Device |

| US20100246581A1 (en)* | 2009-03-26 | 2010-09-30 | Terascale Supercomputing Inc. | Method and Apparatus for Packet Routing |

| WO2010108263A1 (en)* | 2009-03-26 | 2010-09-30 | Terascale Supercomputing Inc. | Method and apparatus for packet routing |

| US20100246437A1 (en)* | 2009-03-26 | 2010-09-30 | Terascale Supercomputing Inc. | Network Topology |

| US7957385B2 (en) | 2009-03-26 | 2011-06-07 | Terascale Supercomputing Inc. | Method and apparatus for packet routing |

| US7957400B2 (en) | 2009-03-26 | 2011-06-07 | Terascale Supercomputing Inc. | Hierarchical network topology |

| US20110206053A1 (en)* | 2009-03-26 | 2011-08-25 | Terascale Supercomputing Inc. | Hierarchical Network Topology |

| CN102449961A (en)* | 2009-03-26 | 2012-05-09 | 超级计算公司 | Method and apparatus for packet routing |

| US8457135B2 (en) | 2009-03-26 | 2013-06-04 | Terascale Supercomputing Inc. | Hierarchical network topology |

Also Published As

| Publication number | Publication date |

|---|---|

| EP1845456A1 (en) | 2007-10-17 |

| FR2900017A1 (en) | 2007-10-19 |

| FR2900017B1 (en) | 2008-10-31 |

| DE602007000835D1 (en) | 2009-05-20 |

| EP1845456B1 (en) | 2009-04-08 |

| US8645557B2 (en) | 2014-02-04 |

| ATE428143T1 (en) | 2009-04-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US12306773B2 (en) | Multiprocessor system with improved secondary interconnection network | |

| CN100367730C (en) | an interconnected system | |

| EP3776231B1 (en) | Procedures for implementing source based routing within an interconnect fabric on a system on chip | |

| Agarwal et al. | Survey of network on chip (noc) architectures & contributions | |

| Stefan et al. | daelite: A tdm noc supporting qos, multicast, and fast connection set-up | |

| KR101016987B1 (en) | Integrated circuit and method for exchanging data | |

| US20060209846A1 (en) | Globally asynchronous communication architecture for system on chip | |

| US20070186018A1 (en) | Integrated circuit and method of communication service mapping | |

| US8645557B2 (en) | System of interconnections for external functional blocks on a chip provided with a single configurable communication protocol | |

| JP2008543151A (en) | Communication resource allocation electronic device and method | |

| US7643477B2 (en) | Buffering data packets according to multiple flow control schemes | |

| KR20070010152A (en) | Integrated circuits and methods for issuing transactions | |

| US8086800B2 (en) | Integrated circuit and method for buffering to optimize burst length in networks on chips | |

| WO2005088912A1 (en) | Integrated circuit and method for packet switching control | |

| CN120321204B (en) | Network architecture based on multi-core transmission | |

| WO2006048826A1 (en) | Integrated circuit and method for data transfer in a network on chip environment | |

| Gaizauskas et al. | Formation of multiple filaments in transparent solids | |

| Nambinina et al. | Extension of the LISNoC (Network-on-Chip) | |

| WO2006048822A1 (en) | Integrated circuit and method for providing guarantees at application level |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| AS | Assignment | Owner name:ARTERIS, FRANCE Free format text:ASSIGNMENT OF ASSIGNORS INTEREST;ASSIGNOR:BOUCARD, PHILIPPE;REEL/FRAME:018752/0495 Effective date:20061211 | |

| AS | Assignment | Owner name:QUALCOMM TECHNOLOGIES, INC., CALIFORNIA Free format text:ASSIGNMENT OF ASSIGNORS INTEREST;ASSIGNOR:ARTERIS, SAS;REEL/FRAME:031437/0901 Effective date:20131011 | |

| FEPP | Fee payment procedure | Free format text:PAT HOLDER NO LONGER CLAIMS SMALL ENTITY STATUS, ENTITY STATUS SET TO UNDISCOUNTED (ORIGINAL EVENT CODE: STOL); ENTITY STATUS OF PATENT OWNER: LARGE ENTITY Free format text:PAYOR NUMBER ASSIGNED (ORIGINAL EVENT CODE: ASPN); ENTITY STATUS OF PATENT OWNER: LARGE ENTITY | |

| STCF | Information on status: patent grant | Free format text:PATENTED CASE | |

| FPAY | Fee payment | Year of fee payment:4 | |

| FEPP | Fee payment procedure | Free format text:7.5 YR SURCHARGE - LATE PMT W/IN 6 MO, LARGE ENTITY (ORIGINAL EVENT CODE: M1555); ENTITY STATUS OF PATENT OWNER: LARGE ENTITY | |

| MAFP | Maintenance fee payment | Free format text:PAYMENT OF MAINTENANCE FEE, 8TH YEAR, LARGE ENTITY (ORIGINAL EVENT CODE: M1552); ENTITY STATUS OF PATENT OWNER: LARGE ENTITY Year of fee payment:8 | |

| MAFP | Maintenance fee payment | Free format text:PAYMENT OF MAINTENANCE FEE, 12TH YEAR, LARGE ENTITY (ORIGINAL EVENT CODE: M1553); ENTITY STATUS OF PATENT OWNER: LARGE ENTITY Year of fee payment:12 |