US20070183331A1 - Method and system for providing indeterminate read data latency in a memory system - Google Patents

Method and system for providing indeterminate read data latency in a memory systemDownload PDFInfo

- Publication number

- US20070183331A1 US20070183331A1US11/736,196US73619607AUS2007183331A1US 20070183331 A1US20070183331 A1US 20070183331A1US 73619607 AUS73619607 AUS 73619607AUS 2007183331 A1US2007183331 A1US 2007183331A1

- Authority

- US

- United States

- Prior art keywords

- data packet

- upstream

- memory

- data

- memory controller

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Abandoned

Links

Images

Classifications

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1605—Handling requests for interconnection or transfer for access to memory bus based on arbitration

- G06F13/1652—Handling requests for interconnection or transfer for access to memory bus based on arbitration in a multiprocessor architecture

- G06F13/1657—Access to multiple memories

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1668—Details of memory controller

- G06F13/1673—Details of memory controller using buffers

Definitions

- This inventionrelates to memory systems comprised of hub devices connected to a memory controller by a daisy chained channel.

- the hub devicesare attached to, or reside upon, memory modules that contain memory devices. More particularly, this invention relates to the flow control of read data and the identification of read data returned to the controller by each hub device.

- the memory modulescontain a hub device and multiple memory devices.

- the hub devicefully buffers command, address and data signals between the memory controller and the memory devices.

- the flow of read datais controlled using either a leveled latency or position dependant latency technique. In both cases, the memory controller is able to predict the return time of read data requested from the memory modules and to schedule commands to avoid collisions as read data is merged onto the controller interface by each memory module.

- the memory controlleris able to issue a read data delay adder along with the read command. This instructs the targeted hub device to add additional delay to the return of read data in order to simplify the issuing of commands and to avoid collisions.

- the read datamust be returned in the order in which it was requested. Further, the total read data latency must be completely predictable by the memory controller. During run time operations, these two restrictions result in additional gaps being added to packets of read data that are returned from the memory modules. This adds latency to the average read operation.

- hubsare not able to use indeterminate techniques to return read data faster or slower than normal. These techniques include, but are not limited to, caching read data locally, reading memory devices speculatively, independently managing memory device address pages, data compression, etc.

- Exemplary embodimentsinclude a method for providing indeterminate read data latency.

- the methodincludes determining if a local data packet has been received. If a local data packet has been received, then the local data packet is stored into a buffer device.

- the methodalso includes determining if the buffer device contains a data packet and determining if an upstream driver for transmitting data packets to a memory controller via an upstream channel is idle. If the buffer contains a data packet and the upstream driver is idle, then the data packet is transmitted to the upstream driver.

- the methodfurther includes determining if an upstream data packet has been received.

- the upstream data packetis in a frame format that includes a frame start indicator and an identification tag for use by the memory controller in associating the upstream data packet with its corresponding read instruction.

- the upstream data packetis stored into the buffer device. If an upstream data packet has been received and the buffer device does not contain a data packet and the upstream driver is idle, then the upstream data packet is transmitted to the upstream driver. If the upstream driver is not idle, then any data packets in progress are continued being transmitted to the upstream driver.

- Exemplary embodimentsinclude a hub device in a memory system.

- the hub deviceincludes a device for receiving data packets, an upstream driver for transmitting data packets to a memory controller via an upstream channel and a mechanism including instructions for facilitating indeterminate read data latency.

- the device for receiving data packetsincludes an upstream receiver for receiving upstream data packets from a downstream hub device and a memory interface for receiving local data packets from a local storage device.

- Each data packetis in a frame format that includes a frame start indicator and an identification tag for use by a memory controller in associating the data packet with its corresponding read instruction.

- the instructions on the mechanismfacilitate determining if a local data packet has been received. If a local data packet has been received, then the local data packet is stored into a buffer device.

- the instructionsalso facilitate determining if the buffer device contains a data packet and determining if the upstream driver is idle. If the buffer contains a data packet and the upstream driver is idle, then the data packet is transmitted to the upstream driver.

- the instructionsfurther facilitate determining if an upstream data packet has been received. If an upstream data packet has been received and the upstream driver is not idle, then the upstream data packet is stored into the buffer device. If an upstream data packet has been received and the buffer device does not contain a data packet and the upstream driver is idle, then the upstream data packet is transmitted to the upstream driver. If the upstream driver is not idle, then any data packets in progress are continued being transmitted to the upstream driver.

- Exemplary embodimentsinclude a memory subsystem with one or more memory modules.

- the memory modulesinclude one or more memory devices connected to a memory controller by a daisy chained channel.

- the read datais returned to the memory controller using a frame format that includes an identification tag and frame start indicator.

- the memory systemalso includes one or more hub devices on the memory modules for buffering address, commands and data.

- the hub devicesinclude controller channel buffers that are used in conjunction with a preemptive local data merge algorithm to minimize read data latency and enable indeterminate read data return times to the memory controller.

- FIG. 1For exemplary embodiments, include a memory system with one or more memory modules.

- the memory modulesinclude memory devices that are connected to a memory controller by a daisy chained channel.

- the read datais returned to the memory controller using a frame format that includes an identification tag and frame start indicator.

- the memory systemalso includes one or more hub devices connected to the memory modules for buffering address, commands and data.

- the hub devicesinclude controller channel buffers that are used in conjunction with a preemptive local data merge algorithm to minimize read data latency and enable indeterminate read data return times to the memory controller.

- FIG. 1depicts an exemplary memory system with multiple levels of daisy chained memory modules with point-to-point connections;

- FIG. 2depicts an exemplary memory system with hub devices that are connected to a memory modules and to a memory controller by a daisy chained channel;

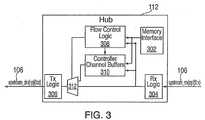

- FIG. 3depicts a hub logic device that may be utilized by exemplary embodiments

- FIG. 4is a exemplary process flow implemented by the hub logic device in exemplary embodiments.

- FIG. 5is a read data format that may be utilized by exemplary embodiments.

- Exemplary embodimentsutilize controller channel buffers (CCBs), read data frame formats with identification tags and a preemptive data merge technique to enable minimized and indeterminate read data latency.

- CBscontroller channel buffers

- Exemplary embodimentsallow memory modules to return read data to a memory controller at an unpredicted time.

- Identification tag informationis added to the read data packet to indicate the read command that the data is a result of, as well as the hub where the data was read.

- the identification tag informationis utilized by the controller to match the read data packet to the read commands issued by the controller. By using the identification tag information, read data can be returned in an order that is different from the issue order of the corresponding read commands.

- Exemplary embodimentsalso provide a preemptive data merge process to prevent data collisions on the upstream channel when implementing the indeterminate read data latency.

- a CCBis added to the hub device to temporarily store read data.

- the datais transferred from the memory interface to the buffer.

- the hub devicedetects that an upstream data packet (i.e., a data packet being sent to the controller from a hub device that is downstream from the detecting hub device) is not in the middle of being transferred into the detecting hub device via an upstream channel (it typically takes several transfers to send the entire data packet)

- the detecting hub devicechecks to see if there is a read data packet in its CCB that is waiting to be sent upstream.

- the hub deviceIf the hub device detects a read data packet in the CCB it drives the read data packet from the CCB onto the upstream data bus. In the meantime, if a new upstream data packet is received via the upstream data bus, the data packet is stored in the CCB on the hub device. In this manner, data packets coming upstream do not collide with data packets being sent upstream from the CCB on the hub device. In the case where there is more than one data packet in the CCB, a variety of methods may be implemented to determine which data packet to send next (e.g., the data packet from the oldest read command may be sent first).

- Exemplary embodimentsapply to memory systems constructed of one or more memory modules 110 that are connected to a memory controller 102 by a daisy chained memory channel 114 as depicted in FIG. 1 .

- the memory modules 110contain both a hub device 112 that buffers commands, address and data signals to and from the controller memory channel 114 as well as one or more memory devices 108 connected to the hub device 112 .

- the downstream portion of the memory channel 114 , the downstream channel 104transmits write data and memory operation commands to the hub devices 112 .

- the upstream portion of the controller channel 114 , the upstream channel 106returns requested read data (referred to herein as upstream data packets).

- FIG. 2depicts an alternate exemplary embodiment that includes a memory system constructed of one or more memory modules 110 connected to hub devices 112 that are further connected to a memory controller 102 by a daisy chained memory channel 114 .

- the hub device 112is not located on the memory module 110 ; instead the hub device 112 is in communication with the memory module 110 .

- the memory modules 110may be in communication with the hub devices 112 via multi-drop connections and/or point-to-point connections.

- Other hardware configurationsare possible, for example exemplary embodiments may utilize only a single level of daisy chained hub devices 112 and/or memory modules 110 .

- FIG. 3depicts a hub device 112 with flow control logic 308 utilized by exemplary embodiments to perform the processing described herein.

- the hub device 112 and the components within the hub device 112may be implemented in hardware and/or software.

- the hub device 112receives upstream data packets on the upstream channel 104 via the receiver logic 304 (also referred to herein as an upstream receiver).

- the upstream data packetsare data packets being sent to the controller 102 from a hub device 112 that is downstream from the receiving hub device 112 .

- An upstream data packetcan be sent to the driver logic 306 (also referred to herein as the upstream driver) to be driven towards the controller 102 on the upstream channel 106 or, if the upstream channel 106 is busy, the upstream data packet can be temporarily stored in the CCB 310 on the hub device 112 .

- the destination of the upstream data packetis determined by the flow control logic 308 and implemented by sending a signal to the local data multiplexer 312 .

- CCBs 310reside in the hub device 112 and safely capture upstream data packet transfers (via the receiver logic 304 ) that are shunted into the CCB 310 while the hub device 112 is merging its local data packets onto the upstream channel 106 .

- Local data packetsare data packets that are read from memory devices 108 attached to the memory module 110 being directed by the hub device 112 . These memory devices 108 are also referred to herein as local storage devices. The data read from the local storage devices, the local data packets, are formatted for return on an upstream controller interface via the upstream driver and stored in the CCB 310 .

- the formattingincludes serializing the local data packet into the proper frame format (e.g., see exemplary frame format depicted in FIG. 5 ), and inserting values into the identification tag (sourced from the read request), first transfer field, and bus cyclical redundancy code (CRC) field.

- the formatting of the local data packetis performed as part of storing the local data packet into the CCB 310 .

- a data packetWhen a data packet is received at the memory interface 302 , it is stored into the CCB 310 while the local data packets are waiting to be merged onto the upstream channel 106 (via the driver logic 306 ).

- the identification tag within the data packetallows the memory controller 102 to correlate a returned read data packet with its corresponding read data request command.

- the data packetalso contains a small, easy to decode ‘start’, or first transfer (‘ft’) field (also referred to herein as a frame start indicator) delivered near the beginning of an upstream read data frame (data packets are formatted as read data frames) which indicates that a read data frame is present in the data packet. This is used by the flow control logic 308 in the hub device 112 to monitor the channel read data activity.

- the hub device 112When there is data in the CCBs 310 from either a local read operation or from a previously shunted read data packet from a downstream hub device (the data packets in the CCB are referred to herein as stored data packets), the hub device 112 will merge it onto the upstream channel 106 via the driver logic 306 as soon as it is allowed. The hub device 112 merges local data onto the upstream channel 106 whenever the upstream channel 106 is idle, or immediately following the last transfer of a data packet that is currently in progress.

- Read data frameswill never be bisected using this method, but read data frames that are in flight on the upstream channel 106 that have not yet arrived at a hub device's 112 local data multiplexer 312 may be preempted and shunted into the CCB 310 . This allows gaps in read data on the upstream channel 106 to be minimized which increases bus efficiency and results in reduced average read data latency under real world work load conditions.

- the hub device 112can be configured to send the read data packet corresponding to the earliest read command. This minimizes undue latency on read requests issued to hub devices 112 that are many daisy chain positions away from the memory controller 102 .

- Other CCB 310 unload prioritization algorithmsmay also be implemented.

- the identification tag field of the read data framemay contain a priority field. The priority field can be used to guide the unloading of the CCBs 310 .

- priority informationmay be delivered as the read data is requested.

- Hub devices 112can then compare the identification tag to previously recorded priority information to determine the location in the CCB 310 to send next.

- a methodmay also be employed that occasionally sends lower priority data before high priority data to ensure that low priority data is not completely stalled by requests that have been tagged with a higher priority.

- FIG. 4is a process flow that is facilitated by the flow control logic 308 located in the hub device 112 in exemplary embodiments.

- the process depicted in FIG. 4performs preemptive local data merge and may be implemented by a mechanism including hardware and/or software instructions such as a finite state machine in the flow control logic 308 .

- the processstarts at block 402 and is repeated, in exemplary embodiments, on a periodic basis (e.g., after each controller channel transfer, or upstream channel cycle).

- any local read data packetsi.e., from memory devices 108 on memory modules 110 attached to the hub device 112

- the memory interface 302are loaded into the CCB 310 .

- the flow control logic 308is aware of and managing the upstream driving of local read data.

- block 408is performed to determine if an upstream channel operation is in process (i.e., is an upstream data packet or a local read data packet in the middle of being driven onto the upstream channel 106 via the driver logic 306 ). Processing continues at block 412 if an upstream channel operation is in process (i.e., the driver is busy). At block 412 , upstream read data packets are routed from the receiver logic 304 to the driver logic 306 by setting the local data multiplexer 312 to send the upstream data packet to the driver logic 306 .

- processingcontinues at block 410 if an upstream channel operation is not in process (i.e., the driver is idle) and there is data in the CCB 310 .

- data from the CCB 310is driven onto the upstream channel 106 while any data packets received in the receiver logic 304 from the upstream channel 106 are shunted (stored) into the next available CCB 310 location.

- the shuntingis performed by the flow control logic 308 directing the upstream data packets to be loaded into the CCB 310 .

- Processingthen continues at 414 which sends processing back to block 404 at the next upstream channel cycle.

- FIG. 5is an exemplary read data frame format for upstream data packets and local read data packets on the upstream channel 106 .

- the frame format depicted in FIG. 5uses twenty-one signal lanes and each packet includes sixteen transfers. It includes a one bit first start indicator 502 and an identification tag 504 , as well as 256 bits (32 B) of read data 506 with a bus CRCs 508 for transmission error detection.

- Other combinations of signal lanes and transfer depthscan be used to create frame formats that include a frame start indicator, read data identification tag and read data that are compatible with this invention.

- Exemplary embodimentspertain to a computer memory system constructed of daisy chained hub logic devices connected to, or contained upon, memory modules.

- the hubsare daisy chained on a memory controller channel and are further attached to memory devices on the memory modules.

- the memory controllerissues requests for read data to the hubs which merge this read data from the memory modules onto the memory channel.

- the hubsare able to return read data at a time unpredicted by the memory controller, and at a time that may preempt a read request that had been issued earlier, without loosing or corrupting any of the read data returned on the channel to the memory controller.

- Exemplary embodimentsmay be utilized to optimize average read data latency by more fully utilizing the upstream channel.

- CCBsread data frame formats with identification tags and a preemptive data merge technique, indeterminate read data latency may be performed to more fully utilize the controller channel.

- the embodiments of the inventionmay be embodied in the form of computer-implemented processes and apparatuses for practicing those processes.

- Embodiments of the inventionmay also be embodied in the form of computer program code containing instructions embodied in tangible media, such as floppy diskettes, CD-ROMs, hard drives, or any other computer-readable storage medium, wherein, when the computer program code is loaded into and executed by a computer, the computer becomes an apparatus for practicing the invention.

- the present inventioncan also be embodied in the form of computer program code, for example, whether stored in a storage medium, loaded into and/or executed by a computer, or transmitted over some transmission medium, such as over electrical wiring or cabling, through fiber optics, or via electromagnetic radiation, wherein, when the computer program code is loaded into and executed by a computer, the computer becomes an apparatus for practicing the invention.

- computer program code segmentsconfigure the microprocessor to create specific logic circuits.

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Information Transfer Systems (AREA)

- Small-Scale Networks (AREA)

- Data Exchanges In Wide-Area Networks (AREA)

- Communication Control (AREA)

Abstract

Description

- This application is a continuation of U.S. patent application Ser. No. 11/289,193 filed Nov. 28, 2005, the contents of which are incorporated by reference herein in their entirety.

- This invention relates to memory systems comprised of hub devices connected to a memory controller by a daisy chained channel. The hub devices are attached to, or reside upon, memory modules that contain memory devices. More particularly, this invention relates to the flow control of read data and the identification of read data returned to the controller by each hub device.

- Many high performance computing main memory systems use multiple fully buffered memory modules connected to a memory controller by one or more channels. The memory modules contain a hub device and multiple memory devices. The hub device fully buffers command, address and data signals between the memory controller and the memory devices. The flow of read data is controlled using either a leveled latency or position dependant latency technique. In both cases, the memory controller is able to predict the return time of read data requested from the memory modules and to schedule commands to avoid collisions as read data is merged onto the controller interface by each memory module.

- In some cases, the memory controller is able to issue a read data delay adder along with the read command. This instructs the targeted hub device to add additional delay to the return of read data in order to simplify the issuing of commands and to avoid collisions. In all cases, the read data must be returned in the order in which it was requested. Further, the total read data latency must be completely predictable by the memory controller. During run time operations, these two restrictions result in additional gaps being added to packets of read data that are returned from the memory modules. This adds latency to the average read operation. In addition, hubs are not able to use indeterminate techniques to return read data faster or slower than normal. These techniques include, but are not limited to, caching read data locally, reading memory devices speculatively, independently managing memory device address pages, data compression, etc.

- To optimize average read data latency under real workload conditions, and to enable advanced hub device capabilities, what is needed is a way to allow memory modules to return read data to the memory controller at an unpredicted time. This must be done in a way that does not corrupt read data and that allows the memory controller to identify each read data packet. Preventing data corruption by avoiding data collisions is especially complicated as hub devices merge local read data onto a cascaded memory controller channel.

- Exemplary embodiments include a method for providing indeterminate read data latency. The method includes determining if a local data packet has been received. If a local data packet has been received, then the local data packet is stored into a buffer device. The method also includes determining if the buffer device contains a data packet and determining if an upstream driver for transmitting data packets to a memory controller via an upstream channel is idle. If the buffer contains a data packet and the upstream driver is idle, then the data packet is transmitted to the upstream driver. The method further includes determining if an upstream data packet has been received. The upstream data packet is in a frame format that includes a frame start indicator and an identification tag for use by the memory controller in associating the upstream data packet with its corresponding read instruction. If an upstream data packet has been received and the upstream driver is not idle, then the upstream data packet is stored into the buffer device. If an upstream data packet has been received and the buffer device does not contain a data packet and the upstream driver is idle, then the upstream data packet is transmitted to the upstream driver. If the upstream driver is not idle, then any data packets in progress are continued being transmitted to the upstream driver.

- Exemplary embodiments include a hub device in a memory system. The hub device includes a device for receiving data packets, an upstream driver for transmitting data packets to a memory controller via an upstream channel and a mechanism including instructions for facilitating indeterminate read data latency. The device for receiving data packets includes an upstream receiver for receiving upstream data packets from a downstream hub device and a memory interface for receiving local data packets from a local storage device. Each data packet is in a frame format that includes a frame start indicator and an identification tag for use by a memory controller in associating the data packet with its corresponding read instruction. The instructions on the mechanism facilitate determining if a local data packet has been received. If a local data packet has been received, then the local data packet is stored into a buffer device. The instructions also facilitate determining if the buffer device contains a data packet and determining if the upstream driver is idle. If the buffer contains a data packet and the upstream driver is idle, then the data packet is transmitted to the upstream driver. The instructions further facilitate determining if an upstream data packet has been received. If an upstream data packet has been received and the upstream driver is not idle, then the upstream data packet is stored into the buffer device. If an upstream data packet has been received and the buffer device does not contain a data packet and the upstream driver is idle, then the upstream data packet is transmitted to the upstream driver. If the upstream driver is not idle, then any data packets in progress are continued being transmitted to the upstream driver.

- Exemplary embodiments include a memory subsystem with one or more memory modules. The memory modules include one or more memory devices connected to a memory controller by a daisy chained channel. The read data is returned to the memory controller using a frame format that includes an identification tag and frame start indicator. The memory system also includes one or more hub devices on the memory modules for buffering address, commands and data. The hub devices include controller channel buffers that are used in conjunction with a preemptive local data merge algorithm to minimize read data latency and enable indeterminate read data return times to the memory controller.

- Further exemplary embodiments include a memory system with one or more memory modules. The memory modules include memory devices that are connected to a memory controller by a daisy chained channel. The read data is returned to the memory controller using a frame format that includes an identification tag and frame start indicator. The memory system also includes one or more hub devices connected to the memory modules for buffering address, commands and data. The hub devices include controller channel buffers that are used in conjunction with a preemptive local data merge algorithm to minimize read data latency and enable indeterminate read data return times to the memory controller.

- Referring now to the drawings wherein like elements are numbered alike in the several FIGURES:

FIG. 1 depicts an exemplary memory system with multiple levels of daisy chained memory modules with point-to-point connections;FIG. 2 depicts an exemplary memory system with hub devices that are connected to a memory modules and to a memory controller by a daisy chained channel;FIG. 3 depicts a hub logic device that may be utilized by exemplary embodiments;FIG. 4 is a exemplary process flow implemented by the hub logic device in exemplary embodiments; andFIG. 5 is a read data format that may be utilized by exemplary embodiments.- Exemplary embodiments utilize controller channel buffers (CCBs), read data frame formats with identification tags and a preemptive data merge technique to enable minimized and indeterminate read data latency. Exemplary embodiments allow memory modules to return read data to a memory controller at an unpredicted time. Identification tag information is added to the read data packet to indicate the read command that the data is a result of, as well as the hub where the data was read. The identification tag information is utilized by the controller to match the read data packet to the read commands issued by the controller. By using the identification tag information, read data can be returned in an order that is different from the issue order of the corresponding read commands.

- Exemplary embodiments also provide a preemptive data merge process to prevent data collisions on the upstream channel when implementing the indeterminate read data latency. A CCB is added to the hub device to temporarily store read data. When a memory device on the memory module reads data, the data is transferred from the memory interface to the buffer. When the hub device detects that an upstream data packet (i.e., a data packet being sent to the controller from a hub device that is downstream from the detecting hub device) is not in the middle of being transferred into the detecting hub device via an upstream channel (it typically takes several transfers to send the entire data packet), the detecting hub device checks to see if there is a read data packet in its CCB that is waiting to be sent upstream. If the hub device detects a read data packet in the CCB it drives the read data packet from the CCB onto the upstream data bus. In the meantime, if a new upstream data packet is received via the upstream data bus, the data packet is stored in the CCB on the hub device. In this manner, data packets coming upstream do not collide with data packets being sent upstream from the CCB on the hub device. In the case where there is more than one data packet in the CCB, a variety of methods may be implemented to determine which data packet to send next (e.g., the data packet from the oldest read command may be sent first).

- Exemplary embodiments apply to memory systems constructed of one or

more memory modules 110 that are connected to amemory controller 102 by a daisy chainedmemory channel 114 as depicted inFIG. 1 . Thememory modules 110 contain both ahub device 112 that buffers commands, address and data signals to and from thecontroller memory channel 114 as well as one ormore memory devices 108 connected to thehub device 112. The downstream portion of thememory channel 114, thedownstream channel 104, transmits write data and memory operation commands to thehub devices 112. The upstream portion of thecontroller channel 114, theupstream channel 106, returns requested read data (referred to herein as upstream data packets). FIG. 2 depicts an alternate exemplary embodiment that includes a memory system constructed of one ormore memory modules 110 connected tohub devices 112 that are further connected to amemory controller 102 by a daisy chainedmemory channel 114. In this embodiment, thehub device 112 is not located on thememory module 110; instead thehub device 112 is in communication with thememory module 110. As depicted inFIG. 2 , thememory modules 110 may be in communication with thehub devices 112 via multi-drop connections and/or point-to-point connections. Other hardware configurations are possible, for example exemplary embodiments may utilize only a single level of daisy chainedhub devices 112 and/ormemory modules 110.FIG. 3 depicts ahub device 112 withflow control logic 308 utilized by exemplary embodiments to perform the processing described herein. Thehub device 112 and the components within thehub device 112 may be implemented in hardware and/or software. Thehub device 112 receives upstream data packets on theupstream channel 104 via the receiver logic304 (also referred to herein as an upstream receiver). The upstream data packets are data packets being sent to thecontroller 102 from ahub device 112 that is downstream from the receivinghub device 112. An upstream data packet can be sent to the driver logic306 (also referred to herein as the upstream driver) to be driven towards thecontroller 102 on theupstream channel 106 or, if theupstream channel 106 is busy, the upstream data packet can be temporarily stored in theCCB 310 on thehub device 112. The destination of the upstream data packet is determined by theflow control logic 308 and implemented by sending a signal to thelocal data multiplexer 312.- In exemplary embodiments,

CCBs 310, or buffer devices, reside in thehub device 112 and safely capture upstream data packet transfers (via the receiver logic304) that are shunted into theCCB 310 while thehub device 112 is merging its local data packets onto theupstream channel 106. Local data packets are data packets that are read frommemory devices 108 attached to thememory module 110 being directed by thehub device 112. Thesememory devices 108 are also referred to herein as local storage devices. The data read from the local storage devices, the local data packets, are formatted for return on an upstream controller interface via the upstream driver and stored in theCCB 310. The formatting includes serializing the local data packet into the proper frame format (e.g., see exemplary frame format depicted inFIG. 5 ), and inserting values into the identification tag (sourced from the read request), first transfer field, and bus cyclical redundancy code (CRC) field. In exemplary embodiments, the formatting of the local data packet is performed as part of storing the local data packet into theCCB 310. - When a data packet is received at the

memory interface 302, it is stored into theCCB 310 while the local data packets are waiting to be merged onto the upstream channel106 (via the driver logic306). The identification tag within the data packet allows thememory controller 102 to correlate a returned read data packet with its corresponding read data request command. The data packet also contains a small, easy to decode ‘start’, or first transfer (‘ft’) field (also referred to herein as a frame start indicator) delivered near the beginning of an upstream read data frame (data packets are formatted as read data frames) which indicates that a read data frame is present in the data packet. This is used by theflow control logic 308 in thehub device 112 to monitor the channel read data activity. - When there is data in the

CCBs 310 from either a local read operation or from a previously shunted read data packet from a downstream hub device (the data packets in the CCB are referred to herein as stored data packets), thehub device 112 will merge it onto theupstream channel 106 via thedriver logic 306 as soon as it is allowed. Thehub device 112 merges local data onto theupstream channel 106 whenever theupstream channel 106 is idle, or immediately following the last transfer of a data packet that is currently in progress. Read data frames will never be bisected using this method, but read data frames that are in flight on theupstream channel 106 that have not yet arrived at a hub device's112 local data multiplexer312 may be preempted and shunted into theCCB 310. This allows gaps in read data on theupstream channel 106 to be minimized which increases bus efficiency and results in reduced average read data latency under real world work load conditions. - When there are multiple read data packets present in the

CCBs 310, thehub device 112 can be configured to send the read data packet corresponding to the earliest read command. This minimizes undue latency on read requests issued tohub devices 112 that are many daisy chain positions away from thememory controller 102.Other CCB 310 unload prioritization algorithms may also be implemented. For example, the identification tag field of the read data frame may contain a priority field. The priority field can be used to guide the unloading of theCCBs 310. Alternatively, priority information may be delivered as the read data is requested.Hub devices 112 can then compare the identification tag to previously recorded priority information to determine the location in theCCB 310 to send next. A method may also be employed that occasionally sends lower priority data before high priority data to ensure that low priority data is not completely stalled by requests that have been tagged with a higher priority. FIG. 4 is a process flow that is facilitated by theflow control logic 308 located in thehub device 112 in exemplary embodiments. The process depicted inFIG. 4 performs preemptive local data merge and may be implemented by a mechanism including hardware and/or software instructions such as a finite state machine in theflow control logic 308. The process starts atblock 402 and is repeated, in exemplary embodiments, on a periodic basis (e.g., after each controller channel transfer, or upstream channel cycle). Atblock 404 any local read data packets (i.e., frommemory devices 108 onmemory modules 110 attached to the hub device112) in thememory interface 302 are loaded into theCCB 310. This insures that theflow control logic 308 is aware of and managing the upstream driving of local read data. Atblock 406, it is determined if there is data in theCCB 310. If there is no data in theCCB 310, then the data is routed from thereceiver logic 304 to thedriver logic 306 atblock 412. The routing is directed by theflow control logic 308 by setting thelocal data multiplexer 312 to send the upstream data packet to thedriver logic 306 for driving the upstream data packet onto theupstream channel 106 towards thecontroller 102. Processing then continues at414, where processing is sent back to block404 at the next upstream channel cycle.- If it is determined at

block 406, that there is data in theCCB 310 then block408 is performed to determine if an upstream channel operation is in process (i.e., is an upstream data packet or a local read data packet in the middle of being driven onto theupstream channel 106 via the driver logic306). Processing continues atblock 412 if an upstream channel operation is in process (i.e., the driver is busy). Atblock 412, upstream read data packets are routed from thereceiver logic 304 to thedriver logic 306 by setting thelocal data multiplexer 312 to send the upstream data packet to thedriver logic 306. Alternatively, processing continues atblock 410 if an upstream channel operation is not in process (i.e., the driver is idle) and there is data in theCCB 310. Atblock 410, data from theCCB 310 is driven onto theupstream channel 106 while any data packets received in thereceiver logic 304 from theupstream channel 106 are shunted (stored) into the nextavailable CCB 310 location. The shunting is performed by theflow control logic 308 directing the upstream data packets to be loaded into theCCB 310. Processing then continues at414 which sends processing back to block404 at the next upstream channel cycle. FIG. 5 is an exemplary read data frame format for upstream data packets and local read data packets on theupstream channel 106. The frame format depicted inFIG. 5 uses twenty-one signal lanes and each packet includes sixteen transfers. It includes a one bitfirst start indicator 502 and anidentification tag 504, as well as 256 bits (32 B) of readdata 506 with abus CRCs 508 for transmission error detection. Other combinations of signal lanes and transfer depths can be used to create frame formats that include a frame start indicator, read data identification tag and read data that are compatible with this invention.- Exemplary embodiments pertain to a computer memory system constructed of daisy chained hub logic devices connected to, or contained upon, memory modules. The hubs are daisy chained on a memory controller channel and are further attached to memory devices on the memory modules. The memory controller issues requests for read data to the hubs which merge this read data from the memory modules onto the memory channel. Using channel buffers and packet identification tags, the hubs are able to return read data at a time unpredicted by the memory controller, and at a time that may preempt a read request that had been issued earlier, without loosing or corrupting any of the read data returned on the channel to the memory controller.

- Exemplary embodiments may be utilized to optimize average read data latency by more fully utilizing the upstream channel. Through the use of CCBs, read data frame formats with identification tags and a preemptive data merge technique, indeterminate read data latency may be performed to more fully utilize the controller channel.

- As described above, the embodiments of the invention may be embodied in the form of computer-implemented processes and apparatuses for practicing those processes. Embodiments of the invention may also be embodied in the form of computer program code containing instructions embodied in tangible media, such as floppy diskettes, CD-ROMs, hard drives, or any other computer-readable storage medium, wherein, when the computer program code is loaded into and executed by a computer, the computer becomes an apparatus for practicing the invention. The present invention can also be embodied in the form of computer program code, for example, whether stored in a storage medium, loaded into and/or executed by a computer, or transmitted over some transmission medium, such as over electrical wiring or cabling, through fiber optics, or via electromagnetic radiation, wherein, when the computer program code is loaded into and executed by a computer, the computer becomes an apparatus for practicing the invention. When implemented on a general-purpose microprocessor, the computer program code segments configure the microprocessor to create specific logic circuits.

- While the invention has been described with reference to exemplary embodiments, it will be understood by those skilled in the art that various changes may be made and equivalents may be substituted for elements thereof without departing from the scope of the invention. In addition, many modifications may be made to adapt a particular situation or material to the teachings of the invention without departing from the essential scope thereof. Therefore, it is intended that the invention not be limited to the particular embodiment disclosed as the best mode contemplated for carrying out this invention, but that the invention will include all embodiments falling within the scope of the appended claims. Moreover, the use of the terms first, second, etc. do not denote any order or importance, but rather the terms first, second, etc. are used to distinguish one element from another.

Claims (20)

1. A memory controller for use in a memory system, the memory controller comprising:

an upstream channel for receiving one or more read data packets at an unpredicted time from a downstream hub device, each packet in a frame format including a frame start indicator and an identification tag; and

computer instructions for correlating the received data packets with their corresponding read data request commands using the identification tags included in the read data packets.

2. The memory controller ofclaim 1 wherein each read data packet is received at an unpredicted time relative to its corresponding read request command.

3. The memory controller ofclaim 1 wherein the read data packets are received in an unpredicted order relative to an issue order of their corresponding read request commands.

4. The memory controller ofclaim 1 wherein the upstream channel is a daisy chain channel.

5. The memory controller ofclaim 1 wherein the hub device is physically located on a memory module.

6. The memory controller ofclaim 1 wherein the hub device includes a buffer device.

7. A method for providing indeterminate read data latency at a memory controller, the method comprising:

sending a memory data request from the memory controller to a memory module via a downstream bus, the memory module including a hub device;

receiving and processing the memory data request on the memory module;

sending a response data packet from the memory module to the memory controller via an upstream bus, the response data packet including a frame start indicator and an identification tag;

determining if the response data packet has been received at the memory controller using at least the frame start indicator; and

correlating the received response data packet with the memory data request based on the identification tag included in the response data packet.

8. The method ofclaim 7 wherein the identification tag in the memory response data packet is sourced from the read request.

9. The method ofclaim 7 wherein the receiving a response data packet at the memory controller occurs at an unpredicted time.

10. The method ofclaim 7 wherein the receiving of a response data packet at the memory controller occurs in an unpredicted order relative to an issue order of the corresponding memory data request command and other memory data request commands issued by the memory controller.

11. The method ofclaim 7 wherein the receiving and processing of the memory data request on the memory module includes:

receiving the memory data request at the memory module; and

servicing the memory data request at the memory module, resulting in the response data packet.

12. The method ofclaim 7 wherein the sending a response data packet includes executing a local preemptive data merge algorithm a the hub device to minimize read data latency and to enable indeterminate read data return times to the memory controller.

13. The method ofclaim 12 wherein the local preemptive data merge algorithm includes:

determining if a local data packet has been received;

if a local data packet has been received, then storing the local data packet into a buffer device;

determining if the buffer device contains a data packet;

determining if an upstream driver is idle;

if the buffer device contains a data packet and the upstream driver is idle, then transmitting the data packet to the upstream driver;

determining if an upstream data packet has been received;

if an upstream data packet has been received and the upstream driver is not idle, then storing the upstream data packet into the buffer device;

if an upstream data packet has been received and the buffer device does not contain a data packet and the upstream driver is idle, then transmitting the upstream data packet to the upstream driver; and

continuing to transmit any data packets in progress if the upstream driver is not idle.

14. The method ofclaim 13 wherein the determining if a local data packet has been received, the determining if the buffer device contains a data packet, the determining if an upstream driver is idle and the determining if a data packet has been received are performed on a periodic basis.

15. The method ofclaim 14 wherein the periodic basis is once every upstream channel cycle.

16. The method ofclaim 13 wherein the buffer device contains a plurality of data packets and the data packet is selected based on a prioritization algorithm.

17. The method ofclaim 16 wherein the prioritization algorithm selects the data packet based on the age of the read instruction that corresponds to the data packet.

18. The method ofclaim 17 wherein the prioritization algorithm selects the data packet based on a priority associated with the data packet.

19. The method ofclaim 1 wherein the frame format further includes a bus cyclical redundancy code (CRC) field.

20. A memory system comprising:

a memory controller including;

an upstream channel for receiving one or more read data packets at an unpredicted time; and

computer instructions for correlating the received read data packets with their corresponding read data request commands using identification tags included in the read data packets;

one or more memory modules with one or more memory devices connected to the memory controller by a daisy chained channel, wherein the read data is returned to the memory controller as the read data packets using a frame format that includes the identification tag and a frame start indicator; and

one or more hub devices on the memory modules for buffering address, commands and data, the hub devices including controller channel buffers used in conjunction with a preemptive local data merge algorithm to minimize read data latency and enable indeterminate read data return times to the memory controller.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/736,196US20070183331A1 (en) | 2005-11-28 | 2007-04-17 | Method and system for providing indeterminate read data latency in a memory system |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/289,193US7685392B2 (en) | 2005-11-28 | 2005-11-28 | Providing indeterminate read data latency in a memory system |

| US11/736,196US20070183331A1 (en) | 2005-11-28 | 2007-04-17 | Method and system for providing indeterminate read data latency in a memory system |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| US11/289,193ContinuationUS7685392B2 (en) | 2005-11-28 | 2005-11-28 | Providing indeterminate read data latency in a memory system |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| US20070183331A1true US20070183331A1 (en) | 2007-08-09 |

Family

ID=37698119

Family Applications (6)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| US11/289,193Expired - Fee RelatedUS7685392B2 (en) | 2005-11-28 | 2005-11-28 | Providing indeterminate read data latency in a memory system |

| US11/736,196AbandonedUS20070183331A1 (en) | 2005-11-28 | 2007-04-17 | Method and system for providing indeterminate read data latency in a memory system |

| US11/843,271Expired - Fee RelatedUS8151042B2 (en) | 2005-11-28 | 2007-08-22 | Method and system for providing identification tags in a memory system having indeterminate data response times |

| US11/843,150Expired - Fee RelatedUS8145868B2 (en) | 2005-11-28 | 2007-08-22 | Method and system for providing frame start indication in a memory system having indeterminate read data latency |

| US13/397,819Expired - Fee RelatedUS8327105B2 (en) | 2005-11-28 | 2012-02-16 | Providing frame start indication in a memory system having indeterminate read data latency |

| US13/397,827Expired - Fee RelatedUS8495328B2 (en) | 2005-11-28 | 2012-02-16 | Providing frame start indication in a memory system having indeterminate read data latency |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| US11/289,193Expired - Fee RelatedUS7685392B2 (en) | 2005-11-28 | 2005-11-28 | Providing indeterminate read data latency in a memory system |

Family Applications After (4)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| US11/843,271Expired - Fee RelatedUS8151042B2 (en) | 2005-11-28 | 2007-08-22 | Method and system for providing identification tags in a memory system having indeterminate data response times |

| US11/843,150Expired - Fee RelatedUS8145868B2 (en) | 2005-11-28 | 2007-08-22 | Method and system for providing frame start indication in a memory system having indeterminate read data latency |

| US13/397,819Expired - Fee RelatedUS8327105B2 (en) | 2005-11-28 | 2012-02-16 | Providing frame start indication in a memory system having indeterminate read data latency |

| US13/397,827Expired - Fee RelatedUS8495328B2 (en) | 2005-11-28 | 2012-02-16 | Providing frame start indication in a memory system having indeterminate read data latency |

Country Status (6)

| Country | Link |

|---|---|

| US (6) | US7685392B2 (en) |

| EP (1) | EP1958073A1 (en) |

| JP (1) | JP5186382B2 (en) |

| CN (1) | CN101300556B (en) |

| TW (1) | TWI399649B (en) |

| WO (1) | WO2007060250A1 (en) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20100122003A1 (en)* | 2008-11-10 | 2010-05-13 | Nec Laboratories America, Inc. | Ring-based high speed bus interface |

| US7969985B1 (en)* | 2008-09-03 | 2011-06-28 | Motion Engineering, Inc. | Method and system for scheduling, transporting, and receiving inbound packets efficiently in networks with cyclic packet scheduling |

Families Citing this family (63)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7389375B2 (en) | 2004-07-30 | 2008-06-17 | International Business Machines Corporation | System, method and storage medium for a multi-mode memory buffer device |

| US7539800B2 (en) | 2004-07-30 | 2009-05-26 | International Business Machines Corporation | System, method and storage medium for providing segment level sparing |

| US7296129B2 (en)* | 2004-07-30 | 2007-11-13 | International Business Machines Corporation | System, method and storage medium for providing a serialized memory interface with a bus repeater |

| US7512762B2 (en) | 2004-10-29 | 2009-03-31 | International Business Machines Corporation | System, method and storage medium for a memory subsystem with positional read data latency |

| US7356737B2 (en) | 2004-10-29 | 2008-04-08 | International Business Machines Corporation | System, method and storage medium for testing a memory module |

| US7299313B2 (en) | 2004-10-29 | 2007-11-20 | International Business Machines Corporation | System, method and storage medium for a memory subsystem command interface |

| US7305574B2 (en) | 2004-10-29 | 2007-12-04 | International Business Machines Corporation | System, method and storage medium for bus calibration in a memory subsystem |

| US7395476B2 (en) | 2004-10-29 | 2008-07-01 | International Business Machines Corporation | System, method and storage medium for providing a high speed test interface to a memory subsystem |

| US7331010B2 (en) | 2004-10-29 | 2008-02-12 | International Business Machines Corporation | System, method and storage medium for providing fault detection and correction in a memory subsystem |

| US7441060B2 (en) | 2004-10-29 | 2008-10-21 | International Business Machines Corporation | System, method and storage medium for providing a service interface to a memory system |

| US7277988B2 (en) | 2004-10-29 | 2007-10-02 | International Business Machines Corporation | System, method and storage medium for providing data caching and data compression in a memory subsystem |

| US7478259B2 (en) | 2005-10-31 | 2009-01-13 | International Business Machines Corporation | System, method and storage medium for deriving clocks in a memory system |

| US7368950B2 (en)* | 2005-11-16 | 2008-05-06 | Montage Technology Group Limited | High speed transceiver with low power consumption |

| US7558124B2 (en)* | 2005-11-16 | 2009-07-07 | Montage Technology Group, Ltd | Memory interface to bridge memory buses |

| US7577039B2 (en)* | 2005-11-16 | 2009-08-18 | Montage Technology Group, Ltd. | Memory interface to bridge memory buses |

| US7685392B2 (en) | 2005-11-28 | 2010-03-23 | International Business Machines Corporation | Providing indeterminate read data latency in a memory system |

| JP5065618B2 (en)* | 2006-05-16 | 2012-11-07 | 株式会社日立製作所 | Memory module |

| US7636813B2 (en) | 2006-05-22 | 2009-12-22 | International Business Machines Corporation | Systems and methods for providing remote pre-fetch buffers |

| US7640386B2 (en)* | 2006-05-24 | 2009-12-29 | International Business Machines Corporation | Systems and methods for providing memory modules with multiple hub devices |

| US7345900B2 (en)* | 2006-07-26 | 2008-03-18 | International Business Machines Corporation | Daisy chained memory system |

| US7345901B2 (en)* | 2006-07-26 | 2008-03-18 | International Business Machines Corporation | Computer system having daisy chained self timed memory chips |

| US7669086B2 (en) | 2006-08-02 | 2010-02-23 | International Business Machines Corporation | Systems and methods for providing collision detection in a memory system |

| US7539842B2 (en) | 2006-08-15 | 2009-05-26 | International Business Machines Corporation | Computer memory system for selecting memory buses according to physical memory organization information stored in virtual address translation tables |

| US7490217B2 (en) | 2006-08-15 | 2009-02-10 | International Business Machines Corporation | Design structure for selecting memory busses according to physical memory organization information stored in virtual address translation tables |

| US7870459B2 (en) | 2006-10-23 | 2011-01-11 | International Business Machines Corporation | High density high reliability memory module with power gating and a fault tolerant address and command bus |

| US7721140B2 (en) | 2007-01-02 | 2010-05-18 | International Business Machines Corporation | Systems and methods for improving serviceability of a memory system |

| US7603526B2 (en) | 2007-01-29 | 2009-10-13 | International Business Machines Corporation | Systems and methods for providing dynamic memory pre-fetch |

| US7606988B2 (en) | 2007-01-29 | 2009-10-20 | International Business Machines Corporation | Systems and methods for providing a dynamic memory bank page policy |

| US20080298468A1 (en)* | 2007-06-04 | 2008-12-04 | Mediaphy Corporation | Error tagging for decoder |

| US8601181B2 (en) | 2007-11-26 | 2013-12-03 | Spansion Llc | System and method for read data buffering wherein an arbitration policy determines whether internal or external buffers are given preference |

| US8332572B2 (en) | 2008-02-05 | 2012-12-11 | Spansion Llc | Wear leveling mechanism using a DRAM buffer |

| US20100005218A1 (en)* | 2008-07-01 | 2010-01-07 | International Business Machines Corporation | Enhanced cascade interconnected memory system |

| DE102008050102B4 (en)* | 2008-10-06 | 2010-11-04 | Phoenix Contact Gmbh & Co. Kg | Communication entity for communication via a bus-oriented communication network |

| US8472199B2 (en)* | 2008-11-13 | 2013-06-25 | Mosaid Technologies Incorporated | System including a plurality of encapsulated semiconductor chips |

| CN101425052B (en)* | 2008-12-04 | 2010-06-09 | 中国科学院计算技术研究所 | A Realization Method of Transactional Memory |

| US9123409B2 (en) | 2009-06-11 | 2015-09-01 | Micron Technology, Inc. | Memory device for a hierarchical memory architecture |

| JP5372687B2 (en)* | 2009-09-30 | 2013-12-18 | ソニー株式会社 | Transmitting apparatus, transmitting method, receiving apparatus, and receiving method |

| US8327052B2 (en) | 2009-12-23 | 2012-12-04 | Spansion Llc | Variable read latency on a serial memory bus |

| US8549378B2 (en) | 2010-06-24 | 2013-10-01 | International Business Machines Corporation | RAIM system using decoding of virtual ECC |

| US8898511B2 (en)* | 2010-06-24 | 2014-11-25 | International Business Machines Corporation | Homogeneous recovery in a redundant memory system |

| US8484529B2 (en) | 2010-06-24 | 2013-07-09 | International Business Machines Corporation | Error correction and detection in a redundant memory system |

| US8631271B2 (en) | 2010-06-24 | 2014-01-14 | International Business Machines Corporation | Heterogeneous recovery in a redundant memory system |

| TWI462103B (en)* | 2011-01-19 | 2014-11-21 | Mstar Semiconductor Inc | Controller and controlling method for memory and memory system |

| US8522122B2 (en) | 2011-01-29 | 2013-08-27 | International Business Machines Corporation | Correcting memory device and memory channel failures in the presence of known memory device failures |

| CN103164366A (en)* | 2011-12-09 | 2013-06-19 | 鸿富锦精密工业(深圳)有限公司 | Electronic equipment provided with universal input and output expander and signal detecting method |

| US8880819B2 (en) | 2011-12-13 | 2014-11-04 | Micron Technology, Inc. | Memory apparatuses, computer systems and methods for ordering memory responses |

| US8938656B2 (en) | 2012-09-14 | 2015-01-20 | Sandisk Technologies Inc. | Data storage device with intermediate ECC stage |

| US9424314B2 (en)* | 2012-10-19 | 2016-08-23 | Oracle International Corporation | Method and apparatus for joining read requests |

| US9081700B2 (en) | 2013-05-16 | 2015-07-14 | Western Digital Technologies, Inc. | High performance read-modify-write system providing line-rate merging of dataframe segments in hardware |

| EP3058571A1 (en) | 2013-10-15 | 2016-08-24 | Rambus Inc. | Load reduced memory module |

| CN110299157B (en) | 2013-11-11 | 2023-04-28 | 拉姆伯斯公司 | Mass storage system using standard controller components |

| USD733145S1 (en)* | 2014-03-14 | 2015-06-30 | Kingston Digital, Inc. | Memory module |

| USD735201S1 (en)* | 2014-07-30 | 2015-07-28 | Kingston Digital, Inc. | Memory module |

| US10223309B2 (en)* | 2014-12-19 | 2019-03-05 | Rambus Inc. | Dynamic random access memory (DRAM) component for high-performance, high-capacity registered memory modules |

| AT14695U1 (en)* | 2015-01-19 | 2016-04-15 | Bachmann Gmbh | Serial bus system with coupling modules |

| KR102425470B1 (en)* | 2015-04-06 | 2022-07-27 | 에스케이하이닉스 주식회사 | Data storage device and operating method thereof |

| CN107122134B (en)* | 2017-04-25 | 2020-01-03 | 杭州迪普科技股份有限公司 | Data reading method and device |

| US10970239B2 (en)* | 2018-03-16 | 2021-04-06 | Intel Corporation | Hub circuit for a DIMM having multiple components that communicate with a host |

| PL3582368T3 (en) | 2018-04-16 | 2025-03-10 | Lg Electronics Inc. | Apparatus and method for performing transmission of data stream in wireless power transmission system |

| US11178055B2 (en) | 2019-06-14 | 2021-11-16 | Intel Corporation | Methods and apparatus for providing deterministic latency for communications interfaces |

| US11258755B2 (en)* | 2019-09-19 | 2022-02-22 | GM Global Technology Operations LLC | Method and system for processing coherent data |

| JP2023044544A (en) | 2021-09-17 | 2023-03-30 | キオクシア株式会社 | memory system |

| US12164773B2 (en)* | 2022-10-18 | 2024-12-10 | Micron Technology, Inc. | Controller architecture for reliability, availability, serviceability access |

Citations (94)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3825904A (en)* | 1973-06-08 | 1974-07-23 | Ibm | Virtual memory system |

| US4028675A (en)* | 1973-05-14 | 1977-06-07 | Hewlett-Packard Company | Method and apparatus for refreshing semiconductor memories in multi-port and multi-module memory system |

| US4135240A (en)* | 1973-07-09 | 1979-01-16 | Bell Telephone Laboratories, Incorporated | Protection of data file contents |

| US4654857A (en)* | 1981-10-01 | 1987-03-31 | Stratus Computer, Inc. | Digital data processor with high reliability |

| US4723120A (en)* | 1986-01-14 | 1988-02-02 | International Business Machines Corporation | Method and apparatus for constructing and operating multipoint communication networks utilizing point-to point hardware and interfaces |

| US4740916A (en)* | 1985-12-19 | 1988-04-26 | International Business Machines Corporation | Reconfigurable contiguous address space memory system including serially connected variable capacity memory modules and a split address bus |

| US4796231A (en)* | 1985-01-22 | 1989-01-03 | Texas Instruments Incorporated | Serial accessed semiconductor memory with reconfigurable shift registers |

| US4803485A (en)* | 1987-03-23 | 1989-02-07 | Amp Incorporated | Lan communication system and medium adapter for use therewith |

| US4833605A (en)* | 1984-08-16 | 1989-05-23 | Mitsubishi Denki Kabushiki Kaisha | Cascaded information processing module having operation unit, parallel port, and serial port for concurrent data transfer and data processing |

| US4839534A (en)* | 1986-10-16 | 1989-06-13 | Siemens Aktiengesellschaft | Method and apparatus for establishing a system clock in response to the level of one of two clock signal sources |

| US4943984A (en)* | 1988-06-24 | 1990-07-24 | International Business Machines Corporation | Data processing system parallel data bus having a single oscillator clocking apparatus |

| US4985828A (en)* | 1987-03-19 | 1991-01-15 | Hitachi, Ltd. | Method and apparatus for generating a real address multiple virtual address spaces of a storage |

| US5177375A (en)* | 1989-12-28 | 1993-01-05 | Mitsubishi Denki Kabushiki Kaisha | Power on reset circuit for semiconductor integrated circuit device |

| US5206946A (en)* | 1989-10-27 | 1993-04-27 | Sand Technology Systems Development, Inc. | Apparatus using converters, multiplexer and two latches to convert SCSI data into serial data and vice versa |

| US5214747A (en)* | 1990-12-24 | 1993-05-25 | Eastman Kodak Company | Segmented neural network with daisy chain control |

| US5287531A (en)* | 1990-10-31 | 1994-02-15 | Compaq Computer Corp. | Daisy-chained serial shift register for determining configuration of removable circuit boards in a computer system |

| US5387911A (en)* | 1992-02-21 | 1995-02-07 | Gleichert; Marc C. | Method and apparatus for transmitting and receiving both 8B/10B code and 10B/12B code in a switchable 8B/10B transmitter and receiver |

| US5394535A (en)* | 1989-04-21 | 1995-02-28 | Nec Corporation | Memory access control circuit with automatic access mode determination circuitry with read-modify-write and write-per-bit operations |

| US5513135A (en)* | 1994-12-02 | 1996-04-30 | International Business Machines Corporation | Synchronous memory packaged in single/dual in-line memory module and method of fabrication |

| US5592632A (en)* | 1991-11-05 | 1997-01-07 | Monolithic System Technology, Inc. | Defect tolerant integrated circuit subsystem for communication between a module and a bus controller in a wafer-scale integrated circuit system |

| US5611055A (en)* | 1994-09-27 | 1997-03-11 | Novalink Technologies | Method and apparatus for implementing a PCMCIA auxiliary port connector for selectively communicating with peripheral devices |

| US5627963A (en)* | 1992-04-30 | 1997-05-06 | International Business Machines Corporation | Redundant read bus for correcting defective columns in a cache memory |

| US5629685A (en)* | 1995-02-23 | 1997-05-13 | International Business Machines Corporation | Segmentable addressable modular communication network hubs |

| US5661677A (en)* | 1996-05-15 | 1997-08-26 | Micron Electronics, Inc. | Circuit and method for on-board programming of PRD Serial EEPROMS |

| US5764155A (en)* | 1996-04-03 | 1998-06-09 | General Electric Company | Dynamic data exchange server |

| US5870325A (en)* | 1998-04-14 | 1999-02-09 | Silicon Graphics, Inc. | Memory system with multiple addressing and control busses |

| US5872996A (en)* | 1992-03-06 | 1999-02-16 | Rambus, Inc. | Method and apparatus for transmitting memory requests by transmitting portions of count data in adjacent words of a packet |

| US5926838A (en)* | 1997-03-19 | 1999-07-20 | Micron Electronics | Interface for high speed memory |

| US5930273A (en)* | 1996-04-18 | 1999-07-27 | Oki Electric Industry Co., Ltd. | STM-N signal error correction coding system and method |

| US5928343A (en)* | 1990-04-18 | 1999-07-27 | Rambus Inc. | Memory module having memory devices containing internal device ID registers and method of initializing same |

| US6038132A (en)* | 1996-12-06 | 2000-03-14 | Mitsubishi Denki Kabushiki Kaisha | Memory module |

| US6049476A (en)* | 1995-05-15 | 2000-04-11 | Silicon Graphics, Inc. | High memory capacity DIMM with data and state memory |

| US6076158A (en)* | 1990-06-29 | 2000-06-13 | Digital Equipment Corporation | Branch prediction in high-performance processor |

| US6096091A (en)* | 1998-02-24 | 2000-08-01 | Advanced Micro Devices, Inc. | Dynamically reconfigurable logic networks interconnected by fall-through FIFOs for flexible pipeline processing in a system-on-a-chip |

| US6170047B1 (en)* | 1994-11-16 | 2001-01-02 | Interactive Silicon, Inc. | System and method for managing system memory and/or non-volatile memory using a memory controller with integrated compression and decompression capabilities |

| US6170059B1 (en)* | 1998-07-10 | 2001-01-02 | International Business Machines Corporation | Tracking memory modules within a computer system |

| US6173382B1 (en)* | 1998-04-28 | 2001-01-09 | International Business Machines Corporation | Dynamic configuration of memory module using modified presence detect data |

| US6215686B1 (en)* | 1999-02-09 | 2001-04-10 | Silicon Graphics, Inc. | Memory system with switching for data isolation |

| US6219288B1 (en)* | 2000-03-03 | 2001-04-17 | International Business Machines Corporation | Memory having user programmable AC timings |

| US20010003839A1 (en)* | 1999-12-09 | 2001-06-14 | Hidetoshi Kondo | Data access method in the network system and the network system |

| US6260127B1 (en)* | 1998-07-13 | 2001-07-10 | Compaq Computer Corporation | Method and apparatus for supporting heterogeneous memory in computer systems |

| US6262493B1 (en)* | 1999-10-08 | 2001-07-17 | Sun Microsystems, Inc. | Providing standby power to field replaceable units for electronic systems |

| US6338113B1 (en)* | 1998-06-10 | 2002-01-08 | Mitsubishi Denki Kabushiki Kaisha | Memory module system having multiple memory modules |

| US20020019926A1 (en)* | 1997-12-17 | 2002-02-14 | Huppenthal Jon M. | Switch/network adapter port for clustered computers employing a chain of multi-adaptive processors in a dual in-line memory module format |

| US20020038405A1 (en)* | 1998-09-30 | 2002-03-28 | Michael W. Leddige | Method and apparatus for implementing multiple memory buses on a memory module |

| US6370631B1 (en)* | 1994-11-16 | 2002-04-09 | Interactive Silicon, Inc. | Memory controller including compression/decompression capabilities for improved data access |

| US6378018B1 (en)* | 1997-10-10 | 2002-04-23 | Intel Corporation | Memory device and system including a low power interface |

| US6393528B1 (en)* | 1999-06-30 | 2002-05-21 | International Business Machines Corporation | Optimized cache allocation algorithm for multiple speculative requests |

| US20020083255A1 (en)* | 2000-12-22 | 2002-06-27 | Roy Greeff | Method and apparatus using switches for point to point bus operation |

| US20020103988A1 (en)* | 1996-12-18 | 2002-08-01 | Pascal Dornier | Microprocessor with integrated interfaces to system memory and multiplexed input/output bus |

| US20020112119A1 (en)* | 1998-02-13 | 2002-08-15 | Intel Corporation | Dual-port buffer-to-memory interface |

| US20020112194A1 (en)* | 2000-12-15 | 2002-08-15 | Uzelac Lawrence S. | Clock phase generator |

| US6507888B2 (en)* | 2001-01-03 | 2003-01-14 | Leadtek Research Inc. | SDR and DDR conversion device and associated interface card, main board and memory module interface |

| US6510100B2 (en)* | 2000-12-04 | 2003-01-21 | International Business Machines Corporation | Synchronous memory modules and memory systems with selectable clock termination |

| US6513091B1 (en)* | 1999-11-12 | 2003-01-28 | International Business Machines Corporation | Data routing using status-response signals |

| US20030033364A1 (en)* | 2001-08-10 | 2003-02-13 | Garnett Paul J. | Interfacing computer modules |

| US6532525B1 (en)* | 2000-09-29 | 2003-03-11 | Ati Technologies, Inc. | Method and apparatus for accessing memory |

| US20030056183A1 (en)* | 1999-01-26 | 2003-03-20 | Munenori Kobayashi | Scan test circuit, and semiconductor integrated circuit including the circuit |

| US6546359B1 (en)* | 2000-04-24 | 2003-04-08 | Sun Microsystems, Inc. | Method and apparatus for multiplexing hardware performance indicators |

| US6549971B1 (en)* | 1999-08-26 | 2003-04-15 | International Business Machines Corporation | Cascaded differential receiver circuit |

| US6553450B1 (en)* | 2000-09-18 | 2003-04-22 | Intel Corporation | Buffer to multiply memory interface |

| US6557069B1 (en)* | 1999-11-12 | 2003-04-29 | International Business Machines Corporation | Processor-memory bus architecture for supporting multiple processors |

| US20030084309A1 (en)* | 2001-10-22 | 2003-05-01 | Sun Microsystems, Inc. | Stream processor with cryptographic co-processor |

| US6564329B1 (en)* | 1999-03-16 | 2003-05-13 | Linkup Systems Corporation | System and method for dynamic clock generation |

| US20030090879A1 (en)* | 2001-06-14 | 2003-05-15 | Doblar Drew G. | Dual inline memory module |

| US20030118044A1 (en)* | 2001-12-21 | 2003-06-26 | International Business Machines Corporation | Queue scheduling mechanism in a data packet transmission system |

| US6601121B2 (en)* | 1999-12-29 | 2003-07-29 | Intel Corporation | Quad pumped bus architecture and protocol |

| US6611902B2 (en)* | 2000-11-13 | 2003-08-26 | Matsushita Electric Industrial Co., Ltd. | Information processor and information processing method |

| US20040006674A1 (en)* | 2002-07-05 | 2004-01-08 | Hargis Jeff G. | System and method for multi-modal memory controller system operation |

| US6678811B2 (en)* | 2001-04-07 | 2004-01-13 | Hewlett-Packard Development Company, L.P. | Memory controller with 1X/MX write capability |

| US6697919B2 (en)* | 2000-06-10 | 2004-02-24 | Hewlett-Packard Development Company, L.P. | System and method for limited fanout daisy chaining of cache invalidation requests in a shared-memory multiprocessor system |

| US6704842B1 (en)* | 2000-04-12 | 2004-03-09 | Hewlett-Packard Development Company, L.P. | Multi-processor system with proactive speculative data transfer |

| US20040049723A1 (en)* | 2002-09-02 | 2004-03-11 | Teruhisa Obara | Semiconductor integrated circuit with a test circuit |

| US6721944B2 (en)* | 2000-05-31 | 2004-04-13 | Sun Microsystems, Inc. | Marking memory elements based upon usage of accessed information during speculative execution |

| US6738836B1 (en)* | 2000-08-31 | 2004-05-18 | Hewlett-Packard Development Company, L.P. | Scalable efficient I/O port protocol |

| US20040117588A1 (en)* | 2002-12-12 | 2004-06-17 | International Business Machines Corporation | Access request for a data processing system having no system memory |

| US20040128474A1 (en)* | 2000-10-09 | 2004-07-01 | Martin Vorbach | Method and device |

| US6766389B2 (en)* | 2001-05-18 | 2004-07-20 | Broadcom Corporation | System on a chip for networking |

| US6775747B2 (en)* | 2002-01-03 | 2004-08-10 | Intel Corporation | System and method for performing page table walks on speculative software prefetch operations |

| US6839393B1 (en)* | 1999-07-14 | 2005-01-04 | Rambus Inc. | Apparatus and method for controlling a master/slave system via master device synchronization |

| US20050023560A1 (en)* | 2003-07-28 | 2005-02-03 | Ahn Young-Man | Memory module test system |

| US20050050255A1 (en)* | 2003-08-28 | 2005-03-03 | Jeddeloh Joseph M. | Multiple processor system and method including multiple memory hub modules |

| US20050050237A1 (en)* | 2003-08-28 | 2005-03-03 | Jeddeloh Joseph M. | Memory module and method having on-board data search capabilities and processor-based system using such memory modules |

| US20050066136A1 (en)* | 2003-09-18 | 2005-03-24 | Schnepper Randy L. | Memory hub with integrated non-volatile memory |

| US6877078B2 (en)* | 2000-04-06 | 2005-04-05 | Hitachi, Ltd. | Information processing system with memory element performance-dependent memory control |