US20070014168A1 - Method and circuit for configuring memory core integrated circuit dies with memory interface integrated circuit dies - Google Patents

Method and circuit for configuring memory core integrated circuit dies with memory interface integrated circuit diesDownload PDFInfo

- Publication number

- US20070014168A1 US20070014168A1US11/474,076US47407606AUS2007014168A1US 20070014168 A1US20070014168 A1US 20070014168A1US 47407606 AUS47407606 AUS 47407606AUS 2007014168 A1US2007014168 A1US 2007014168A1

- Authority

- US

- United States

- Prior art keywords

- integrated circuit

- memory core

- interface

- circuit die

- memory

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Abandoned

Links

Images

Classifications

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/04—Detection or location of defective memory elements, e.g. cell constructio details, timing of test signals

- G11C29/50—Marginal testing, e.g. race, voltage or current testing

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1668—Details of memory controller

- G06F13/1694—Configuration of memory controller to different memory types

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/4076—Timing circuits

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/409—Read-write [R-W] circuits

- G11C11/4093—Input/output [I/O] data interface arrangements, e.g. data buffers

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/409—Read-write [R-W] circuits

- G11C11/4096—Input/output [I/O] data management or control circuits, e.g. reading or writing circuits, I/O drivers or bit-line switches

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/02—Detection or location of defective auxiliary circuits, e.g. defective refresh counters

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/02—Detection or location of defective auxiliary circuits, e.g. defective refresh counters

- G11C29/022—Detection or location of defective auxiliary circuits, e.g. defective refresh counters in I/O circuitry

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/02—Detection or location of defective auxiliary circuits, e.g. defective refresh counters

- G11C29/028—Detection or location of defective auxiliary circuits, e.g. defective refresh counters with adaption or trimming of parameters

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/04—Detection or location of defective memory elements, e.g. cell constructio details, timing of test signals

- G11C29/08—Functional testing, e.g. testing during refresh, power-on self testing [POST] or distributed testing

- G11C29/12—Built-in arrangements for testing, e.g. built-in self testing [BIST] or interconnection details

- G11C29/18—Address generation devices; Devices for accessing memories, e.g. details of addressing circuits

- G11C29/24—Accessing extra cells, e.g. dummy cells or redundant cells

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/04—Detection or location of defective memory elements, e.g. cell constructio details, timing of test signals

- G11C29/50—Marginal testing, e.g. race, voltage or current testing

- G11C29/50012—Marginal testing, e.g. race, voltage or current testing of timing

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1006—Data managing, e.g. manipulating data before writing or reading out, data bus switches or control circuits therefor

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1006—Data managing, e.g. manipulating data before writing or reading out, data bus switches or control circuits therefor

- G11C7/1012—Data reordering during input/output, e.g. crossbars, layers of multiplexers, shifting or rotating

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1015—Read-write modes for single port memories, i.e. having either a random port or a serial port

- G11C7/1045—Read-write mode select circuits

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/12—Group selection circuits, e.g. for memory block selection, chip selection, array selection

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2207/00—Indexing scheme relating to arrangements for writing information into, or reading information out from, a digital store

- G11C2207/10—Aspects relating to interfaces of memory device to external buses

- G11C2207/107—Serial-parallel conversion of data or prefetch

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2207/00—Indexing scheme relating to arrangements for writing information into, or reading information out from, a digital store

- G11C2207/22—Control and timing of internal memory operations

- G11C2207/2254—Calibration

Definitions

- the present inventionis directed toward the field of building custom memory systems cost-effectively for a wide range of markets.

- DRAMDynamic Random Access Memory

- Mb/$Cost-effectiveness

- Specialty memoryis typically memory that is not used by the PC main memory but is memory that is designed for one or more niche markets.

- the PC graphics marketuses GDDR (Graphics Dual Data Rate) DRAM.

- FCRAMFist Cycle RAM

- RLDRAMReduced Latency DRAM.

- Legacy memoryis typically memory that was used in the past but is not used in that particular market segment now.

- SDRAMSynchronous DRAM

- a methodcombines memory core integrated circuit dies with interface integrated circuit dies to configure a memory device. At least one test on the memory core integrated circuit dies is conducted. In one embodiment, the test measures the amount of time required for a read, write, activate, pre-charge, or refresh operations. From the test, at least one characteristic of the memory core integrated circuit dies is identified. In one embodiment, the characteristic comprises the speed of operation for the memory core integrated circuit die.

- the interface integrated circuit dieis electrically coupled to the memory core integrated circuit die based on the memory core integrated circuit characteristic.

- the memory core integrated circuit diesare speed binned based on “slow”, “typical” and “high” speed.

- the slow memory core integrated circuit diesare coupled to an interface integrated circuit die designed for low power markets.

- the typical speed memory core integrated circuit diesare coupled to an interface integrated circuit die designed for power conservation and performance markets.

- the high-speed memory core integrated circuit diesare coupled to an interface integrated circuit die designed for high performance markets.

- an effective data rate for an interface on the memory core integrated circuit dieis configured based on the speed of operation of the memory core integrated circuit die.

- An interface integrated circuit dieis electrically coupled to the memory core integrated circuit die to operate with an external bus and to operate in conjunction with the effective data rate of the interface on the memory core integrated circuit die.

- FIG. 1is a block diagram illustrating a conventional DRAM chip.

- FIG. 2illustrates a typical organization of a 4-bank modern SDRAM.

- FIG. 3is a block diagram illustrating one embodiment of banks arranged in sub-arrays.

- FIG. 4illustrates a block diagram of an interface and multiple banks in a DRAM.

- FIG. 5is a block diagram illustrating a DRAM chip with an interface removed.

- FIG. 6illustrates one embodiment for a center bonded DRAM core chip.

- FIG. 7illustrates one embodiment for an edge bonded DRAM core chip.

- FIG. 8illustrates one embodiment for a concentrated-bank architecture.

- FIG. 9illustrates one embodiment for a distributed-bank architecture.

- FIG. 10illustrates one embodiment for a quadrant in a distributed-bank architecture DRAM core chip.

- FIG. 11is block diagram illustrating one embodiment of a distributed-bank architecture universal DRAM core chip.

- FIG. 12is a block diagram illustrating a distributed-bank architecture DRAM core chip configured to support DDR2 speeds.

- FIG. 13is a block diagram illustrating a distributed-bank architecture DRAM core chip configured to support DDR speeds and external bus widths from 17 to 32 bits.

- FIG. 14is a block diagram illustrating a distributed-bank architecture DRAM core chip configured to support DDR speeds and external bus widths from 9 to 16 bits.

- FIG. 15is a block diagram illustrating a distributed-bank architecture DRAM core chip configured to support DDR speeds and external bus widths from 1 to 8 bits.

- FIG. 16illustrates one embodiment for a portion of a DRAM core chip that includes a decoder for selecting a mode of operation.

- FIG. 17 ais a block diagram illustrating the relationship between the internal data bus rate and the external data bus rate for 4n pre-fetching.

- FIG. 17 bis a block diagram illustrating the relationship between the internal data bus rate and the external data bus rate for burst mode with a length of 4n.

- FIG. 18is a block diagram illustrating an example multi-chip memory implementation.

- FIG. 19illustrates techniques for stacking two DRAM core chips behind a single interface chip.

- ⁇ 16 ( ⁇ 16 denotes the external data width) 256 Mb SDRAM, ⁇ 16 256 Mb DDR SDRAM, and ⁇ 16 256 Mb DDR2 SDRAMconsist of:

- Memory arraysthat store the data

- control logic blockwhich implements the protocol, among other functions

- width of the data that is accessed per column addressand in the data I/O section.

- data I/O sectionare usually considered part of the interface section of the DRAM while the rest of the circuits (address decoder, memory arrays, and data selection) are considered part of the memory core.

- the core timing parametersare typically specified in absolute units of time (seconds) rather than in terms of clock periods.

- the Micron 256 Mb DDR2 SDRAM data sheetlists the following core timing parameters: TABLE 1 Speed Grade t RCD (ns) t RP (ns) t RC (ns) ⁇ 5E 15 15 55 ⁇ 37E 15 15 55 ⁇ 3 15 15 55 ⁇ 3E 12 12 54

- the Micron 256 Mb DDR SDRAM data sheetidentifies the following timing specifications: TABLE 2 Speed Grade t RCD (ns) t RP (ns) t RC (ns) ⁇ 75Z 20 20 65 ⁇ 75 20 20 65

- the Micron 256 Mb SDRAM data sheetdiscloses the following specifications: TABLE 3 Speed Grade t RCD (ns) t RP (ns) t RC (ns) ⁇ 7E 15 15 60 ⁇ 75 20 20 66

- One embodiment of the inventioncomprises a multi-chip implementation, wherein one or more DRAM core chips are attached to an interface chip.

- the interface chipsits between the host electronic system and the DRAM core chips.

- the interface chipcan be thought of as a “wrapper” that surrounds the DRAM core chips.

- the partitioning of the conventional DRAM into DRAM core chip and interface chipshould preferably be done is such a way that that the functions and circuits that are relatively constant across many different architectures are retained in the DRAM core chip while the functions and circuits that vary between the different architectures are moved to the interface chip.

- the DRAM core chipcan be designed to be suitable for a large number of markets (i.e. a “universal core”).

- the interface chipcan now be designed to meet the exact needs of a market, and even the exact needs of individual customers in that market.

- the proposed solutionenables the design of an interface chip to meet the exact needs of Nokia for the cell phone market and another interface chip to meet the exact needs of Motorola for the cell phone market.

- the DRAM core chipIn order to accommodate the needs of the different markets, the DRAM core chip must be capable of operating across a wide range of frequencies, be capable of supporting high data rates, and must be low cost.

- the DRAM core chipis asynchronous, wide, and operates at its natural speed.

- the natural speedis between 5 ns to 10 ns per column access, which is equivalent to 100 MHz to 200 MHz synchronous operation. That is, a modern DRAM core can keep up with an external memory bus or interface that runs at a speed from 100 MHz to 200 MHz.

- n bitscan be fetched from the DRAM core once every clock cycle. In fact, this is how SDRAMs operate.

- Newer synchronous DRAMsrun at higher clock speeds.

- JEDECdefines the DDR SDRAM specification with external data rates of 200 MHz, 266 MHz, 333 MHz, and 400 MHz.

- An even newer specification called DDR2 SDRAMhas been defined with external data rates of 400 MHz, 533 MHz, 667 MHz, and 800 MHz.

- Effortis currently underway in JEDEC to define a DDR3 SDRAM specification that spans data rates from 800 MHz to 1600 MHz.

- GDDR, GDDR2, and GDDR3 SDRAMstypically run faster than the DDR, DDR2, and DDR3 SDRAMs.

- the DRAM industryhas adopted a technique called “pre-fetching.”

- FIG. 1is a block diagram illustrating a conventional DRAM chip.

- a DRAM chip 100comprises a DRAM core 110 , Internal Data Bus 120 , DRAM interface 130 and External data bus 140 .

- TABLE 4shows the concept of pre-fetching for a DRAM chip.

- the universal DRAM core chipmust be sufficiently wide enough to support the data rates required by many different markets. Obviously there is a limit to how wide the universal DRAM core chip can be before it starts to negatively impact the cost of the chip. In general, if the width of the DRAM core chip is so large so as to make either the core chip or the interface chip pad limited (especially the core chip), the cost of this solution would be very high.

- Modern DRAMsalso feature multiple banks.

- a bankis a section of the DRAM core that can be accessed independently.

- the DRAM coreis broken up into banks that can be active simultaneously. Within each bank, only one row can be open at any given time.

- Most DRAMs up to 512 Mb densitiesare organized into 4 banks. 1 Gb (and possibly, up to 4 Gb) DRAMs are organized into 8 banks but only 4 banks can be activated within a specific time window. This is dictated by power and thermal considerations. So, the universal DRAM core chip must be capable of supporting multiple banks.

- a ⁇ 16 256 Mb SDRAMmay have 4 banks, each of which is 64 Mb.

- Each bankcan be conceptualized as consisting of 16 sub-arrays, each sub-array being a 8192 ⁇ 512 matrix of memory cells. That is, each sub-array has 8192 or 8k rows and 512 columns. So, when a bank is accessed, a particular row is accessed (activated) in each of the 16 sub-arrays in the bank. The row is determined by the row address. After the 16 rows are activated, a particular bit in each row is selected. The bit is specified by the column address. So, on each access to a bank, 16 bits are accessed.

- FIG. 2illustrates a typical organization of a 4-bank modern SDRAM.

- the memory cellsare arranged into four banks: bank 0 ( 220 ), bank 1 ( 210 ), bank 2 ( 230 ) and bank 3 ( 240 ).

- Each bankhas associated word line drivers ( 275 , 280 , 285 and 290 ) and sense amplifiers ( 255 , 260 , 265 and 270 ).

- the banksare selected through use of MUX 250 .

- FIG. 3is a block diagram illustrating one embodiment of banks arranged in sub-arrays.

- each bankhas 16 sub-arrays (each sub-array being 8K ⁇ 512) because the DRAM is organized as a ⁇ 16 memory.

- Each bankhas 32 sub-arrays.

- the reason for having 32 sub-arraysis that DDR SDRAM memory uses a pre-fetching of 2n. Since this is a ⁇ 16 DDR memory, 32 bits must be accessed from each bank for a read or write operation.

- pre-fetchingcan be done in a number of ways.

- a memory arraythat is organized as a P ⁇ Q matrix that needs to support 2n pre-fetching.

- One approachis to divide the P ⁇ Q array into two arrays (i.e. two P ⁇ Q/2 arrays) and access both arrays in parallel, so that we get 2 bits per column address.

- Another approachis to not split the array but modify the column decoder so that 2 bits are selected for each column address (in other words, the least significant bit of the column address is not used).

- the ⁇ 16 256 Mb DDR2 SDRAMis organized similar to the ⁇ 16 256 Mb SDRAM (and the ⁇ 16 256 Mb DDR SDRAM). The following identify some of the changes to the memory core:

- FIG. 4illustrates a block diagram of an interface and multiple banks in a DRAM. As shown in FIG. 4 , bank 0 ( 410 ), bank 1 ( 420 ), bank 2 ( 430 ) and bank 3 ( 440 ) are accessed by interface 450 .

- FIG. 5is a block diagram illustrating a DRAM chip with an interface removed.

- bank 0 ( 510 ), bank 1 ( 520 ), bank 2 ( 530 ) and bank 3 ( 540 )are coupled to I/O pads 550 , 560 , 570 and 580 , respectively.

- some part or all of the multiplexing of the data I/O from the banksis done in the core chip itself.

- FIG. 6illustrates one embodiment for a center bonded DRAM core chip.

- integrated circuit 600includes bank 0 ( 610 ), bank 1 ( 620 ), bank 2 ( 630 ) and bank 3 ( 640 ) coupled to MUX 650 .

- MUX 650is connected to substrate bonding pads 670 via bond wires 680 through I/O pads 660 .

- bond wires 680 that connect I/O pads 660 on the DRAM core die to the substrate bonding pads 670become quite long. Long bond wires have significant inductance and limit the speed at which the memory chip can operate.

- FIG. 7illustrates one embodiment for an edge bonded DRAM core chip.

- integrated circuit 700includes bank 0 ( 710 ), bank 1 ( 720 ), bank 2 ( 730 ) and bank 3 ( 740 ).

- I/O pads 750located on the silicon die 705 , are connected to the substrate bonding pads 760 via bond wires 780 .

- the number of data I/O padswill be equal to 4m as illustrated previously.

- the other optionis to route the data bits from each bank to a centrally located MUX (as shown in FIG. 6 ) and then route the signals from the other side of the MUX to the periphery of the die.

- this means that the data signalswill have to traverse the die twice—once from the bank to the central MUX and once from the central MUX to the periphery.

- This increases routing complexitymay possibly require an extra metal layer on the die (higher cost), and adds to the latency of the memory core.

- an inventive “Distributed-Bank” architectureis used.

- a bankis distributed (or spread) across all 4 quadrants instead of concentrating a bank in only one quadrant.

- data MUXslocated in all 4 quadrants, select the appropriate bank, and the data signals corresponding to the selected bank can be easily routed to the periphery of the chip.

- FIG. 8illustrates one embodiment for a concentrated-bank architecture.

- a ⁇ 16, 4-bank, 256 Mb DDR2 SDRAM coreis used.

- any type of DRAM, with different external data widths, different number of banks, different density, and different amount of pre-fetchingmay be used without deviating from the spirit or scope of the invention.

- each bank ( 810 , 820 , 830 and 840 ) in a ⁇ 16, 4-bank, 256 Mb DDR2 SDRAMconsists of 64 sub-arrays, with each sub-array organized as a 8192 ⁇ 128 array of memory cells.

- FIG. 9illustrates one embodiment for a distributed-bank architecture.

- the DRAM core chipis divided into four quadrants ( 910 , 920 , 930 and 940 ). Each quadrant includes a portion of a bank.

- FIG. 10illustrates one embodiment for a quadrant in a distributed-bank architecture DRAM core chip.

- local data MUXsare located in each quadrant to select one of the four banks.

- FIG. 11is block diagram illustrating one embodiment of a distributed-bank architecture universal DRAM core chip.

- the banks of DRAM cellsare distributed among quadrant 1110 , 1120 , 1130 and 1140 .

- An address decoder 1150located in the center of the chip, controls word line drivers 1155 , 1164 , 1170 and 1176 in quadrants 1110 , 1120 , 1130 and 1140 respectively.

- the data from the bank sub-arraysare output to sense amplifiers ( 1157 , 1166 , 1172 and 1178 ) and input to the respective bank select MUXs ( 1160 , 1168 , 1174 and 1180 ).

- the datais then routed to data I/O pads 1162 located in the proximity for each of the quadrants.

- the interface chipmay be designed or configured to act similar to a ⁇ 16 DDR2 SDRAM, ⁇ 8 DDR2 SDRAM, ⁇ 4 DDR2 SDRAM, ⁇ 2 DDR2 SDRAM, or ⁇ 1 DDR2 SDRAM.

- the interface chipmay be designed to support any data width between ⁇ 1 and ⁇ 16 when operating in a 4n pre-fetch mode.

- the distributed-bank architectureis flexible enough to support protocols like SDRAM, DDR SDRAM, DDR2 SDRAM, and DDR3 SDRAM.

- the DRAM core chip shown in FIG. 11may be configured or used as shown in FIG. 12 to support DDR2 speeds.

- FIG. 12is a block diagram illustrating a distributed-bank architecture DRAM core chip configured to support DDR2 speeds.

- MUX 1210selects 64 bits of data for one of the banks ( 1220 , 1230 , 1240 and 1250 ).

- MUX 1210represents the data MUXs located in all four quadrants on the DRAM core chip.

- the DRAM core chip shown in FIG. 11may also be configured or used as shown in FIG. 13 to support DDR SDRAM speeds when it is operated in a 2n pre-fetch mode.

- FIG. 13is a block diagram illustrating a distributed-bank architecture DRAM core chip configured to support DDR speeds and external bus widths from 17 to 32 bits.

- MUX 1310selects 64 bits of data for one of the banks ( 1320 , 1330 , 1340 and 1350 ).

- the mode of operation shown in FIG. 13may be used with the appropriate interface chip to support external data widths between (and inclusive) of 17 and 32 in a 2n pre-fetch mode.

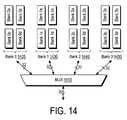

- FIG. 14is a block diagram illustrating a distributed-bank architecture DRAM core chip configured to support DDR speeds and external bus widths from 9 to 16 bits.

- MUX 1410selects 32 bits of data for one of the banks ( 1420 , 1430 , 1440 and 1450 ).

- FIG. 15is a block diagram illustrating a distributed-bank architecture DRAM core chip configured to support DDR speeds and external bus widths from 1 to 8 bits.

- MUX 1510selects 16 bits of data for one of the banks ( 1520 , 1530 , 1540 and 1550 ).

- the internal data bus width(the width of the bus between the DRAM core chip and the interface chip) may be configured to match the amount of pre-fetching required (which is determined by the external data rate) and the width of the external data bus.

- the external data busis the bus from the interface chip to the ASIC or memory controller.

- the DRAM core chip as shown in FIG. 11may be configured to support the following modes and requirements shown in TABLE 6. TABLE 6 Internal Data Pre- Minimum External Maximum External Bus Width Fetching Used Data Bus Width Data Bus Width 64 8n 1 8 4n 1 16 2n 1 32 1n 1 64 32 8n 1 4 4n 1 8 2n 1 16 1n 1 32 16 8n 1 2 4n 1 4 2n 1 8 1n 1 16

- the proposed DDR3 SDRAMis an example of an 8n pre-fetch protocol

- DDR2 SDRAMis an example of a 4n pre-fetch protocol

- DDR SDRAMis an example of a 2n pre-fetch protocol

- SDRAMis an example of a in pre-fetch protocol (i.e. no pre-fetching needed).

- Mode[ 1 : 0 ]may be inputs to the DRAM core chip so that the internal data bus width is selected through external means.

- the Mode[ 1 : 0 ] inputs to the core chipmay be selected by means of fuses on the core chip or on the interface chip, by means of pull-up or pull-down resistors in the package of either chip (or in the common package) or on the printed circuit board, or may be driven by a register on the interface chip, or may be part of the address input to the core chip.

- FIG. 16illustrates one embodiment for a portion of a DRAM core chip that includes a decoder for selecting a mode of operation.

- the decoder 1610 in the core chipis aware of the Mode[ 1 : 0 ] inputs as shown in FIG. 16 .

- a universal DRAM core chipsuch as the embodiment shown in FIG. 11 , may be configured to support a wide variety of data speeds and widths.

- the core chip shown in FIG. 11may support data rates up to 8*f MB/s, where f is the maximum clock rate (in MHz) at which the DRAM core can run in sync with the external data bus without using pre-fetching (i.e. using a pre-fetching of in).

- fis typically between 100 MHz and 200 MHz. So, the DRAM core chip shown in FIG. 11 supports maximum data rates between 800 MB/s and 1600 MB/s (1.6 GB/s).

- Semiconductor fabrication processis inherently statistical in nature. That is, if we fabricate a statistically significant number of identical chips, some of the chips will only be capable of operating below the target speed, some of the chip will be capable of operating at the target speed, and some of the chips will be capable of operating above the target speed. These are known in the industry as slow, typical, and fast parts respectively. Usually, the fast parts are sold at a price premium over the other parts while the slow parts are sold at lower prices compared to the typical parts.

- Attach interface chips designed for low power marketse.g. an SDRAM-like interface for the cell phone market

- Attach interface chips designed for low power marketse.g. an SDRAM-like interface for the cell phone market

- Attach interface chips designed for the high performance/speed marketse.g. a GDDR3-like interface for the game console market

- Attach interface chipsdesigned for the high performance/speed markets (e.g. a GDDR3-like interface for the game console market) to the fast core parts

- Attach interface chipsdesigned for markets sensitive to both power and performance (e.g. a DDR-like interface for the server market) to the typical core parts.

- Speed binning of memory chipsis typically done after it is packaged. Note that it is possible to do a simple speed sort of the memory chips at the wafer level itself. In order to do a speed sort or speed bin, we need to use ATE (automatic test equipment), also known as tester.

- ATEautomated test equipment

- the DRAM core chipsWhen we speed bin the DRAM core chips, we need to measure the time required for basic operations like Read, Write, Activate (open one or more pages), Precharge (close one or more pages), and Refresh.

- the DRAM core chipsdefined by the present invention, are fully functional asynchronous DRAM chips capable of stand-alone operation. In other words, the DRAM core chips contain all the necessary circuits and capabilities needed to access the internal array used to store the data.

- the partially functional diesi.e. those with some defective rows and/or columns

- Interface chipsthat are designed for high performance markets may be attached to the DRAM core dies that do not have any defective rows and/or columns in the main array.

- These DRAM core chipsmay then be attached to interface chips that are designed for high performance markets.

- DDR2 SDRAMuses 4n pre-fetching. This means that for an n-bit wide external data bus, 4n data bits are accessed from the memory core for every read or write.

- increasing the amount of pre-fetchingincreases the amount of metal interconnects on the die, which has a modest impact on the cost.

- increasing the amount of pre-fetchingmay make either the memory core chip or the interface chip or both pad limited. Being pad limited can increase the cost substantially.

- Burst modeis another technique that can be used to increase the data rate of memory chips.

- the memory chipreads or writes multiple data bits per column address.

- an n-bit wide (external data bus width) memory chip that is configured for a burst mode of 4nwill access 4n bits from the memory core for a given column address. So this is quite similar to a 4n pre-fetch except that in burst mode, the same data wires are used.

- the internal data bus between the memory core and the interfaceis only n-bits wide. Each line in the internal bus carries 4 data bits that are separated in time.

- FIG. 17 ais a block diagram illustrating the relationship between the internal data bus rate and the external data bus rate for 4n pre-fetching.

- Memory core 1710is coupled to memory interface 1720 via internal data bus 1715 at 4n @ f 1 , Hz data rate.

- the memory interface 1720is coupled to external data bus 1725 , and under these conditions, the external data bus operates at a n @ 4*f 1 , Hz data rate.

- FIG. 17 bis a block diagram illustrating the relationship between the internal data bus rate and the external data bus rate for burst mode with a length of 4n.

- Memory core 1730is coupled to memory interface 1750 via internal data bus 1740 at n @ 4*f 2 , Hz data rate.

- the memory interface 1750is coupled to external data bus 1760 , and for the burst mode of operation, the external data bus operates at a n @ 4*f 2 , Hz data rate.

- burst modedoes not increase the amount of off-chip connections between the core chip and the interface chip. So, in some embodiments, it is preferable to design the DRAM core chip of this invention with burst mode capability.

- one of the aspects of this inventionis the ability to test and speed bin the memory core chips and then attach the appropriate interface chips.

- Testing and speed binning of the DRAM core chipis usually done on a tester. This requires the core chip to have sufficiently strong output drivers to drive the inputs of the tester, which are usually some distance (several inches) from the outputs of the core chip. However, in the normal mode of operation, the inputs of the interface chip will be much closer ( ⁇ 1′′) to the outputs of the core chip. So, it is not necessary to have strong output drivers in the core chip in the normal mode of operation. In order to satisfy both requirements, in some embodiments the DRAM core chip preferably has output drivers whose strength or drive capability is adjustable.

- the core chipmay have, by default, normal strength output drivers that are capable of driving signals across some distance to the inputs of the tester. However, when an interface chip is attached to the core chip, a signal from the interface chip decreases the drive strength of the core chip's output drivers.

- the output drivers of interface chip that interface with the DRAM core chiphave similar adjustable drive strength capability. This allows testing of the interface chips separately prior to attaching them to the core chips.

- the adjustable drive strength driversare not necessarily required on the interface chip on the pins that interface to the electronic host system. However, it is preferable to have the adjustable strength capability on these drivers as well so that the drive strength can be tailored to the requirements of the system or external world.

- the strength of the output drivers on the interface chip that communicate with the core chipare preferably controlled by a signal from the core chip.

- FIG. 18is a block diagram illustrating an example multi-chip memory implementation.

- the solutionincludes a DRAM core chip 1810 and an interface chip 1820 .

- the main characteristics of the DRAM core chip of this inventionare:

- a plurality of DRAM core chipsmay be coupled together with one or more interface chips;

- a plurality of interface chipsmay be coupled together with one or more DRAM core chips;

- the interface on the DRAM core chipmay include a custom and/or industry standard interface

- Has address inputs(bank address, row address, column address—row and column address can be on separate inputs or multiplexed on same pins);

- Has control inputs that determine mode of operationare inputs that determine the width of the internal data bus (bus between the memory core chip and interface chip) and inputs that determine the strength of the output drivers;

- Internal data bus width⁇ external data bus width (bus from interface chip to memory controller or ASIC);

- the main characteristics of the interface chip of this inventionare:

- Interface chipimplements an industry standard protocol like DDR SDRAM, DDR2 SDRAM, GDDR2 SDRAM, etc.;

- Interface chipimplements an industry standard protocol with custom extensions (e.g. GDDR2 SDRAM with extensions as specified by mutual agreement with one or more customers);

- custom extensionse.g. GDDR2 SDRAM with extensions as specified by mutual agreement with one or more customers

- Interface chipimplements a fully custom protocol as specified by one or more customers or a fully custom protocol developed in-house;

- Interface chipoperates as a transformer to convert protocols from the external interface to the interface of the DRAM core chip (e.g., synchronous to asynchronous and asynchronous to synchronous);

- Interface chipdetermines the signaling used by the external interface

- push-pull outputsopen drain/collector outputs

- Examplespecial error detection and error correction capabilities, as well as other types of redundancy capabilities and functions.

- the DRAM core chip and the interface chip of this inventionmay be attached together in a number of different ways:

- the core chip diemay be put in a separate package, and then the interface chip die may then be electrically attached to the package containing the core chip die;

- the interface chip diemay be put in a separate package, and then the core chip die may then be electrically attached to the package containing the interface chip die;

- the core chip diecan be put in a separate package; the interface chip die may be put in a separate package; and the two packages can be electrically attached to each other;

- Multiple DRAM core chip diesmay be put in a separate package; the interface chip die may be put in a separate package; and the two packages can be electrically attached to each other;

- a DRAM core chip diemay be put in a separate package; multiple interface chip dies may be put in a separate package; and the two packages can be electrically attached to each other;

- the DRAM core chip die and the interface chip diemay be electrically attached in any way without deviating from the spirit or scope of the invention.

- One aspect of this inventionis that a multi-chip DRAM that is built according to this invention, might have higher cost than a traditional DRAM, especially if the DRAM core chip die and the interface chip die were packaged separately and then attached to each other. This is due to the cost associated with the extra package.

- One way to ameliorate thisis to put multiple DRAM core chip dies in a single package. For the purpose of this discussion, we shall consider putting two DRAM core chip dies in a single package, each die being a 256 Mb density device.

- a typical DRAM manufacturing processmight have the following sequences after the wafer has been fully processed:

- DRAM dies on a waferare tested at low speed and dies with defective rows and/or columns are marked;

- the defective rows and/or columnsare replaced with redundant rows and/or columns;

- Waferis diced into individual dies, which are then packaged;

- Packaged partsare tested for functionality—parts damaged by the packaging process are eliminated;

- Burnt in partsare optionally tested again for functionality and shipped.

- Bin Aboth the DRAM core chip dies are functional, so the total capacity is 512 Mb

- Bin Bonly one of the DRAM core chip dies is functional, so the total capacity is 256 Mb

- Bin Cneither of the DRAM core chip dies is functional, so the total capacity is 0 Mb

- the bin C partsshould be discarded.

- the bin B partsfor those markets and/or customers who require only 256 Mb devices.

- a handheld device manufacturermight require only a 256 Mb DRAM. So, the bin B parts can be attached to the interface chips designed for this manufacturer.

- Other markets and/or manufacturersmight require 512 Mb devices.

- a network router manufacturermight need 512 Mb DRAMs. So, we can use bin A parts for this manufacturer by attaching the appropriate interface chips to the bin A parts. This concept can be extended to cover more than two DRAM core chip dies in a single package as well as DRAM core chip dies of all densities.

- some embodimentscover the idea of attaching multiple DRAM core chips to a single interface chip.

- the core chipsmay be attached to the interface chip in a number of different ways. Some of these ways are described below and in FIG. 19 . Again, for the purpose of illustration, we shall assume that two 4-bank 256 Mb DRAM core chips ( FIG. 11 ) are attached to the interface chip. Each of the core chips has a 64-bit wide data bus designed to connect to the interface chip. Note that the idea explained below can be applied to DRAM core chips with different number of banks, density, data bus width, etc.

- the row addressesare used to select the DRAM core chip.

- bank addressesare used to select DRAM core chips.

- column addressesare used to select the DRAM core chip.

- the two DRAM core chipsare attached to the interface chip such that only one of the core chips is accessible at any given time. That is, the two core chips look to the electronic host system as a single 512 Mb DRAM with 4 banks. This implies that the interface chip will use the row address to select one or the other core chip.

- the two DRAM core chipsare attached to the interface such that both of the core chips are accessible at any given time, and that the two chips look to the external world electronic host system as a single 512 Mb DRAM with 8 banks. This implies that the interface chip will use the bank address to select one or the other core chip.

- the two DRAM core chipsare attached to the interface chip such that both of the core chips are accessible at any given time, and that the two chips look to the electronic host system as a single 512 Mb DRAM with 4 banks.

- the interface chipuses the column address to select one or the other core chip. Note that in other embodiments an interface chip always accesses both the core chips in parallel, so that the data bus between the core chips and the interface chip becomes 128-bits wide. For this embodiment, the interface chip doubles the external data rate. In other words, the amount of pre-fetching has been doubled.

- the multi-chip solutionis configured such that the attachment of the DRAM core chips to the interface chip is programmable.

- the customermay choose between one of the three methods listed above to attach two 4-bank, 64-bit wide, 256 Mb DRAM core chips to an interface chip by programmable means. These means include using fuses on the interface chip or the core chips, pull-up or pull-down resistors on the package substrates or printed circuit board, or by means of a register on the interface chip or core chips.

- any way of attaching the DRAM core chips to the interface chipmay be accomplished without deviating from the spirit or scope of the invention.

- inventions of the inventioninclude building redundant memory systems by attaching multiple DRAM core chips to an interface chip. For example, when more than one core chip is attached to an interface chip, redundancy is added by several means including:

- the interface chipcan read the multiple copies of the data from the different core chips and select the correct copy and transmit it to the memory controller.

- the correct copycan be determined by means like majority voting, and/or by the use of parity or ECC bits;

- Another aspect of this inventionis placing memory core chips of different types behind a common interface chip.

- DRAMDynamic Random Access Memory

- SRAMStatic Random Access Memory

- FlashFlash

- MCPMulti-Chip Package

- Another aspect of this inventionis placing a large and slow memory as well as a smaller and faster memory behind a common interface chip and using the faster memory as a cache for the slower memory.

- an SRAM chipmight be used as the cache for a DRAM core chip or a DRAM core chip can be used as the cache for a Flash chip.

- the cache management logicmay be built into the interface chip so that the cache is transparent to the memory controller. Alternately, the cache may be made visible to the memory controller and managed by the memory controller. Let us consider the case of an interface chip that has been designed to interface to one or more DRAM core chips and an SRAM chip.

- the SRAM chipcan be used to cache the rows in the DRAM core chips that were recently opened.

- the SRAMmay be used to cache the entire contents of the recently opened rows in the DRAM or cache part of the contents of the recently opened rows in the DRAM.

- the properties of the cachemay be determined by programming certain registers in the interface chip. By storing data that has a high likelihood of being accessed in the near future, system performance is improved.

- a cachealso allows the interface chip to do speculative pre-fetching of data from the DRAM core chip (and storing it in the SRAM cache chip), which again improves system performance.

- the interface chipmay operate with SRAM chips (that are used as caches) of different densities. This allows the same interface chip to be used across several different segments within a market.

- a DRAM/SRAM combination memory devicemay includes a common interface where the DRAM capacity is 512 Mb and the SRAM capacity ranges from 0 to 32 Mb.

- the techniques of the present inventionare not just applicable to DRAM.

- the DRAM core chipneed not necessarily be a trench-capacitor or stacked-capacitor device.

- the present inventionis applicable to a variety of memory technologies like MRAM (Magnetic RAM), FRAM (Ferro-electric RAM), Ovonics memory, molecular memory (e.g. memory technology developed by ZettaCore), carbon nanotube memory (e.g. memory technology developed by Nantero Inc.), etc.

- Another aspect of this inventionis that it can be used with DRAM core chips that have different architectures like FCRAM (Fast Cycle RAM), RLDRAM (Reduced Latency DRAM), ESDRAM (Enhanced SDRAM).

- FCRAMFlust Cycle RAM

- RLDRAMReduced Latency DRAM

- ESDRAMEnhanced SDRAM

- Some embodiments of inventionallow the use of a common memory core across a wide range of markets while varying the interface of the memory core according to the market and customer needs. It also allows the interface to be kept constant while changing the memory core behind the interface to address the needs of the different segments within a market.

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Databases & Information Systems (AREA)

- Dram (AREA)

- For Increasing The Reliability Of Semiconductor Memories (AREA)

Abstract

Description

- This patent application claims the benefit to U.S. Provisional Patent Application entitled “Methods and Apparatus for Integrating Multi-Chip Memory Devices,” Ser. No. 60/693,631, filed on Jun. 24, 2005.

- 1. Field of the Invention

- The present invention is directed toward the field of building custom memory systems cost-effectively for a wide range of markets.

- 2. Art Background

- Dynamic Random Access Memory (DRAM) is the most popular type of volatile memory and is widely used in a number of different markets. The popularity of DRAMs is mostly due to their cost-effectiveness (Mb/$). The PC main memory market has traditionally been the largest consumer of DRAMs. However, in recent times, other important markets have adopted DRAMs. A report published by De Dios and Associates showed that in 2004, the PC main memory market consumed only 50% of the total DRAM bits.

- Several of the non-PC markets use specialty or legacy memories. Specialty memory is typically memory that is not used by the PC main memory but is memory that is designed for one or more niche markets. For example, the PC graphics market uses GDDR (Graphics Dual Data Rate) DRAM. Similarly, some segments of the network infrastructure market use FCRAM (Fast Cycle RAM) or RLDRAM (Reduced Latency DRAM). Legacy memory is typically memory that was used in the past but is not used in that particular market segment now. For example, SDRAM (Synchronous DRAM) was used for PC main memory from ˜1997 to ˜2001 but is no longer used today for PC main memory. Instead, most cellular phones and handheld (or mobile) devices use SDRAM today.

- Bringing a new DRAM architecture into the market requires significant investment of time and money. For example, it typically takes 4 years for JEDEC to approve a new DRAM architecture. DRAM makers must then spend hundreds of millions of dollars to productize the new architecture. Unless the investment is amortized over an extremely large number of devices, the cost of the new devices will be high. In addition, the DRAM makers have optimized their manufacturing flow for high volumes. Any deviation from the norm disrupts the flow. This is the reason why specialty and legacy memory typically carry a price premium over memory used by the PC main memory market (which is usually referred to as commodity memory).

- Given the time and money required to bring a new DRAM architecture into the market, it is obvious that the industry does not have the luxury of being able to define a DRAM architecture that exclusively meets the needs of the smaller markets for DRAMs. For example, it is difficult for the DRAM makers to cost-effectively produce a DRAM that perfectly meets the needs of the cell phone market. Therefore, it is even more difficult for each cell phone maker (e.g. Nokia or Motorola) to design DRAMs tailor made for its phones. So, cell phone designers are forced to choose the DRAM architecture that is least objectionable from their perspective. Hence the selection of SDRAM for cell phones.

- This situation will become even worse in the future. Most analyst projections show that not only will DRAM usage expand rapidly into newer markets but also that the DRAM bit consumption growth rate will be higher for non-PC markets. The needs of these markets are quite different from the needs of the PC main memory market. Clearly, there is a need in the market for a way to quickly and cost-effectively build custom memory that is tailor made for a customer's exact needs.

- A method combines memory core integrated circuit dies with interface integrated circuit dies to configure a memory device. At least one test on the memory core integrated circuit dies is conducted. In one embodiment, the test measures the amount of time required for a read, write, activate, pre-charge, or refresh operations. From the test, at least one characteristic of the memory core integrated circuit dies is identified. In one embodiment, the characteristic comprises the speed of operation for the memory core integrated circuit die. The interface integrated circuit die is electrically coupled to the memory core integrated circuit die based on the memory core integrated circuit characteristic.

- In one embodiment, the memory core integrated circuit dies are speed binned based on “slow”, “typical” and “high” speed. The slow memory core integrated circuit dies are coupled to an interface integrated circuit die designed for low power markets. The typical speed memory core integrated circuit dies are coupled to an interface integrated circuit die designed for power conservation and performance markets. Also, the high-speed memory core integrated circuit dies are coupled to an interface integrated circuit die designed for high performance markets.

- In other embodiments, an effective data rate for an interface on the memory core integrated circuit die is configured based on the speed of operation of the memory core integrated circuit die. An interface integrated circuit die is electrically coupled to the memory core integrated circuit die to operate with an external bus and to operate in conjunction with the effective data rate of the interface on the memory core integrated circuit die.

FIG. 1 is a block diagram illustrating a conventional DRAM chip.FIG. 2 illustrates a typical organization of a 4-bank modern SDRAM.FIG. 3 is a block diagram illustrating one embodiment of banks arranged in sub-arrays.FIG. 4 illustrates a block diagram of an interface and multiple banks in a DRAM.FIG. 5 is a block diagram illustrating a DRAM chip with an interface removed.FIG. 6 illustrates one embodiment for a center bonded DRAM core chip.FIG. 7 illustrates one embodiment for an edge bonded DRAM core chip.FIG. 8 illustrates one embodiment for a concentrated-bank architecture.FIG. 9 illustrates one embodiment for a distributed-bank architecture.FIG. 10 illustrates one embodiment for a quadrant in a distributed-bank architecture DRAM core chip.FIG. 11 is block diagram illustrating one embodiment of a distributed-bank architecture universal DRAM core chip.FIG. 12 is a block diagram illustrating a distributed-bank architecture DRAM core chip configured to support DDR2 speeds.FIG. 13 is a block diagram illustrating a distributed-bank architecture DRAM core chip configured to support DDR speeds and external bus widths from 17 to 32 bits.FIG. 14 is a block diagram illustrating a distributed-bank architecture DRAM core chip configured to support DDR speeds and external bus widths from 9 to 16 bits.FIG. 15 is a block diagram illustrating a distributed-bank architecture DRAM core chip configured to support DDR speeds and external bus widths from 1 to 8 bits.FIG. 16 illustrates one embodiment for a portion of a DRAM core chip that includes a decoder for selecting a mode of operation.FIG. 17 ais a block diagram illustrating the relationship between the internal data bus rate and the external data bus rate for 4n pre-fetching.FIG. 17 bis a block diagram illustrating the relationship between the internal data bus rate and the external data bus rate for burst mode with a length of 4n.FIG. 18 is a block diagram illustrating an example multi-chip memory implementation.FIG. 19 illustrates techniques for stacking two DRAM core chips behind a single interface chip.- The disclosure of U.S. Provisional Patent Application Ser. No. 60/693,631, entitled “Methods and Apparatus for Integrating Multi-Chip Memory Devices”, filed on Jun. 24, 2005, is hereby expressly incorporated herein by reference.

- By examining several different DRAM architectures, it is clear that the internal organizations of the DRAMs are quite similar. For example, a ×16 (×16 denotes the external data width) 256 Mb SDRAM, ×16 256 Mb DDR SDRAM, and ×16 256 Mb DDR2 SDRAM consist of:

- Control logic block;

- Address input register and decoder;

- Memory arrays that store the data;

- Data selection circuit (I/O gating);

- Data read circuit; and

- Data write circuit.

- It is obvious that most of the blocks are common across all the three architectures. The main differences are in the control logic block (which implements the protocol, among other functions), in the width of the data that is accessed per column address, and in the data I/O section. These are usually considered part of the interface section of the DRAM while the rest of the circuits (address decoder, memory arrays, and data selection) are considered part of the memory core. The core timing parameters are typically specified in absolute units of time (seconds) rather than in terms of clock periods. For example, the Micron 256 Mb DDR2 SDRAM data sheet lists the following core timing parameters:

TABLE 1 Speed Grade tRCD(ns) tRP(ns) tRC(ns) − 5E 15 15 55 − 37E 15 15 55 −3 15 15 55 −3E 12 12 54 - Similarly, the Micron 256 Mb DDR SDRAM data sheet identifies the following timing specifications:

TABLE 2 Speed Grade tRCD(ns) tRP(ns) tRC(ns) −75Z 20 20 65 −75 20 20 65 - The Micron 256 Mb SDRAM data sheet discloses the following specifications:

TABLE 3 Speed Grade tRCD(ns) tRP(ns) tRC(ns) − 7E 15 15 60 −75 20 20 66 - So, even though the protocol and speed of SDRAM, DDR SDRAM, and DDR2 SDRAM are quite different, it is clear that the internal core or array of all these types of DRAMs has similar characteristics. In fact, we can go even further and observe that all synchronous DRAMs are composed of an asynchronous core and an interface that defines the protocol, synchronous operation, speed, and signaling. The memory core typically comprises ˜90%-95% of the total die area.

- Current practice is to integrate the memory core and the interface onto a common die. The drawback with this approach is that a change in the protocol, speed, or signaling for example requires a re-design of the entire chip. This is usually very expensive and time consuming, and hence the inability to bring specialty or custom DRAMs to the market quickly and cost-effectively. One embodiment of the invention comprises a multi-chip implementation, wherein one or more DRAM core chips are attached to an interface chip. The interface chip sits between the host electronic system and the DRAM core chips. In other words, the interface chip can be thought of as a “wrapper” that surrounds the DRAM core chips. The partitioning of the conventional DRAM into DRAM core chip and interface chip should preferably be done is such a way that that the functions and circuits that are relatively constant across many different architectures are retained in the DRAM core chip while the functions and circuits that vary between the different architectures are moved to the interface chip.

- The DRAM core chip can be designed to be suitable for a large number of markets (i.e. a “universal core”). The interface chip can now be designed to meet the exact needs of a market, and even the exact needs of individual customers in that market. To illustrate, the proposed solution enables the design of an interface chip to meet the exact needs of Nokia for the cell phone market and another interface chip to meet the exact needs of Motorola for the cell phone market.

- In order to accommodate the needs of the different markets, the DRAM core chip must be capable of operating across a wide range of frequencies, be capable of supporting high data rates, and must be low cost. In one embodiment, the DRAM core chip is asynchronous, wide, and operates at its natural speed. For the case of modern DRAM cores, the natural speed is between 5 ns to 10 ns per column access, which is equivalent to 100 MHz to 200 MHz synchronous operation. That is, a modern DRAM core can keep up with an external memory bus or interface that runs at a speed from 100 MHz to 200 MHz. So, for the case of a synchronous DRAM that operates at 100 MHz to 200 MHz and is n-bits wide (1≦n≦32 typically), n bits can be fetched from the DRAM core once every clock cycle. In fact, this is how SDRAMs operate.

- Newer synchronous DRAMs run at higher clock speeds. JEDEC defines the DDR SDRAM specification with external data rates of 200 MHz, 266 MHz, 333 MHz, and 400 MHz. An even newer specification called DDR2 SDRAM has been defined with external data rates of 400 MHz, 533 MHz, 667 MHz, and 800 MHz. Effort is currently underway in JEDEC to define a DDR3 SDRAM specification that spans data rates from 800 MHz to 1600 MHz. GDDR, GDDR2, and GDDR3 SDRAMs typically run faster than the DDR, DDR2, and DDR3 SDRAMs. However, even though the external data rate has been increasing quite rapidly, the speed of the DRAM core has not kept pace. In order to bridge the gap between the external data rate and the internal core speed, the DRAM industry has adopted a technique called “pre-fetching.”

- Pre-fetching involves accessing more bits than the external data bus width on every column access. To illustrate, an n-bit wide DDR SDRAM accesses 2n bits every column access. This allows the external data bus to run at 200 MHz to 400 MHz while the internal memory core runs at 100 MHz to 200 MHz respectively.

FIG. 1 is a block diagram illustrating a conventional DRAM chip. ADRAM chip 100 comprises aDRAM core 110, Internal Data Bus120,DRAM interface 130 and External data bus140. TABLE 4 shows the concept of pre-fetching for a DRAM chip.TABLE 4 External Internal Data Data External Internal Bus 140 Bus 120 Data Data Protocol Width Width Rate (MHz) Rate (MHz) SDRAM N n 66-133 66-133 DDR SDRAM N 2n 200-400 100-200 DDR2 SDRAM n 4n 400-800 100-200 DDR3 SDRAM n 8n 800-1600 100-200 (proposed) - This implies that the universal DRAM core chip must be sufficiently wide enough to support the data rates required by many different markets. Obviously there is a limit to how wide the universal DRAM core chip can be before it starts to negatively impact the cost of the chip. In general, if the width of the DRAM core chip is so large so as to make either the core chip or the interface chip pad limited (especially the core chip), the cost of this solution would be very high.

- Modern DRAMs also feature multiple banks. A bank is a section of the DRAM core that can be accessed independently. The DRAM core is broken up into banks that can be active simultaneously. Within each bank, only one row can be open at any given time. Most DRAMs up to 512 Mb densities are organized into 4 banks. 1 Gb (and possibly, up to 4 Gb) DRAMs are organized into 8 banks but only 4 banks can be activated within a specific time window. This is dictated by power and thermal considerations. So, the universal DRAM core chip must be capable of supporting multiple banks.

- Let us consider the internal organization of a ×16 256 Mb SDRAM. A ×16 256 Mb SDRAM may have 4 banks, each of which is 64 Mb. Each bank can be conceptualized as consisting of 16 sub-arrays, each sub-array being a 8192×512 matrix of memory cells. That is, each sub-array has 8192 or 8k rows and 512 columns. So, when a bank is accessed, a particular row is accessed (activated) in each of the 16 sub-arrays in the bank. The row is determined by the row address. After the 16 rows are activated, a particular bit in each row is selected. The bit is specified by the column address. So, on each access to a bank, 16 bits are accessed.

FIG. 2 illustrates a typical organization of a 4-bank modern SDRAM. The memory cells are arranged into four banks: bank0 (220), bank1 (210), bank2 (230) and bank3 (240). Each bank contains P×Q×16 cells (e.g., P=8192 and Q=512 for a 256 Mb SDRAM). Each bank has associated word line drivers (275,280,285 and290) and sense amplifiers (255,260,265 and270). The banks are selected through use ofMUX 250.- In one embodiment, the banks are organized in sub-arrays.

FIG. 3 is a block diagram illustrating one embodiment of banks arranged in sub-arrays. For this embodiment, each bank has 16 sub-arrays (each sub-array being 8K×512) because the DRAM is organized as a ×16 memory. - Consider the internal organization of a ×16 256 Mb DDR SDRAM. The ×16 256 Mb DDR SDRAM is organized similar to the ×16 256 Mb SDRAM with some changes to the memory core. The more important changes to the core organization are:

- Each bank has 32 sub-arrays; and

- Each sub-array is now 8192×256 matrix (i.e. P=8192, Q=256). The reason for having 32 sub-arrays is that DDR SDRAM memory uses a pre-fetching of 2n. Since this is a ×16 DDR memory, 32 bits must be accessed from each bank for a read or write operation.

- Note that pre-fetching can be done in a number of ways. Consider a memory array that is organized as a P×Q matrix that needs to support 2n pre-fetching. One approach is to divide the P×Q array into two arrays (i.e. two P×Q/2 arrays) and access both arrays in parallel, so that we get 2 bits per column address. Another approach is to not split the array but modify the column decoder so that 2 bits are selected for each column address (in other words, the least significant bit of the column address is not used). Some embodiments of the invention are described that use the first approach. However, the teachings of the present invention are applicable to different pre-fetching implementations.

- Looking at the organization of a ×16 256 Mb DDR2 SDRAM, the ×16 256 Mb DDR2 SDRAM is organized similar to the ×16 256 Mb SDRAM (and the ×16 256 Mb DDR SDRAM). The following identify some of the changes to the memory core:

- Each bank has 64 sub-arrays. Each sub-array is now a 8192×128 matrix (i.e. P=8192, Q=128). The reason for the 64 sub-arrays per bank is that DDR2 SDRAM uses a 4n pre-fetching. Since this is a ×16 DDR2 memory (n=16), 64 bits must be accessed from each bank for a read or write operation.

- In all cases (SDRAM, DDR, DDR2), data bits to/from each bank are brought to a multiplexer/de-multiplexer (hereafter referred to as a MUX), which in turn is connected to the external DQ pins. This MUX is typically in the middle of the DRAM chip.

FIG. 4 illustrates a block diagram of an interface and multiple banks in a DRAM. As shown inFIG. 4 , bank0 (410), bank1 (420), bank2 (430) and bank3 (440) are accessed byinterface 450. Note that for SDRAM, m=n, for DDR SDRAM, m=2n, DDR2 SDRAM, m=4n, and DDR3 SDRAM (proposed), m=8n, Also note that the data MUX is typically part of the interface. - This arrangement works well for a conventional DRAM since everything is on a single die. However, in one embodiment of the invention, the interface is on a separate die. If we were to just move the interface alone (to another die) without disturbing the memory core, then the number of I/O pads on both the memory core chip and the interface chip will become quite large, as shown in TABLE 5 below for a ×16 4-bank implementation.

FIG. 5 is a block diagram illustrating a DRAM chip with an interface removed. For this embodiment, bank0 (510), bank1 (520), bank2 (530) and bank3 (540) are coupled to I/O pads TABLE 5 Total Number of External Data Bus Off-Chip Data Protocol Width (n) m Pins (4m) SDRAM 16 16 64 DDR SDRAM 16 32 128 DDR2 16 64 256 SDRAM DDR3 16 128 512 SDRAM - So, it is quite obvious that removing the interface without disturbing the rest of the memory core quickly leads to a very large number of off-chip connections, especially for wider external data bus widths and higher data speeds (because, the amount of pre-fetching will increase with higher data speeds). Under these conditions, either the DRAM core chip or the interface chip or both will become pad limited, which will increase the cost of the total solution.

- In one embodiment, in order to reduce the number of off-chip connections between the DRAM core chip and the interface chip, some part or all of the multiplexing of the data I/O from the banks is done in the core chip itself.

- One option is to route all the data bits from each bank to a central MUX, and then connect the other side of the MUX to off-chip drivers. This is quite similar to the current practice for center bonded DRAMs.

FIG. 6 illustrates one embodiment for a center bonded DRAM core chip. For this example, integratedcircuit 600 includes bank0 (610), bank1 (620), bank2 (630) and bank3 (640) coupled toMUX 650.MUX 650 is connected tosubstrate bonding pads 670 viabond wires 680 through I/O pads 660. - The drawback with this approach is that

bond wires 680 that connect I/O pads 660 on the DRAM core die to thesubstrate bonding pads 670 become quite long. Long bond wires have significant inductance and limit the speed at which the memory chip can operate. - In another embodiment, edge bonding for the core chip is used.

FIG. 7 illustrates one embodiment for an edge bonded DRAM core chip. For this embodiment, integratedcircuit 700 includes bank0 (710), bank1 (720), bank2 (730) and bank3 (740). I/O pads 750, located on the silicon die705, are connected to thesubstrate bonding pads 760 viabond wires 780. - If the DRAM core was organized with one bank per quadrant, then the number of data I/O pads will be equal to 4m as illustrated previously. The other option is to route the data bits from each bank to a centrally located MUX (as shown in

FIG. 6 ) and then route the signals from the other side of the MUX to the periphery of the die. However, this means that the data signals will have to traverse the die twice—once from the bank to the central MUX and once from the central MUX to the periphery. This increases routing complexity, may possibly require an extra metal layer on the die (higher cost), and adds to the latency of the memory core. - In another embodiment, an inventive “Distributed-Bank” architecture is used. In this architecture, a bank is distributed (or spread) across all 4 quadrants instead of concentrating a bank in only one quadrant. Using this architecture, data MUXs, located in all 4 quadrants, select the appropriate bank, and the data signals corresponding to the selected bank can be easily routed to the periphery of the chip.

FIG. 8 illustrates one embodiment for a concentrated-bank architecture. For the purpose of this illustration, a ×16, 4-bank, 256 Mb DDR2 SDRAM core is used. However, any type of DRAM, with different external data widths, different number of banks, different density, and different amount of pre-fetching may be used without deviating from the spirit or scope of the invention. As previously shown, each bank (810,820,830 and840) in a ×16, 4-bank, 256 Mb DDR2 SDRAM consists of 64 sub-arrays, with each sub-array organized as a 8192×128 array of memory cells.FIG. 9 illustrates one embodiment for a distributed-bank architecture. For this embodiment, the DRAM core chip is divided into four quadrants (910,920,930 and940). Each quadrant includes a portion of a bank.FIG. 10 illustrates one embodiment for a quadrant in a distributed-bank architecture DRAM core chip. As discussed previously, there are 64 sub-arrays per quadrant with each sub-array being a 8192×128 matrix. Instead of assigning all 64 sub-arrays in a single quadrant to a single bank in the concentrated-bank architecture, there are 16 sub-arrays to each of the 4 banks within a single quadrant in the distributed-bank architecture. In the distributed-bank architecture embodiment, local data MUXs are located in each quadrant to select one of the four banks.FIG. 11 is block diagram illustrating one embodiment of a distributed-bank architecture universal DRAM core chip. For this embodiment, the banks of DRAM cells are distributed amongquadrant address decoder 1150, located in the center of the chip, controlsword line drivers quadrants O pads 1162 located in the proximity for each of the quadrants.- Since 64 data bits are accessed from the core chip for every read or write operation, the interface chip may be designed or configured to act similar to a ×16 DDR2 SDRAM, ×8 DDR2 SDRAM, ×4 DDR2 SDRAM, ×2 DDR2 SDRAM, or ×1 DDR2 SDRAM. In fact, the interface chip may be designed to support any data width between ×1 and ×16 when operating in a 4n pre-fetch mode.

- The distributed-bank architecture is flexible enough to support protocols like SDRAM, DDR SDRAM, DDR2 SDRAM, and DDR3 SDRAM. For example, the DRAM core chip shown in

FIG. 11 may be configured or used as shown inFIG. 12 to support DDR2 speeds.FIG. 12 is a block diagram illustrating a distributed-bank architecture DRAM core chip configured to support DDR2 speeds.MUX 1210 selects 64 bits of data for one of the banks (1220,1230,1240 and1250).MUX 1210 represents the data MUXs located in all four quadrants on the DRAM core chip. - The DRAM core chip shown in

FIG. 11 may also be configured or used as shown inFIG. 13 to support DDR SDRAM speeds when it is operated in a 2n pre-fetch mode.FIG. 13 is a block diagram illustrating a distributed-bank architecture DRAM core chip configured to support DDR speeds and external bus widths from 17 to 32 bits.MUX 1310 selects 64 bits of data for one of the banks (1320,1330,1340 and1350). The mode of operation shown inFIG. 13 may be used with the appropriate interface chip to support external data widths between (and inclusive) of 17 and 32 in a 2n pre-fetch mode. The same DRAM core chip may be used with the appropriate interface chip to support external data widths between (and inclusive) 9 and 16 in a 2n pre-fetch mode when operated as shown inFIG. 14 .FIG. 14 is a block diagram illustrating a distributed-bank architecture DRAM core chip configured to support DDR speeds and external bus widths from 9 to 16 bits. For this embodiment,MUX 1410 selects 32 bits of data for one of the banks (1420,1430,1440 and1450). - Also, the same DRAM core chip can be used with the appropriate interface chip to support external data widths between (and inclusive of) 1 and 8 in a 2n pre-fetch mode.

FIG. 15 is a block diagram illustrating a distributed-bank architecture DRAM core chip configured to support DDR speeds and external bus widths from 1 to 8 bits. For this embodiment,MUX 1510 selects 16 bits of data for one of the banks (1520,1530,1540 and1550). - From these architectures, the internal data bus width (the width of the bus between the DRAM core chip and the interface chip) may be configured to match the amount of pre-fetching required (which is determined by the external data rate) and the width of the external data bus. The external data bus is the bus from the interface chip to the ASIC or memory controller. The DRAM core chip as shown in

FIG. 11 may be configured to support the following modes and requirements shown in TABLE 6.TABLE 6 Internal Data Pre- Minimum External Maximum External Bus Width Fetching Used Data Bus Width Data Bus Width 64 8n 1 8 4n 1 16 2n 1 32 1n 1 64 32 8n 1 4 4n 1 8 2n 1 16 1n 1 32 16 8n 1 2 4n 1 4 2n 1 8 1n 1 16 - Note that:

- The proposed DDR3 SDRAM is an example of an 8n pre-fetch protocol;

- DDR2 SDRAM is an example of a 4n pre-fetch protocol;

- DDR SDRAM is an example of a 2n pre-fetch protocol; and

- SDRAM is an example of a in pre-fetch protocol (i.e. no pre-fetching needed).

- Again, for the DRAM core chip shown in

FIG. 11 , 3 modes of operation may be defined and a 2-bit binary code may be assigned to represent them as shown in TABLE 7.TABLE 7 Mode of Operation (Mode[1:0]) Internal Data Bus Width 00 64 01 32 10 16 11 Undefined/Reserved - These two bits (Mode[1:0]) may be inputs to the DRAM core chip so that the internal data bus width is selected through external means. For example, the Mode[1:0] inputs to the core chip may be selected by means of fuses on the core chip or on the interface chip, by means of pull-up or pull-down resistors in the package of either chip (or in the common package) or on the printed circuit board, or may be driven by a register on the interface chip, or may be part of the address input to the core chip.

- Let us assume that the Mode[1:0] inputs to the DRAM core chip are controlled by a register in the interface chip.

FIG. 16 illustrates one embodiment for a portion of a DRAM core chip that includes a decoder for selecting a mode of operation. Thedecoder 1610 in the core chip is aware of the Mode[1:0] inputs as shown inFIG. 16 . - Note that the embodiments disclosed below are based on the DRAM core chip shown in