US20050013163A1 - Semiconductor memory cell, array, architecture and device, and method of operating same - Google Patents

Semiconductor memory cell, array, architecture and device, and method of operating sameDownload PDFInfo

- Publication number

- US20050013163A1 US20050013163A1US10/829,877US82987704AUS2005013163A1US 20050013163 A1US20050013163 A1US 20050013163A1US 82987704 AUS82987704 AUS 82987704AUS 2005013163 A1US2005013163 A1US 2005013163A1

- Authority

- US

- United States

- Prior art keywords

- transistor

- memory cell

- random access

- dynamic random

- access memory

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 239000004065semiconductorSubstances0.000titleclaimsdescription112

- 238000000034methodMethods0.000titleabstractdescription41

- 210000000746body regionAnatomy0.000claimsdescription31

- 230000004044responseEffects0.000claimsdescription9

- 239000011159matrix materialSubstances0.000claimsdescription6

- 230000000295complement effectEffects0.000abstractdescription11

- 238000005070samplingMethods0.000abstractdescription4

- 239000000463materialSubstances0.000description10

- 239000003990capacitorSubstances0.000description9

- 239000000969carrierSubstances0.000description9

- 230000003247decreasing effectEffects0.000description3

- 238000004519manufacturing processMethods0.000description3

- 239000002800charge carrierSubstances0.000description2

- 238000007599dischargingMethods0.000description2

- 230000010354integrationEffects0.000description2

- 238000013459approachMethods0.000description1

- 238000003491arrayMethods0.000description1

- 238000007796conventional methodMethods0.000description1

- 238000002347injectionMethods0.000description1

- 239000007924injectionSubstances0.000description1

- 239000013642negative controlSubstances0.000description1

- 230000007935neutral effectEffects0.000description1

- 230000002093peripheral effectEffects0.000description1

- 239000013641positive controlSubstances0.000description1

- 238000005086pumpingMethods0.000description1

Images

Classifications

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/26—Sensing or reading circuits; Data output circuits

- G11C16/28—Sensing or reading circuits; Data output circuits using differential sensing or reference cells, e.g. dummy cells

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/403—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells with charge regeneration common to a multiplicity of memory cells, i.e. external refresh

- G11C11/404—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells with charge regeneration common to a multiplicity of memory cells, i.e. external refresh with one charge-transfer gate, e.g. MOS transistor, per cell

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/20—DRAM devices comprising floating-body transistors, e.g. floating-body cells

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/711—Insulated-gate field-effect transistors [IGFET] having floating bodies

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2211/00—Indexing scheme relating to digital stores characterized by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C2211/401—Indexing scheme relating to cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C2211/4013—Memory devices with multiple cells per bit, e.g. twin-cells

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2211/00—Indexing scheme relating to digital stores characterized by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C2211/401—Indexing scheme relating to cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C2211/4016—Memory devices with silicon-on-insulator cells

Definitions

- This inventionrelates to a semiconductor memory cell, array, architecture and device, and techniques for controlling and/or operating such cell and device; and more particularly, in one aspect, to a semiconductor dynamic random access memory (“DRAM”) cell, array, architecture and/or device wherein the memory cell includes an electrically floating body in which an electrical charge is stored.

- DRAMsemiconductor dynamic random access memory

- DRAM cellsThere are many different types and/or forms of DRAM cells, including, for example, a semiconductor memory cell consisting of an access transistor and a capacitor, which stores an electric charge representing a bi-stable memory state.

- the access transistorserves as a switch for controlling the charging and discharging of the capacitor as well as reading and writing of the logic states into the capacitor (i.e., charging or discharging the capacitor).

- DRAM devices employing one transistor—one capacitor memory cellstend to be fabricated using manufacturing processes that are different from and/or incompatible with manufacturing processes for logic devices (for example, microprocessors).

- logic devicesfor example, microprocessors

- integration of one transistor—one capacitor memory cells into logic devicesis often complicated and expensive.

- each memory cell 12consists of transistor 14 having gate 16 , body region 18 , which is electrically floating, source region 20 and drain region 22 .

- the body region 18is disposed between and adjacent to source region 20 and drain region 22 .

- Datais written into or read from a selected memory cell by applying suitable control signals to a selected word line(s) 24 , a selected source line(s) 26 and/or a selected bit line(s) 28 .

- charge carriersare accumulated in or emitted and/or ejected from electrically floating body region 18 wherein the data states are defined by the amount of carriers within electrically floating body region 18 .

- the entire contents of the Semiconductor Memory Device Patent Applicationincluding, for example, the features, attributes, architectures, configurations, materials, techniques and advantages described and illustrated therein, are incorporated by reference herein.

- the memory cell of the Semiconductor Memory Device Patent Applicationoperates by accumulating in or emitting/ejecting majority carriers (electrons or holes) 30 from body region 18 of, for example, N-channel transistors.

- accumulating majority carriers (in this example, “holes”) 30 in body region 18 of memory cells 12 via, for example, impact ionization near source region 20 and/or drain region 22is representative of a logic high or “1” data state.

- Emitting or ejecting majority carriers 30 from body region 18 via, for example, forward biasing the source/body junction and/or the drain/body junctionis representative of a logic low or “0”. (See, FIG. 2B ).

- a current sense amplifier(not illustrated) may be employed to read the data stored in memory cells 12 .

- a current sense amplifiermay compare the cell current to a reference current, for example, the current of a reference cell (not illustrated). From that comparison, it may be determined whether memory cell 12 contained a logic high (relatively more majority carries 30 contained within body region 18 ) or logic low data state (relatively less majority carries 28 contained within body region 18 ).

- transistor 14may be a symmetrical or non-symmetrical device. Where transistor 14 is symmetrical, the source and drain regions are essentially interchangeable. However, where transistor 14 is a non-symmetrical device, the source or drain regions of transistor 14 have different electrical, physical, doping concentration and/or doping profile characteristics. As such, the source or drain regions of a non-symmetrical device are typically not interchangeable.

- the present inventionis a semiconductor dynamic random access memory cell for storing a first data state and a second data state.

- the memory cellincludes first and second transistors, wherein each transistor includes a source region, a drain region, an electrically floating body region disposed between and adjacent to the source region and the drain region, and a gate spaced apart from, and capacitively coupled to, the body region.

- each transistorincludes a first state representative of a first charge in the body region, and a second data state representative of a second charge in the body region.

- the memory cellis in: (1) the first data state when the first transistor is in the first state and the second transistor is in the second state and (2) the second data state when the first transistor is in the second state and the second transistor is in the first state.

- the semiconductor dynamic random access memory cellincludes two outputs including a first output connected to the drain region of the first transistor and a second output connected to the drain region of the second transistor.

- the gate of the first transistoris connected to the gate of the second transistor, and the source region of the first transistor and the source region of the second transistor are the same region.

- the semiconductor dynamic random access memory cellincludes two outputs including a first output connected to the source region of the first transistor and a second output connected to the source region of the second transistor.

- the drain region of the first transistor and the drain region of the second transistorare the same region.

- the memory cellmay be programmed to a first data state by applying a first control signal to the gate of the first transistor and a second control signal to the gate of the second transistor and wherein the first and second control signals include different voltage amplitudes.

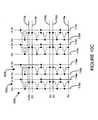

- the present inventionis a semiconductor memory array comprising a plurality of semiconductor dynamic random access memory cells arranged in a matrix of rows and columns.

- Each semiconductor dynamic random access memory cellincludes first and second transistors.

- Each transistorincludes a source region, a drain region, a electrically floating body region disposed between and adjacent to the source region and the drain region, and a gate spaced apart from, and capacitively coupled to, the body region.

- the transistorsinclude a first state representative of a first charge in the body region; and a second data state representative of a second charge in the body region. Further each memory cell is in: (1) the first data state when its first transistor is in the first state and its second transistor is in the second state and (2) the second data state when its first transistor is in the second state and its second transistor is in the first state.

- the semiconductor memory arraymay also include a comparator having a plurality of inputs to sense the states of the first and second transistors of a semiconductor dynamic random access memory cell of the plurality of semiconductor dynamic random access memory cell.

- a first input of the comparatoris selectively coupled to a first transistor of the semiconductor dynamic random access memory cell and the second input of the comparator is selectively coupled to the second transistor of a semiconductor dynamic random access memory cell.

- At least one of the rows of semiconductor dynamic random access memory cellsincludes a source line that is connected to each of the semiconductor dynamic random access memory cells of the row.

- each row of semiconductor dynamic random access memory cellsincludes an associated source line which is connected to only the semiconductor dynamic random access memory cells of the associated row.

- a first input of a comparatoris selectively coupled to the drain region of the first transistor of the semiconductor dynamic random access memory cell and a second input of the comparator is selectively coupled to the drain of second first transistor of a semiconductor dynamic random access memory cell.

- each row of semiconductor dynamic random access memory cellsincludes an associated source line which is connected to only the semiconductor dynamic random access memory cells of the row.

- the semiconductor dynamic random access memory cellmay be programmed in a first data state by performing a clear operation of the first and second transistors of the semiconductor dynamic random access memory cell and then performing a write operation. In response, the first transistor of the semiconductor dynamic random access memory cell is in a first state and the second transistor of the semiconductor dynamic random access memory cell is in a second state.

- the semiconductor dynamic random access memory cellmay be programmed in a first data state by first placing the first and second transistors of the semiconductor dynamic random access memory cell in a first state and thereafter placing the second transistor of the semiconductor dynamic random access memory cell is in a second state.

- an unselected portion of the semiconductor memory arrayis maintained in a fixed state when programming the at least one semiconductor dynamic random access memory cell by applying a write inhibit signal to the transistors of the semiconductor dynamic random access memory cells comprising the unselected portion of the semiconductor memory array.

- each semiconductor dynamic random access memory cellincludes two outputs including a first output connected to the drain region of the first transistor and a second output connected to the drain region of the second transistor.

- the gate of the first transistor and the gate of the second transistor of each semiconductor dynamic random access memory cellare each connected to an associated common gate line.

- the source region of the first transistor and the source region of the second transistor of each semiconductor dynamic random access memory cellare the same region.

- the source region of the first transistor and the source region of the second transistor of each semiconductor dynamic random access memory cellare connected to different source lines.

- a first output of each semiconductor dynamic random access memory cellmay be connected to the source region of the first transistor and a second output of the semiconductor dynamic random access memory cell may be connected to the source region of the second transistor.

- the drain region of the first transistor and the drain region of the second transistor of each semiconductor dynamic random access memory cellare the same region.

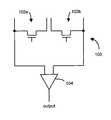

- FIG. 1Ais a schematic representation of a semiconductor DRAM array as illustrated (and described) in the Semiconductor Memory Device Patent Application;

- FIG. 1Billustrates a memory cell according to the Semiconductor Memory Device Patent Application

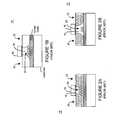

- FIGS. 2A and 2Bare exemplary schematic illustrations of the charge relationship, for a particular memory state, of the floating body, source and drain regions of a memory cell according to the Semiconductor Memory Device Patent Application;

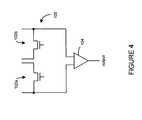

- FIGS. 3A and 3Billustrate a memory cell, according to certain embodiments of certain aspects of the present inventions

- FIG. 4illustrates a memory cell, in conjunction with a read amplifier, according to one embodiment of the present invention

- FIG. 5illustrates a memory cell including two transistors that are configured to have a common drain region, according to one embodiment of the present invention

- FIG. 6illustrates an exemplary layout of the memory cell of FIG. 5 ;

- FIGS. 7A, 7B , 8 A and 8 Billustrate writing and/or programming techniques including exemplary programming voltage values, according to two embodiments of the present invention, for the memory cell including two transistors that are configured to have a common drain region;

- FIG. 9illustrates a memory cell of this embodiment, in conjunction with a read amplifier and read operation including exemplary voltage values, according to an embodiment of the present invention, for the memory cell including two transistors that are configured to have a common drain region;

- FIGS. 10A and 10Billustrate writing and/or programming techniques including exemplary programming voltage values, according to two embodiments of the present invention, for a memory array including a plurality of memory cells each having two transistors that are configured to have a common drain region;

- FIG. 10Cillustrates exemplary read operation voltage values, according to an embodiment of the present invention, for a memory array including a plurality of memory cells each having two transistors that are configured to have a common drain region;

- FIG. 11illustrates a memory cell including two transistors that are configured to have a common source region and connected gates, according to one embodiment of the present invention

- FIG. 12illustrates an exemplary layout of the memory cell of FIG. 11 ;

- FIGS. 13A and 13Billustrate writing and/or programming techniques including exemplary programming voltage values, for the memory cell of FIG. 11 ;

- FIG. 14illustrates a memory cell of FIG. 11 , in conjunction with a read amplifier and read operation including exemplary voltage values, according to an embodiment of the present invention

- FIGS. 15A and 15Billustrate writing and/or programming techniques including exemplary programming voltage values, for a memory array including a plurality of memory cells of FIG. 11 ;

- FIG. 15Cillustrates exemplary read operation voltage values, according to an embodiment of the present invention, for a memory array including a plurality of memory cells of FIG. 11 ;

- FIGS. 16A-16Cillustrate writing and/or programming techniques (including exemplary programming voltage values), according to another aspect of the present invention, for a memory cell of FIG. 11 ;

- FIGS. 17 and 18illustrate a memory array including a plurality of memory cells having a separate source line array that define a particular row of memory cells, and exemplary writing and/or programming techniques (including exemplary programming voltage values), according to another aspect of the present invention

- FIGS. 19A and 19Billustrate exemplary and alternative read operation voltage values, according to an embodiment of the present invention, for a memory array of FIGS. 17 and 18 ;

- FIG. 20illustrates an exemplary layout of the memory array of FIGS. 17 and 18 ;

- FIGS. 21 and 22illustrate a memory array including a plurality of memory cells having a common source line array that define a particular row of memory cells, and exemplary writing and/or programming techniques (including exemplary programming voltage values), according to another aspect of the present invention

- FIG. 23illustrates exemplary read operation voltage values, according to an embodiment of the present invention, for a memory array of FIGS. 21 and 22 ;

- FIG. 24illustrates an exemplary layout of the memory array of FIGS. 21 and 22 ;

- FIGS. 25 and 26illustrate another memory array architecture including a plurality of memory cells having a common source line array, and exemplary writing and/or programming techniques (including exemplary programming voltage values), according to another aspect of the present invention

- FIG. 27illustrates exemplary read operation voltage values, according to an embodiment of the present invention, for a memory array of FIGS. 25 and 26 ;

- FIG. 28illustrates an exemplary layout of the memory array of FIGS. 25 and 26 ;

- FIGS. 29 and 30illustrate a refresh architecture and technique for the memory cell and memory cell array according to one embodiment of the present invention.

- the present inventionis directed to a memory cell and technique of reading data from and writing data into that memory cell.

- the memory cellincludes two transistors which store complementary data states. That is, the two-transistor memory cell includes a first transistor that maintains a complementary state relative to the second transistor. As such, when programmed, one of the transistors of the memory cell stores a logic low (a binary “0”) and the other transistor of the memory cell stores a logic high (a binary “1”).

- the data state of the two-transistor complementary memory cellmay be read and/or determined by sampling, sensing measuring and/or detecting the polarity of the logic states stored in each transistor of complementary memory cell. That is, the two-transistor complementary memory cell is read by sampling, sensing, measuring and/or detecting the difference in signals (current or voltage) stored in the two transistors.

- memory cell 100is a bi-stable memory cell which includes transistor 102 a and transistor 102 b .

- transistor 102 astores a logic low and transistor 102 b stores a logic high.

- transistor 102 bstores a logic low.

- transistor 102 astores a logic high

- transistor 102 bstores a logic low.

- the state of memory cell 100may be read and/or determined by comparator 104 , which may be a voltage or current type comparator (for example, a cross-coupled sense amplifier).

- comparator 104may compare the different logic states stored in transistor 102 a and transistor 102 b .

- pass gates and/or column switch circuitrymay be employed to selectively connect transistors 102 a and 102 b to comparator 104 to facilitate the read operation of the data state of memory cell 100 .

- memory cell 100 of the present inventionmay include several advantages relative to conventional dynamic random access memory cells, including, for example: (i) the read operation is less sensitive to variation in the values of the binary states because a logic state is determined by the difference in states of the individual transistors, (ii) no reference circuit is necessary, (iii) the memory cell 100 includes a larger read window (as compared to conventional dynamic random access memory cells), which results in faster access time, and (iv) a less complicated and/or complex sense amplifier may be employed.

- the transistor 102 a and/or transistor 102 bmay be symmetrical or non-symmetrical devices. Where transistors 102 a and/or transistor 102 b are symmetrical, the source and drain regions are essentially interchangeable. However, where transistors 102 a and/or transistor 102 b are non-symmetrical devices, the source or drain regions of transistor 102 a and/or transistor 102 b may have different electrical, physical, doping concentration and/or doping profile characteristics. As such, the source or drain regions of the non-symmetrical device are typically not interchangeable.

- memory cell 100includes transistors 102 a and 102 b that have the same or similar characteristics.

- transistors 102 a and/or 102 bmay have the same or similar characteristics as the transistors described and illustrated in the Semiconductor Memory Device Patent Application.

- transistors 102 a and 102 bmay employ any type of design and/or control technique, whether now known or later developed, including, for example, those discussed above in the Semiconductor Memory Device Patent Application. All such designs of and/or control techniques for transistors 102 a and 102 b , whether now known or later developed, are intended to be within the present invention.

- transistors 102 a and 102 bare designed to have the same or similar characteristics, it may be advantageous to physically locate transistors 102 a and 102 b nearby each other. In this way, during manufacturing, transistors 102 a and 102 b are likely to be fabricated with little to no process variations or differences and, as such, transistors 102 a and 102 b are likely to have the same or similar electrical, physical, doping concentration and/or profile characteristics.

- a memory devicemay include a plurality of memory cells 100 arranged in repeating patterns.

- the memory cell 100may be arranged in an array in many different ways. All layout configurations for transistors 102 a and 102 b , whether now known or later developed, are intended to be within the present invention.

- transistors 102 a and 102 bare configured to have a common drain region.

- transistors 102 a and 102 binclude a common drain regions 110 a and 110 b .

- Datais written into or read from transistors 102 a and 102 b by applying suitable control signals to source regions 108 a and 108 b , drain regions 110 a and 110 b and/or gates 112 a and 112 b , respectively.

- charge carriersare accumulated in or emitted from electrically floating body regions 106 a and 106 b wherein the data state of each transistors 102 a and 102 b is defined by the amount of carriers within electrically floating body regions 106 a and 106 b , respectively.

- a logic low(binary “0” state) is written into transistor 102 a and a logic high (binary “1” state) is written into transistor 102 b using the indicated (exemplary) voltage levels.

- the voltage levels indicated in FIGS. 7A and 7Bmay be relative or absolute.

- a logic lowmay be written into transistor 102 a ( FIG. 7A ) or transistor 102 b ( FIG. 7B ) using the voltages indicated.

- the voltages indicatedmay be relative in that each voltage level, for example, may be increased or decreased by a given voltage (for example, 0.5 volts).

- the logic levelsmay be programmed into transistors 102 a and 102 b using a low power consumption technique.

- the low power consumption techniqueemploys positive and negative control signals/voltages in order to program the complementary states. For example, a logic high is written into transistor 102 a ( FIG. 8B ) and a logic high is written into transistor 102 b ( FIG. 8A ) using a negative gate voltage.

- the source regions 108 a and 108 b of transistors 102 a and 102 bare employed to read, sense and/or determine the data state of cell 100 .

- source regions 108 a and 108 bare selectively connected to comparator 104 (for example, a voltage or current sense amplifier) to permit the logic value of memory cell 110 to be read, sensed and/or determined.

- comparator 104for example, a voltage or current sense amplifier

- transistors 102 a and 102 bmay store the respective data state via majority carriers within the electrically floating body regions 106 a and 106 b , respectively.

- the logic state of each transistor 102 a and 102 bis read by comparator 104 in a differential manner. Exemplary read voltage signals are indicated in FIG. 9 .

- a memory devicemay include a plurality of memory cells 100 , arranged in repeating patterns.

- the exemplary write techniquesdescribed above, are illustrated in a schematic representation of a memory matrix.

- the exemplary read techniquedescribed above, is illustrated in a schematic representation of a memory matrix.

- 10A-10Cmay reduce, minimize and/or eliminate any disturbance issues (for example, issues of stored charge loss or gain within memory cells) caused to memory cells having common gate lines, drain lines and/or source lines with memory cells that are accessed via read and write operations.

- disturbance issuesfor example, issues of stored charge loss or gain within memory cells

- memory cell 100may include a layout whereby transistors 102 a and 102 b include (1) common source regions 108 a and 108 b , respectively, and (2) gates 112 a and 112 b , respectively, that are connected to the same gate line 118 .

- Exemplary write techniquesare indicated in FIG. 13A (write logic low) and FIG. 13B (write logic high).

- An exemplary read techniqueis illustrated in FIG. 14 .

- the voltage levels indicated in FIGS. 13A, 13B and 14may be relative or absolute.

- a logic lowmay be written into transistor 102 a ( FIG. 13A ) or transistor 102 b ( FIG. 13B ) using the voltages indicated.

- the voltages indicatedmay be relative in that each voltage level, for example, may be increased or decreased by a given voltage (for example, 0.25 volts).

- a memory array having a plurality of memory cells 100 wherein the source regions and gates (gate lines) of transistors 102 a and 102 b are in commonmay include a layout as illustrated in FIGS. 15A-15C .

- exemplary write techniques of the memory array of this embodimentare illustrated in a schematic representation of a memory matrix.

- an exemplary read techniqueis illustrated in a schematic representation of a memory matrix including a plurality of memory cells 100 configured with common source regions and gates (gate line).

- the exemplary read and write techniques of FIGS. 15A-15Cincluding the exemplary levels of the read and write voltages, may reduce, minimize and/or eliminate any disturbance issues (to neighboring cells) that may result using other read and write voltage levels.

- a two-step write operationmay be employed to program memory cell 100 a with little to no disturbance to adjacent and/or neighboring cells (i.e., cells that share source lines, drain lines and/or gate lines).

- an entire row of memory cellsmay first be written to the same logic state and thereafter, individual bits are written to the opposite state in accordance with a desired data state (i.e., the individual bits are written to another state to reflect a desired data state).

- the memory cells having a common source lineare first written to the same logic state (for example, logic high or binary “1”). In this way, the state of memory cell 100 is “cleared”. Thereafter, individual transistors 102 of memory cells 100 are written to a particular, desired and/or predetermined logic state (see, for example, FIG. 16B (write “0”) and FIG. 16C (write “1”)) according to the particular, desired and/or predetermined logic state of memory cell 100 . That is, one of the transistors of memory cell 100 is written to logic low (binary “0”) to write either a logic high or logic low into memory cell 100 (i.e., transistor 102 a of FIG. 16B to store logic low in memory cell 100 ; and transistor 102 b of FIG. 16C to store logic high in memory cell 100 ). Notably, writing logic low to the other transistor of memory cell 100 is inhibited by applying a suitable bitline voltage.

- the first step of the write operationclears the memory cells having a common source line and the second step writes or stores new data or the previous data (in the event that the data did not change).

- Array architectures employing this write operation techniquemay have an advantage that the memory cells of the array are not “disturbed” (or experience little and/or negligible disturbance) because “high” voltages are applied in the row direction (i.e., on source lines 114 ) but not in the column direction (i.e., on the drain lines 116 ).

- this write techniquemay be performed as a page mode write where the page is first “cleared” and then individual bytes (or bits) in a page are written to a new state.

- Such a write techniquemay also be suitable for other memory array architectures or configurations.

- the write techniquemay be implemented where memory cells 100 of each row of transistors 102 has a dedicated source line to minimize, reduce and/or eliminate disturbance on adjacent rows.

- a given rowmay be written to by applying a clear operation followed by a selective write operation.

- a plurality of memory cells 100having gates that are connected to a common gate line, are arranged to form row 120 .

- Exemplary voltages that implement a clear operation for row 120 and maintain the remaining portion of the array in a fixed state (i.e., unchanged in response to the clear operation)are indicated in FIG. 17 .

- the same logic statefor example, logic high or binary “1” is stored in both transistors 102 a and 102 b of memory cells 100 of row 120 . In this way, the state of memory cell 100 is “cleared”.

- individual transistors 102 a and 102 b of the memory cells 100 of row 120are written to a particular, desired and/or predetermined logic state (see, for example, FIG. 18 (write “1”) in memory cell 100 a ) in order to store a particular, desired and/or predetermined logic state in memory cell 100 . That is, as described above, one of the transistors of memory cell 100 is written to logic low (binary “0”) to write either a logic high or logic low into memory cell 100 . Notably, writing logic low to the other transistor of the memory cell 100 is inhibited by applying a suitable bitline voltage.

- the datamay be read from memory cells 100 of row 120 by applying the exemplary voltages indicated.

- the exemplary read voltages of FIG. 19Bmay avoid, reduce and/or minimize the need for charge pumping to eliminate minority carriers from the floating body—gate interface.

- FIGS. 21-24Another memory array architectures that may employ the two-step write technique that eliminates, minimizes and/or reduces disturbance to memory cells when reading from and/or writing to adjacent memory cells is illustrated in FIGS. 21-24 .

- the source linesare shared but bit lines are separated.

- the transistors 102 a and 102 b of memory cell 100 aare located on separate rows.

- the gates of transistors 102 a and 102 bare connected together at the array boundary.

- transistors 102 a and 102 b of memory cell 100 aare located on separate rows with the gates of each transistor 102 a and 102 b connected at, for example, the array boundary.

- FIGS. 25-28illustrate another memory array architecture in which a plurality of memory cells “share” a source line and employ the two-step write technique that may eliminate, minimize and/or reduce disturbance to memory cells when reading from and/or writing to adjacent memory cells.

- a given rowmay be written to by applying suitable voltages to implement a clear operation followed by a selective write operation.

- a write inhibit signalis applied to the gates of memory cells that share a source line 114 (for example, a write inhibit signal may be applied to the gates of transistors that comprise memory cell 100 x and memory cell 100 y ).

- exemplary voltages that implement a clear operation for row 120 and maintain the neighboring memory cells (for example, memory cells 100 x and 100 y ) remaining portion of the array in a fixed state (i.e., unchanged in response to the clear operation)are indicated in FIG. 25 .

- the individual transistors 102 of the memory cells 100 of row 120are written to a particular, desired and/or predetermined logic state (see, for example, FIG. 26 (write “1”) in memory cell 100 a ) in order to store a particular, desired and/or predetermined logic state of the memory cell 100 . That is, as described above, one of the transistors of memory cell 100 is written to logic low (binary “0”) to write either a logic high or logic low into the memory cell 100 .

- the datamay be read from memory cells 100 of row 120 by applying the exemplary voltages indicated.

- an exemplary read inhibit voltage for the remaining portion of the array (including the neighboring memory cells)is also indicated.

- the read inhibit voltage/signalmaintains the unselected portion of the array in a fixed state (i.e., unchanged in response to the read operation).

- the memory cell 100is a dynamic storage device. As such, memory cell 100 must be periodically or intermittently refreshed to maintain its data state.

- FIGS. 29 and 30illustrate an exemplary (and inventive) refresh configuration and technique for refreshing and/or re-storing the data state of memory cell 100 .

- gates 112 a and 112 b and source regions 108 a and 108 b of transistors 102 a and 102 b (respectively) of memory cell 100are connected and thereafter a current (I) is applied on the electrically shorted gates and sources.

- the drain regions 110 a and 110 b of transistors 102 a and 102 bare maintained at a predetermined voltage (for example, 0V).

- the forced current (I)will pass mainly through the transistor having the lower threshold (i.e., the transistor storing a logic high (binary “1”)).

- the transistor currentswill differ by orders of magnitude.

- the higher current through the low threshold transistorwill inject holes into the body of that transistor and, as such, will reinforce the logic high (binary “1”).

- the high threshold transistormay have some hole injection but not enough to overcome the natural tendency to return to the neutral state.

- the current (I)may also be applied to the electrically shorted gates and drains with the sources maintained at a predetermined voltage (for example, 0V).

- FIG. 30illustrates the refresh technique in the context of a memory array wherein row 120 of memory cells 100 are refreshed.

- the forced currentflows almost exclusively through all the transistors storing a logic high (binary “1”).

- this refresh techniqueis well suited to the memory cells and memory array architecture of the present inventions because the optimum range of forced current is independent of the data stored in the refreshed row (that is, half the transistors contain a logic high and the other half contain a logic low).

- FIG. 30illustrates a “separated source” array architecture

- the techniqueis also applicable to the other array architectures described herein.

- the discussion regarding refreshwill not be repeated for such other array architectures.

- the illustrated voltage levels to implement the write and read operationsare exemplary.

- the indicated voltage levelsmay be relative or absolute. That is, for example, a logic low may be written into transistor 102 a (see, for example, FIG. 7A ) or transistor 102 b (see, for example, FIG. 7B ) using the voltages indicated therein.

- the voltages indicatedmay be relative in that each voltage level, for example, may be increased or decreased by a given voltage amount (for example, each voltage may be increased by 0.5 volts).

- the inventions(and embodiments thereof described herein are entirely applicable to P-channel transistors.

- majority carriers in body region 18are electrons and minority carriers are holes.

- the memory arraysmay be comprised of N-channel, P-channel and/or both types of transistors.

- the circuitry that is peripheral to the memory arraymay include P-channel and/or N-channel type transistors, including transistors like transistor 14 .

- memory cell(s) 102may also employ the structure, features, attributes, architectures, configurations, materials, techniques and advantages described and illustrated in non-provisional patent application entitled “Semiconductor Device”, which was filed on Feb. 18, 2004, by Fazan and Okhonin, and assigned Ser. No. 10/487,157 (hereinafter “Semiconductor Device Patent Application”).

- semiconductor Device Patent ApplicationThe entire contents of the Semiconductor Device Patent Application, including, for example, the inventions, features, attributes, architectures, configurations, materials, techniques and advantages described and illustrated therein, are hereby incorporated by reference herein.

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Semiconductor Memories (AREA)

- Dram (AREA)

- For Increasing The Reliability Of Semiconductor Memories (AREA)

Abstract

Description

- This application claims priority to: U.S. Provisional Application Ser. No. 60/470,385, entitled “Two Transistor Gain Cell”, filed May 13, 2003 (hereinafter “the Provisional Application”). The contents of the Provisional Application are incorporated by reference herein in their entirety.

- This invention relates to a semiconductor memory cell, array, architecture and device, and techniques for controlling and/or operating such cell and device; and more particularly, in one aspect, to a semiconductor dynamic random access memory (“DRAM”) cell, array, architecture and/or device wherein the memory cell includes an electrically floating body in which an electrical charge is stored.

- There are many different types and/or forms of DRAM cells, including, for example, a semiconductor memory cell consisting of an access transistor and a capacitor, which stores an electric charge representing a bi-stable memory state. The access transistor serves as a switch for controlling the charging and discharging of the capacitor as well as reading and writing of the logic states into the capacitor (i.e., charging or discharging the capacitor).

- Although significant integration densities can be achieved with DRAM devices employing one transistor—one capacitor memory cells, such devices tend to be limited or restricted with respect to the size of the memory cell. In this regard, conventional techniques employ stacked and/or trench capacitor approaches, whereby the capacitor is partially disposed above and/or below an access transistor.

- In addition, DRAM devices employing one transistor—one capacitor memory cells tend to be fabricated using manufacturing processes that are different from and/or incompatible with manufacturing processes for logic devices (for example, microprocessors). As a result, integration of one transistor—one capacitor memory cells into logic devices is often complicated and expensive.

- Another type of dynamic random access memory cell is described and illustrated in non-provisional patent application entitled “Semiconductor Memory Device”, which was filed on Jun. 10, 2003 and assigned Ser. No. 10/450,238 (hereinafter “Semiconductor Memory Device Patent Application”). With reference to

FIGS. 1A and 1B , the Semiconductor Memory Device Patent Application discloses, among other things,semiconductor DRAM device 10 in which eachmemory cell 12 consists oftransistor 14 havinggate 16,body region 18, which is electrically floating,source region 20 anddrain region 22. Thebody region 18 is disposed between and adjacent tosource region 20 and drainregion 22. Data is written into or read from a selected memory cell by applying suitable control signals to a selected word line(s)24, a selected source line(s)26 and/or a selected bit line(s)28. In response, charge carriers are accumulated in or emitted and/or ejected from electrically floatingbody region 18 wherein the data states are defined by the amount of carriers within electrically floatingbody region 18. Notably, the entire contents of the Semiconductor Memory Device Patent Application, including, for example, the features, attributes, architectures, configurations, materials, techniques and advantages described and illustrated therein, are incorporated by reference herein. - In particular, in one embodiment, the memory cell of the Semiconductor Memory Device Patent Application operates by accumulating in or emitting/ejecting majority carriers (electrons or holes)30 from

body region 18 of, for example, N-channel transistors. (See,FIGS. 2A and 2B ). In this regard, accumulating majority carriers (in this example, “holes”)30 inbody region 18 ofmemory cells 12 via, for example, impact ionization nearsource region 20 and/ordrain region 22, is representative of a logic high or “1” data state. (See,FIG. 2A ). Emitting or ejectingmajority carriers 30 frombody region 18 via, for example, forward biasing the source/body junction and/or the drain/body junction, is representative of a logic low or “0”. (See,FIG. 2B ). - Several techniques may be implemented to read the data stored in (or write the data into) a memory device of the Semiconductor Memory Device Patent Application. For example, a current sense amplifier (not illustrated) may be employed to read the data stored in

memory cells 12. In this regard, a current sense amplifier may compare the cell current to a reference current, for example, the current of a reference cell (not illustrated). From that comparison, it may be determined whethermemory cell 12 contained a logic high (relatively more majority carries30 contained within body region18) or logic low data state (relatively less majority carries28 contained within body region18). - Notably,

transistor 14 may be a symmetrical or non-symmetrical device. Wheretransistor 14 is symmetrical, the source and drain regions are essentially interchangeable. However, wheretransistor 14 is a non-symmetrical device, the source or drain regions oftransistor 14 have different electrical, physical, doping concentration and/or doping profile characteristics. As such, the source or drain regions of a non-symmetrical device are typically not interchangeable. - There are many inventions described and illustrated herein. In a first principal aspect, the present invention is a semiconductor dynamic random access memory cell for storing a first data state and a second data state. The memory cell includes first and second transistors, wherein each transistor includes a source region, a drain region, an electrically floating body region disposed between and adjacent to the source region and the drain region, and a gate spaced apart from, and capacitively coupled to, the body region. In addition, each transistor includes a first state representative of a first charge in the body region, and a second data state representative of a second charge in the body region. Further the memory cell is in: (1) the first data state when the first transistor is in the first state and the second transistor is in the second state and (2) the second data state when the first transistor is in the second state and the second transistor is in the first state.

- In one embodiment, the semiconductor dynamic random access memory cell includes two outputs including a first output connected to the drain region of the first transistor and a second output connected to the drain region of the second transistor. In this embodiment, the gate of the first transistor is connected to the gate of the second transistor, and the source region of the first transistor and the source region of the second transistor are the same region.

- In another embodiment, the semiconductor dynamic random access memory cell includes two outputs including a first output connected to the source region of the first transistor and a second output connected to the source region of the second transistor. In this embodiment, the drain region of the first transistor and the drain region of the second transistor are the same region.

- Notably, the memory cell may be programmed to a first data state by applying a first control signal to the gate of the first transistor and a second control signal to the gate of the second transistor and wherein the first and second control signals include different voltage amplitudes.

- In another principal aspect, the present invention is a semiconductor memory array comprising a plurality of semiconductor dynamic random access memory cells arranged in a matrix of rows and columns. Each semiconductor dynamic random access memory cell includes first and second transistors. Each transistor includes a source region, a drain region, a electrically floating body region disposed between and adjacent to the source region and the drain region, and a gate spaced apart from, and capacitively coupled to, the body region. The transistors include a first state representative of a first charge in the body region; and a second data state representative of a second charge in the body region. Further each memory cell is in: (1) the first data state when its first transistor is in the first state and its second transistor is in the second state and (2) the second data state when its first transistor is in the second state and its second transistor is in the first state.

- The semiconductor memory array may also include a comparator having a plurality of inputs to sense the states of the first and second transistors of a semiconductor dynamic random access memory cell of the plurality of semiconductor dynamic random access memory cell. A first input of the comparator is selectively coupled to a first transistor of the semiconductor dynamic random access memory cell and the second input of the comparator is selectively coupled to the second transistor of a semiconductor dynamic random access memory cell.

- In one embodiment, at least one of the rows of semiconductor dynamic random access memory cells includes a source line that is connected to each of the semiconductor dynamic random access memory cells of the row. Indeed, in another embodiment, each row of semiconductor dynamic random access memory cells includes an associated source line which is connected to only the semiconductor dynamic random access memory cells of the associated row.

- In another embodiment, a first input of a comparator is selectively coupled to the drain region of the first transistor of the semiconductor dynamic random access memory cell and a second input of the comparator is selectively coupled to the drain of second first transistor of a semiconductor dynamic random access memory cell. In this embodiment, each row of semiconductor dynamic random access memory cells includes an associated source line which is connected to only the semiconductor dynamic random access memory cells of the row.

- The semiconductor dynamic random access memory cell may be programmed in a first data state by performing a clear operation of the first and second transistors of the semiconductor dynamic random access memory cell and then performing a write operation. In response, the first transistor of the semiconductor dynamic random access memory cell is in a first state and the second transistor of the semiconductor dynamic random access memory cell is in a second state.

- Moreover, the semiconductor dynamic random access memory cell may be programmed in a first data state by first placing the first and second transistors of the semiconductor dynamic random access memory cell in a first state and thereafter placing the second transistor of the semiconductor dynamic random access memory cell is in a second state. In this embodiment, an unselected portion of the semiconductor memory array is maintained in a fixed state when programming the at least one semiconductor dynamic random access memory cell by applying a write inhibit signal to the transistors of the semiconductor dynamic random access memory cells comprising the unselected portion of the semiconductor memory array.

- In one embodiment, each semiconductor dynamic random access memory cell includes two outputs including a first output connected to the drain region of the first transistor and a second output connected to the drain region of the second transistor.

- In another embodiment, the gate of the first transistor and the gate of the second transistor of each semiconductor dynamic random access memory cell are each connected to an associated common gate line.

- In yet another embodiment, the source region of the first transistor and the source region of the second transistor of each semiconductor dynamic random access memory cell are the same region. However, in another embodiment, the source region of the first transistor and the source region of the second transistor of each semiconductor dynamic random access memory cell are connected to different source lines.

- Indeed, a first output of each semiconductor dynamic random access memory cell may be connected to the source region of the first transistor and a second output of the semiconductor dynamic random access memory cell may be connected to the source region of the second transistor. In this embodiment, the drain region of the first transistor and the drain region of the second transistor of each semiconductor dynamic random access memory cell are the same region.

- Again, there are many inventions described and illustrated herein. This Summary of the Invention is not exhaustive of the scope of the present invention. Moreover, this Summary is not intended to be limiting of the invention and should not be interpreted in that manner. While certain embodiments, features, attributes and advantages of the inventions have been described in this Summary, it should be understood that many others, as well as different and/or similar embodiments, features, attributes and/or advantages of the present inventions, which are apparent from the description, illustrations and claims, which follow.

- In the course of the detailed description to follow, reference will be made to the attached drawings. These drawings show different aspects of the present invention and, where appropriate, reference numerals illustrating like structures, components, materials and/or elements in different figures are labeled similarly. It is understood that various combinations of the structures, components, materials and/or elements, other than those specifically shown, are contemplated and are within the scope of the present invention.

FIG. 1A is a schematic representation of a semiconductor DRAM array as illustrated (and described) in the Semiconductor Memory Device Patent Application;FIG. 1B illustrates a memory cell according to the Semiconductor Memory Device Patent Application;FIGS. 2A and 2B are exemplary schematic illustrations of the charge relationship, for a particular memory state, of the floating body, source and drain regions of a memory cell according to the Semiconductor Memory Device Patent Application;FIGS. 3A and 3B illustrate a memory cell, according to certain embodiments of certain aspects of the present inventions;FIG. 4 illustrates a memory cell, in conjunction with a read amplifier, according to one embodiment of the present invention;FIG. 5 illustrates a memory cell including two transistors that are configured to have a common drain region, according to one embodiment of the present invention;FIG. 6 illustrates an exemplary layout of the memory cell ofFIG. 5 ;FIGS. 7A, 7B ,8A and8B illustrate writing and/or programming techniques including exemplary programming voltage values, according to two embodiments of the present invention, for the memory cell including two transistors that are configured to have a common drain region;FIG. 9 illustrates a memory cell of this embodiment, in conjunction with a read amplifier and read operation including exemplary voltage values, according to an embodiment of the present invention, for the memory cell including two transistors that are configured to have a common drain region;FIGS. 10A and 10B illustrate writing and/or programming techniques including exemplary programming voltage values, according to two embodiments of the present invention, for a memory array including a plurality of memory cells each having two transistors that are configured to have a common drain region;FIG. 10C illustrates exemplary read operation voltage values, according to an embodiment of the present invention, for a memory array including a plurality of memory cells each having two transistors that are configured to have a common drain region;FIG. 11 illustrates a memory cell including two transistors that are configured to have a common source region and connected gates, according to one embodiment of the present invention;FIG. 12 illustrates an exemplary layout of the memory cell ofFIG. 11 ;FIGS. 13A and 13B illustrate writing and/or programming techniques including exemplary programming voltage values, for the memory cell ofFIG. 11 ;FIG. 14 illustrates a memory cell ofFIG. 11 , in conjunction with a read amplifier and read operation including exemplary voltage values, according to an embodiment of the present invention;FIGS. 15A and 15B illustrate writing and/or programming techniques including exemplary programming voltage values, for a memory array including a plurality of memory cells ofFIG. 11 ;FIG. 15C illustrates exemplary read operation voltage values, according to an embodiment of the present invention, for a memory array including a plurality of memory cells ofFIG. 11 ;FIGS. 16A-16C illustrate writing and/or programming techniques (including exemplary programming voltage values), according to another aspect of the present invention, for a memory cell ofFIG. 11 ;FIGS. 17 and 18 illustrate a memory array including a plurality of memory cells having a separate source line array that define a particular row of memory cells, and exemplary writing and/or programming techniques (including exemplary programming voltage values), according to another aspect of the present invention;FIGS. 19A and 19B illustrate exemplary and alternative read operation voltage values, according to an embodiment of the present invention, for a memory array ofFIGS. 17 and 18 ;FIG. 20 illustrates an exemplary layout of the memory array ofFIGS. 17 and 18 ;FIGS. 21 and 22 illustrate a memory array including a plurality of memory cells having a common source line array that define a particular row of memory cells, and exemplary writing and/or programming techniques (including exemplary programming voltage values), according to another aspect of the present invention;FIG. 23 illustrates exemplary read operation voltage values, according to an embodiment of the present invention, for a memory array ofFIGS. 21 and 22 ;FIG. 24 illustrates an exemplary layout of the memory array ofFIGS. 21 and 22 ;FIGS. 25 and 26 illustrate another memory array architecture including a plurality of memory cells having a common source line array, and exemplary writing and/or programming techniques (including exemplary programming voltage values), according to another aspect of the present invention;FIG. 27 illustrates exemplary read operation voltage values, according to an embodiment of the present invention, for a memory array ofFIGS. 25 and 26 ;FIG. 28 illustrates an exemplary layout of the memory array ofFIGS. 25 and 26 ; andFIGS. 29 and 30 illustrate a refresh architecture and technique for the memory cell and memory cell array according to one embodiment of the present invention.- There are many inventions described and illustrated herein. In a first aspect, the present invention is directed to a memory cell and technique of reading data from and writing data into that memory cell. In this regard, in one embodiment of this aspect of the invention, the memory cell includes two transistors which store complementary data states. That is, the two-transistor memory cell includes a first transistor that maintains a complementary state relative to the second transistor. As such, when programmed, one of the transistors of the memory cell stores a logic low (a binary “0”) and the other transistor of the memory cell stores a logic high (a binary “1”).

- The data state of the two-transistor complementary memory cell may be read and/or determined by sampling, sensing measuring and/or detecting the polarity of the logic states stored in each transistor of complementary memory cell. That is, the two-transistor complementary memory cell is read by sampling, sensing, measuring and/or detecting the difference in signals (current or voltage) stored in the two transistors.

- With reference to

FIGS. 3A and 3B , in one embodiment,memory cell 100 is a bi-stable memory cell which includestransistor 102aandtransistor 102b. In a first logic state ofmemory cell 100,transistor 102astores a logic low andtransistor 102bstores a logic high. (See, for example,FIG. 3A ). In contrast, in a second logic state ofmemory cell 100,transistor 102astores a logic high andtransistor 102bstores a logic low. (See, for example,FIG. 3B ). - With reference to

FIG. 4 , the state ofmemory cell 100 may be read and/or determined bycomparator 104, which may be a voltage or current type comparator (for example, a cross-coupled sense amplifier). In this regard,comparator 104 may compare the different logic states stored intransistor 102aandtransistor 102b. Thus, wheretransistor 102aandtransistor 102bstore either logic “1” or logic “0”, the difference is either 1−0=1 or 0−1=−1. As such, the read window may be described as the absolute difference between the logic high state and logic low state (i.e., 1−(−1)=2), which may be 2× the read window of the conventional memory cell. Notably, pass gates and/or column switch circuitry (not illustrated) may be employed to selectively connecttransistors comparator 104 to facilitate the read operation of the data state ofmemory cell 100. - Thus,

memory cell 100 of the present invention may include several advantages relative to conventional dynamic random access memory cells, including, for example: (i) the read operation is less sensitive to variation in the values of the binary states because a logic state is determined by the difference in states of the individual transistors, (ii) no reference circuit is necessary, (iii) thememory cell 100 includes a larger read window (as compared to conventional dynamic random access memory cells), which results in faster access time, and (iv) a less complicated and/or complex sense amplifier may be employed. - The

transistor 102aand/ortransistor 102bmay be symmetrical or non-symmetrical devices. Wheretransistors 102aand/ortransistor 102bare symmetrical, the source and drain regions are essentially interchangeable. However, wheretransistors 102aand/ortransistor 102bare non-symmetrical devices, the source or drain regions oftransistor 102aand/ortransistor 102bmay have different electrical, physical, doping concentration and/or doping profile characteristics. As such, the source or drain regions of the non-symmetrical device are typically not interchangeable. - In one embodiment,

memory cell 100 includestransistors transistors 102aand/or102bmay have the same or similar characteristics as the transistors described and illustrated in the Semiconductor Memory Device Patent Application. Notably,transistors transistors - In those instances where

transistors transistors transistors transistors - A memory device may include a plurality of

memory cells 100 arranged in repeating patterns. Thememory cell 100 may be arranged in an array in many different ways. All layout configurations fortransistors transistors FIGS. 5 and 6 , in one embodiment,transistors common drain regions transistors regions drain regions gates body regions transistors body regions - In particular, with reference to

FIGS. 7A and 7B , in one embodiment, a logic low (binary “0” state) is written intotransistor 102aand a logic high (binary “1” state) is written intotransistor 102busing the indicated (exemplary) voltage levels. Notably, the voltage levels indicated inFIGS. 7A and 7B may be relative or absolute. In this regard, a logic low may be written intotransistor 102a(FIG. 7A ) ortransistor 102b(FIG. 7B ) using the voltages indicated. Alternatively, the voltages indicated may be relative in that each voltage level, for example, may be increased or decreased by a given voltage (for example, 0.5 volts). - With reference to

FIGS. 8A and 8B , the logic levels may be programmed intotransistors transistor 102a(FIG. 8B ) and a logic high is written intotransistor 102b(FIG. 8A ) using a negative gate voltage. - The

source regions transistors cell 100. In this regard,source regions transistors body regions transistor comparator 104 in a differential manner. Exemplary read voltage signals are indicated inFIG. 9 . - Notably, pass gates and/or column switch circuitry (not illustrated) may be employed to selectively connect

source regions transistors cell 100. Moreover, as is apparent fromFIG. 6 , a memory device may include a plurality ofmemory cells 100, arranged in repeating patterns. In this regard, with reference toFIGS. 10A and 10B , the exemplary write techniques, described above, are illustrated in a schematic representation of a memory matrix. Further, with reference toFIG. 10C , the exemplary read technique, described above, is illustrated in a schematic representation of a memory matrix. Notably, the exemplary read and write techniques ofFIGS. 10A-10C , including the exemplary levels of the read and write voltages, may reduce, minimize and/or eliminate any disturbance issues (for example, issues of stored charge loss or gain within memory cells) caused to memory cells having common gate lines, drain lines and/or source lines with memory cells that are accessed via read and write operations. - In another embodiment, with reference to

FIGS. 11 and 12 ,memory cell 100 may include a layout wherebytransistors common source regions gates FIG. 13A (write logic low) andFIG. 13B (write logic high). An exemplary read technique is illustrated inFIG. 14 . Notably, the voltage levels indicated inFIGS. 13A, 13B and14 may be relative or absolute. In this regard, a logic low may be written intotransistor 102a(FIG. 13A ) ortransistor 102b(FIG. 13B ) using the voltages indicated. Alternatively, the voltages indicated may be relative in that each voltage level, for example, may be increased or decreased by a given voltage (for example, 0.25 volts). - A memory array having a plurality of

memory cells 100 wherein the source regions and gates (gate lines) oftransistors FIGS. 15A-15C . In this regard, with reference toFIGS. 15A and 15B , exemplary write techniques of the memory array of this embodiment are illustrated in a schematic representation of a memory matrix. With reference toFIG. 15C , an exemplary read technique is illustrated in a schematic representation of a memory matrix including a plurality ofmemory cells 100 configured with common source regions and gates (gate line). Notably, the exemplary read and write techniques ofFIGS. 15A-15C , including the exemplary levels of the read and write voltages, may reduce, minimize and/or eliminate any disturbance issues (to neighboring cells) that may result using other read and write voltage levels. - In certain embodiments, it may be advantageous to further reduce, minimize and/or eliminate any issues of disturbance (for example, issues of stored charge loss or gain within memory cells) of the data states of memory cells having common gate lines, drain lines and/or source lines with those memory cells that are being accessed (i.e., being read from or written to). In one embodiment, a two-step write operation may be employed to

program memory cell 100awith little to no disturbance to adjacent and/or neighboring cells (i.e., cells that share source lines, drain lines and/or gate lines). In this regard, an entire row of memory cells may first be written to the same logic state and thereafter, individual bits are written to the opposite state in accordance with a desired data state (i.e., the individual bits are written to another state to reflect a desired data state). - In particular, with reference to

FIG. 16A , in one embodiment, the memory cells having a common source line are first written to the same logic state (for example, logic high or binary “1”). In this way, the state ofmemory cell 100 is “cleared”. Thereafter, individual transistors102 ofmemory cells 100 are written to a particular, desired and/or predetermined logic state (see, for example,FIG. 16B (write “0”) andFIG. 16C (write “1”)) according to the particular, desired and/or predetermined logic state ofmemory cell 100. That is, one of the transistors ofmemory cell 100 is written to logic low (binary “0”) to write either a logic high or logic low into memory cell100 (i.e.,transistor 102aofFIG. 16B to store logic low inmemory cell 100; andtransistor 102bofFIG. 16C to store logic high in memory cell100). Notably, writing logic low to the other transistor ofmemory cell 100 is inhibited by applying a suitable bitline voltage. - Thus, in this embodiment, the first step of the write operation clears the memory cells having a common source line and the second step writes or stores new data or the previous data (in the event that the data did not change). Array architectures employing this write operation technique may have an advantage that the memory cells of the array are not “disturbed” (or experience little and/or negligible disturbance) because “high” voltages are applied in the row direction (i.e., on source lines114) but not in the column direction (i.e., on the drain lines116). Notably, this write technique may be performed as a page mode write where the page is first “cleared” and then individual bytes (or bits) in a page are written to a new state.

- Such a write technique may also be suitable for other memory array architectures or configurations. For example, the write technique may be implemented where

memory cells 100 of each row of transistors102 has a dedicated source line to minimize, reduce and/or eliminate disturbance on adjacent rows. With reference toFIGS. 17, 18 ,19A and19B, and20, in one embodiment, a given row may be written to by applying a clear operation followed by a selective write operation. In this regard, a plurality ofmemory cells 100, having gates that are connected to a common gate line, are arranged to formrow 120. Exemplary voltages that implement a clear operation forrow 120 and maintain the remaining portion of the array in a fixed state (i.e., unchanged in response to the clear operation) are indicated inFIG. 17 . In response, the same logic state (for example, logic high or binary “1”) is stored in bothtransistors memory cells 100 ofrow 120. In this way, the state ofmemory cell 100 is “cleared”. - Thereafter,

individual transistors memory cells 100 ofrow 120 are written to a particular, desired and/or predetermined logic state (see, for example,FIG. 18 (write “1”) inmemory cell 100a) in order to store a particular, desired and/or predetermined logic state inmemory cell 100. That is, as described above, one of the transistors ofmemory cell 100 is written to logic low (binary “0”) to write either a logic high or logic low intomemory cell 100. Notably, writing logic low to the other transistor of thememory cell 100 is inhibited by applying a suitable bitline voltage. - With reference to

FIGS. 19A and 19B , the data may be read frommemory cells 100 ofrow 120 by applying the exemplary voltages indicated. Notably, the exemplary read voltages ofFIG. 19B may avoid, reduce and/or minimize the need for charge pumping to eliminate minority carriers from the floating body—gate interface. - Another memory array architectures that may employ the two-step write technique that eliminates, minimizes and/or reduces disturbance to memory cells when reading from and/or writing to adjacent memory cells is illustrated in

FIGS. 21-24 . In this architecture, the source lines are shared but bit lines are separated. Thetransistors memory cell 100aare located on separate rows. The gates oftransistors - Notably,

transistors memory cell 100aare located on separate rows with the gates of eachtransistor drain lines transistor memory cell 100aso that eachtransistor FIG. 23 ). FIGS. 25-28 illustrate another memory array architecture in which a plurality of memory cells “share” a source line and employ the two-step write technique that may eliminate, minimize and/or reduce disturbance to memory cells when reading from and/or writing to adjacent memory cells. In this regard, with reference toFIGS. 25 and 26 , in one embodiment, a given row may be written to by applying suitable voltages to implement a clear operation followed by a selective write operation. In conjunction with applying suitable voltages to implement the clear operation, a write inhibit signal is applied to the gates of memory cells that share a source line114 (for example, a write inhibit signal may be applied to the gates of transistors that comprisememory cell 100xandmemory cell 100y).- In particular, exemplary voltages that implement a clear operation for

row 120 and maintain the neighboring memory cells (for example,memory cells FIG. 25 . The individual transistors102 of thememory cells 100 ofrow 120 are written to a particular, desired and/or predetermined logic state (see, for example,FIG. 26 (write “1”) inmemory cell 100a) in order to store a particular, desired and/or predetermined logic state of thememory cell 100. That is, as described above, one of the transistors ofmemory cell 100 is written to logic low (binary “0”) to write either a logic high or logic low into thememory cell 100. - With reference to

FIG. 27 , the data may be read frommemory cells 100 ofrow 120 by applying the exemplary voltages indicated. Notably, an exemplary read inhibit voltage for the remaining portion of the array (including the neighboring memory cells) is also indicated. The read inhibit voltage/signal maintains the unselected portion of the array in a fixed state (i.e., unchanged in response to the read operation). - The

memory cell 100 is a dynamic storage device. As such,memory cell 100 must be periodically or intermittently refreshed to maintain its data state.FIGS. 29 and 30 illustrate an exemplary (and inventive) refresh configuration and technique for refreshing and/or re-storing the data state ofmemory cell 100. In one embodiment,gates source regions transistors memory cell 100 are connected and thereafter a current (I) is applied on the electrically shorted gates and sources. Thedrain regions transistors - With reference to

FIG. 29 , in operation, becausetransistors memory cell 100 have different thresholds depending on which transistor is storing logic low and which transistor is storing a logic high, the forced current (I) will pass mainly through the transistor having the lower threshold (i.e., the transistor storing a logic high (binary “1”)). With a small forced current, the transistor currents will differ by orders of magnitude. The higher current through the low threshold transistor will inject holes into the body of that transistor and, as such, will reinforce the logic high (binary “1”). The high threshold transistor may have some hole injection but not enough to overcome the natural tendency to return to the neutral state. - Notably, the current (I) may also be applied to the electrically shorted gates and drains with the sources maintained at a predetermined voltage (for example, 0V).

FIG. 30 illustrates the refresh technique in the context of a memory array whereinrow 120 ofmemory cells 100 are refreshed. When refreshing an entire row, the forced current flows almost exclusively through all the transistors storing a logic high (binary “1”). It should be noted that this refresh technique is well suited to the memory cells and memory array architecture of the present inventions because the optimum range of forced current is independent of the data stored in the refreshed row (that is, half the transistors contain a logic high and the other half contain a logic low).- Notably, although

FIG. 30 illustrates a “separated source” array architecture, the technique is also applicable to the other array architectures described herein. For the sake of brevity, the discussion regarding refresh will not be repeated for such other array architectures. - There are many inventions described and illustrated herein. While certain embodiments, features, materials, configurations, attributes and advantages of the inventions have been described and illustrated, it should be understood that many other, as well as different and/or similar embodiments, features, materials, configurations, attributes, structures and advantages of the present inventions that are apparent from the description, illustration and claims. As such, the embodiments, features, materials, configurations, attributes, structures and advantages of the inventions described and illustrated herein are not exhaustive and it should be understood that such other, similar, as well as different, embodiments, features, materials, configurations, attributes, structures and advantages of the present inventions are within the scope of the present invention.

- For example, as mentioned above, the illustrated voltage levels to implement the write and read operations are exemplary. The indicated voltage levels may be relative or absolute. That is, for example, a logic low may be written into