TWI780709B - Spliced display apparatus - Google Patents

Spliced display apparatusDownload PDFInfo

- Publication number

- TWI780709B TWI780709BTW110117761ATW110117761ATWI780709BTW I780709 BTWI780709 BTW I780709BTW 110117761 ATW110117761 ATW 110117761ATW 110117761 ATW110117761 ATW 110117761ATW I780709 BTWI780709 BTW I780709B

- Authority

- TW

- Taiwan

- Prior art keywords

- display panel

- display

- outer pin

- pixel

- bonding area

- Prior art date

Links

Images

Landscapes

- Liquid Crystal (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Processing Of Terminals (AREA)

Abstract

Description

Translated fromChinese本發明是有關於一種拼接式顯示裝置。The invention relates to a spliced display device.

微型發光二極體(micro LED)顯示器具有低耗能及高亮度的優點,是許多面板廠所積極開發的重點項目之一。目前微型發光二極體顯示器單一模組的最大尺寸僅為12至14吋,若要大於55吋以上,甚至100吋以上,需要透過拼接多個微型發光二極體顯示器來達成。然而,難以避免可視的拼接縫,像是亮縫、暗縫,或模組亮態暗態顯示不良(mura),降低了顯示器視覺上的品味。The micro light emitting diode (micro LED) display has the advantages of low power consumption and high brightness, and is one of the key projects that many panel manufacturers are actively developing. At present, the maximum size of a single micro-LED display module is only 12 to 14 inches. If it is larger than 55 inches or even 100 inches, it needs to be achieved by splicing multiple micro-light-emitting diode displays. However, it is difficult to avoid visible stitching seams, such as bright seams, dark seams, or poor display (mura) of modules in bright and dark states, which reduces the visual taste of the display.

本發明提供一種拼接式顯示裝置,其拼接縫不可視。The invention provides a splicing display device, the splicing seam of which is invisible.

本發明提供一種拼接式顯示裝置,包括多個顯示面板。顯示面板各具有至少一第一側面對相鄰之顯示面板其中之一以及與第一側相交的第二側,各顯示面板具有外引腳接合區。各顯示面板包括基板、畫素陣列及多條資料線。畫素陣列位於基板上,外引腳接合區位於畫素陣列及第二側之間。資料線位於基板上,且電性連接畫素陣列,畫素陣列包括第一畫素行,第一畫素行鄰近於第一側,顯示面板包括第一顯示面板及第二顯示面板,資料線包括多條第一扇出線及多條第二扇出線。第一扇出線電性連接第一顯示面板的第一畫素行。第二扇出線電性連接第二顯示面板的第一畫素行,第二扇出線跨越第二顯示面板的第一側至第一顯示面板的第一側並延伸至第一顯示面板的外引腳接合區上。The invention provides a spliced display device, which includes a plurality of display panels. Each of the display panels has at least one first side facing one of the adjacent display panels and a second side intersecting the first side, and each display panel has an outer lead bonding area. Each display panel includes a substrate, a pixel array and a plurality of data lines. The pixel array is located on the substrate, and the outer pin bonding area is located between the pixel array and the second side. The data line is located on the substrate and is electrically connected to the pixel array. The pixel array includes a first pixel row adjacent to the first side. The display panel includes a first display panel and a second display panel. The data line includes multiple A first fan-out line and a plurality of second fan-out lines. The first fan-out line is electrically connected to the first pixel row of the first display panel. The second fan-out line is electrically connected to the first pixel row of the second display panel, the second fan-out line crosses the first side of the second display panel to the first side of the first display panel and extends to the outside of the first display panel on the pin land.

本發明提供一種拼接式顯示裝置,包括多個顯示面板及電路板,顯示面板包括第一顯示面板及第二顯示面板。顯示面板各具有至少一第一側面對相鄰之顯示面板其中之一以及與第一側相交的第二側,各顯示面板具有外引腳接合區,且各顯示面板包括基板、畫素陣列及多條資料線。畫素陣列位於基板上,外引腳接合區位於畫素陣列及第二側之間。資料線位於基板上且電性連接畫素陣列,畫素陣列包括第一畫素行,第一畫素行鄰近於第一側。電路板配置於第一顯示面板的外引腳接合區及第二顯示面板的外引腳接合區上,電路板具有多條導線,導線電性連接第二顯示面板的第一畫素行,導線自第二顯示面板的外引腳接合區跨越第二顯示面板的第一側至第一顯示面板的第一側並延伸至第一顯示面板的外引腳接合區上。The present invention provides a spliced display device, which includes a plurality of display panels and circuit boards, and the display panels include a first display panel and a second display panel. Each display panel has at least one first side facing one of the adjacent display panels and a second side intersecting with the first side, each display panel has an outer pin bonding area, and each display panel includes a substrate, a pixel array and Multiple data lines. The pixel array is located on the substrate, and the outer pin bonding area is located between the pixel array and the second side. The data line is located on the substrate and is electrically connected to the pixel array. The pixel array includes a first pixel row adjacent to the first side. The circuit board is arranged on the outer pin bonding area of the first display panel and the outer pin bonding area of the second display panel. The circuit board has a plurality of wires, and the wires are electrically connected to the first pixel row of the second display panel. The outer pin land of the second display panel spans from the first side of the second display panel to the first side of the first display panel and extends onto the outer pin land of the first display panel.

本發明提供一種拼接式顯示裝置,包括母板及多個顯示面板。母板具有支撐基材及位於支撐基材上之多條導線。顯示面板位於母板上且各具有至少一第一側面對相鄰之顯示面板其中之一以及與第一側相交的第二側,各顯示面板具有外引腳接合區,且各顯示面板包括基板及畫素陣列。基板具有多個導電通孔。畫素陣列位於基板上,外引腳接合區位於畫素陣列及第二側之間,畫素陣列包括第一畫素行,第一畫素行鄰近於第一側,顯示面板包括第一顯示面板及第二顯示面板,導線透過導電通孔電性連接第二顯示面板的第一畫素行,導線自第二顯示面板的外引腳接合區跨越第二顯示面板的第一側至第一顯示面板的第一側並延伸至第一顯示面板的外引腳接合區上。The invention provides a spliced display device, which includes a motherboard and a plurality of display panels. The motherboard has a support substrate and a plurality of wires located on the support substrate. The display panels are located on the motherboard and each has at least one first side facing one of the adjacent display panels and a second side intersecting the first side, each display panel has an outer pin bonding area, and each display panel includes a substrate and pixel arrays. The substrate has a plurality of conductive vias. The pixel array is located on the substrate, the outer pin bonding area is located between the pixel array and the second side, the pixel array includes a first pixel row, and the first pixel row is adjacent to the first side, and the display panel includes the first display panel and The second display panel, the wire is electrically connected to the first pixel row of the second display panel through the conductive via hole, and the wire crosses the first side of the second display panel from the outer pin bonding area of the second display panel to the first display panel of the first display panel. The first side extends to the outer pin bonding area of the first display panel.

基於上述,在本發明一實施例的拼接式顯示裝置中,顯示面板各具有至少一第一側面對相鄰之顯示面板其中之一,第一扇出線電性連接第一顯示面板的第一畫素行。第二扇出線電性連接第二顯示面板的第一畫素行,第二扇出線跨越第二顯示面板的第一側至第一顯示面板的第一側並延伸至第一顯示面板的外引腳接合區上。藉此,第一顯示面板的第一側及第二顯示面板的第一側之拼接縫左右兩側的第一畫素行可由單一外接電路控制。藉由單一外接電路來調整第一畫素行之灰階,可使拼接縫不可視。Based on the above, in a spliced display device according to an embodiment of the present invention, each display panel has at least one first side facing one of the adjacent display panels, and the first fan-out line is electrically connected to the first side of the first display panel. Pixel row. The second fan-out line is electrically connected to the first pixel row of the second display panel, the second fan-out line crosses the first side of the second display panel to the first side of the first display panel and extends to the outside of the first display panel on the pin land. Thereby, the first pixel rows on the left and right sides of the seam between the first side of the first display panel and the first side of the second display panel can be controlled by a single external circuit. Adjusting the gray scale of the first pixel row by a single external circuit can make the stitching seam invisible.

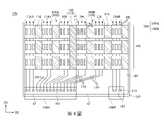

第1圖是依照本發明一實施例的拼接式顯示裝置10的上視示意圖。請參照第1圖,拼接式顯示裝置10包括多個顯示面板100。顯示面板100各具有至少一第一側a1面對相鄰之顯示面板100其中之一以及與第一側a1相交的第二側a2。為了方便說明,第1圖中繪示了第一方向D1及第二方向D2,第一方向D1與第二方向D2相交。舉例而言,第一方向D1與第二方向D2垂直,然而本發明不限於此。於本實施例中,第一側a1平行於第一方向D1,第二側a2平行於第二方向D2。FIG. 1 is a schematic top view of a spliced

各顯示面板100包括基板102、畫素陣列AR及多條資料線DL。畫素陣列AR位於基板102上。資料線DL位於基板102上,且電性連接畫素陣列AR。基板102的材質例如為玻璃、石英、塑膠、有機聚合物、不透光/反射材料(例如:導電材料、金屬、晶圓、陶瓷、或其他可適用的材料)或是其他可適用的材料。在一些實施例中,基板102也可為可撓性基板,其材質包括有機聚合物,例如:聚醯亞胺(polyimide,PI)、聚萘二甲酸乙醇酯(polyethylene naphthalate,PEN)或其它合適的材料,本發明不以此為限。舉例而言,基板102可為黃色聚醯亞胺基板。Each

各顯示面板100具有外引腳接合區103,用以連接外部電路。外部電路例如是驅動晶片、控制電路、軟性印刷電路(flexible printed circuit,FPC)或配置有驅動晶片的印刷電路板(printed circuit board,PCB)等,軟性印刷電路舉例可為液晶高分子軟性印刷電路板(Liquid Crystal Polymer (LCP) FPC board),以使畫素陣列AR能夠被驅動。外引腳接合區103位於畫素陣列AR及第二側a2之間。Each

舉例而言,顯示面板100包括第一顯示面板100A及第二顯示面板100B,拼接式顯示裝置10還包括驅動元件104,驅動元件104包括第一驅動元件104A及第二驅動元件104B。第一驅動元件104A位於第一顯示面板100的外引腳接合區103上,第二驅動元件104B位於第二顯示面板100B的外引腳接合區103上。第一顯示面板100B的外引腳接合區103連接第一驅動元件104A。第二顯示面板100B的外引腳接合區103連接第二驅動元件104B,第一驅動元件104A和第二驅動元件104B互相電性獨立。For example, the

於本實施例中,畫素陣列AR包括第一畫素行106,第一畫素行106鄰近於第一側a1。資料線DL包括多條第一扇出線108及多條第二扇出線110。第一扇出線108電性連接第一顯示面板100A的第一畫素行106。第二扇出線110電性連接第二顯示面板100B的第一畫素行106,第二扇出線110跨越第二顯示面板100B的第一側a1至第一顯示面板100A的第一側a1並延伸至第一顯示面板100A的外引腳接合區103上。藉此,第一顯示面板100A的第一側a1及第二顯示面板100B的第一側a1之拼接縫112左右兩側的第一畫素行106都是由第一驅動元件104A所控制,換言之,由單一驅動元件控制。藉由單一驅動元件來調整第一畫素行106之灰階(即亮度),可使拼接縫112不可視。In this embodiment, the pixel array AR includes a

各顯示面板100可包括多個接墊113,接墊113位於外引腳接合區103,接墊113的第一部分113A可用於將第一扇出線108及第二扇出線110連接第一驅動元件104A。由於接墊113的尺寸遠大於第一扇出線108及第二扇出線110的線寬,舉例而言,接墊113的面積為數百平方微米。因此,第二扇出線110可打線接合於第一驅動元件104A,不需耗費額外的微影製程,從而使得製程簡單化。於其他實施例中,第二扇出線110可利用噴墨塗佈技術(ink jet printing,IJP)來形成。基於導電性的考量,第一扇出線108及第二扇出線110的材質為金屬(例如鉻、金、銀、銅、錫、鉛、鉿、鎢、鉬、釹、鈦、鉭、鋁、鋅、前述金屬之合金或前述金屬之堆疊層)。然而,本發明不限於此。Each

各畫素陣列AR還包括多個第二畫素行114,第二畫素行114位於第一畫素行106之一側,且第二畫素行114用以顯示畫面,第一顯示面板100A的第二畫素行114A電性連接第一顯示面板100A的外引腳接合區103,第二顯示面板100B的第二畫素行114B電性連接第二顯示面板100B的外引腳接合區103。也就是說,第一顯示面板100A的第二畫素行114A和第二顯示面板100B的第二畫素行114B分別由第一驅動元件104A及第二驅動元件104B所控制,使各第二畫素行114A、114B可獨立顯示畫面。Each pixel array AR also includes a plurality of

於本實施例中,拼接式顯示裝置10還包括多個遮光部116及遮光層118。遮光部116分別位於相鄰的第二畫素行114A、114B之間以及第一畫素行106及第二畫素行114之間。舉例而言,第一畫素行106及第二畫素行114A、114B各包括紅色發光元件、綠色發光元件及藍色發光元件。遮光部116即俗稱的黑色矩陣(Black Matrix,BM)。遮光部116及遮光層118的材質例如是黑色樹脂,但本發明不以此為限。In this embodiment, the spliced

遮光層118覆蓋第一顯示面板100A的第一側a1及第二顯示面板100B的第一側a1,且可透過噴墨塗佈技術所形成。遮光層118具有第一遮光層120及第二遮光層122,第一遮光層120的寬度w1小於或等於各遮光部116的寬度w2,用以將第一顯示面板100A的第一畫素行106及第二顯示面板100B的第一畫素行106區隔開。The

於一實施例中,拼接式顯示裝置10還包括母板124,第一顯示面板100A及第二顯示面板100B位於母板124上,且透過黏膠126固定於母板124。第二遮光層122位於母板124上,第二扇出線110位於第二遮光層122上,因此,即使受限於拼接機台目前的精度不足以達造成拼接縫112之寬度為零,拼接縫112造成第一顯示面板100A和第二顯示面板100B之間有高低差,第二遮光層122可以將拼接縫112填平,使第二扇出線110受到支撐,提升其可靠度。黏膠126可為光學膠(optical clear adhesive)。In one embodiment, the

第3圖是依照本發明另一實施例的拼接式顯示裝置10a的上視示意圖。第3圖之拼接式顯示裝置10a及第1圖之拼接式顯示裝置10的主要差異在於:第一扇出線108各包括第一分支108Y,各第一分支108Y跨越第一顯示面板100A的第一側a1至第二顯示面板100B的第一側a1並延伸至第二顯示面板100B的外引腳接合區103上。藉此,第一顯示面板100A的第一畫素行106還可以是由第二驅動元件104B所控制。FIG. 3 is a schematic top view of a spliced

於一實施例中,第二扇出線110各包括第二分支110Y,各第二分支110Y延伸至第二顯示面板100B的外引腳接合區103上。藉此,第二顯示面板100B的第一畫素行106還可以是由第二驅動元件104B所控制。藉此,第一顯示面板100A的第一側a1及第二顯示面板100B的第一側a1之拼接縫112左右兩側的第一畫素行106還可以都是由第二驅動元件104B所控制,換言之,由單一外接電路控制。藉由單一外接電路來調整第一畫素行106之灰階(即亮度),可使拼接縫112不可視。In one embodiment, each of the second fan-out

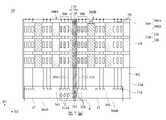

第4圖是依照本發明另一實施例的拼接式顯示裝置10b的上視示意圖。第4圖之拼接式顯示裝置10b及第1圖之拼接式顯示裝置10的主要差異在於:第二顯示面板100B的畫素陣列AR還包括第三畫素行128,資料線DL還包括多條第三扇出線130,第三扇出線130電性連接第二顯示面板100B的第三畫素行128,第三扇出線130跨越第二顯示面板100B的第一側a1至第一顯示面板100A的第一側a1並延伸至第一顯示面板100A的外引腳接合區103上。藉此,第二顯示面板100B的第一畫素行106及第三畫素行128都是由第一驅動元件104A所控制。換言之,第二顯示面板100B的最左兩排畫素行可由單一外接電路控制。藉由單一外接電路來調整第一畫素行106及第三畫素行128之灰階(即亮度),可使拼接縫112不可視。且藉由這樣的配置,可依照產品需求調整多個畫素行的灰階。FIG. 4 is a schematic top view of a spliced

第5圖是依照本發明另一實施例的拼接式顯示裝置20的上視示意圖。第6圖是沿著第5圖的剖線6-6’的剖面示意圖,第5圖及第6圖的實施例沿用第1圖至第2圖的實施例的元件標號與部分內容,其中採用相同或近似的標號來表示相同或近似的元件,並且省略了相同技術內容的說明。關於省略部分的說明可參考前述實施例,在此不贅述。FIG. 5 is a schematic top view of a spliced

拼接式顯示裝置20包括多個顯示面板200。顯示面板200各具有至少一第一側a1面對相鄰之顯示面板200其中之一以及與第一側a1相交的第二側a2,各顯示面板200具有外引腳接合區203,且各顯示面板200包括基板202、畫素陣列AR及多條資料線DL。畫素陣列AR位於基板202上,外引腳接合區203位於畫素陣列AR及第二側a2之間。多條資料線DL位於基板202上,且電性連接畫素陣列AR,畫素陣列AR包括第一畫素行206,第一畫素行206鄰近於第一側a1,顯示面板200包括第一顯示面板200A及第二顯示面板200B。The spliced

電路板208配置於第一顯示面板200A的外引腳接合區203及第二顯示面板200B的外引腳接合區203上,電路板208具有基板SB及位於基板SB上的多個接墊PD,各接墊PD對應於第一顯示面板200A及第二顯示面板200B的接墊213,電路板208具有位於基板SB上的多條導線210,導線210電性連接第二顯示面板200B的第一畫素行206,導線210自第二顯示面板200B的外引腳接合區203跨越第二顯示面板200B的第一側a1至第一顯示面板200A的第一側a1並延伸至第一顯示面板200A的外引腳接合區203上。藉此,第一顯示面板200A的第一側a1及第二顯示面板200B的第一側a1之拼接縫212左右兩側的第一畫素行206都是由第一驅動元件204A所控制,換言之,由單一驅動元件控制。藉由單一驅動元件來調整第一畫素行206之灰階(即亮度),可使拼接縫212不可視。The

第二遮光層122位於母板224上,因此,即使拼接精度不高,造成拼接縫212之寬度不為零,拼接縫212造成第一顯示面板200A和第二顯示面板200B之間有高低差,第二遮光層122可以將拼接縫212填平,使電路板208受到支撐,提升其可靠度。The second light-

於本實施例中,拼接式顯示裝置20還包括異方性導電膠214,異方性導電膠214位於電路板208及第一顯示面板200A之間,且位於電路板208及第二顯示面板200B之間,用於將電路板208固定於第一顯示面板200A及第二顯示面板200B。In this embodiment, the spliced

第7圖是依照本發明一實施例的拼接式顯示裝置30的俯視示意圖,第8圖是第7圖的區域R的放大示意圖。第9圖是沿著8圖的剖線9a-9a’及9b-9b’的剖面示意圖。第7圖至第9圖的實施例沿用第1圖至第2圖的實施例的元件標號與部分內容,其中採用相同或近似的標號來表示相同或近似的元件,並且省略了相同技術內容的說明。關於省略部分的說明可參考前述實施例,在此不贅述。FIG. 7 is a schematic top view of a

拼接式顯示裝置30包括母板324及多個顯示面板300。母板324具有支撐基材326及位於支撐基材326上之多條導線328。於一實施例中,母板324還包括多個接墊305,接墊305位於導線328上。The spliced

基於導電性的考量,導線328的材質為金屬(例如鉻、金、銀、銅、錫、鉛、鉿、鎢、鉬、釹、鈦、鉭、鋁、鋅、前述金屬之合金或前述金屬之堆疊層)。然而,本發明不限於此。Based on the consideration of conductivity, the material of the

顯示面板300位於母板324上且各具有至少一第一側a1面對相鄰之顯示面板300其中之一以及與第一側a1相交的第二側a2,各顯示面板300具有外引腳接合區303,且各顯示面板300包括基板302及畫素陣列AR。基板302具有多個導電通孔V。The

畫素陣列AR位於基板302上,外引腳接合區303位於畫素陣列AR及第二側a2之間,畫素陣列AR包括第一畫素行306,第一畫素行306鄰近於第一側a1,顯示面板300包括第一顯示面板300A及第二顯示面板300B。The pixel array AR is located on the

各顯示面板300可包括多個接墊314,接墊314位於外引腳接合區303,資料線DL還包括多條第一扇出線308及多條第二扇出線310,接墊314包含第一部分314A用於將第二扇出線310連接第一驅動元件304A。接墊314的第一部分314A重疊於母板324的接墊305,且接墊314的第一部分314A透過導電通孔V電性連接母板324的接墊305。Each

導線328自第二顯示面板300B的外引腳接合區303跨越第二顯示面板300A的第一側a1至第一顯示面板300B的第一側a1並延伸至第一顯示面板300A的外引腳接合區303上,導線328透過導電通孔V電性連接第二顯示面板300B的第一畫素行306。The

舉例而言,第一驅動元件304A的訊號沿著箭頭316自第一顯示面板300A的接墊314的第一部分314A傳遞至導電通孔V及母板324的接墊305,然後經過母板324的導線328,再傳遞至母板324的接墊305及導電通孔V,最後傳遞至第二顯示面板300B的接墊314的第一部分314A,使第二顯示面板300B的第一畫素行306接收到訊號。For example, the signal of the

藉此,第一顯示面板300A的第一側a1及第二顯示面板300B的第一側a1之拼接縫312左右兩側的第一畫素行306都是由第一驅動元件304A所控制,換言之,由單一驅動元件控制。藉由單一驅動元件來調整第一畫素行306之灰階(即亮度),可使拼接縫312不可視。Thus, the

綜上所述,在本發明一實施例的拼接式顯示裝置中,第二扇出線電性連接第二顯示面板的第一畫素行,第二扇出線跨越第二顯示面板的第一側至第一顯示面板的第一側並延伸至第一顯示面板的外引腳接合區上。藉此,第一顯示面板的第一側及第二顯示面板的第一側之拼接縫左右兩側的第一畫素行可由單一外接電路控制。藉由單一外接電路來調整第一畫素行之灰階,可使拼接縫不可視。To sum up, in the spliced display device according to an embodiment of the present invention, the second fan-out line is electrically connected to the first pixel row of the second display panel, and the second fan-out line crosses the first side of the second display panel to the first side of the first display panel and extend to the outer pin bonding area of the first display panel. Thereby, the first pixel rows on the left and right sides of the seam between the first side of the first display panel and the first side of the second display panel can be controlled by a single external circuit. Adjusting the gray scale of the first pixel row by a single external circuit can make the stitching seam invisible.

2-2’,6-6’:剖線 9a-9a’,9b-9b’:剖線 10,10a,10b:拼接式顯示裝置 20,30:拼接式顯示裝置 100:顯示面板 100A:第一顯示面板 100B:第二顯示面板 102:基板 103:外引腳接合區 104:驅動元件 104A:第一驅動元件 104B:第二驅動元件 106:第一畫素行 108:第一扇出線 108Y:第一分支 110:第二扇出線 110Y:第二分支 112:拼接縫 113:接墊 113A:第一部分 114,114A,114B:第二畫素行 116:遮光部 118:遮光層 120:第一遮光層 122:第二遮光層 124:母板 126:黏膠 128:第三畫素行 130:第三扇出線 200:顯示面板 202:基板 203:外引腳接合區 204A:第一驅動元件 206:第一畫素行 208:電路板 210:導線 212:拼接縫 214:異方性導電膠 300:顯示面板 302:基板 303:外引腳接合區 304A:第一驅動元件 305:接墊 306,306B:第一畫素行 308:第一扇出線 310:第二扇出線 314:接墊 314A:第一部分 316:箭頭 324:母板 326:支撐基材 328:導線 a1:第一側 a2:第二側 AR:畫素陣列 D1:第一方向 D2:第二方向 DL:資料線 PD:接墊 SB:基板 V:導電通孔 w1,w2:寬度2-2', 6-6': split line 9a-9a', 9b-9b': broken line 10, 10a, 10b: Mosaic display device 20,30: Mosaic display device 100: display panel 100A: The first display panel 100B: second display panel 102: Substrate 103: Outer pin land 104: drive element 104A: the first driving element 104B: the second driving element 106: The first pixel line 108: The first fan out 108Y: the first branch 110: Second fan outlet 110Y: the second branch 112: stitching seam 113: Pad 113A: Part I 114, 114A, 114B: the second pixel row 116: shading part 118: shading layer 120: the first shading layer 122: the second shading layer 124: motherboard 126: viscose 128: The third pixel line 130: The third fan out 200: display panel 202: Substrate 203: Outer pin land 204A: first driving element 206: The first pixel line 208: circuit board 210: wire 212: stitching seam 214: Anisotropic conductive adhesive 300: display panel 302: Substrate 303: Outer pin land 304A: first driving element 305: Pad 306,306B: the first pixel row 308: The first fan out 310: The second fan out 314: Pad 314A: Part I 316: arrow 324: motherboard 326: supporting substrate 328: wire a1: first side a2: second side AR: pixel array D1: the first direction D2: Second direction DL: data line PD: Pad SB: Substrate V: Conductive Via w1, w2: width

閱讀以下詳細敘述並搭配對應之圖式,可了解本揭露之多個樣態。需留意的是,圖式中的多個特徵並未依照該業界領域之標準作法繪製實際比例。事實上,所述之特徵的尺寸可以任意的增加或減少以利於討論的清晰性。 第1圖是依照本發明一實施例的拼接式顯示裝置的上視示意圖。 第2圖是沿著第1圖的剖線2-2’的剖面示意圖。 第3圖是依照本發明另一實施例的拼接式顯示裝置的上視示意圖。 第4圖是依照本發明另一實施例的拼接式顯示裝置的上視示意圖。 第5圖是依照本發明另一實施例的拼接式顯示裝置的上視示意圖。 第6圖是沿著第5圖的剖線6-6’的剖面示意圖。 第7圖是依照本發明另一實施例的拼接式顯示裝置的上視示意圖。 第8圖是第7圖的區域R的放大示意圖。 第9圖是沿著第8圖的剖線9a-9a’及剖線9b-9b’的剖面示意圖。Read the following detailed description and match the corresponding diagrams to understand the multiple aspects of this disclosure. It should be noted that many features in the drawings are not drawn to scale in accordance with standard practice in this industry. In fact, the dimensions of the described features may be arbitrarily increased or decreased for clarity of discussion. FIG. 1 is a schematic top view of a spliced display device according to an embodiment of the present invention. Fig. 2 is a schematic cross-sectional view along line 2-2' of Fig. 1 . FIG. 3 is a schematic top view of a spliced display device according to another embodiment of the present invention. FIG. 4 is a schematic top view of a spliced display device according to another embodiment of the present invention. FIG. 5 is a schematic top view of a spliced display device according to another embodiment of the present invention. Fig. 6 is a schematic cross-sectional view along line 6-6' of Fig. 5 . FIG. 7 is a schematic top view of a spliced display device according to another embodiment of the present invention. Fig. 8 is an enlarged schematic view of the region R in Fig. 7 . Fig. 9 is a schematic cross-sectional view along the

國內寄存資訊(請依寄存機構、日期、號碼順序註記) 無 國外寄存資訊(請依寄存國家、機構、日期、號碼順序註記) 無Domestic deposit information (please note in order of depositor, date, and number) none Overseas storage information (please note in order of storage country, institution, date, and number) none

2-2’:剖線2-2': section line

10:拼接式顯示裝置10: Mosaic display device

100:顯示面板100: display panel

100A:第一顯示面板100A: The first display panel

100B:第二顯示面板100B: second display panel

102:基板102: Substrate

103:外引腳接合區103: Outer pin land

104:驅動元件104: drive element

104A:第一驅動元件104A: the first driving element

104B:第二驅動元件104B: the second driving element

106:第一畫素行106: The first pixel line

108:第一扇出線108: The first fan out

110:第二扇出線110: Second fan outlet

112:拼接縫112: stitching seam

113:接墊113: Pad

113A:第一部分113A: Part I

114,114A,114B:第二畫素行114, 114A, 114B: the second pixel row

116:遮光部116: shading part

118:遮光層118: shading layer

120:第一遮光層120: the first shading layer

122:第二遮光層122: the second shading layer

124:母板124: motherboard

a1:第一側a1: first side

a2:第二側a2: second side

AR:畫素陣列AR: pixel array

D1:第一方向D1: the first direction

D2:第二方向D2: Second direction

DL:資料線DL: data line

w1,w2:寬度w1, w2: width

Claims (10)

Translated fromChinesePriority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| TW110117761ATWI780709B (en) | 2021-05-17 | 2021-05-17 | Spliced display apparatus |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| TW110117761ATWI780709B (en) | 2021-05-17 | 2021-05-17 | Spliced display apparatus |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| TWI780709Btrue TWI780709B (en) | 2022-10-11 |

| TW202247129A TW202247129A (en) | 2022-12-01 |

Family

ID=85462673

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| TW110117761ATWI780709B (en) | 2021-05-17 | 2021-05-17 | Spliced display apparatus |

Country Status (1)

| Country | Link |

|---|---|

| TW (1) | TWI780709B (en) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI873969B (en)* | 2023-11-10 | 2025-02-21 | 友達光電股份有限公司 | Displaying system |

| TWI891417B (en)* | 2024-06-26 | 2025-07-21 | 友達光電股份有限公司 | Splicing display device and driving method thereof |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20170132963A1 (en)* | 2015-06-30 | 2017-05-11 | Boe Technology Group Co., Ltd. | Display driving method, display panel and manufacturing method thereof, and display apparatus |

| US20180108860A1 (en)* | 2016-10-14 | 2018-04-19 | Boe Technology Group Co., Ltd. | Display substrate, display panel and display device |

| CN108766249A (en)* | 2018-08-09 | 2018-11-06 | 武汉天马微电子有限公司 | Foldable display panel and foldable display device |

| CN109935613A (en)* | 2018-04-18 | 2019-06-25 | 友达光电股份有限公司 | display panel |

| US20190266932A1 (en)* | 2015-06-12 | 2019-08-29 | Boe Technology Group Co., Ltd. | Testing method for splicing screens |

- 2021

- 2021-05-17TWTW110117761Apatent/TWI780709B/enactive

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20190266932A1 (en)* | 2015-06-12 | 2019-08-29 | Boe Technology Group Co., Ltd. | Testing method for splicing screens |

| US20170132963A1 (en)* | 2015-06-30 | 2017-05-11 | Boe Technology Group Co., Ltd. | Display driving method, display panel and manufacturing method thereof, and display apparatus |

| US20180108860A1 (en)* | 2016-10-14 | 2018-04-19 | Boe Technology Group Co., Ltd. | Display substrate, display panel and display device |

| CN109935613A (en)* | 2018-04-18 | 2019-06-25 | 友达光电股份有限公司 | display panel |

| CN108766249A (en)* | 2018-08-09 | 2018-11-06 | 武汉天马微电子有限公司 | Foldable display panel and foldable display device |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI873969B (en)* | 2023-11-10 | 2025-02-21 | 友達光電股份有限公司 | Displaying system |

| TWI891417B (en)* | 2024-06-26 | 2025-07-21 | 友達光電股份有限公司 | Splicing display device and driving method thereof |

Also Published As

| Publication number | Publication date |

|---|---|

| TW202247129A (en) | 2022-12-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN107799008B (en) | display device | |

| KR102695728B1 (en) | Display device | |

| CN113130463B (en) | A light-emitting substrate, its preparation method, and a display device | |

| CN100416353C (en) | display device | |

| US12127453B2 (en) | Display device having reduced non-display area | |

| US20080024424A1 (en) | Liquid Crystal Display Device | |

| CN113075808A (en) | Splicing display panel and display device | |

| TWI780709B (en) | Spliced display apparatus | |

| KR101348756B1 (en) | Film-chip complex and display device having the same | |

| WO2021087726A1 (en) | Array substrate, manufacturing method therefor and display device | |

| JP2006209089A (en) | Display device | |

| US20240404959A1 (en) | Wiring substrate, array substrate and light emitting module having control regions arranged into control region rows and control region columns | |

| TWI734062B (en) | Display panel and electronic device | |

| US11410589B2 (en) | Display device | |

| TWI791404B (en) | Display panel | |

| TWI783875B (en) | Display panel | |

| US11798876B2 (en) | Chip on film package and display device including the same | |

| KR101033119B1 (en) | Line on Glass Liquid Crystal Display | |

| CN220914224U (en) | Display device | |

| JP7684851B2 (en) | display device | |

| CN119600971A (en) | Display device and driving method thereof | |

| CN118645499A (en) | Display module and display device | |

| JP2023184061A (en) | Display and driver | |

| WO2024060263A1 (en) | Display panel, display device and tiled display device | |

| KR20210157945A (en) | Display apparatus |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| GD4A | Issue of patent certificate for granted invention patent |