TWI741204B - 電可抹除可程式化記憶體單元、電可程式化及可抹除非揮發性記憶體單元及操作記憶體單元之方法 - Google Patents

電可抹除可程式化記憶體單元、電可程式化及可抹除非揮發性記憶體單元及操作記憶體單元之方法Download PDFInfo

- Publication number

- TWI741204B TWI741204BTW107127198ATW107127198ATWI741204BTW I741204 BTWI741204 BTW I741204BTW 107127198 ATW107127198 ATW 107127198ATW 107127198 ATW107127198 ATW 107127198ATW I741204 BTWI741204 BTW I741204B

- Authority

- TW

- Taiwan

- Prior art keywords

- floating gate

- substrate

- gate

- region

- memory cell

- Prior art date

Links

- 238000000034methodMethods0.000titleclaimsdescription23

- 239000000758substrateSubstances0.000claimsabstractdescription89

- 239000004065semiconductorSubstances0.000claimsabstractdescription8

- 230000008878couplingEffects0.000claimsdescription50

- 238000010168coupling processMethods0.000claimsdescription50

- 238000005859coupling reactionMethods0.000claimsdescription50

- 238000005513bias potentialMethods0.000claimsdescription30

- 238000009413insulationMethods0.000claimsdescription13

- 230000008859changeEffects0.000claimsdescription7

- 229910021420polycrystalline siliconInorganic materials0.000description28

- 229920005591polysiliconPolymers0.000description28

- 150000004767nitridesChemical class0.000description13

- XUIMIQQOPSSXEZ-UHFFFAOYSA-NSiliconChemical compound[Si]XUIMIQQOPSSXEZ-UHFFFAOYSA-N0.000description12

- 238000005530etchingMethods0.000description12

- 229910052710siliconInorganic materials0.000description12

- 239000010703siliconSubstances0.000description11

- 230000008569processEffects0.000description8

- 230000005684electric fieldEffects0.000description7

- 239000002784hot electronSubstances0.000description7

- 238000001020plasma etchingMethods0.000description7

- 230000005641tunnelingEffects0.000description6

- 230000004888barrier functionEffects0.000description4

- 230000007423decreaseEffects0.000description4

- 238000010586diagramMethods0.000description4

- 238000002955isolationMethods0.000description4

- 238000004519manufacturing processMethods0.000description4

- 229910021421monocrystalline siliconInorganic materials0.000description4

- 230000004044responseEffects0.000description4

- VYPSYNLAJGMNEJ-UHFFFAOYSA-NSilicium dioxideChemical compoundO=[Si]=OVYPSYNLAJGMNEJ-UHFFFAOYSA-N0.000description3

- 229910021417amorphous siliconInorganic materials0.000description3

- 238000001514detection methodMethods0.000description3

- 230000007246mechanismEffects0.000description3

- 238000012545processingMethods0.000description3

- 230000009286beneficial effectEffects0.000description2

- 238000013461designMethods0.000description2

- 239000003989dielectric materialSubstances0.000description2

- 238000002347injectionMethods0.000description2

- 239000007924injectionSubstances0.000description2

- 230000004048modificationEffects0.000description2

- 238000012986modificationMethods0.000description2

- 230000003647oxidationEffects0.000description2

- 238000007254oxidation reactionMethods0.000description2

- 238000003860storageMethods0.000description2

- 230000005689Fowler Nordheim tunnelingEffects0.000description1

- 229910052581Si3N4Inorganic materials0.000description1

- 238000009825accumulationMethods0.000description1

- 229910052785arsenicInorganic materials0.000description1

- RQNWIZPPADIBDY-UHFFFAOYSA-Narsenic atomChemical compound[As]RQNWIZPPADIBDY-UHFFFAOYSA-N0.000description1

- 230000015572biosynthetic processEffects0.000description1

- 239000012141concentrateSubstances0.000description1

- 239000004020conductorSubstances0.000description1

- 238000007796conventional methodMethods0.000description1

- 230000007547defectEffects0.000description1

- 238000000151depositionMethods0.000description1

- 239000002019doping agentSubstances0.000description1

- BHEPBYXIRTUNPN-UHFFFAOYSA-Nhydridophosphorus(.) (triplet)Chemical compound[PH]BHEPBYXIRTUNPN-UHFFFAOYSA-N0.000description1

- 239000012535impuritySubstances0.000description1

- 239000012212insulatorSubstances0.000description1

- 238000001459lithographyMethods0.000description1

- 230000000873masking effectEffects0.000description1

- 239000000463materialSubstances0.000description1

- 239000007769metal materialSubstances0.000description1

- 238000001465metallisationMethods0.000description1

- 230000007935neutral effectEffects0.000description1

- 238000002360preparation methodMethods0.000description1

- 230000009467reductionEffects0.000description1

- 230000008439repair processEffects0.000description1

- 238000000926separation methodMethods0.000description1

- 239000000377silicon dioxideSubstances0.000description1

- 235000012239silicon dioxideNutrition0.000description1

- HQVNEWCFYHHQES-UHFFFAOYSA-Nsilicon nitrideChemical compoundN12[Si]34N5[Si]62N3[Si]51N64HQVNEWCFYHHQES-UHFFFAOYSA-N0.000description1

- 229910052814silicon oxideInorganic materials0.000description1

- 239000002210silicon-based materialSubstances0.000description1

- 238000000348solid-phase epitaxyMethods0.000description1

- 239000013589supplementSubstances0.000description1

- 230000007704transitionEffects0.000description1

Images

Classifications

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/20—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by three-dimensional arrangements, e.g. with cells on different height levels

- H10B41/23—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by three-dimensional arrangements, e.g. with cells on different height levels with source and drain on different levels, e.g. with sloping channels

- H10B41/27—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by three-dimensional arrangements, e.g. with cells on different height levels with source and drain on different levels, e.g. with sloping channels the channels comprising vertical portions, e.g. U-shaped channels

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/68—Floating-gate IGFETs

- H10D30/681—Floating-gate IGFETs having only two programming levels

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0408—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors

- G11C16/0416—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors comprising cells containing a single floating gate transistor and no select transistor, e.g. UV EPROM

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

- G11C16/14—Circuits for erasing electrically, e.g. erase voltage switching circuits

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/24—Bit-line control circuits

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/26—Sensing or reading circuits; Data output circuits

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/5222—Capacitive arrangements or effects of, or between wiring layers

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/30—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/0411—Manufacture or treatment of FETs having insulated gates [IGFET] of FETs having floating gates

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/68—Floating-gate IGFETs

- H10D30/6891—Floating-gate IGFETs characterised by the shapes, relative sizes or dispositions of the floating gate electrode

- H10D30/6892—Floating-gate IGFETs characterised by the shapes, relative sizes or dispositions of the floating gate electrode having at least one additional gate other than the floating gate and the control gate, e.g. program gate, erase gate or select gate

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/68—Floating-gate IGFETs

- H10D30/6891—Floating-gate IGFETs characterised by the shapes, relative sizes or dispositions of the floating gate electrode

- H10D30/6894—Floating-gate IGFETs characterised by the shapes, relative sizes or dispositions of the floating gate electrode having one gate at least partly in a trench

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/01—Manufacture or treatment

- H10D64/031—Manufacture or treatment of data-storage electrodes

- H10D64/035—Manufacture or treatment of data-storage electrodes comprising conductor-insulator-conductor-insulator-semiconductor structures

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2216/00—Indexing scheme relating to G11C16/00 and subgroups, for features not directly covered by these groups

- G11C2216/02—Structural aspects of erasable programmable read-only memories

- G11C2216/04—Nonvolatile memory cell provided with a separate control gate for erasing the cells, i.e. erase gate, independent of the normal read control gate

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Non-Volatile Memory (AREA)

- Semiconductor Memories (AREA)

- Electrodes Of Semiconductors (AREA)

Abstract

Description

本發明大體上係關於具有一L形浮動閘之半導體記憶體裝置,其包含(但不限於)電可程式化及可抹除非揮發性記憶體單元,有時稱為「反或(NOR)」記憶體單元。

電可程式化及可抹除非揮發性記憶體單元之大小需要不斷縮小。然而,隨著記憶體單元大小縮小,尺寸大小變化導致記憶體單元元件之間之電容耦合變化及各種臨界區域之寬度變化,除非對記憶體單元之結構作出重大設計變化,否則此等全部有可能負面影響記憶體單元之操作裕度。此外,隨著浮動閘大小縮小,一抹除浮動閘用於儲存正電荷之容量減小,除非作出設計變化來補償,否則其會導致較低信雜比(SNR)及較高錯誤率。

根據一些實施例,一種電可抹除可程式化非揮發性記憶體單元(有時稱為一NOR記憶體單元)包含一基板,其具有一汲極區域、一源極區域及該汲極區域與該源極區域之間之一通道區域。該記憶體單元進一步包含一導電控制閘,其藉由一控制閘絕緣區域來與一第一通道子區域分離。該記憶體單元進一步包含一導電L形浮動閘,其包含藉由一浮動閘絕緣區域來與一第二通道子區域分離之一第一水平部分及電連接至該第一部分之一第二垂直部分。該第二浮動閘部分自該第一浮動閘部分遠離該基板垂直延伸,且強電容耦合至自該源極區域垂直延伸之一源極線。該記憶體單元進一步包含一導電抹除閘,其安置於該浮動閘之該第二部分上方且藉由一抹除閘絕緣區域來與該浮動閘之該第二部分分離。

100:記憶體單元

100a:記憶體單元

101:記憶體單元

102:半導體基板

104:第一基板區域/汲極區域

105:基板區域/汲極區域

106:第二基板區域/源極界面區域

107:反轉層

110:PN接合界面

111:基板表面

112:第一通道部分

114:第二通道部分

120:導電控制閘

125:間隙

130:導電浮動閘

132:水平浮動閘部分/第一浮動閘部分

132a:垂直範圍

132b:水平範圍

134:垂直浮動閘部分/第二浮動閘部分

134a:垂直範圍

134b:水平範圍

136:第一端

137:第二端/尖端

138:第一尖端部分

139:第二尖端部分

140:絕緣層

150:源極線/源極區域

152:第一源極線部分

154:第二源極線部分

156:側壁區域

160:絕緣層

161:絕緣層

162:絕緣層

165:絕緣層

170:導電抹除閘

180:絕緣層

200:操作流程

210:步驟

220:步驟

230:步驟

240:步驟

305:夾止點

320:第一空乏區域

321:區域

322:第二空乏區域/深空乏區域

330:浮動閘反轉層/反轉區域

340:電子流動方向/電子流

345:場線

400:記憶體單元陣列

410:位元線

412:汲極區域

414:源極線

416:控制線

418:抹除線

420:氮化物遮罩

422:主動區域

424:隔離區域

502:矽基板

503:多晶矽層

503a:多晶矽

503b:多晶矽

504:氧化層

504a:氧化區域

504b:氧化區域

506:氮化物

508:氮化物遮罩

509:氮化物遮罩

510:溝槽底部

512:多晶矽壁/浮動閘

514:多晶矽壁/浮動閘

516:區域

518:區域

520:區域

522:區域

524:區域

526:耦合介電區域

528:耦合介電區域

530:輕微摻雜非晶矽/N-單晶矽

532:重度摻雜多晶矽/重度摻雜N+層

534:源極線

538:浮動閘尖端

539:浮動閘尖端

540:氧化層

560:HTO

562:區域

564:區域

570:抹除閘

572:控制閘

574:控制閘

580:汲極區域

582:汲極區域

584:輕微摻雜汲極區域

586:輕微摻雜汲極區域

為了更好理解各種所描述實施例,應結合以下圖式來參考以下[實施方式],其中相同元件符號係指全部圖式中之對應部件。

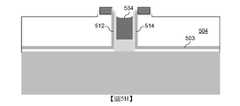

圖1A係繪示根據一些實施例之一對電可抹除可程式化非揮發性記憶體單元之一橫截面圖的一圖式。

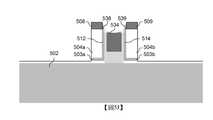

圖1B係繪示根據一些實施例之一L形浮動閘的一圖式。

圖2係繪示根據一些實施例之一電可抹除可程式化非揮發性記憶體單元之操作流程的一流程圖。

圖3係繪示根據一些實施例之一電可抹除可程式化非揮發性記憶體單元之一程式化操作的一圖式。

圖4係繪示根據一些實施例之一記憶體單元陣列之一平面圖的一圖式。

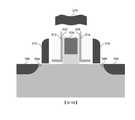

圖5A至圖5M繪示根據一些實施例之用於製造一電可抹除可程式化非揮發性記憶體單元陣列之一程序。

現將詳細參考實施例,附圖中繪示實施例之實例。在以下詳細描述中,闡述諸多特定細節以提供各種所描述實施例之一透徹理解。然而,一般技術者應明白,可在無此等特定細節的情況下實踐所描述之各種實施例。在其他例項中,未詳細描述熟知方法、程序、組件、電路及網路以免不必要地使實施例之態樣不清楚。

亦應瞭解,儘管在一些例項中,術語第一、第二等等在本文中用於描述各種元件,但此等元件不應受限於此等術語。此等術語僅用於使元件彼此區分。例如,在不背離各種所描述實例性之範疇的情況下,一第一接點可被稱為一第二接點,且類似地,一第二接點可被稱為一第一接點。第一接點及第二接點係兩個接點,但除非內文另有清楚指示,否則其等不是相同接點。

本文各種所描述實施例之描述中所用之術語僅用於描述特定實施例且不意在限制。如各種所描述實施例及隨附申請專利範圍之描述中所用,除非內文另有明確指示,否則單數形式「一」及「該」意欲亦包含複數形式。亦應瞭解,本文中所使用之術語「及/或」涉及及涵蓋相關聯列項之一或多者之任何及全部可能組合。應進一步瞭解,本說明書中所使用之術語「包含」及/或「包括」特指存在所述特徵、整體、步驟、操作、元件及/或組件,但不排除存在或新增一或多個其他特徵、整體、步驟、操作、元件、組件及/或其群組。

如本文所使用,根據內文來將術語「若」視情況解釋為意謂「當...時」或「在...之後」或「回應於判定...」或「回應於偵測到...」。類似地,根據內文來將片語「若判定...」或「若偵測到[一規定條件或事件]」視情況解釋為意謂「在判定...之後」或「根據...之一判定」或「回應於判定...」或「在偵測到[規定條件或事件]」之後」或「回應於偵測到[規定條件或事件]」。

隨著分裂閘非揮發性記憶體單元大小縮小,維持此等記憶體單元之浮動閘與源極線之間之一強電容耦合變得更有挑戰。如下文將更詳細討論,歸因於在一抹除操作期間設定抹除閘與浮動閘之間之一大初始電壓差之能力,浮動閘與源極線之間之一強電容耦合導致更有效率抹除。

此外,隨著分裂閘記憶體單元大小縮小,浮動閘與控制閘之間之一絕緣寬度減小,且維持浮動閘與控制閘之間之一弱電容耦合變得更有挑戰。歸因於維持反轉通道部分之間之一大電壓差之能力,浮動閘與控制閘之間之一弱電容耦合導致更有效率程式化,藉此促成一程式化操作期間之熱電子注入。

此外,隨著浮動閘大小縮小,一抹除浮動閘用於儲存正電荷之容量減小。一抹除浮動閘中之較少正電荷導致降低信雜比(SNR)及較高錯誤率。

因此,隨著記憶體單元大小縮小,需要維持浮動閘與源極線之間之一強電容耦合、浮動閘與控制閘之間之一弱電容耦合及浮動閘中之一高電荷儲存容量。此等方法及裝置視情況補充或替代習知方法及裝置用於程式化、抹除及讀取非揮發性記憶體單元中之資料。

此等方法及裝置藉由將一L形浮動閘之一垂直部分安置成相鄰於一垂直源極線來維持非揮發性記憶體單元之浮動閘與源極線之間之一強電容耦合。歸因於相鄰於源極線之浮動閘之部分之增大表面積,一L形浮動閘之一垂直部分提供與一相鄰源極線之極強電容耦合,其增強抹除操作期間所使用之穿隧機制,藉此提高抹除效率。此等方法及裝置藉由將一尖頭尖端(其在抹除操作期間集中電場)安置於一L形浮動閘之垂直部分之一上端處來進一步提高抹除效率。

此等方法及裝置藉由將一L形浮動閘之一水平部分安置成相鄰於控制閘來維持非揮發性記憶體單元之浮動閘與控制閘之間之一弱電容耦合。歸因於相鄰於控制閘之浮動閘之部分之減小表面積,一L形浮動閘之一水平部分提供與一相鄰控制閘之極弱電容耦合,藉此提高程式化效率。

此等方法及裝置藉由提供具有增大表面積之一L形浮動閘來維持一高浮動閘電荷儲存容量。可在一抹除模式中儲存於浮動閘上之正電荷之增加數目提高SNR,藉此導致更少讀取錯誤。

根據一些實施例,一種電可抹除可程式化非揮發性記憶體單元(有時稱為一分裂閘NOR記憶體單元)包含一基板,其具有一汲極區域、一源極區域及該汲極區域與該源極區域之間之一通道區域。該通道區域包含相鄰於該汲極區域之一第一通道子區域及相鄰於該源極區域且定位於該第一通道子區域與該源極區域之間之一第二通道子區域。該記憶體單元進一步包含藉由一控制閘絕緣區域來與該第一通道子區域分離之一導電控制閘。該記憶體單元進一步包含一導電浮動閘。該浮動閘具有藉由一浮動閘絕緣區域來與該第二通道子區域分離之一第一部分及電連接至該第一部分之一第二部分。該第二浮動閘部分自該第一浮動閘部分遠離該基板垂直延伸。該第一浮動閘部分具有相對於該基板之一第一垂直範圍且該第二浮動閘部分具有相對於該基板之一第二垂直範圍。該記憶體單元進一步包含電連接至該源極區域之一導電源極線,其遠離該基板垂直延伸且藉由一源極線絕緣區域來與該浮動閘之該第二部分分離。該記憶體單元進一步包含安置於該浮動閘之該第二部分上方且藉由一抹除閘絕緣區域來與該浮動閘之該第二部分分離之一導電抹除閘。

現將關注點轉向根據一些實施例之一電可抹除可程式化非揮發性記憶體單元(有時稱為一NOR記憶體單元或分裂閘NOR記憶體單元)之實施例。圖1A係一對記憶體單元100、101之一橫截面。記憶體單元互為鏡像,其中一記憶體單元形成於一共用源極線150之各側上且包含共用源極線150。為了簡潔起見,本發明之剩餘部分僅參考一個記憶體單元(記憶體單元100)。然而,應瞭解,相鄰記憶體單元101具有對應特徵且在類似情形下表現類似。

在一些實施例中,記憶體單元100包含具有一第一基板區域104(有時稱為一汲極區域)及一第二基板區域106(有時稱為一源極界面區域)之一半導體基板102。在一些實施例中,第一基板區域104充當一汲極,但應瞭解,可在操作期間對調一電晶體之源極及汲極。此外,在一些實施例中,汲極包含基板區域104以及基板區域105,其中區域105係比區域104淺之一摻雜區域(例如一P摻雜基板中之一中度N-摻雜區域)。基板102之源極界面區域106包括相鄰於基板102與源極線150之間之一PN接合界面110之一界面部分。在一些實施例中,界面110安置於基板102之一表面(諸如表面111)處。然而,在其他實施例中,界面110安置於表面111上方。在其他實施例中,界面110安置於基板102之表面111下方(圖中未展示)。

在一些實施例中,記憶體單元100進一步包含汲極區域104與源極界面區域106之間之一通道區域。在一些實施例中,通道區域包含相鄰於汲極區域104之一第一通道部分112及相鄰於第一通道部分112及源極界面區域106之一第二通道部分114。為了本發明之目的,「通道區域」及「通道部分」用於描述電子在特定情形中流動通過之一區域或一路經。基板102進一步包含安置於汲極區域104上方且沿一橫向方向朝向源極線150延伸之一水平表面111。

在一些實施例中,記憶體單元100進一步包含與第一通道部分112絕緣且安置於第一通道部分112上方之一導電控制閘120及與第二通道部分114絕緣且安置於第二通道部分114上方之一導電浮動閘130。在一些實施例中,浮動閘130包括一水平部分132及一垂直部分134,且一絕緣層140(有時指稱一閘極分離絕緣區域或氧化層)安置於水平部分132上方及垂直部分134與控制閘120之間。

應注意,當控制閘120安置於第一通道部分112上方時,控制閘120不安置於第二通道部分114上方。因此,當一反轉層形成於控制閘120下方時,在第一通道部分112中,歸因於一適當讀取模式控制電壓或程式化模式控制電壓加於控制閘120上,第二通道部分114之至少一部分在記憶體單元處於程式化狀態中時不包含一反轉層。換言之,儘管在一些情形中或在一些實施例中,由控制閘120在第一通道部分112中引起之反轉層可部分延伸至第二通道部分114中,但除非進一步受浮動閘130影響,否則由控制閘120引起之反轉層不延伸至第二通道之其他部分中。在一些實施例中,第二通道部分114具有15奈米至70奈米之間之一橫向尺寸,其對應於第一通道部分112與源極界面區域106之間之一距離。

圖1B繪示浮動閘130之一更詳細視圖。在一些實施例中,浮動閘130包含一第一浮動閘部分132及一第二浮動閘部分134。在一些實施例中,第一浮動閘部分132係實質上水平的(例如,平行於基板表面111或具有相對於基板表面111之不超過15°之一偏移角)。在一些實施例中,第二浮動閘部分134係實質上垂直的(例如,垂直於基板表面111或第一浮動閘部分132或具有相對於基板表面111及第一浮動閘部分132之至少一者之75°至105°之間之一偏移角)。換言之,第一浮動閘部分132及第二浮動閘部分134實質上彼此垂直(例如,相對於彼此具有不小於75°且不大於105°之一偏移角)。第一浮動閘部分132及第二浮動閘部分134交會於共用端136處以形成根據一些實施例之一L形浮動閘。

第一浮動閘部分132具有一垂直範圍132a及一水平範圍132b,而第二浮動閘部分134具有一垂直範圍134a及一水平範圍134b。在一些實施例中,垂直範圍134a比垂直範圍132a長(例如,長達垂直範圍132a之至少3倍或垂直範圍132a之3倍至10倍之間)。在一些實施例中,水平範圍132b比水平範圍134b長(例如,長達水平範圍134b之至少3倍或水平範圍134b之3倍至10倍之間)。

在一些實施例中,第二浮動閘部分134(例如由垂直範圍134a所量測)比第一浮動閘部分132(例如由水平範圍132b所量測)長。在一些實施例中,第二浮動閘部分134長達第一浮動閘部分132之至少2倍,且更明確而言,在一些實施例中,長達第一浮動閘部分132之2倍至5倍之間。然而,在其他實施例中,第一浮動閘部分132比第二浮動閘部分134長。在進一步實施例中,第一浮動閘部分132之一長度與第二浮動閘部分134之一長度相差不超過25%。

在一些實施例中,第二浮動閘部分134具有一第一端136,第二浮動閘部分134在第一端136處電連接至第一浮動閘部分132。在一些實施例中,第二浮動閘部分134具有一第二端137,其包含具有一第一尖端部分138及一第二尖端部分139之一尖端。在一些實施例中,第一尖端部分138具有小於第二尖端部分139之一橫截面。第二端137在本文中有時稱為一尖頭尖端,且第一尖端部分138之橫截面與第二尖端部分139之橫截面之比率有時用作尖頭尖端之銳度之一量測。

返回至圖1A,根據一些實施例,記憶體單元100進一步包含透過界面110電連接至源極界面區域106之一導電源極線150。源極線150沿一垂直方向(例如,沿實質上垂直於橫向方向之一方向)遠離基板延伸。在一些實施例中,源極線150包含電連接至源極界面區域106之一第一源極線部分152及安置於第一源極線部分152上方之一第二源極線部分154。在一些實施例中,第一源極線部分152經相對輕微摻雜(例如n-多晶矽),且第二源極線部分154經更重摻雜(例如n+多晶矽)。在一些實施例中,第一源極線部分152係已轉換成單晶矽之輕微摻雜多晶矽。在一些實施例中,源極線150之側壁區域156安置於源極線之一側壁部分上,該側壁部分自基板表面111開始,相鄰於第二通道部分114與源極界面區域106之交會位置,且沿源極線之側壁垂直向上延伸。

在一些實施例中,記憶體單元100進一步包含垂直浮動閘部分134之至少一部分與源極線150之至少一部分之間之絕緣層160(有時稱為一源極線絕緣區域)。在一些實施例中,絕緣層160係一「薄」介電層以提供浮動閘130與源極線150之間之一強電容耦合。在一些實施例中,絕緣層160包括具有一高介電常數之材料(例如氧化物及氮化物之一組合)。在一些實施例中,絕緣層160具有不超過10nm(或更明確而言,在一些實施例中介於6nm至10nm之間)之一組合總厚度。

在一些實施例中,記憶體單元100進一步包含與垂直浮動閘部分134之尖端137絕緣且安置於垂直浮動閘部分134之尖端137上方之一導電抹除閘170。抹除閘170藉由安置於抹除閘與垂直閘部分之間之一絕緣層180(有時稱為一抹除閘絕緣區域)來與第二浮動閘部分134絕緣。在一些實施例中,抹除閘170進一步安置於源極線150之至少一部分上方。在一些實施例中,浮動閘130與抹除閘170之間之電容耦合比浮動閘130與源極線150之間之電容耦合弱得多,此有益於有效率且快速抹除記憶體單元(下文將更詳細解釋)。在一些實施例中,浮動閘與源極線之間之電容耦合與浮動閘與抹除閘之間之電容耦合之一比率係至少5:1(即,電容耦合比係至少5:1),且在一些實施例中,浮動閘與源極線之間之電容耦合與浮動閘與抹除閘之間之電容耦合之電容耦合比係至少10:1或9:1或2:1。浮動閘與源極線之間之強電容耦合(與浮動閘與抹除閘之間之電容耦合相比)係由浮動閘與源極線之接近性以及緊密接近於源極線之垂直浮動閘部分134之垂直面之大表面積引起。

在一些實施例中,浮動閘及源極線與浮動閘及控制閘存在類似電容耦合比。更明確而言,在一些實施例中,浮動閘與源極線之間之電容耦合與浮動閘與控制閘之間之電容耦合之一比率係至少5:1(即,電容耦合比係至少5:1),且在一些實施例中,浮動閘-源極線電容耦合與浮動閘-控制閘電容耦合之電容耦合比係至少10:1或9:1或2:1。

在一些實施例中,記憶體單元100進一步包含安置於控制閘120與第一通道部分112之至少一部分之間之一絕緣層161(有時稱為一控制閘絕緣區域)。在一些實施例中,記憶體單元100進一步包含安置於水平浮動閘部分132與基板102之至少一部分(其包含第二通道部分114)之間之一絕緣層162(有時稱為一浮動閘絕緣區域)。在一些實施例中,絕緣層161及162係連接的。在一些實施例中,絕緣層162比絕緣層161厚。在一些實施例中,與一習知氧化矽層相比,絕緣層162提供待熱電子克服以注入至浮動閘130中之一較低界面能量障壁(有時稱為一能量障壁高度)。在一些實施例中,由絕緣層162之介電材料提供之低界面能量障壁小於2.5eV(電子伏特),且在一些實施例中小於2.0eV或小於1.3eV。在一些實施例中,記憶體單元100進一步包含安置於絕緣層140與控制閘120之間之一絕緣層165。在一些實施例中,絕緣層165安置於第一通道部分112及第二通道部分114交會之基板102之一區域處之基板表面111上方。

在一些實施例中,記憶體單元100之導電元件(例如控制閘120、浮動閘130、源極線150及/或抹除閘170)由適當摻雜多晶矽構成。應瞭解,「多晶矽」係指可用於形成非揮發性記憶體單元之導電元件之任何適合導電材料,其至少部分由矽或金屬材料形成。另外,根據一些實施例,記憶體單元100之絕緣元件(例如絕緣層140及180)由二氧化矽、氮化矽及/或可用於形成非揮發性記憶體單元之絕緣元件之任何適當絕緣體構成。

現將關注記憶體單元100之通道部分。在一些實施例中,第一通道部分112及第二通道部分114形成沿橫向方向自汲極區域104/105延伸至源極界面區域106之一連續通道區域。另外,第一通道部分112及第二通道部分114沿垂直方向延伸以包含基板表面111。在一些實施例中,第一通道部分112及第二通道部分114彼此相鄰或彼此重疊,且在一些實施例中,第一通道部分112與汲極區域104/105重疊。

現將描述根據一些實施例之記憶體單元100之操作。圖2係繪示根據一些實施例之一記憶體單元100之一操作流程200的一流程圖。操作流程200開始於步驟210,其中一記憶體控制器著手抹除記憶體單元100(例如,同時抹除包含記憶體單元100之一列記憶體單元)(步驟220)、程式化先前被抹除之一記憶體單元100(步驟230)或自先前被程式化或抹除之一記憶體單元讀取(步驟240)。在一些實施例中,操作流程200包含對不同記憶體單元之同時抹除及程式化操作,且在一些實施例中,操作流程200包含對不同記憶體單元之同時抹除及讀取操作。

抹除操作

為抹除根據一些實施例之記憶體單元(步驟220),將一第一偏壓電位(例如接地電位)施加至控制閘120及源極線150兩者,且將一第二偏壓電位(例如一正電位)施加至抹除閘170。通常,第二偏壓電位與第一偏壓電位之間之一差不大於10伏特。由於浮動閘130高度電容耦合至源極線150,所以浮動閘電位被下拉至或保持於僅高於接地電位(本文中亦簡稱「接地」或「電路接地」)之一電位。作為一非限制性實例,針對10/1之一電容比(即,浮動閘至源極線電容係浮動閘至抹除閘之10倍),若抹除閘電位自0V變成10V(例如,用於開始一抹除操作)且源極線電位維持為0V,則抹除閘中之10V電位變化引起小於1V之一浮動閘電位變化。

浮動閘與抹除閘之間之電位差引起電子離開浮動閘。更明確而言,透過福勒-諾德海姆(Fowler-Nordheim)穿隧(或一等效穿隧機制)誘發浮動閘130上之電子自垂直浮動閘部分134(主要來自尖頭尖端137)通過絕緣層180而穿隧至抹除閘170上以使浮動閘130保持帶正電。藉由尖端137之銳度來增強電子自浮動閘130之尖端137通過絕緣層180至抹除閘170之穿隧。儘管傳統記憶體單元可需要14V或更高電壓用於抹除,但當前所揭示實施例需要將不超過10V施加至抹除閘170(例如,相對於施加至控制閘120及源極線150之電壓,施加至抹除閘170之電壓不超過+10V),且在一些實施例甚至更低(例如8V)。除電容比之外,垂直浮動閘部分134之尖頭尖端137亦促成較低抹除電壓。特定而言,浮動閘130之尖頭尖端137促進在浮動閘130與抹除閘170之間形成一緊密集中電場,其繼而促進電子穿隧通過絕緣層180,藉此允許針對絕緣層180之任何給定厚度使用較低抹除電壓。例如,若無一尖頭尖端之一平面浮動閘通常需要小於100埃之一絕緣厚度(層180),則具有一尖頭尖端137允許絕緣厚度在將僅10V施加至抹除閘時高達700埃且仍容許穿隧。

程式化操作

為程式化根據一些實施例之記憶體單元(步驟230),首先將關注點轉至圖3,其繪示一程式化操作期間之來自圖1A之記憶體單元100之另一視圖(100a)。與圖1A至圖1B共用之構件標有類似元件符號,且為了簡潔而不進一步討論一些構件。圖3中所描繪之額外構件包含一弱反轉層107、一第一空乏區域320、一第二空乏區域322、一浮動閘反轉層330、一電子流動方向340及由場線345表示之一電場(例如,在浮動閘反轉層330與反轉層107之間之通道區域中)。如此項技術中所知,電子被吸引至正電壓電位且因此沿與圖3中所描繪之電場線345相反之一方向牽引。

為程式化根據一些實施例之記憶體單元,將第一偏壓電位(例如接地電位)施加至抹除閘170,且將一第五偏壓電位(例如一低電壓,諸如0V或0V至0.5V之間之一電壓)施加至汲極區域104/105。將接近MOS結構之臨限電壓之一正電壓位準(例如約0.2V至約0.7V,其高於汲極區域之電壓電位)施加至控制閘120。施加至汲極區域104/105及控制閘120之電壓形成基板102之汲極區域104/105及通道部分112(圖1A)周圍之一第一空乏區域320。此外,將高於第五偏壓電位之一第六偏壓電位施加至控制閘120,且將高於第六偏壓電位之一第七偏壓電位(例如一正高電壓,例如約4V至約6V)施加至源極線150。

施加至控制閘120之第六偏壓電位引起一弱反轉層107形成於基板102中,連接至汲極區域104/105,且具有定位於控制閘120下方之一夾止點305。反轉層107具有接近於汲極區域104/105之電壓之一電壓,此係因為汲極區域與夾止點305之間之極低次臨限電流僅引起汲極區域與夾止點305之間之一極小電壓降。

將第七偏壓電位(如上文所提及,一正高電壓,例如約4V至約6V)施加至源極線150引起浮動閘130之一電壓歸因於源極線與浮動閘之間之電容耦合而根據第七偏壓電位升高,藉此引起基板之一通道區域中之電子獲得能量且注入至浮動閘上。由於浮動閘130高度電容耦合至源極線150,所以源極線150上之(例如)自0V至4V之電壓轉變引起浮動閘130之電壓與源極線150上之電壓增大成比例地增大。例如,在一些實施例中,浮動閘130之電壓增大源極線150上之電壓變化之至少80%。浮動閘130上之所得電壓(例如,歸因於浮動閘130先前已被抹除及歸因於與源極線150之電容耦合之電壓增大)與源極線150上之高電壓一起形成浮動閘130及源極線150下方之基板102中之一第二空乏區域322(本文中有時指稱一深空乏區域)。歸因於浮動閘130及源極線150上之相對較高電壓,深空乏區域322具有大於空乏區域320之一空乏寬度。較大空乏區域322推動夾止點305朝向汲極區域104/105以引起反轉層107夾止於控制閘120下方。浮動閘130上之正電荷(例如,歸因於浮動閘130先前已被抹除)與源極線150上之高電壓進一步一起形成浮動閘130下方之通道部分114及源極線150下方之源極界面區域106中之一反轉層330(參閱圖1A之通道部分114及源極界面區域106)。反轉層330具有接近於源極線之電壓之一電壓,其實質上高於反轉層107(其具有接近於汲極區域之電壓之一電壓)之電壓。反轉層330與107之間之此電壓差引起反轉層330與反轉層107之間之一電壓降。電壓降發生於空乏區域322中,鄰近於空乏區域320及322交會之位置(圖3中指示為321)。歸因於電壓降之所得電場由場線345表示(圖3)。區域321處之空乏區域322之面積受控制閘120與水平浮動閘部分132之間之間隙125之一大小影響。明確而言,在一些實施例中,由於較大空乏區域322推動夾止點305朝向汲極區域104/105以引起反轉層107在到達間隙125之前夾止,所以反轉層107與330之間之空乏區域322之面積比間隙125寬且直接與間隙125之大小相關。

在一程式化操作開始時,來自汲極區域104/105之一電子流(有時稱為程式化電流)流動通過反轉層107,其隨機移動但具有沿由電子流340表示之方向之一淨漂移速度。電子橫穿反轉層107且前進至夾止點305。在離開夾止點305之後,程式化電流中之電子因由場線345表示之電場而沿電子流340之方向加速通過空乏區域322。加速電子在本文中指稱熱電子。

隨著程式化電流中之熱電子通過空乏區域322而朝向反轉層330行進,一些熱電子因與基板中之雜質或晶格缺陷之碰撞而散射。具有足夠能量及動能之一些散射熱電子繼續擊穿基板表面111而進入定位於水平浮動閘部分132與基板表面111之間之絕緣層162。在一些實施例中,當電子能量高於基板102之矽與絕緣層162之介電材料之間之界面處之能量障壁高度時,電子具有足夠能量來進入絕緣層162。在闖入絕緣層162之後,將電子注入至浮動閘130上。

橫穿空乏區域322但不具有足夠能量來擊穿表面111之電子繼續通過反轉層330而至源極線150。在一些實施例中,一低電阻累積層形成於源極線150之側壁區域156中以形成使電子(例如未擊穿表面111之電子)流動至源極線150之較高部分之一連續路徑。

電子至浮動閘130上之注入(本文中有時稱為閘極電流)持續至源極線150及控制閘120上之程式化電壓被移除或浮動閘130上之電壓因注入至浮動閘130上之電子而降低使得反轉層330弱化至其無法再傳送源極線電壓至間隙125之點,以引起電子流340中之電子不再具有足夠能量來橫穿絕緣層162。換言之,浮動閘之降低電壓無法再支持空乏區域322之電位降產生熱電子。此時,達到記憶體單元之一「程式化狀態」。在一些實施例中,一程式化操作期間之程式化電流係在100nA至10mA之範圍內,且在一些實施例中,在不到100奈秒內達到程式化狀態。在一些實施例中,程式化具有防止單元變得「過度」程式化之一自限機制。此係有益的,因為在抹除操作期間自單元移除過量電子增加單元之耗損。

讀取操作

最後,為讀取根據一些實施例之一選定記憶體單元(步驟240),將第一偏壓電位(例如一接地電位)施加至源極線150。將一第四偏壓電位(例如一讀取電壓,諸如0.5V至2V之範圍內之一電壓)施加至汲極區域104,且將一第三偏壓電位(有時稱為讀取電位)(例如一正電壓,例如約1V至約4V,取決於由其中製造裝置之技術支援之電源供應電壓)施加至控制閘120。

若浮動閘130帶正電(例如,浮動閘(例如)由於記憶體單元100已被抹除且隨後未被程式化而釋放電子),則藉由形成一反轉層330來接通第二通道部分114。當將控制閘120升高至讀取電位時,藉由在控制閘下方之基板區域中形成一強反轉層107來接通第一通道部分112。在第二通道部分中,兩個空乏區域與自汲極區域104/105指向浮動閘130下方之反轉區域330之基板表面111下方之一電場重疊。因此,整個通道區域(其包含通道部分112及114)促成沿汲極區域104/105之方向之一電子流。因此,電子自源極線150(例如,自側壁156)通過通道部分114中之反轉層330、空乏區域322及通道部分112中之反轉層107而流動至汲極區域104/105。當使用記憶體裝置中之電路(圖中未展示)來感測所得電流(有時稱為讀取電流)時,感測到記憶體單元處於「1」狀態或等效「抹除」狀態中。

另一方面,若浮動閘130呈中性或帶負電,則無反轉層形成於第二通道部分114中。因此,弱接通或完全切斷第二通道部分114且相較於浮動閘130帶正電(例如,由於一抹除操作)時之空乏區域322之寬度而減小空乏區域322之寬度。此外,空乏區域322之減小寬度引起空乏區域322及320不再重疊。歸因於空乏區域中之間隙,第二通道部分114之至少一部分不在一空乏區域中。因此,即使將控制閘120及汲極區域104升高至讀取電位,但極少或無電流(有時稱為讀取電流)流動於源極線150與汲極區域104之間。在此情況中,讀取電流比「1」狀態之讀取電流小很多或完全無讀取電流。依此方式,感測到記憶體單元處於「0」狀態或等效「程式化」狀態中。

在一些實施例中,針對非選定行及列將一接地電位施加至汲極區域104、源極區域150及控制閘120以僅讀取(若干)選定記憶體單元。

記憶體陣列之平面圖

現將關注點轉至圖4,其繪示根據一些實施例之一記憶體單元陣列400之一平面圖。在一些實施例中,位元線410與汲極區域412互連。控制線416及氮化物遮罩420(在製程中被移除)界定源極線、水平浮動閘及控制閘且延伸橫跨主動區域422及隔離區域424兩者。源極線414電連接至成對記憶體單元之各列之源極區域。浮動閘安置於抹除線418下方之主動區域422中之溝槽中。

製程

現將關注點轉至圖5A至圖5M,其繪示根據一些實施例之用於製造一記憶體單元之一程序。根據一些實施例之一程序開始於圖5A,其展示矽基板502、多晶矽層503及氧化層504之一橫截面圖,氮化物506沈積於氧化層504上方。已自基板502移除數個隔離溝槽,且圖5A之右手部分展示準備用於形成記憶體單元之一區域(其具有氧化層504)。圖5B係沿位元線方向(參閱圖4)之另一橫截面圖,其正交於圖5A之橫截面圖。接著,如圖5C中所繪示,蝕刻氮化層506以留下具有部分508及509之氮化物遮罩。

接著,如圖5D中所繪示,在氮化物遮罩部分508與509之間蝕刻穿過氧化層504以停止於多晶矽層503處之一溝槽。在一些實施例中,藉由反應性離子蝕刻(「RIE」)來執行蝕刻。在蝕刻之後,將多晶矽(本文中有時稱為「多晶」)沈積於溝槽中及溝槽周圍。接著,使用RIE來自溝槽底部510蝕刻多晶矽以留下兩個垂直多晶矽壁512及514。多晶矽壁512及514形成兩個L形浮動閘(例如包括多晶矽512/503a之一浮動閘及包括多晶矽514/503b之另一浮動閘)之基礎。接著,如圖5E中所繪示,在浮動閘分離、遮罩及蝕刻之處理步驟之後,自區域516及518各向同性蝕刻剩餘多晶矽。接著,如圖5F中所繪示,沈積一介電層且接著使用RIE來各向異性蝕刻介電層以形成耦合介電區域526及528。在此等處理步驟之後蝕除區域520、522及524之氧化物。

接著,如圖5G中所繪示,為形成根據一些實施例之一源極線534(參閱圖5H),首先沈積輕微摻雜非晶矽530且接著使用一固相磊晶(「SPE」)程序來將輕微摻雜非晶矽530轉換成單晶矽。接著,植入及熱驅入一N型摻雜劑(例如砷或磷)以在溝槽中之輕微摻雜矽上方形成一重度摻雜N+層532。接著,執行一各向同性多晶矽蝕刻以移除溝槽外之過量矽(如圖5H中所展示)來形成源極線534之頂部。在其他實施例中,圖5G及圖5H中之處理步驟完成如下:藉由首先執行一磊晶矽生長步驟以在溝槽底部處選擇性地生長N-單晶矽530,接著沈積重度摻雜多晶矽532來形成層530及532。各向同性蝕除溝槽外之過量多晶矽532以形成源極線534之頂部。如自如何形成源極線534之描述可見,源極線534及垂直多晶矽壁512(其將變成浮動閘130之垂直部分(參閱圖1A))歸因於使用垂直多晶矽壁512、514及耦合介電區域526及528(參閱圖5F)來界定源極線534之垂直邊界而自對準。換言之,垂直浮動閘部分不是沿垂直於源極線方向(參閱平面圖(圖4)中之源極線方向)之方向微影界定,而是可在不影響記憶體單元電特性的情況下進一步容忍源極線方向之微影失準。

接著,如圖5I中所繪示,自氮化物遮罩部分508及509之頂部及側移除氧化物之一控制量,同時暴露氧化物覆蓋浮動閘512、514之尖端部分538、539。接著,熱生長一薄氧化層540以保護浮動閘尖端538、539及源極線矽之頂部。此熱氧化層540生長步驟亦銳化浮動閘512、514之尖端538、539。

接著,如圖5J中所繪示,使用RIE來蝕刻氧化層504及多晶矽層503(參閱圖5I)。在蝕刻期間,氮化物遮罩508、509及另一遮罩(圖中未展示)保護浮動閘尖端538、539及源極線534。氧化區域504a及504b在蝕刻之後保留。在一些實施例中,調節RIE蝕刻條件以最小化對矽502造成之損壞。接著,如圖5K中所繪示,在矽表面503上方生長一薄氧化層(圖中未展示)以修復由用於蝕刻氧化層504之RIE程序對矽表面造成之損壞。在一些實施例中,氧化亦進一步銳化浮動閘之尖端。接著,自氧化區域504a及504b之頂部剝離氮化物。接著,如圖5L中所繪示,將HTO 560沈積於記憶體單元區域上方以充當一穿隧介電質。在一些實施例中,HTO之一厚度係100埃至300埃。在其他實施例中,HTO之一厚度高達700埃。在一些實施例中,使用一遮罩來保護浮動閘尖端,且各向同性蝕刻HTO 560以(例如)沿氧化區域504a、504b之側壁移除過量氧化物。在一些實施例中,各向異性蝕刻氧化物以自區域562及564移除氧化物來準備形成控制閘。接著,在區域562及564上方生長閘極氧化物且沈積多晶矽以覆蓋包含區域562及564中之閘極氧化物之整個記憶體陣列區域。接著,遮罩及蝕刻多晶矽以形成控制閘572、574,如圖5M中所展示。在一些實施例中,亦使用用於形成控制閘572、574之相同遮罩及蝕刻步驟來界定抹除閘570,而在其他實施例中,使用區別於形成控制閘572、574之遮罩及蝕刻步驟之遮罩及蝕刻步驟來形成抹除閘570。

最後,使用半導體產業中已熟知之處理步驟來形成輕微摻雜汲極區域584、586(例如相鄰於控制閘572、574之汲極區域)及汲極區域580、582以形成包含相鄰於鄰近電晶體閘極之輕微摻雜汲極(LDD)子區域及不相鄰於鄰近電晶體閘極之重度摻雜汲極子區域之汲極區域(美國專利4,994,404中描述其等之一實例),接著形成接點及進行後續金屬化及其他步驟以完成裝置製造。

已為了解釋而參考特定實施例來描述以上描述。然而,以上繪示性討論不意欲具窮舉性或使本發明受限於所揭示之精確形式。可鑑於以上教示進行諸多修改及變動。選擇及描述實施例以最佳解釋本發明之原理及其實際應用以藉此使熟悉技術者能夠最佳利用本發明及各種實施例以及適合於特定考量用途之各種修改。

100:記憶體單元

101:記憶體單元

102:半導體基板

104:第一基板區域/汲極區域

105:基板區域/汲極區域

106:第二基板區域/源極界面區域

110:PN接合界面

111:基板表面

112:第一通道部分

114:第二通道部分

120:導電控制閘

130:導電浮動閘

132:水平浮動閘部分/第一浮動閘部分

134:垂直浮動閘部分/第二浮動閘部分

137:第二端/尖端

140:絕緣層

150:源極線/源極區域

152:第一源極線部分

154:第二源極線部分

156:側壁區域

160:絕緣層

161:絕緣層

162:絕緣層

165:絕緣層

170:導電抹除閘

180:絕緣層

Claims (19)

- 一種電可抹除可程式化記憶體單元,其包括:一半導體基板,其具有一第一基板區域及沿一橫向方向與該第一基板區域隔開之一第二基板區域;一通道區域,其介於該第一基板區域與該第二基板區域之間,該通道區域具有:一第一通道部分,其相鄰於該第一基板區域,及一第二通道部分,其相鄰於該第二基板區域及該第一通道部分;一導電控制閘,其與該第一通道部分絕緣且安置於該第一通道部分上方;一導電浮動閘,其與該第二通道部分絕緣且安置於該第二通道部分上方,該浮動閘具有:一第一浮動閘部分,其在該第二通道部分上方沿該橫向方向延伸,及一第二浮動閘部分,其遠離該基板延伸,該第二浮動閘部分在一第一端上電連接至該第一浮動閘部分且在一第二端上具有一尖端,其中該尖端之一第一部分具有小於該尖端之一第二部分之一橫截面;一導電源極線,其電耦合至該第二基板區域,該源極線遠離該基板延伸且與該浮動閘形成一第一電容耦合;一介電層,其包含定位介於該第二浮動閘部分與該源極線之間且與該第二浮動閘部分與該源極線接觸之一部分;及一導電抹除閘,其與該源極線及該第二浮動閘部分之該尖端絕緣且安置於該源極線及該第二浮動閘部分之該尖端上方;其中該第一浮動閘部分包含一部份,該部分在該第二通道部分上方自該源極線延伸超過該第二浮動閘部分。

- 如請求項1之電可抹除可程式化記憶體單元,其中該第一浮動閘部分及該第二浮動閘部分形成一L形浮動閘。

- 如請求項1之電可抹除可程式化記憶體單元,其中該抹除閘與該浮動閘形成一第二電容耦合,且其中該第一電容耦合大於該第二電容耦合。

- 如請求項3之電可抹除可程式化記憶體單元,其中該第一電容耦合與該第二電容耦合之一比率係至少5:1。

- 如請求項1之電可抹除可程式化記憶體單元,其中該控制閘與該浮動閘形成一第三電容耦合,且其中該第一電容耦合大於該第三電容耦合。

- 如請求項5之電可抹除可程式化記憶體單元,其中該第一電容耦合與該第三電容耦合之一比率係至少5:1。

- 如請求項1至6中任一項之電可抹除可程式化記憶體單元,其進一步包括:一控制閘絕緣區域,其安置於該控制閘與該第一通道部分之間;及一浮動閘絕緣區域,其安置於該第一浮動閘部分與該第二通道部分之間。

- 如請求項7之電可抹除可程式化記憶體單元,其中該浮動閘絕緣區域比該控制閘絕緣區域厚。

- 如請求項7之電可抹除可程式化記憶體單元,其中使用單獨絕緣區域生長操作來形成該浮動閘絕緣區域及該控制閘絕緣區域。

- 如請求項1至6中任一項之電可抹除可程式化記憶體單元,其進一步包括:一抹除閘絕緣區域,其安置於該抹除閘與該第二浮動閘部分之該尖端之間,該抹除閘絕緣區域具有容許電子自該第二浮動閘部分之該尖端穿隧之一厚度。

- 如請求項10之電可抹除可程式化記憶體單元,其中該抹除閘絕緣區域厚度大於200埃且容許電子在將不超過10V施加至該抹除閘之後穿隧。

- 如請求項1至6中任一項之電可抹除可程式化記憶體單元,其中該控制閘包括安置於與該第一浮動閘部分之一第一距離處之一第一區域及安置於與該第二浮動閘部分之一第二距離處之一第二區域,其中該第二距離大於該第一距離。

- 如請求項1至6中任一項之電可抹除可程式化記憶體單元,其進一步包括安置於該第一浮動閘部分上方且相鄰於該第二浮動閘部分之氧化層。

- 如請求項1至6中任一項之電可抹除可程式化記憶體單元,其中不沿垂直於一源極線方向之一方向微影界定該第二浮動閘部分。

- 一種電可程式化及可抹除非揮發性記憶體單元,其包括:一基板,其具有一汲極區域、一源極區域、該汲極區域與該源極區域之間之一通道區域及一上表面;該通道區域包含相鄰於該汲極區域之一第一通道子區域及相鄰於該源極區域且定位於該第一通道子區域與該源極區域之間之一第二通道子區域;一導電控制閘,其藉由一控制閘絕緣區域來與該第一通道子區域分離;及一導電浮動閘,其具有藉由一浮動閘絕緣區域來與該第二通道子區域分離且安置在該基板之該上表面上方之一第一部分及電耦合至該第一部分且自該第一部分遠離該基板之該上表面垂直延伸且安置在該基板之該上表面上方之一第二部分,其中該浮動閘之該第一部分具有相對於該基板之該上表面之一第一垂直範圍且該浮動閘之該第二部分具有相對於該基板之一第二垂直範圍,該第二垂直範圍係相對於該基板之該上表面之該浮動閘之該第一部分之該第一垂直範圍之至少兩倍;一導電源極線,其電耦合至該源極區域,遠離該基板垂直延伸,且藉由一源極線絕緣區域來與該浮動閘之該第二部分分離,使用一第一電容耦合來將該浮動閘電容耦合至該源極線;其中該浮動閘之該第一部分包含一部分,該部分在該基板之該上表面上方自該源極線延伸超過該浮動閘之該第二部分;及一導電抹除閘,其安置於該浮動閘之該第二部分上方且藉由一抹除閘絕緣區域來與該浮動閘之該第二部分分離。

- 一種操作一記憶體單元之方法,該記憶體單元包括:一半導體基板;一控制閘;一浮動閘,其安置在該基板之一上表面上方,該浮動閘具有平行於該基板延伸之一第一浮動閘部分及遠離該基板延伸之一第二浮動閘部分,該第二浮動閘部分在一第一端上電連接至該第一浮動閘部分且在一第二端上具有一尖端;一源極線,其藉由一介電層電容耦合至該第二浮動閘部分,該介電層包含定位介於該第二浮動閘部分與該源極線之間且與該第二浮動閘部分與該源極線接觸之一部分;及一抹除閘,其與該第二浮動閘部分之該尖端絕緣且安置於該第二浮動閘部分之該尖端上方;其中該第一浮動閘部分包含一部分,該部分在該基板上方自該源極線延伸超過該第二浮動閘部分;該方法包括:藉由以下操作來抹除該記憶體單元:將一第一偏壓電位施加至該控制閘及該源極線;及將一第二偏壓電位施加至該抹除閘以誘發電子自該第二浮動閘部分之該尖端穿隧至該抹除閘,其中該浮動閘與該源極線之間之一電容耦合實質上限制由該浮動閘與該抹除閘之間之電容耦合引起之該浮動閘之電位變化;其中該第二偏壓電位與該第一偏壓電位之間之一差不大於10伏特。

- 如請求項16之方法,其進一步包括:在抹除該記憶體單元之後,藉由以下操作來讀取該記憶體單元:將該第一偏壓電位施加至該源極線;將一第三偏壓電位施加至該控制閘以引起在該控制閘下方之一基板區域中形成一反轉層;將一第四偏壓電位施加至該基板之一汲極區域以引起高於一臨限值之一電流在該浮動閘處於一預定抹除狀態中時自該汲極區域流動至該源極線;及感測自該汲極區域流動至該源極線之該電流(若存在)。

- 如請求項16至17中任一項之方法,其進一步包括:在抹除該記憶體單元之後,藉由以下操作來程式化該記憶體單元:將該第一偏壓電位施加至該抹除閘;及將一第五偏壓電位施加至該基板之一汲極區域;將高於該第五偏壓電位之一第六偏壓電位施加至該控制閘;及將高於該第六偏壓電位之一第七偏壓電位施加至該源極線以引起該浮動閘之一電壓歸因於該源極線與該浮動閘之間之電容耦合而根據該第七偏壓電位升高且藉此引起該基板之一通道區域中之若干電子獲得能量而注入至該浮動閘上。

- 如請求項18之方法,其中注入至該浮動閘上之該等電子引起該記憶體單元在不到100奈秒內達到一程式化狀態。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201762559414P | 2017-09-15 | 2017-09-15 | |

| US62/559,414 | 2017-09-15 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| TW201916331A TW201916331A (zh) | 2019-04-16 |

| TWI741204Btrue TWI741204B (zh) | 2021-10-01 |

Family

ID=65720743

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| TW107127198ATWI741204B (zh) | 2017-09-15 | 2018-08-06 | 電可抹除可程式化記憶體單元、電可程式化及可抹除非揮發性記憶體單元及操作記憶體單元之方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US10756100B2 (zh) |

| JP (1) | JP2020534672A (zh) |

| KR (1) | KR102388308B1 (zh) |

| CN (1) | CN111183507B (zh) |

| TW (1) | TWI741204B (zh) |

| WO (1) | WO2019055297A1 (zh) |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI742299B (zh)* | 2017-09-15 | 2021-10-11 | 美商綠芯智慧財產有限責任公司 | 電可抹除可程式化非揮發性記憶體單元及操作記憶體單元之方法 |

| CN110739312B (zh)* | 2018-07-19 | 2021-05-14 | 合肥晶合集成电路股份有限公司 | 分栅式非易失性存储器及其制备方法 |

| CN111341776B (zh)* | 2020-03-18 | 2023-11-14 | 上海华虹宏力半导体制造有限公司 | 存储器及其形成方法、存储器单元阵列及其驱动方法 |

| IT202000011548A1 (it) | 2020-05-19 | 2021-11-19 | Ennio Calabria | Elemento posizionatore sotto-gengivale doppio |

| CN113594167B (zh)* | 2021-07-29 | 2024-03-12 | 上海集成电路制造创新中心有限公司 | 非易失性可编程异质结存储器 |

| CN114122138A (zh)* | 2021-11-09 | 2022-03-01 | 上海集成电路制造创新中心有限公司 | 薄膜晶体管存储器及其制备方法 |

| CN114121994B (zh)* | 2021-11-30 | 2025-02-14 | 上海华虹宏力半导体制造有限公司 | 镜像位sonos闪存单元及其制造方法 |

| CN114156273A (zh)* | 2021-12-09 | 2022-03-08 | 华虹半导体(无锡)有限公司 | 一种浮栅型分栅闪存器件的制备方法及器件 |

| CN114709215A (zh)* | 2022-04-29 | 2022-07-05 | 上海华虹宏力半导体制造有限公司 | 存储器及存储器的形成方法 |

| CN117998852A (zh)* | 2022-10-28 | 2024-05-07 | 上海华力微电子有限公司 | 超级闪存及其制造方法 |

| CN118434137B (zh)* | 2024-04-26 | 2025-02-11 | 浙江大学 | 一种非易失性1.5t浮栅型flash存储器 |

| CN118946148B (zh)* | 2024-10-14 | 2025-03-11 | 合肥晶合集成电路股份有限公司 | 多次可编程器件及其制造方法 |

| CN120358781A (zh)* | 2025-06-23 | 2025-07-22 | 杭州谱析光晶半导体科技有限公司 | 一种集成沟道二极管SiC MOSFET器件及制备方法 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20050045940A1 (en)* | 2003-08-28 | 2005-03-03 | Bomy Chen | Self-aligned method of forming a semiconductor memory array of floating gate memory cells with buried floating gate, and a memory array made thereby |

| US20070262368A1 (en)* | 2006-04-20 | 2007-11-15 | Ko-Hsing Chang | Non-volatile memory and manufacturing method thereof |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4994404A (en) | 1989-08-28 | 1991-02-19 | Motorola, Inc. | Method for forming a lightly-doped drain (LDD) structure in a semiconductor device |

| TW445649B (en) | 1999-06-09 | 2001-07-11 | Sanyo Electric Co | Semiconductor memory and method for operating a semiconductor memory |

| JP2001085544A (ja)* | 1999-09-14 | 2001-03-30 | Sanyo Electric Co Ltd | スプリットゲート型メモリセル |

| EP1107317B1 (en)* | 1999-12-09 | 2007-07-25 | Hitachi Europe Limited | Memory device |

| JP2001284473A (ja)* | 2000-03-28 | 2001-10-12 | Sanyo Electric Co Ltd | 不揮発性半導体メモリ |

| US6891220B2 (en)* | 2002-04-05 | 2005-05-10 | Silicon Storage Technology, Inc. | Method of programming electrons onto a floating gate of a non-volatile memory cell |

| US7358134B2 (en)* | 2003-09-15 | 2008-04-15 | Powerchip Semiconductor Corp. | Split gate flash memory cell and manufacturing method thereof |

| US7129536B2 (en) | 2004-09-02 | 2006-10-31 | Silicon Storage Technology, Inc. | Non-planar non-volatile memory cell with an erase gate, an array therefor, and a method of making same |

| US20060157773A1 (en)* | 2005-01-14 | 2006-07-20 | Yu Andy T | Non-volatile electrically alterable memory cell for storing multiple data and manufacturing thereof |

| US7312490B2 (en)* | 2005-03-31 | 2007-12-25 | Intel Corporation | Vertical memory device and method |

| US7755132B2 (en)* | 2006-08-16 | 2010-07-13 | Sandisk Corporation | Nonvolatile memories with shaped floating gates |

| CN101419972B (zh) | 2008-11-13 | 2012-12-12 | 上海宏力半导体制造有限公司 | 高效擦写的分栅闪存 |

| US9293204B2 (en)* | 2013-04-16 | 2016-03-22 | Silicon Storage Technology, Inc. | Non-volatile memory cell with self aligned floating and erase gates, and method of making same |

| US20150179749A1 (en)* | 2013-12-19 | 2015-06-25 | Silicon Storage Technology, Inc | Non-volatile Memory Cell With Self Aligned Floating And Erase Gates, And Method Of Making Same |

| TWI742299B (zh)* | 2017-09-15 | 2021-10-11 | 美商綠芯智慧財產有限責任公司 | 電可抹除可程式化非揮發性記憶體單元及操作記憶體單元之方法 |

- 2018

- 2018-08-06TWTW107127198Apatent/TWI741204B/zhactive

- 2018-09-05USUS16/122,795patent/US10756100B2/enactiveActive

- 2018-09-07JPJP2020508343Apatent/JP2020534672A/jaactivePending

- 2018-09-07WOPCT/US2018/049875patent/WO2019055297A1/ennot_activeCeased

- 2018-09-07KRKR1020207010618Apatent/KR102388308B1/koactiveActive

- 2018-09-07CNCN201880058769.5Apatent/CN111183507B/zhactiveActive

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20050045940A1 (en)* | 2003-08-28 | 2005-03-03 | Bomy Chen | Self-aligned method of forming a semiconductor memory array of floating gate memory cells with buried floating gate, and a memory array made thereby |

| US20070262368A1 (en)* | 2006-04-20 | 2007-11-15 | Ko-Hsing Chang | Non-volatile memory and manufacturing method thereof |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20200047715A (ko) | 2020-05-07 |

| US20190088667A1 (en) | 2019-03-21 |

| US10756100B2 (en) | 2020-08-25 |

| CN111183507B (zh) | 2023-10-31 |

| KR102388308B1 (ko) | 2022-04-18 |

| TW201916331A (zh) | 2019-04-16 |

| JP2020534672A (ja) | 2020-11-26 |

| CN111183507A (zh) | 2020-05-19 |

| WO2019055297A1 (en) | 2019-03-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TWI741204B (zh) | 電可抹除可程式化記憶體單元、電可程式化及可抹除非揮發性記憶體單元及操作記憶體單元之方法 | |

| TWI742299B (zh) | 電可抹除可程式化非揮發性記憶體單元及操作記憶體單元之方法 | |

| US7315057B2 (en) | Split gate non-volatile memory devices and methods of forming same | |

| CN1677675B (zh) | 非易失性半导体存储器件 | |

| US6972997B2 (en) | Nonvolatile semiconductor memory device | |

| JP5761866B2 (ja) | スプリットゲート不揮発性メモリセルの作製に有用な半導体構造を形成する方法 | |

| KR101632124B1 (ko) | 그들 사이에 향상된 커플링 비율을 갖는 커플링 게이트 및 플로팅 게이트를 구비하는 비휘발성 메모리 셀 | |

| US11081557B2 (en) | Memory and method for forming the same | |

| US20150179749A1 (en) | Non-volatile Memory Cell With Self Aligned Floating And Erase Gates, And Method Of Making Same | |

| US8633080B2 (en) | Methods of making multi-state non-volatile memory cells | |

| JP2008047726A (ja) | スプリットゲート型不揮発性メモリとその製造方法 | |

| KR100448912B1 (ko) | 반도체 메모리 소자 구조 및 그 제조 방법 | |

| US20160126250A1 (en) | Charge-trapping memory device | |

| JP2014160846A (ja) | 半導体記憶装置 |