TWI728916B - 電子裝置 - Google Patents

電子裝置Download PDFInfo

- Publication number

- TWI728916B TWI728916BTW109132018ATW109132018ATWI728916BTW I728916 BTWI728916 BTW I728916BTW 109132018 ATW109132018 ATW 109132018ATW 109132018 ATW109132018 ATW 109132018ATW I728916 BTWI728916 BTW I728916B

- Authority

- TW

- Taiwan

- Prior art keywords

- electrode

- gate

- contact holes

- electronic device

- minimum distance

- Prior art date

Links

- 239000004065semiconductorSubstances0.000claimsabstractdescription49

- 239000000758substrateSubstances0.000claimsabstractdescription21

- 239000010410layerSubstances0.000description102

- 208000022859zygodactyly type 1Diseases0.000description25

- 208000018670synpolydactyly type 1Diseases0.000description17

- 239000000463materialSubstances0.000description7

- 239000000470constituentSubstances0.000description6

- 229910052751metalInorganic materials0.000description5

- 239000002184metalSubstances0.000description5

- XLOMVQKBTHCTTD-UHFFFAOYSA-NZinc monoxideChemical compound[Zn]=OXLOMVQKBTHCTTD-UHFFFAOYSA-N0.000description4

- 229920000139polyethylene terephthalatePolymers0.000description3

- 239000005020polyethylene terephthalateSubstances0.000description3

- 239000002096quantum dotSubstances0.000description3

- 239000002356single layerSubstances0.000description3

- 239000004642PolyimideSubstances0.000description2

- 239000004020conductorSubstances0.000description2

- 239000013078crystalSubstances0.000description2

- 238000005530etchingMethods0.000description2

- 229910010272inorganic materialInorganic materials0.000description2

- 239000011147inorganic materialSubstances0.000description2

- 239000004973liquid crystal related substanceSubstances0.000description2

- 238000000034methodMethods0.000description2

- 239000011368organic materialSubstances0.000description2

- -1polyethylene terephthalatePolymers0.000description2

- 229920001721polyimidePolymers0.000description2

- 229910052594sapphireInorganic materials0.000description2

- 239000010980sapphireSubstances0.000description2

- 239000011787zinc oxideSubstances0.000description2

- RYGMFSIKBFXOCR-UHFFFAOYSA-NCopperChemical compound[Cu]RYGMFSIKBFXOCR-UHFFFAOYSA-N0.000description1

- GYHNNYVSQQEPJS-UHFFFAOYSA-NGalliumChemical compound[Ga]GYHNNYVSQQEPJS-UHFFFAOYSA-N0.000description1

- ZOKXTWBITQBERF-UHFFFAOYSA-NMolybdenumChemical compound[Mo]ZOKXTWBITQBERF-UHFFFAOYSA-N0.000description1

- BQCADISMDOOEFD-UHFFFAOYSA-NSilverChemical compound[Ag]BQCADISMDOOEFD-UHFFFAOYSA-N0.000description1

- 229910052782aluminiumInorganic materials0.000description1

- XAGFODPZIPBFFR-UHFFFAOYSA-NaluminiumChemical compound[Al]XAGFODPZIPBFFR-UHFFFAOYSA-N0.000description1

- 229910021417amorphous siliconInorganic materials0.000description1

- 239000000919ceramicSubstances0.000description1

- 229910052802copperInorganic materials0.000description1

- 239000010949copperSubstances0.000description1

- 230000009977dual effectEffects0.000description1

- 230000000694effectsEffects0.000description1

- 229910052733galliumInorganic materials0.000description1

- 239000011521glassSubstances0.000description1

- 229910052738indiumInorganic materials0.000description1

- APFVFJFRJDLVQX-UHFFFAOYSA-Nindium atomChemical compound[In]APFVFJFRJDLVQX-UHFFFAOYSA-N0.000description1

- 229910003437indium oxideInorganic materials0.000description1

- PJXISJQVUVHSOJ-UHFFFAOYSA-Nindium(iii) oxideChemical compound[O-2].[O-2].[O-2].[In+3].[In+3]PJXISJQVUVHSOJ-UHFFFAOYSA-N0.000description1

- AMGQUBHHOARCQH-UHFFFAOYSA-Nindium;oxotinChemical compound[In].[Sn]=OAMGQUBHHOARCQH-UHFFFAOYSA-N0.000description1

- 238000009413insulationMethods0.000description1

- 239000007769metal materialSubstances0.000description1

- 229910044991metal oxideInorganic materials0.000description1

- 150000004706metal oxidesChemical class0.000description1

- 238000012986modificationMethods0.000description1

- 230000004048modificationEffects0.000description1

- 229910052750molybdenumInorganic materials0.000description1

- 239000011733molybdenumSubstances0.000description1

- 230000003287optical effectEffects0.000description1

- 230000002093peripheral effectEffects0.000description1

- 210000004508polar bodyAnatomy0.000description1

- 229920000515polycarbonatePolymers0.000description1

- 239000004417polycarbonateSubstances0.000description1

- 229910021420polycrystalline siliconInorganic materials0.000description1

- 229920005591polysiliconPolymers0.000description1

- 239000010453quartzSubstances0.000description1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-Nsilicon dioxideInorganic materialsO=[Si]=OVYPSYNLAJGMNEJ-UHFFFAOYSA-N0.000description1

- 229910052709silverInorganic materials0.000description1

- 239000004332silverSubstances0.000description1

- KKEYFWRCBNTPAC-UHFFFAOYSA-Lterephthalate(2-)Chemical compound[O-]C(=O)C1=CC=C(C([O-])=O)C=C1KKEYFWRCBNTPAC-UHFFFAOYSA-L0.000description1

- XOLBLPGZBRYERU-UHFFFAOYSA-Ntin dioxideChemical compoundO=[Sn]=OXOLBLPGZBRYERU-UHFFFAOYSA-N0.000description1

- 229910001887tin oxideInorganic materials0.000description1

- YVTHLONGBIQYBO-UHFFFAOYSA-Nzinc indium(3+) oxygen(2-)Chemical compound[O--].[Zn++].[In+3]YVTHLONGBIQYBO-UHFFFAOYSA-N0.000description1

Images

Classifications

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/441—Interconnections, e.g. scanning lines

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6729—Thin-film transistors [TFT] characterised by the electrodes

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/20—Electrodes characterised by their shapes, relative sizes or dispositions

- H10D64/23—Electrodes carrying the current to be rectified, amplified, oscillated or switched, e.g. sources, drains, anodes or cathodes

- H10D64/251—Source or drain electrodes for field-effect devices

- H10D64/258—Source or drain electrodes for field-effect devices characterised by the relative positions of the source or drain electrodes with respect to the gate electrode

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

Landscapes

- Thin Film Transistor (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Electrodes Of Semiconductors (AREA)

Abstract

Description

本揭露是有關於一種電子裝置,且特別是有關於一種可具有較小的尺寸的電子裝置。

平面顯示面板已廣泛地應用於電子設備例如行動電話、電視、監視器、平板電腦、車用顯示器、穿戴裝置以及桌上型電腦中。隨電子產品蓬勃發展,對於電子產品上的顯示品質的要求越來越高,使得用於顯示的電子裝置不斷朝向更大及更高解析度的顯示效果改進。

本揭露是提供一種電子裝置,其可具有較小的尺寸。

本揭露的實施例的電子裝置包括基板以及多個電晶體。多個電晶體設置於基板上。多個電晶體包括半導體層、閘絕緣層、閘極、第一電極以及第二電極。半導體層設置於基板上。閘絕緣層設置於半導體層上且包括多個第一接觸孔與多個第二接觸孔。閘極設置於閘絕緣層上。第一電極設置於閘極上且具有遠離閘極的第一側。第一電極通過多個第一接觸孔接觸半導體層。第二電極設置於閘極上且具有遠離閘極的第二側。第二電極通過多個第二接觸孔接觸半導體層。多個第一接觸孔具有遠離閘極的第一邊緣。第一側與閘極之間的最小距離小於多個第一接觸孔中的一個第一接觸孔的第一邊緣與閘極之間的最小距離。

為讓本揭露的上述特徵和優點能更明顯易懂,下文特舉實施例,並配合所附圖式作詳細說明如下。

通過參考以下的詳細描述並同時結合附圖可以理解本揭露,須注意的是,為了使讀者能容易瞭解及為了圖式的簡潔,本揭露中的多張圖式只繪出電子裝置的一部分,且圖式中的特定元件並非依照實際比例繪圖。此外,圖中各元件的數量及尺寸僅作為示意,並非用來限制本揭露的範圍。

在下文說明書與權利要求書中,「含有」與「包括」等詞為開放式詞語,因此其應被解釋為「含有但不限定為…」之意。

應了解到,當元件或膜層被稱為在另一個元件或膜層「上」或「連接到」另一個元件或膜層時,它可以直接在此另一元件或膜層上或直接連接到此另一元件或層,或者兩者之間存在有插入的元件或膜層(非直接情況)。相反地,當元件被稱為「直接」在另一個元件或膜層「上」或「直接連接到」另一個元件或膜層時,兩者之間不存在有插入的元件或膜層。

雖然術語第一、第二、第三…可用以描述多種組成元件,但組成元件並不以此術語為限。此術語僅用於區別說明書內單一組成元件與其他組成元件。權利要求中可不使用相同術語,而依照權利要求中元件宣告的順序以第一、第二、第三…取代。因此,在下文說明書中,第一組成元件在權利要求中可能為第二組成元件。

在本揭露一些實施例中,關於接合、連接之用語例如「連接」、「互連」等,除非特別定義,否則可指兩個結構係直接接觸,或者亦可指兩個結構並非直接接觸,其中有其它結構設於此兩個結構之間。且此關於接合、連接之用語亦可包括兩個結構都可移動,或者兩個結構都固定之情況。此外,用語「耦接」包括任何直接及間接的電性連接手段。

在本揭露中,長度與寬度的量測方式可以是採用光學顯微鏡量測而得,厚度則可以由電子顯微鏡中的剖面影像量測而得,但不以此為限。另外,任兩個用來比較的數值或方向,可存在著一定的誤差。

本揭露的電子裝置可包括顯示裝置、天線裝置、感測裝置、觸控電子裝置(touch display)、曲面電子裝置(curved display)或非矩形電子裝置(free shape display),但不以此為限。電子裝置可為可彎折或可撓式電子裝置。電子裝置可例如包括發光二極體、液晶(liquid crystal)、螢光(fluorescence)、磷光(phosphor)、量子點(quantum dot,QD)、其它合適的顯示介質、或前述之組合,但不以此為限。發光二極體可例如包括有機發光二極體(organic light emitting diode,OLED)、無機發光二極體(inorganic light-emitting diode,LED)、次毫米發光二極體(mini LED)、微發光二極體(micro LED)或量子點發光二極體(可例如為QLED、QDLED)、或其他適合之材料或上述的任意排列組合,但不以此為限。顯示裝置可例如包括拼接顯示裝置,但不以此為限。天線裝置可例如是液晶天線,但不以此為限。天線裝置可例如包括天線拼接裝置,但不以此為限。需注意的是,電子裝置可為前述之任意排列組合,但不以此為限。此外,電子裝置的外型可為矩形、圓形、多邊形、具有彎曲邊緣的形狀或其他適合的形狀。電子裝置可以具有驅動系統、控制系統、光源系統、層架系統…等週邊系統以支援顯示裝置、天線裝置或拼接裝置。下文將以電子裝置說明本揭露內容,但本揭露不以此為限。

須知悉的是,以下所舉實施例可以在不脫離本揭露的精神下,可將數個不同實施例中的特徵進行替換、重組、混合以完成其他實施例。各實施例間特徵只要不違背發明精神或相衝突,均可任意混合搭配使用。

現將詳細地參考本揭露的示範性實施例,示範性實施例的實例說明於附圖中。只要有可能,相同元件符號在圖式和描述中用來表示相同或相似部分。

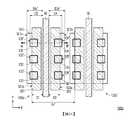

圖1A為本揭露一實施例的電子裝置的上視示意圖。圖1B為圖1A的電子裝置沿剖面線A-A’的剖面示意圖。為了附圖清楚及方便說明,圖1A省略繪示了電子裝置中的若干元件。

請同時參照圖1A與圖1B,本實施例的電子裝置100包括基板110以及多個電晶體120、120’。其中,基板110可包括硬性基板、軟性基板或前述的組合。舉例來說,基板110的材料可包括玻璃、石英、藍寶石(sapphire)、陶瓷、聚碳酸酯(polycarbonate,PC)、聚醯亞胺(polyimide,PI)、聚對苯二甲酸乙二酯(polyethylene terephthalate,PET)、其它合適的基板材料、或前述的組合,但不以此為限。

在本實施例中,多個電晶體120、120’設置於基板110上。多個電晶體120、120’可設置於電子裝置100的非顯示區(未繪示)中,但不以此為限。舉例來說,多個電晶體120、120’可設置於非顯示區中的解多工器電路(de-multiplexer circuits,demux)和/或靜電放電防護電路(anti-electrostatic discharge circuits) (未繪示),但不以此為限。在一些實施例中,多個電晶體120、120’也可以設置於電子裝置100的顯示區和/或非顯示區(未繪示)中。雖然圖1A示意地繪示2個電晶體,但本揭露並不對電晶體的數量加以限制。以下以電晶體120為例進行說明。

在本實施例中,電晶體120包括半導體層SE、閘極絕緣層GI、閘極GE、第一電極SD1以及第二電極SD2。其中,半導體層SE設置於基板110上。半導體層SE包括第一側邊SE1以及與第一側邊SE1相對的第二側邊SE2。第一側邊SE1鄰近於第一電極SD1且第二側邊SE2鄰近於第二電極SD2。半導體層SE的材料可包括非晶質矽(amorphous silicon)、低溫多晶矽(LTPS)、金屬氧化物(例如氧化銦鎵鋅IGZO)、其他合適的材料或上述的組合,但不以此為限。

在本實施例中,閘極絕緣層GI設置於半導體層SE上且覆蓋緩衝層142。閘極絕緣層GI包括多個第一接觸孔131、132、133與多個第二接觸孔134、135、136。多個第一接觸孔131、132、133與多個第二接觸孔134、135、136分別暴露出部分的半導體層SE以及部分的緩衝層142。此外,在電子裝置100的上視圖中(如圖1A),多個第一接觸孔131、132、133分別沿著閘極GE的延伸方向(方向Y)排列,且多個第二接觸孔134、135、136分別沿著閘極GE的延伸方向(方向Y)排列。多個第一接觸孔131、132、133與多個第二接觸孔134、135、136分別設置於閘極GE的相對兩側。於方向X,第一接觸孔131與第二接觸孔134對應設置,第一接觸孔132與第二接觸孔135對應設置,且第一接觸孔133與第二接觸孔136對應設置,但不以此為限。其中,方向X可以為剖面線A-A’的延伸方向,方向X不同於方向Y,且方向X垂直於方向Y。此外,雖然圖1A示意地繪示3個第一接觸孔131、132、133與3個第二接觸孔134、135、136,但本揭露並不對第一接觸孔與第二接觸孔的數量加以限制。此外,閘極絕緣層GI可為單層或多層結構,且可例如包括有機材料、無機材料或前述的組合,但不以此為限。

在本實施例中,閘極GE設置於閘極絕緣層GI上。在電子裝置100的上視圖中(如圖1A),閘極GE設置於多個第一接觸孔131、132、133與多個第二接觸孔134、135、136之間,且閘極GE設置於第一電極SD1與第二電極SD2之間。在一些實施例中,第一電極SD1可以是源極,第二電極SD2可以是汲極。而在一些實施例中,第一電極SD1可以是汲極,第二電極SD2可以是源極。

在本實施例中,電子裝置100還包括絕緣層140、絕緣層141、緩衝層142以及介電層150。絕緣層140設置於閘極GE與閘極絕緣層GI之間,且對應於閘極GE。緩衝層142設置於閘極絕緣層GI與基板110之間。此外,絕緣層140、絕緣層141、緩衝層142以及介電層150可為單層或多層結構,且可例如包括有機材料、無機材料或前述的組合,但不以此為限。

在本實施例中,介電層150設置於閘極絕緣層GI上,且介電層150覆蓋閘極GE以及絕緣層140。介電層150包括多個第一開孔151、152、153與多個第二開孔154、155、156。多個第一開孔151、152、153連通對應的多個第一接觸孔131、132、133,且多個第二開孔154、155、156連通對應的多個第二接觸孔134、135、136,以分別暴露出部分的半導體層SE。此外,在電子裝置100的上視圖中(如圖1A),多個第一開孔151、152、153分別沿著閘極GE的延伸方向(方向Y)排列,且多個第二開孔154、155、156分別沿著閘極GE的延伸方向(方向Y)排列。多個第一開孔151、152、153與多個第二開孔154、155、156分別設置於閘極GE的相對兩側。於方向X,第一開孔151與第二開孔154對應設置,第一開孔152與第二開孔155對應設置,且第一開孔153與第二開孔156對應設置,但不以此為限。

在本實施例中,第一電極SD1設置於閘極GE以及介電層150上,且第一電極SD1具有遠離閘極GE的第一側SD1a。如圖1A及圖1B,電晶體120、120’於基板110上沿方向X排列,其中第一電極SD1和第二電極SD2與閘極GE有些許距離,所以第一電極SD1遠離閘極GE的側邊,可為第一電極SD1沿方向X遠離閘極GE的第一側SD1a,而第二電極SD2遠離閘極GE的側邊,可為第二電極SD2沿方向X遠離閘極GE的第二側SD2a。在一些實施例中,第一電極SD1和第二電極SD2與閘極GE切齊或重疊(未圖示),同樣會有第一電極SD1沿方向X遠離閘極GE的第一側SD1a以及第二電極SD2沿方向X遠離閘極GE的第二側SD2a。在另一實施例中,如圖1C電晶體120、120’於基板110上也可沿方向Y排列,第一電極SD1遠離閘極GE的側邊,可為第一電極SD1沿方向Y遠離閘極GE的第一側SD1a,而第二電極SD2遠離閘極GE的側邊,可為第二電極SD2沿方向Y遠離閘極GE的第二側SD2a。在一些實施例中,第一電極SD1和第二電極SD2與閘極GE切齊或重疊(未圖示),同樣會有第一電極SD1沿方向Y遠離閘極GE的第一側SD1a以及第二電極SD2沿方向Y遠離閘極GE的第二側SD2a。第一電極SD1還可設置於介電層150的多個第一開孔151、152、153以及閘極絕緣層GI的多個第一接觸孔131、132、133內,以使第一電極SD1可通過多個第一開孔151、152、153以及多個第一接觸孔131、132、133接觸半導體層SE。在本實施例中,第二電極SD2設置於閘極GE以及介電層150上,且第二電極SD2具有遠離閘極GE的第二側SD2a。第二電極SD2還可設置於介電層150的多個第二開孔154、155、156以及閘極絕緣層GI的多個第二接觸孔134、135、136內,以使第二電極SD2可通過多個第二開孔154、155、156以及多個第二接觸孔134、135、136接觸半導體層SE。在一些實施例中,介電層150的多個第一開孔151、152、153可以較大於第一接觸孔131、132、133。在一些實施例中,介電層150的多個第二開孔154、155、156可以較大於第二接觸孔134、135、136,但不以此為限。此外,在電子裝置100的上視圖中(如圖1A),第一電極SD1與第二電極SD2可分別設置於閘極GE的相對兩側。在本實施例中,第一電極SD1及/或第二電極SD2的材料可包括透明導電材料或非透明導電材料,例如銦錫氧化物、銦鋅氧化物、氧化銦、氧化鋅、氧化錫、金屬材料(例如鋁、鉬、銅、銀等)、其它合適的材料或上述的組合,但不以此為限。在本實施例中,第一電極SD1及/或第二電極SD2的結構,可以是單層或多層結構,但不以此為限。此外,在本實施例中,在電子裝置100的上視圖中(如圖1A),多個第一接觸孔131、132、133的底部具有遠離閘極GE的第一邊緣131’、132’、133’。其中,第一電極SD1的第一側SD1a與閘極GE之間的最小距離D1可以小於多個第一接觸孔131、132、133中的一個第一接觸孔131的第一邊緣131’與閘極GE之間的最小距離D2,但不以此為限。在一些實施例中,第一電極SD1的第一側SD1a與閘極GE之間的最小距離D1也可以小於多個第一接觸孔131、132、133的第一邊緣131’、132’、133’與閘極GE之間的最小距離D2。也就是說,第一電極SD1並未填滿於多個第一開孔151、152、153以及多個第一接觸孔131、132、133內。即,在多個第一接觸孔131、132、133中,第一電極SD1的第一側SD1a與多個第一接觸孔131、132、133的第一邊緣131’、132’、133’之間具有第一間隙G1。此外,在本實施例中,第一間隙G1的寬度W1例如是小於多個第一接觸孔131、132、133的寬度W2的一半,也就是說,第一電極SD1於多個第一接觸孔131、132、133中的寬度例如是大於多個第一接觸孔131、132、133的寬度W2的一半,但不以此為限。在本實施例中,最小距離D1、D2以及寬度W1、W2例如是沿著方向X進行量測。

在本實施例中,在電子裝置100的上視圖中(如圖1A),多個第二接觸孔134、135、136的底部具有遠離閘極GE的第二邊緣134’、135’、136’。其中,第二電極SD2的第二側SD2a與閘極GE之間的最小距離D3可以小於多個第二接觸孔134、135、136中的一個第二接觸孔134的第二邊緣134’與閘極GE之間的最小距離D4,但不以此為限。在一些實施例中,第二電極SD2的第二側SD2a與閘極GE之間的最小距離D3也可以小於多個第二接觸孔134、135、136的第二邊緣134’、135’、136’與閘極GE之間的最小距離D4。也就是說,第二電極SD2並未填滿於多個第二開孔154、155、156以及多個第二接觸孔134、135、136內。即,在多個第二接觸孔134、135、136中,第二電極SD2的第二側SD2a與多個第二接觸孔134、135、136的第二邊緣134’、135’、136’之間具有第二間隙G2。第二間隙G2的寬度W3例如是小於多個第二接觸孔134、135、136的寬度W4的一半,即第二電極SD2於多個第二接觸孔134、135、136中的寬度大於多個第二接觸孔134、135、136的寬度W4的一半,但不以此為限。在本實施例中,最小距離D3、D4以及寬度W3、W4例如是沿著方向X進行量測。

在本實施例中,絕緣層141設置於介電層150上、第一間隙G1內以及第二間隙G2內。絕緣層141覆蓋第一電極SD1以及第二電極SD2。絕緣層141與閘極絕緣層GI分別位於介電層150的相對兩側。

在本實施例中,第一電極SD1的第一側SD1a可以與半導體層SE的第一側邊SE1實質上切齊,且第二電極SD2的第二側SD2a可以與半導體層SE的第二側邊SE2實質上切齊。因此,半導體層SE的第一側邊SE1與閘極GE之間的最小距離D1’可大致上相似於第一電極SD1的第一側SD1a與閘極GE之間的最小距離D1,且半導體層SE的第二側邊SE2與閘極GE之間的最小距離D3’也可大致上相似於第二電極SD2的第二側SD2a與閘極GE之間的最小距離D3。因此,在本實施例中,半導體層SE的第一側邊SE1與閘極GE之間的最小距離D1’也可以小於多個第一接觸孔131、132、133的第一邊緣131’、132’、133’與閘極GE之間的最小距離D2,且半導體層SE的第二側邊SE2與閘極GE之間的最小距離D3’也可以小於多個第二接觸孔134、135、136的第二邊緣134’、135’、136’與閘極GE之間的最小距離D4,但不以此為限。在本實施例中,最小距離D1’、D3’例如是沿著方向X進行量測。在一些實施例中,第一電極SD1的第一側SD1a可以小於半導體層SE的第一側邊SE1,且第二電極SD2的第二側SD2a可以小於半導體層SE的第二側邊SE2,但不以此為限。

在本實施例中,在電子裝置100的上視圖中(如圖1A),電晶體120與電晶體120’相鄰設置。其中,電晶體120與電晶體120’之間的間距P1可為電晶體120的第一電極SD1的第一側SD1a與電晶體120’的第一電極SD1’的第一側SD1a’之間的最小距離,且所述最小距離可避免電晶體120與電晶體120’之間發生短路。在本實施例中,由於最小距離D1小於最小距離D2且最小距離D3小於最小距離D4,因而可使本實施例的電子裝置100中的電晶體120、120’的尺寸可縮小。藉此,也可使相鄰的電晶體120與電晶體120’之間的間距P1可縮小,本實施例中可縮小1微米至5微米,但不以此為限。

簡言之,在本揭露實施例的電子裝置100中,藉由使第一電極SD1的第一側SD1a與閘極GE之間的最小距離D1小於第一接觸孔131、132、133的第一邊緣131’、132’、133’與閘極GE之間的最小距離D2的方式,可用來縮小電晶體120、120’的尺寸並縮小相鄰的兩電晶體120、120’之間的間距P1。此外,藉由使第二電極SD2的第二側SD2a與閘極GE之間的最小距離D3小於第二接觸孔134、135、136的第二邊緣134’、135’、136’與閘極GE之間的最小距離D4的方式,也可用來縮小電晶體120、120’的尺寸並縮小相鄰的兩電晶體120、120’之間的間距P1。因此,藉由上述的方式,可使本揭露實施例的電子裝置100具有較小的尺寸。

以下將列舉其他實施例以作為說明。在此必須說明的是,下述實施例沿用前述實施例的元件標號與部分內容,其中採用相同的標號來表示相同或近似的元件,並且省略了相同技術內容的說明。關於省略部分的說明可參考前述實施例,下述實施例不再重複贅述。

圖2為本揭露另一實施例的電子裝置的上視示意圖。請同時參照圖1A與圖2,本實施例的電子裝置100a大致相似於圖1A的電子裝置100,因此兩實施例中相同與相似的構件於此不再重述。在本實施例的電子裝置100a的上視圖中,多個第一接觸孔131a、132a(或131a’、132a’)與多個第二接觸孔134a(或134a’)呈交錯排列。

具體來說,請參照圖2,於方向X,電晶體120a的第一接觸孔131a不會與第二接觸孔134a對應設置,第一接觸孔132a不會與第二接觸孔134a對應設置,且第一接觸孔131a以及第一接觸孔132a可與第二接觸孔134a呈交錯排列。因此,在相鄰的電晶體120a與電晶體120a’之間,電晶體120a的第二接觸孔134a也會與電晶體120a’的第一接觸孔131a’以及第一接觸孔132a’呈交錯排列。藉此,可縮小電晶體120a的第二電極SD2的第二側SD2a與電晶體120a’的第一電極SD1’的第一側SD1a’之間的間距,以使本實施例的電子裝置100a的相鄰的電晶體120a與電晶體120a’之間的間距P2可小於圖1A的電子裝置100的相鄰的電晶體120與電晶體120’之間的間距P1,且例如是間距P2可小於間距P1 1微米至3微米,但不以此為限。

圖3為本揭露另一實施例的電子裝置的上視示意圖。請同時參照圖1A與圖3,本實施例的電子裝置100b大致相似於圖1A的電子裝置100,因此兩實施例中相同與相似的構件於此不再重述。在本實施例的電子裝置100b的上視圖中,電子裝置100b還包括金屬走線160。

具體來說,請參照圖3,金屬走線160與第一電極SD1以及第二電極SD2為同一層別,且金屬走線160設置於電晶體120b與電晶體120b’之間。金屬走線160沿著方向Y延伸,且大致上平行於閘極GE。其中,由於本實施例的電子裝置100b中的電晶體120b、120b’的尺寸可小於習知的電子裝置中的電晶體的尺寸,因此,相鄰的電晶體120b與電晶體120b’之間的間距P3(即電晶體120b的第一電極SD1的第一側SD1a與電晶體120b’的第一電極SD1’的第一側SD1a’之間的最小距離)也可小於習知的電子裝置的相鄰的兩個電晶體之間的間距,且例如是小於1微米至5微米,但不以此為限。

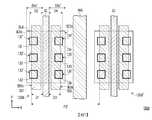

圖4A為本揭露另一實施例的電子裝置的剖面示意圖。圖4B為圖4A的電子裝置沿剖面線B-B’的剖面示意圖。請同時參照圖1A-1B與圖4A-4B,本實施例的電子裝置100c大致相似於圖1A-1B的電子裝置100,因此兩實施例中相同與相似的構件於此不再重述。在本實施例的電子裝置100c的上視圖中,電晶體120c的半導體層SEc的第一側邊SE1c與閘極GE之間的最小距離D1c’大於第一接觸孔131、132、133的第一邊緣131’、132’、133’與閘極GE之間的最小距離D2,且半導體層SE的第二側邊SE2c與閘極GE之間的最小距離D3c’大於第二接觸孔134、135、136的第二邊緣134’、135’、136’與閘極GE之間的最小距離D4。

具體來說,請同時參照圖4A與圖4B,半導體層SEc的第一側邊SE1c以及第二側邊SE2c可分別以遠離閘極GE的方向延伸,以使半導體層SEc的第一側邊SE1c以及第二側邊SE2c可分別延伸至第一接觸孔131、132、133以及第二接觸孔134、135、136外。藉此,在對閘極絕緣層GI進行蝕刻以形成第一接觸孔131、132、133以及第二接觸孔134、135、136時,可以確保閘極絕緣層GI的第一接觸孔131、132、133以及第二接觸孔134、135、136可完全地形成在半導體層SEc上,以避免在對閘極絕緣層GI進行蝕刻時也會繼續對下方的緩衝層142進行蝕刻。

此外,相較於圖1A-1B的電子裝置100,由於本實施例並未變更第一電極SD1的第一側SD1a與閘極GE之間的最小距離D1以及第二電極SD2的第二側SD2a與閘極GE之間的最小距離D3,因此,本實施例的電子裝置100c的電晶體120c與電晶體120c’之間的間距P1’可大致上相似於圖1A-1B的電子裝置100的電晶體120與電晶體120’之間的間距P1。

圖5為本揭露另一實施例的電子裝置的剖面示意圖。請同時參照圖3與圖5,本實施例的電子裝置100d大致相似於圖3的電子裝置100b,因此兩實施例中相同與相似的構件於此不再重述。在本實施例的電子裝置100d的上視圖中,電晶體120d的半導體層SEd的第一側邊SE1d與閘極GE之間的最小距離D1d’大於第一接觸孔131、132、133的第一邊緣131’、132’、133’與閘極GE之間的最小距離D2,且半導體層SEd的第二側邊SE2d與閘極GE之間的最小距離D3d’大於第二接觸孔134、135、136的第二邊緣134’、135’、136’與閘極GE之間的最小距離D4。

具體來說,半導體層SEd的第一側邊SE1d以及第二側邊SE2d可分別以遠離閘極GE的方向延伸,以使半導體層SEd的第一側邊SE1d以及第二側邊SE2d可分別延伸至第一接觸孔131、132、133以及第二接觸孔134、135、136外。藉此,在形成第一接觸孔131、132、133以及第二接觸孔134、135、136時,可以確保第一接觸孔131、132、133以及第二接觸孔134、135、136可完全地形成在半導體層SEd上,以避免在進行蝕刻時也會繼續對下方的緩衝層(未繪示)進行蝕刻。

此外,相較於圖3的電子裝置100b,由於本實施例並未變更第一電極SD1的第一側SD1a與閘極GE之間的最小距離D1以及第二電極SD2的第二側SD2a與閘極GE之間的最小距離D3,因此,本實施例的電子裝置100d的電晶體120d與電晶體120d’之間的間距P3’可大致上相似於圖3的電子裝置100b的電晶體120b與電晶體120b’之間的間距P3。

圖6A為本揭露另一實施例的電子裝置的剖面示意圖。圖6B為圖6A的電子裝置沿剖面線C-C’的剖面示意圖。請同時參照圖4A-4B與圖6A-6B,本實施例的電子裝置100e大致相似於圖4A-4B的電子裝置100c,因此兩實施例中相同與相似的構件於此不再重述。在本實施例的電子裝置100e的上視圖中,電晶體120e的閘極GE’的輪廓為U型。

具體來說,閘極GE’具有左臂L與右臂R。其中,閘極GE’的左臂L與右臂R可分別對應於半導體層SEe的通道層CH1以及通道層CH2。因此,相較於圖4B的電子裝置100c的電晶體120c的半導體層SEc為一個通道層CH,本實施例的電子裝置100e的電晶體120e的半導體層SEe為雙通道結構。

綜上所述,在本揭露實施例的電子裝置中,藉由使第一電極的第一側與閘極之間的最小距離小於第一接觸孔中的第一邊緣與閘極之間的最小距離,可用來縮小電晶體的尺寸並縮小相鄰的兩電晶體之間的間距。此外,藉由使第二電極的第二側與閘極之間的最小距離小於第二接觸孔中的第二邊緣與閘極之間的最小距離,也可用來縮小電晶體的尺寸並縮小相鄰的兩電晶體之間的間距。因此,藉由上述的方式,可使本揭露實施例的電子裝置具有較小的尺寸。

雖然本揭露已以實施例揭露如上,然其並非用以限定本揭露,任何所屬技術領域中具有通常知識者,在不脫離本揭露的精神和範圍內,當可作些許的更動與潤飾,故本揭露的保護範圍當視後附的申請專利範圍所界定者為準。

100、100a、100b、100c、100d、100e:電子裝置 110:基板 120、120’、120a、120a’、120b、120b’、120c、120c’、120d、120d’、120e:電晶體 131、131a、131a’、132、132a、132a’、133:第一接觸孔 131’、132’、133’:第一邊緣 134、134a、134a’、135、136:第二接觸孔 134’、135’、136’:第二邊緣 140、141:絕緣層 142:緩衝層 150:介電層 151、152、153:第一開孔 154、155、156:第二開孔 160:金屬走線 A-A’、B-B’、C-C’:剖面線 CH、CH1、CH2:通道層 D1、D1’、D1c’、D1d’、D2、D3、D3’、D3c’、D3d’、D4:最小距離 G1:第一間隙 G2:第二間隙 GE、GE’:閘極 GI:閘極絕緣層 L:左臂 P1、P1’、P2、P3、P3’:間距 R:右臂 SD1、SD1’:第一電極 SD1a、SD1a’:第一側 SD2:第二電極 SD2a:第二側 SE、SEc、SEd、SEe:半導體層 SE1、SE1c、SE1d:第一側邊 SE2、SE2c、SE2d:第二側邊 W1、W2、W3、W4:寬度 X、Y:方向

圖1A為本揭露一實施例的電子裝置的上視示意圖。 圖1B為圖1A的電子裝置沿剖面線A-A’的剖面示意圖。 圖1C為本揭露另一實施例的電子裝置的上視示意圖 圖2為本揭露另一實施例的電子裝置的上視示意圖。 圖3為本揭露另一實施例的電子裝置的上視示意圖。 圖4A為本揭露另一實施例的電子裝置的剖面示意圖。 圖4B為圖4A的電子裝置沿剖面線B-B’的剖面示意圖。 圖5為本揭露另一實施例的電子裝置的剖面示意圖。 圖6A為本揭露另一實施例的電子裝置的剖面示意圖。 圖6B為圖6A的電子裝置沿剖面線C-C’的剖面示意圖。

100:電子裝置

120、120’:電晶體

131、132、133:第一接觸孔

131’、132’、133’:第一邊緣

134、135、136:第二接觸孔

134’、135’、136’:第二邊緣

151、152、153:第一開孔

154、155、156:第二開孔

A-A’:剖面線

D1、D1’、D2、D3、D3’、D4:最小距離

GE:閘極

P1:間距

SD1、SD1’:第一電極

SD1a、SD1a’:第一側

SD2:第二電極

SD2a:第二側

SE:半導體層

SE1:第一側邊

SE2:第二側邊

X、Y:方向

Claims (10)

- 一種電子裝置,包括:基板;以及多個電晶體,設置於所述基板上,其中所述多個電晶體中至少一個,包括:半導體層,設置於所述基板上;閘絕緣層,設置於所述半導體層上,且包括多個第一接觸孔與多個第二接觸孔;閘極,設置於所述閘絕緣層上;第一電極,設置於所述閘極上,具有遠離所述閘極的第一側,且通過所述多個第一接觸孔接觸所述半導體層;以及第二電極,設置於所述閘極上,具有遠離所述閘極的第二側,且通過所述多個第二接觸孔接觸所述半導體層,其中所述多個第一接觸孔具有遠離所述閘極的第一邊緣,且所述第一側與所述閘極之間的最小距離小於所述多個第一接觸孔中的一個所述第一接觸孔的所述第一邊緣與所述閘極之間的最小距離,其中在至少一個所述第一接觸孔中,所述第一側與所述第一邊緣之間具有第一間隙。

- 如請求項1所述的電子裝置,其中所述第一側與所述閘極之間的最小距離小於所述多個第一接觸孔的所述第一邊緣與所述閘極之間的最小距離。

- 如請求項1所述的電子裝置,其中所述多個第二接觸孔具有遠離所述閘極的第二邊緣,且所述第二側與所述閘極之間的最小距離小於所述多個第二接觸孔中的一個所述第二接觸孔的所述第二邊緣與所述閘極之間的最小距離。

- 如請求項3所述的電子裝置,所述第二側與所述閘極之間的最小距離小於所述多個第二接觸孔的所述第二邊緣與所述閘極之間的最小距離。

- 如請求項3所述的電子裝置,在所述多個第二接觸孔中,所述第二側與所述第二邊緣之間具有第二間隙。

- 如請求項5所述的電子裝置,更包括:介電層,設置於所述閘絕緣層上,且包括多個第一開孔與多個第二開孔,其中所述多個第一開孔連通所述多個第一接觸孔,且所述多個第二開孔連通所述多個第二接觸孔;以及絕緣層,設置於所述介電層上、所述第一間隙內以及所述第二間隙內。

- 如請求項3所述的電子裝置,所述半導體層包括第一側邊以及與所述第一側邊相對的第二側邊,所述第一側邊鄰近於所述第一電極,且所述第二側邊鄰近於所述第二電極。

- 如請求項7所述的電子裝置,所述第一電極的所述第一側與所述半導體層的所述第一側邊切齊,且所述第二電極的所述第二側與所述半導體層的所述第二側邊切齊。

- 如請求項7所述的電子裝置,所述第一側邊與所述閘極之間的最小距離大於所述第一邊緣與所述閘極之間的最小距離,且所述第二側邊與所述閘極之間的最小距離大於所述第二邊緣與所述閘極之間的最小距離。

- 如請求項1所述的電子裝置,所述多個第一接觸孔與所述多個第二接觸孔呈交錯排列。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201962946976P | 2019-12-12 | 2019-12-12 | |

| US62/946,976 | 2019-12-12 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| TWI728916Btrue TWI728916B (zh) | 2021-05-21 |

| TW202123420A TW202123420A (zh) | 2021-06-16 |

Family

ID=76344288

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| TW109132018ATWI728916B (zh) | 2019-12-12 | 2020-09-17 | 電子裝置 |

Country Status (2)

| Country | Link |

|---|---|

| CN (1) | CN112993020B (zh) |

| TW (1) | TWI728916B (zh) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN118073362B (zh)* | 2024-01-10 | 2025-03-18 | 江苏卓胜微电子股份有限公司 | 半导体器件、射频芯片及电子设备 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TW201001715A (en)* | 2008-05-02 | 2010-01-01 | Ensiltech Corp | Thin film transistor and method of fabricating the same |

| TW201717405A (zh)* | 2010-12-28 | 2017-05-16 | 半導體能源研究所股份有限公司 | 半導體裝置及其製造方法 |

| TW201803095A (zh)* | 2016-04-08 | 2018-01-16 | 群創光電股份有限公司 | 顯示裝置及其製造方法 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100884541B1 (ko)* | 2002-12-10 | 2009-02-18 | 엘지디스플레이 주식회사 | 액정표시장치 및 그 제조방법 |

| KR20070115221A (ko)* | 2006-06-01 | 2007-12-05 | 삼성전자주식회사 | 박막 트랜지스터 표시판 및 그 제조 방법 |

| CN103715265B (zh)* | 2013-12-23 | 2016-06-01 | 京东方科技集团股份有限公司 | 薄膜晶体管、阵列基板和显示装置 |

| TWI564644B (zh)* | 2015-08-28 | 2017-01-01 | 群創光電股份有限公司 | 顯示裝置 |

| KR20170080996A (ko)* | 2015-12-31 | 2017-07-11 | 삼성디스플레이 주식회사 | 표시 장치용 박막 트랜지스터 및 이를 포함하는 유기 발광 표시 장치 |

- 2020

- 2020-09-17TWTW109132018Apatent/TWI728916B/zhactive

- 2020-09-17CNCN202010979495.2Apatent/CN112993020B/zhactiveActive

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TW201001715A (en)* | 2008-05-02 | 2010-01-01 | Ensiltech Corp | Thin film transistor and method of fabricating the same |

| TW201717405A (zh)* | 2010-12-28 | 2017-05-16 | 半導體能源研究所股份有限公司 | 半導體裝置及其製造方法 |

| TW201803095A (zh)* | 2016-04-08 | 2018-01-16 | 群創光電股份有限公司 | 顯示裝置及其製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN112993020A (zh) | 2021-06-18 |

| CN112993020B (zh) | 2023-05-30 |

| TW202123420A (zh) | 2021-06-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US12349439B2 (en) | Electronic device | |

| US20240062713A1 (en) | Electronic device | |

| US20250221048A1 (en) | Electronic device | |

| TWI728916B (zh) | 電子裝置 | |

| US12045100B2 (en) | Electronic device | |

| US20230148146A1 (en) | Electronic device | |

| CN112863329B (zh) | 显示装置 | |

| TWI754393B (zh) | 電子裝置 | |

| TWI804313B (zh) | 電子裝置及其製造方法 | |

| US11676973B2 (en) | Display device | |

| TWI752508B (zh) | 顯示裝置 | |

| US11658207B2 (en) | Capacitor and electronic device | |

| CN111863787B (zh) | 电子装置 | |

| WO2023008243A1 (ja) | 画素構造体および表示装置 | |

| TW202526894A (zh) | 電子裝置 |