RU2447500C1 - Device for identification of painting original - Google Patents

Device for identification of painting originalDownload PDFInfo

- Publication number

- RU2447500C1 RU2447500C1RU2011112524/08ARU2011112524ARU2447500C1RU 2447500 C1RU2447500 C1RU 2447500C1RU 2011112524/08 ARU2011112524/08 ARU 2011112524/08ARU 2011112524 ARU2011112524 ARU 2011112524ARU 2447500 C1RU2447500 C1RU 2447500C1

- Authority

- RU

- Russia

- Prior art keywords

- inputs

- outputs

- output

- input

- block

- Prior art date

Links

Images

Landscapes

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

Abstract

Description

Translated fromRussianИзобретение относится к аппаратным средствам опознавания подлинников произведений живописи и может быть использовано для получения кодов оригиналов живописи.The invention relates to hardware for identifying originals of paintings and can be used to obtain codes for the originals of painting.

Технический прототип при поиске не обнаружен. Техническим результатом является осуществление опознавания подлинника произведения живописи сравнением кода оригинала с кодом произведения живописи, претендующим на оригинал.No technical prototype was found during the search. The technical result is the implementation of the identification of the original painting by comparing the code of the original with the code of the painting, claiming to be the original.

Сущность изобретения в том, что устройство опознавания подлинника живописи выполняется в составе устройства кодирования, блока опознавания, блока энергонезависимой памяти и источника света с соответствующим реле времени.The essence of the invention is that the recognition device recognition of the painting is performed as part of the encoding device, recognition unit, non-volatile memory unit and light source with a corresponding time relay.

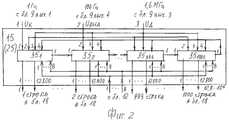

Устройство опознавания подлинника живописи на фиг.1, накопитель кодов кадра на фиг.2, блок регистров на фиг.3, 4, блок сравнения на фиг.5, общий вид одного элемента матрицы и его вид сверху на фиг.6, излучающая ячейка на фиг.7, 8, расположение элементов матрицы в экране на фиг.9, опознавание произведения живописи на фиг.10. Устройство опознавания подлинника живописи содержит /фиг.1/ устройство кодирования, блок 2 опознавания, блок 3 энергонезависимой памяти, представляемой тремя модулями флэшь-памяти, и источник света 43 с реле 44 времени /фиг.10/. Устройство 1 кодирования включает /фиг.1/ фотоэлектрический преобразователь /ФЭП/, включающий соответствующий объектив 4, матрицу 5 приборов с зарядовой инжекцией /ПЗИ/ из трехслойного КМОП-датчика [1 с.832], фоточувствительная сторона которой расположена в фокальной плоскости объектива 4, оптическое разрешение матрицы ПЗИ 1600×1000 строк /вариант/, первый-третий выходы ее подключены к входам предварительных усилителей ФЭП соответственно 6, 7, 8. Устройство 1 кодирования включает синтезатор 9 частот, первый 10 и второй 11 ключи, управляющие входы которых объединены и подключены к первому Uк выходу синтезатора 9 частот, второй выход Uс/1 кГц/ которого подключен к сигнальному входу первого ключа 10, третий выход Uд /1,6 МГц/ подключен к сигнальному входу второго ключа 11, включает три идентичных аналого-цифровых преобразователя /АЦП/ 12, 13, 14, три идентичных накопителя 15, 16, 17 кодов кадра, три идентичных блока 18, 19, 20 импульсных усилителя, каждый содержит импульсных усилителей по числу строк 1000, числу отсчетов в строке 1600 и числу разрядов в коде 8, всего 12,8×106 штук, и включает плоскопанельный экран 21.The authenticating device recognition of the painting in Fig. 1, the frame code storage in Fig. 2, the register block in Figs. 3, 4, the comparison block in Fig. 5, a general view of one matrix element and its top view in Fig. 6, the emitting cell in Fig.7, 8, the location of the matrix elements in the screen of Fig.9, the recognition of the painting in Fig.10. The recognition device recognition device contains / Fig. 1/ an encoding device, an

Блок 2 опознавания включает /фиг.1/ три идентичных блока 22, 23, 24 сравнения, каждый из которых содержит /фиг.5/ первый регистр 40, первый-восьмой входы которого подключены к первому-восьмому выходам своего АЦП, второй регистр 41, первый-восьмой входы которого подключены через разъемные соединители к первому-восьмому выходам соответствующего выхода блока 3, и с первого по восьмой логические элементы 421-8 в составе И-НЕ1-НЕ2-НЕ3, первые входы логических элементов 421-8 подключены к выходам первого-восьмого разрядов регистра 40, вторые их входы подключены к выходам первого-восьмого разрядов регистра 41 /фиг.5/, а выходы логических элементов 421-8являются первым-восьмым выходами блока 22 /23, 24/ сравнения.The

Блок 2 опознавания включает /фиг.1/ три накопителя 25, 26, 27 кодов кадра, идентичные блокам 15-17, три блока 28, 29, 30 импульсных усилителей, в каждом по 12,8×106 импульсных усилителей /1000×1600×8/, и плоскопанельный экран 31. Состояние регистров 40, 41 в блоках 22, 23, 24 сравнения в таблице 1.The

Блок 3 энергонезависимой памяти включает три идентичных модуля 32, 33, 34 флэшь-памяти. Информационными входами модулей флэшь-памяти являются первый-восьмой входы 1, 2, 3 входов блока 3, подключенные через разъемные соединители к первому-восьмому выходам АЦП соответственно 12, 13, 14, управляющие входы Uд модулей флэшь-памяти подключаются через разъемные соединители и через включатель SA1 к третьему выходу синтезатора 9 частот. Выходы модулей флэшь-памяти 32, 33, 34 через разъемные соединения подключаются к 1, 2, 3 входам блоков 22, 23, 24 сравнения. При кодировании подлинника во флешь-память 32 за кадр поступают 1,6 Мбайт /1000×1600/ 8-и разрядных кодов видеосигналов R с АЦП 12 во флэшь-память 33 поступают 1,6 Мбайт кодов видеосигналов G с АЦП 13, во флэшь-память 34 поступают 1,6 Мбайт кодов, видеосигнала B с АЦП 14. При кодировании картины живописи она освечивается источником 43 света /фиг.10/. Спектр излучения источника 43 света содержит семь основных цветов, т.е. спектр близок к спектру солнечного света, лучший вариант - солнечное облучение картины. Источник 43 света запитывается через реле 44 времени, работающее в режиме "постоянно" или в режиме "один кадр" и подключено через включатель SA4 к пятому выходу синтезатора 9 частот /фиг.1/. Накопители 15 - 17 и 25 - 27 кодов кадра идентичны, каждый включает /фиг.2/ блоки 351-1000 регистров по числу строк в кадре. Информационным входом являются поразрядно объединенные первый-восьмой входы блоков 351-1000 регистров. Управляющими входами являются: первым - первый управляющий вход Uк первого блока 351 регистров, вторым - объединенные вторые управляющие входы Uвыд 100 Гц блоков 351-1000 регистров, третьим - объединенные третьи управляющие входы Uд 1,6 МГц блоков регистров 351-1000. Каждый управляющий выход предыдущего блока 35 регистров является первым управляющим входом для каждого последующего блока 35 регистров. Управляющий выход последнего блока 351000 регистров подключен параллельно к четвертым управляющим входам всех блоков 35 регистров /фиг.2/. Выходами накопителя кодов кадра 15 являются выходы всех блоков 35 регистров, всего выходов 12,8×106/1600×8×1000/. Блоки 35 регистров идентичны, каждый содержит /фиг.3, 4/ первый 36, второй 37 ключи, распределитель 38 импульсов и восемь регистров 391-8, каждый из 1600 разрядов по числу отсчетов в строке. Информационными первым-восьмым входами блока 35 являются поразрядно объединенные через диоды третьи входы разрядов регистров 391-8. Выходами являются ПАРАЛЛЕЛЬНЫЕ выходы всех разрядов восьми регистров 39, которых 12800 /1600×8/, выход каждого разряда подключен и к своему третьему входу после диода. Управляющими входами блока 35 являются: первым - первый управляющий вход Uот первого ключа 36, вторым - сигнальный вход ключа 37, третьим - сигнальный вход ключа 36, четвертым - управляющий вход Uот второго ключа 37. Выход ключа 36 подключен к входу распределителя 38 импульсов, выходы которого, начиная с первого, подключены последовательно к первым /тактовым/ входам разрядов параллельно восьми регистрам 39, последний 1600 выход подключен к второму управляющему Uз входу ключа 36 и к первому управляющему входу Uот ключа 36 в следующем блоке 352 регистров. Емкость накопителя кодов 15-17 /25-27/ кадра составляет 1,6 Мбайт. Получение кода картины выполняется за один кадр /1 сек./. Для воспроизведения изображения на экране 21 длительное время сигналы кодов кадра в блоках 351-1000 регистров /фиг.3, 4/ сохраняются до выключения питания в устройстве 1 кодирования.

Сохранение кодов в регистрах 391-8 выполняется возвращением сигналов при выдаче из регистров 39 вновь в свой разряд, для этого выхода разрядов подключены к третьим входам их после диодов, которые предохраняют от смешивания сигналов. Плоскопанельные экраны 21 и 31 выполнены идентично, каждый содержит элементы матрицы 1,6×106пикселов /1600×1000/. Каждый элемент матрицы формирует пиксел тремя излучающими ячейками, излучающие базовые цвета R, G, B. Общий вид элемента матрицы и его вид сверху на фиг.6 и включает непрозрачный корпус 45 соответствующей формы, объединяющий три излучающие ячейки 46, 47, 48. Левая ячейка 46 излучает красный R цвет, верхняя 47 излучает зеленый G цвет, нижняя правая 48 излучает синий B цвет. Каждая излучающая ячейка содержит /фиг.7, 8/ в переднем торце корпуса 45 микролинзу 49, выполняющую роль микрообъектива, в выходном торце корпуса закреплен цветной светофильтр 50 одного из базовых цветов, между микролинзой 49 и цветным светофильтром 50 расположена диафрагма 51, имеющая цилиндрический корпус 52 с восемью прорезями, в которых расположены восемь нейтральных микросветофильтров 531-8, прикрепленные к своим микропьезоэлементам 541-8 с двумя управляющими входами. Первые торцы микропьезоэлементов 54 с двумя управляющими входами жестко закреплены в корпусе элемента матрицы 45, к вторым свободным концам микропьезоэлементов 54 прикреплены нейтральные микросветофильтры 53, которые в отсутствие управляющих импульсов с блоков 18-20 /20-30/ полностью перекрывают поток излучения от микролинзы 49. Излучающие ячейки работают идентично. Принцип их действия основан на том, что каждый нейтральный микросветофильтр 53 ослабляет поток излучения соответственно весу своего разряда в коде, коэффициенты ослабления приведены в таблице 2. Значения коэффициентов ослабления соответствуют принципу двоичного кода. Микросветофильтры 53 расположены друг за другом по оптической оси микролинзы 49 в порядке уменьшения значений коэффициентов ослабления, нейтральный микросветофильтр 531 с наибольшим коэффициентом расположен первым от микролинзы 49 /фиг.7/. Излучение от источников облучения /подсветки/ сверхяркими светодиодами белого свечения микролинзой 49 направляется сквозь нейтральные микросветофильтры на цветной светофильтр 50 /фиг.7/, придающий излучению соответствующий цвет.Saving codes in registers 391-8 is performed by returning the signals when issuing from registers 39 again to their category, for this output the bits are connected to their third inputs after the diodes, which protect against signal mixing. Flat panel screens 21 and 31 are identical, each containing matrix elements of 1.6 × 106 pixels / 1600 × 1000 /. Each matrix element forms a pixel with three radiating cells emitting the basic colors R, G, B. The general view of the matrix element and its top view in Fig. 6 includes an

Входы микропьезоэлементов 54 являются управляющими входами элемента матрицы и подключены к выходам соответствующих импульсных усилителей 18-20 /28-30/. В отсутствие управляющих импульсов /сигналов единиц кода/ микропьезоэлементы 54 находятся в ненапряженном состоянии, все микросветофильтры 531-8 расположены по оси микролинзы и полностью перекрывают поток излучения. При поступлении управляющего сигнала на микропьезоэлемент 54 его свободный конец изгибается и выводит свой нейтральный микросветофильтр 53 из потока излучения на длительность управляющего импульса 10 мс, чтобы он не перекрывал поток, что соответствует единице в разряде кода, не выведенный из потока микросветофильтр 53 соответствует нулю в разряде кода. При поступлении кода из одних единиц 11111111 из потока выводятся все микросветофильтры 531-8: из ячейки идет максимальное излучение. При поступлении разных кодов из потока излучения выводятся нейтральные микросветофильтры 53, соответствующие единицам в разрядах кода.The inputs of the micropiezoelectric elements 54 are the control inputs of the matrix element and are connected to the outputs of the respective pulse amplifiers 18-20 / 28-30 /. In the absence of control pulses / signals of code units / micro-piezoelectric elements 54 are in an unstressed state, all micro-filters 531-8 are located along the axis of the microlens and completely block the radiation flux. When the control signal arrives at the micropiezoelectric element 54, its free end bends and removes its

В качестве микропьезоэлементов 54 применяются трубчатые пьезоэлементы, работающие на изгиб, прочные и надежные для длительной работы [2 с.27]. Элементы излучающих ячеек выполняются максимально миниатюрными для получения элементов матриц размером 2×2 мм. Излучающие ячейки изготавливаются отдельно и объединяются в корпусе 45 /фиг.6/, а из элементов матрицы набирается экран /фиг.9/. Излучающие ячейки выполняют преобразование "код-яркость излучения". Излучение трех ячеек формирует пиксел яркостью и цветовым тоном соответственно трем кодам R, G, B. Облучение /подсветка/ микролинз 49 элементов матрицы выполняется светодиодами белого свечения, расположенными в соответствующем количестве и в соответствующем порядке на тыльной стороне внутри корпусов экранов 21, 31 таким образом, что каждый светодиод облучает несколько элементов матрицы. Синтезатор 9 частот выдает /фиг.1/ с первого выхода импульсы 1 Гц на открытие ключей 10, 11 на длительность 1 секунды, со второго выхода выдает импульсы 1 кГц частоты строк для считывания сигналов пикселов по строкам, с третьего выхода импульсы 1,6 МГц для считывания сигналов пикселов в строке, с четвертого выхода выдает сигналы Uвыд 100 Гц для выдачи кодов из накопителей 15-17 и 25-27 кодов и с пятого выхода импульс длительностью 1 секунда через включатель SA4 в реле 44 времени.As the micro-piezoelectric elements 54, tubular piezoelectric elements are used, which work on bending, are strong and reliable for long-term operation [2 p. 27]. Elements of radiating cells are made as miniature as possible to obtain

Формирование кода подлинника произведения живописи.Formation of the original code of the painting.

Оригинал картины устанавливается в подготовленное место /фиг.10/ в поле зрения объектива 4. Включается питание устройства 1 кодирования, включается включатель SA2 /фиг.1/, включателем SA5 включается источник 43 света в режим "постоянно" /фиг.10/. Сигнал Uк открывает ключи 10, 11, импульсы дискретизации 1,6 МГц считывают видеосигналы R, G, B пикселов, которые поступают в предварительные усилители 6, 7, 8. АЦП 12, 13, 14 преобразуют видеосигналы в 8-и разрядные коды, поступающие в накопители кодов 15-17, в которых за первый период кадра сосредотачиваются коды кадра. По окончании кадра коды с частотой 100 Гц выдаются в импульсные усилители блоков 18, 19, 20, где сигналы формируются по амплитуде и длительностью 10 мс и поступают в излучающие ячейки экрана 21, на экране 21 появляется изображение картины, которое объективом 4 выводится на максимальную резкость. Включатель SA5 выключается, источник 43 света обесточивается /фиг.10/, выключается питание устройства 1 кодирования. Первый-третий входы блока 3 /фиг.1/ через гнезда разъмных соединений подключаются к первому-третьему выходам устройства 1 кодирования, включается SA1. Реле времени 44 /фиг.10/ имеет два режима работы: первый режим "постоянно" включает источник 43 света на длительное освечивание картины, второй режим "один кадр" включает источник 43 на одну секунду, т.е. на один кадр. Включается питание устройства 1 кодирования, оператор включает SA4, в реле 44 поступает сигнал 1 Гц, источник 43 света облучает картину одну секунду, в ПЗИ 5 считываются видеосигналы кадра, коды с АЦП 12, 13, 14 поступают во флэшь-памяти 32, 33,34. На экране 21 появляется изображение картины, по которому оператор заключает, что в блоке 3 зарегистрированы коды картины подлинника.The original picture is set in the prepared place / Fig. 10/ in the field of view of the

Опознавание картины, претендующей на подлинник.Identification of a picture claiming to be original.

Проверяемая картина устанавливается на место подлинника /фиг.10/. Включаются SA2, питание устройства 1 кодирования, источник 43 света включается в режим "постоянно". На экране 21 появляется изображение картины, которое объективом 4 выводится на максимальную резкость. Затем выключается источник 43 света, выключается питание устройства 1 кодирования, первый-третий выходы блока 3 через гнезда разъемных соединений подключаются к первому-третьему входам блока 2 опознания. Управляющие Uд входы блоков 32, 33, 34 включателем SA1 подключаются к соответствующим выходам разъемных соединений Uд, управляющие входы блоков 22, 23, 24 подключаются включателем SA3 к третьему выходу синтезатора 9 частот, включается включатель SA2. Реле 44 времени ставится в режим "один кадр". Включается питание устройства 1 кодирования, оператор включает SA4: реле 44 включает источник 43 света на один кадр. АЦП 12, 13, 14 выдают коды, которые поступают в накопители 15-17 кодов кадра и в блоки 22, 23, 24 сравнения в регистры 40 /фиг.5/. Сигналы Uд поступают на соответствующие входы флэшь-памяти 32, 33, 34 и выдают коды подлинника на входы через разъемные соединения 1-3 блоков 22, 23, 24 сравнения, которые выполняют сравнение кодов R, G, B проверяемой картины с АЦП 12-14 с кодами подлинника с блока 3. Результаты разницы кодов поступают в накопители 25-27 кодов кадра и отображаются на экране 31. При полном совпадении кодов на экране 31 изображение отсутствует, при частичном несовпадении кодов на экране 31 будет искаженное изображение, либо его отрывки, что и будет наблюдаться присутствующими. Заявляемое устройство может быть использовано для проведения цифровой паспортизации подлинников картин в музеях и в частных коллекциях, а поступающие картины проверять на подлинность.Checked picture is installed in place of the original / Fig.10/. Turns on SA2, the power of the

Использованные источникиUsed sources

1. Колесниченко О.В, Шишигин И.В. Аппаратные средства PC. 5-е изд-е, СПб, 2004, с.832-833.1. Kolesnichenko O.V., Shishigin I.V. PC hardware. 5th ed., St. Petersburg, 2004, p. 832-833.

2. А.Ф.Плонский, В.И.Теаро. Пьезоэлектроника. М., 1979, с.27.2. A.F. Plonsky, V.I. Thearo. Piezoelectronics. M., 1979, p. 27.

3. Гук М.Ю. Аппаратные средства IBM PC. Энциклопедия, 3-е. изд., СПб., 2006, с.415.3. Guk M.Yu. Hardware IBM PC. Encyclopedia, 3rd. ed., St. Petersburg., 2006, p. 415.

4. В.В.Фролов. Язык радиосхем. Изд-е 2-е. М., 1989, с.56 фиг.99 а.4. V.V. Frolov. The language of the radio circuits. 2nd ed. M., 1989, p. 56 Fig. 99 a.

Claims (1)

Translated fromRussianPriority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| RU2011112524/08ARU2447500C1 (en) | 2011-04-01 | 2011-04-01 | Device for identification of painting original |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| RU2011112524/08ARU2447500C1 (en) | 2011-04-01 | 2011-04-01 | Device for identification of painting original |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| RU2447500C1true RU2447500C1 (en) | 2012-04-10 |

Family

ID=46031810

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| RU2011112524/08ARU2447500C1 (en) | 2011-04-01 | 2011-04-01 | Device for identification of painting original |

Country Status (1)

| Country | Link |

|---|---|

| RU (1) | RU2447500C1 (en) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN112834507A (en)* | 2020-12-31 | 2021-05-25 | 易旻 | Uniqueness identification system and method based on image registration and spectrum identification |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| RU2205450C1 (en)* | 2001-10-11 | 2003-05-27 | Осипов Игорь Алексеевич | Method for authenticating antiques |

| RU92736U1 (en)* | 2009-11-13 | 2010-03-27 | Сергей Игоревич Котельников | DEVICE FOR CERTIFICATE THE AUTHENTICITY OF VALUABLE ITEMS |

| RU2385492C2 (en)* | 2004-03-12 | 2010-03-27 | Инджениа Текнолоджи Лимитед | Methods, articles and devices for verification of authenticity |

| EP2175396A2 (en)* | 2005-12-23 | 2010-04-14 | Ingenia Holdings (UK)Limited | Optical authentication |

- 2011

- 2011-04-01RURU2011112524/08Apatent/RU2447500C1/enactive

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| RU2205450C1 (en)* | 2001-10-11 | 2003-05-27 | Осипов Игорь Алексеевич | Method for authenticating antiques |

| RU2385492C2 (en)* | 2004-03-12 | 2010-03-27 | Инджениа Текнолоджи Лимитед | Methods, articles and devices for verification of authenticity |

| EP2175396A2 (en)* | 2005-12-23 | 2010-04-14 | Ingenia Holdings (UK)Limited | Optical authentication |

| RU92736U1 (en)* | 2009-11-13 | 2010-03-27 | Сергей Игоревич Котельников | DEVICE FOR CERTIFICATE THE AUTHENTICITY OF VALUABLE ITEMS |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN112834507A (en)* | 2020-12-31 | 2021-05-25 | 易旻 | Uniqueness identification system and method based on image registration and spectrum identification |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1212669C (en) | Solid photographing device and solid photographing component | |

| US20170187936A1 (en) | Image sensor configuration | |

| RU2447500C1 (en) | Device for identification of painting original | |

| RU2369041C1 (en) | Stereo-television system | |

| RU2452026C1 (en) | Image digitisation method and apparatus for realising said method | |

| RU2358412C1 (en) | Video camera | |

| RU2334369C1 (en) | Stereoscopic television system | |

| RU2326508C1 (en) | Stereo television system | |

| CN110138998A (en) | Image scan method and imaging sensor | |

| RU2477008C1 (en) | Video camera | |

| RU2320095C1 (en) | Flat panel display | |

| RU2356179C1 (en) | System of stereotelevision | |

| RU2420025C1 (en) | System of stereophonic television | |

| RU2428812C1 (en) | Video camera | |

| RU2390104C1 (en) | Flat panel display | |

| RU2368097C1 (en) | Television system | |

| RU2401450C1 (en) | Control system | |

| RU2402052C1 (en) | Code to radiation brightness converter | |

| RU2384010C1 (en) | Stereo television system | |

| RU2351094C1 (en) | Stereotelevision system | |

| RU2481726C1 (en) | Universal television system | |

| RU2334370C1 (en) | Stereoscopic television system | |

| RU2483466C1 (en) | Universal television system | |

| RU2384012C1 (en) | Stereo television system | |

| RU2339183C1 (en) | Television system |