KR20150020136A - Translation layer partitioned between host and controller - Google Patents

Translation layer partitioned between host and controllerDownload PDFInfo

- Publication number

- KR20150020136A KR20150020136AKR20140105759AKR20140105759AKR20150020136AKR 20150020136 AKR20150020136 AKR 20150020136AKR 20140105759 AKR20140105759 AKR 20140105759AKR 20140105759 AKR20140105759 AKR 20140105759AKR 20150020136 AKR20150020136 AKR 20150020136A

- Authority

- KR

- South Korea

- Prior art keywords

- data

- volatile memory

- host

- read

- page

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/0223—User address space allocation, e.g. contiguous or non contiguous base addressing

- G06F12/023—Free address space management

- G06F12/0238—Memory management in non-volatile memory, e.g. resistive RAM or ferroelectric memory

- G06F12/0246—Memory management in non-volatile memory, e.g. resistive RAM or ferroelectric memory in block erasable memory, e.g. flash memory

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/08—Error detection or correction by redundancy in data representation, e.g. by using checking codes

- G06F11/10—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's

- G06F11/1076—Parity data used in redundant arrays of independent storages, e.g. in RAID systems

- G06F11/108—Parity data distribution in semiconductor storages, e.g. in SSD

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/04—Addressing variable-length words or parts of words

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0602—Interfaces specially adapted for storage systems specifically adapted to achieve a particular effect

- G06F3/0608—Saving storage space on storage systems

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0628—Interfaces specially adapted for storage systems making use of a particular technique

- G06F3/0638—Organizing or formatting or addressing of data

- G06F3/064—Management of blocks

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0668—Interfaces specially adapted for storage systems adopting a particular infrastructure

- G06F3/0671—In-line storage system

- G06F3/0673—Single storage device

- G06F3/0679—Non-volatile semiconductor memory device, e.g. flash memory, one time programmable memory [OTP]

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/0223—User address space allocation, e.g. contiguous or non contiguous base addressing

- G06F12/0292—User address space allocation, e.g. contiguous or non contiguous base addressing using tables or multilevel address translation means

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/10—Providing a specific technical effect

- G06F2212/1016—Performance improvement

- G06F2212/1024—Latency reduction

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/40—Specific encoding of data in memory or cache

- G06F2212/401—Compressed data

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/72—Details relating to flash memory management

- G06F2212/7201—Logical to physical mapping or translation of blocks or pages

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/72—Details relating to flash memory management

- G06F2212/7208—Multiple device management, e.g. distributing data over multiple flash devices

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Human Computer Interaction (AREA)

- Quality & Reliability (AREA)

- Techniques For Improving Reliability Of Storages (AREA)

- Memory System (AREA)

- Information Retrieval, Db Structures And Fs Structures Therefor (AREA)

Abstract

Translated fromKoreanDescription

Translated fromKorean본원은 2013년 10월 21일 출원된 미국 가출원 제61/893,383호, 2013년 10월 9일 출원된 미국 가출원 제61/888,681호, 2013년 9월 3일 출원된 미국 가출원 제61/873,357호, 2013년 8월 16일 출원된 미국 가출원 제61/866,672호, 및 2013년 1월 22일 출원된 미국 가출원 제61/755,169호에 관한 것이며, 이들 각각은 그들 전체 내용이 참조로서 본 명세서에 포함된다.This application is a continuation-in-part of U.S. Provisional Application No. 61 / 893,383, filed October 21, 2013, U.S. Provisional Application No. 61 / 888,681, filed October 9, 2013, U.S. Provisional Application No. 61 / 873,357, filed September 3, U.S. Provisional Application No. 61 / 866,672, filed August 16, 2013, and U.S. Provisional Application No. 61 / 755,169, filed January 22, 2013, each of which is incorporated herein by reference in its entirety .

본원은 2010년 3월 22일 출원된 미국 가출원 제61/316,373호와 관련된, 2011년 3월 21일에 출원된 미국 출원번호 제13/053,175호에 관한 것이며, 이들 각각은 그들 전체 내용이 참조로서 본 명세서에 포함된다.This application is related to U.S. Serial No. 13 / 053,175, filed on March 21, 2011, which is related to U.S. Provisional Application No. 61 / 316,373, filed March 22, 2010, each of which is incorporated herein by reference in its entirety Are included herein.

또한, 본원은 2011년 10월 5일 출원된 미국 가출원 제61/543,707호에 대한 우선권을 주장하는, 2012년 10월 4일에 국제출원된 국제출원번호 PCT/US2012/058583호에 관한 것이며, 이들 각각은 그들 전체 내용이 참조로서 본 명세서에 포함된다.This application is also related to International Application No. PCT / US2012 / 058583, filed October 4, 2012, which claims priority to U.S. Provisional Application No. 61 / 543,707, filed October 5, 2011, Each of which is incorporated herein by reference in its entirety.

본원은 2011년 9월 6일 출원된 미국 가출원 제61/531,551호 및 2011년 8월 9일 출원된 미국 가출원 제61/521,739에 대한 우선권을 주장하는, 2012년 8월 8일에 국제출원된 국제출원번호 PCT/US2012/049905호와 관련된, 2013년 7월 10일 출원된 미국 출원번호 제13/936,010호에 관한 것이며, 이들 각각은 그들 전체 내용이 참조로서 본 명세서에 포함된다.This application claims priority to U.S. Provisional Application No. 61 / 531,551, filed September 6, 2011, and U.S. Provisional Application No. 61 / 521,739, filed on August 9, 2011, No. 13 / 936,010, filed July 10, 2013, which is related to Application No. PCT / US2012 / 049905, each of which is incorporated herein by reference in its entirety.

본 발명은 일반적으로 컴퓨팅 호스트 및 입/출력 디바이스 기술에 관한 것이며, 보다 구체적으로는, 호스트와 컨트롤러 간에 파티셔닝된 변환 계층을 제공하는 방법 및/또는 장치에 관한 것이다.

The present invention relates generally to computing hosts and input / output device technologies, and more particularly to a method and / or apparatus for providing a partitioned translation layer between a host and a controller.

종래의 솔리드-스테이트 드라이브(solid-state drive; SSD)는 비휘발성 메모리의 각 페이지에 일정한, 정수 개의 호스트 논리 블록들을 저장한다. 비휘발성 메모리의 각 페이지에 대한 사용자 데이터 사이즈 또는 사용가능한 사이즈가 일정하지 않은 경우, 저장 효율 문제들이 발생하게 된다. 솔리드-스테이트 드라이브들 내의 가변 사이즈 플래시 변환 계층용 아키텍처들은 하드웨어 집중적이다. 페이지 헤더(page header)들은 솔리드-스테이트 드라이브의 페이지들 내에 존재하는 복수의 판독 유닛들 중에서 사용자 데이터가 저장되는 장소를 식별하는데 사용되며, 데이터의 추출은 먼저 이 페이지 헤더들을 판독 및 파싱하는 것을 포함한다.

A conventional solid-state drive (SSD) stores an integer number of host logical blocks in each page of non-volatile memory. If the user data size or usable size for each page of non-volatile memory is not constant, storage efficiency problems will occur. The architectures for the variable size flash translation layer in solid-state drives are hardware-intensive. The page headers are used to identify where the user data is stored among the plurality of read units present in the pages of the solid-state drive, and the extraction of data includes first reading and parsing these page headers do.

본 발명은 파티셔닝된 플래시 변환 계층을 사용하는 방법에 관한 것이다. 단계 (A)는, 호스트로부터의 장치에서, 제 1 기록 데이터를 가진 기록 커맨드를 수신한다. 단계 (B)는 상기 장치에서 제 1 기록 데이터를 압축함으로써 제 2 기록 데이터를 생성한다. 일반적으로, 제 2 기록 데이터는 가변 사이즈를 갖는다. 단계 (C)는 비휘발성 메모리의 물리적 위치에서 제 2 기록 데이터를 저장한다. 물리적 위치는 다음의 기록되지 않은 위치이다. 단계 (D)는, 기록 커맨드에 대한 응답으로, 장치에서 호스트로, 물리적 위치의 표시를 반환한다.

The present invention relates to a method of using a partitioned flash translation layer. Step (A) receives, from the host, a write command having the first write data. Step (B) generates second recording data by compressing the first recording data in the apparatus. Generally, the second recording data has a variable size. Step (C) stores the second record data at the physical location of the non-volatile memory. The physical location is the next unrecorded location. Step (D) returns an indication of the physical location from the device to the host, in response to the write command.

본 발명의 실시예들은 다음의 상세한 설명 및 첨부된 청구항들과 도면들로부터 명백하게 될 것이다.

도 1은 비휘발성 메모리 페이지 내의 고정-사이즈 영역들에 논리 블록 어드레스를 맵핑하는 일 실시예의 선택된 상세 도면이다.

도 2는 선택적으로 비휘발성 메모리 페이지들을 스패닝하는 가변-사이즈 영역에 논리 블록 어드레스를 맵핑하는 일 실시예의 선택된 상세 도면이다.

도 3은 정수 개의 판독 유닛들을 포함하는 비휘발성 메모리 페이지에 대한 일 실시예의 도면이다.

도 4는 하나 이상의 판독 유닛들을 스패닝하는 가변-사이즈 영역에 논리 블록 어드레스를 맵핑하는 일 실시예의 선택된 상세 도면이다.

도 5는 헤더들 및 데이터를 포함하는 판독 유닛에 대한 일 실시예의 선택된 상세 도면이다.

도 6은 헤더들 및 데이터를 포함하는 비휘발성 메모리 페이지에 대한 일 실시예의 선택된 상세 도면이다.

도 7은 헤더들 및 데이터를 포함하는 비휘발성 메모리 페이지에 대한 다른 실시예의 선택된 상세 도면이다.

도 8은 각종 타입의 헤더들에 대한 일 실시예의 선택된 상세 도면이다.

도 9는 맵 엔트리에 대한 일 실시예의 선택된 상세 도면이다.

도 10은 각종 압축된 맵 엔트리들에 대한 일 실시예의 선택된 상세 도면이다.

도 11a는 솔리드-스테이트 드라이브 컨트롤러에 대한 일 실시예의 선택된 상세 도면이다.

도 11b는 데이터 경로 세그먼트에 대한 일 실시예의 선택된 상세 도면이다.

도 11c는 본 발명의 일 실시예에 따른 시스템에 대한 각종 실시예들의 선택된 상세 도면이다.

도 12는 비휘발성 메모리에 데이터를 기록하는 흐름도이다.

도 13은 비휘발성 메모리로부터 데이터를 판독하는 흐름도이다.

도 14는 비휘발성 메모리에서 데이터를 리사이클링하는 흐름도이다.Embodiments of the invention will become apparent from the following detailed description and the appended claims and drawings.

Figure 1 is a selected detail of one embodiment of mapping a logical block address to fixed-size regions within a non-volatile memory page.

FIG. 2 is a selected detail of one embodiment of mapping a logical block address to a variable-size area that optionally spans non-volatile memory pages.

3 is a diagram of an embodiment of a non-volatile memory page including an integer number of read units.

4 is a selected detail of one embodiment of mapping a logical block address to a variable-size area spanning one or more read units.

5 is a selected detailed view of one embodiment of a reading unit that includes headers and data.

6 is a selected detailed view of one embodiment of a non-volatile memory page containing headers and data.

Figure 7 is a selected detail of another embodiment of a non-volatile memory page that includes headers and data.

Figure 8 is a selected detail of one embodiment of various types of headers.

Figure 9 is a selected detail view of an embodiment of a map entry.

10 is a selected detailed view of one embodiment of various compressed map entries.

11A is a selected detail view of an embodiment of a solid-state drive controller.

11B is a selected detail view of an embodiment of a data path segment.

11C is a selected detail of various embodiments of a system according to an embodiment of the present invention.

12 is a flowchart for recording data in a nonvolatile memory.

13 is a flowchart for reading data from a non-volatile memory.

14 is a flow chart for recycling data in a non-volatile memory.

본 발명의 실시예들은 (i) 광범위한 데이터 사이즈들을 지원할 수 있고, (ii) 비-블록 기반 데이터로 동작할 수 있고, (iii) 데이터 기록에 대한 응답으로 호스트에게 핸들(handle)을 반환할 수 있고, (iv) 그 핸들을 이용하여 데이터를 판독할 수 있고/있거나, (v) 하나 이상의 집적 회로들 및/또는 관련 펌웨어 구현될 수 있는, 호스트와 컨트롤러 간에 파티셔닝된 변환 계층을 제공하는 것을 포함한다.Embodiments of the present invention may be used to (i) support a wide range of data sizes, (ii) operate with non-block based data, and (iii) return a handle to the host in response to the data write. (Iv) read and / or read data using its handle, or (v) provide a partitioned translation layer between a host and a controller, which may be implemented on one or more integrated circuits and / or associated firmware do.

호스트는 입/출력 디바이스(예를 들면, 솔리드-스테이트 드라이브(예컨대, SSD) 컨트롤러)에 커플링되고, 입/출력 디바이스는 비휘발성 메모리(예컨대, NVM)에 커플링되고/되거나 이를 포함한다. 호스트의 예들로는 컴퓨팅 호스트, 서버, 개인용 컴퓨터, 랩탑 컴퓨터, 노트북 컴퓨터, 워크스테이션 컴퓨터, PDA(personal digital assistant), 스마트폰, 셀룰러 핸드셋, 미디어 플레이어 or 레코더, 입/출력 컨트롤러, RAID(redundant array of inexpensive/independent disks)-온-칩(예컨대, ROC) 컨트롤러, 및 프로세서 또는 컴퓨터를 포함하는 임의의 다른 디바이스들을 포함한다. 호스트는 입/출력 디바이스를 통해 비휘발성 메모리에 액세스하기 위한(예컨대, 판독 또는 기입을 위한) 요청들을 발생시키며, 이 요청들은 호스트의 조합에 의해(예컨대, 적어도 부분적으로는 호스트에서 실행되는 소프트웨어에 의해) 그리고 입/출력 디바이스에 의해(예컨대, 적어도 부분적으로는 입/출력 디바이스에서 실행되는 펌웨어에 의해) 수행된다.The host is coupled to an input / output device (e.g., a solid-state drive (e.g., SSD) controller) and the input / output device is coupled to and / or included in a non-volatile memory (e.g., NVM). Examples of the host include a computing host, a server, a personal computer, a laptop computer, a laptop computer, a workstation computer, a personal digital assistant (PDA), a smart phone, a cellular handset, a media player or recorder, inexpensive / independent disks-on-chip (e.g., ROC) controller, and any other device including a processor or computer. A host generates requests (e.g., for reading or writing) to access a non-volatile memory through an input / output device, which requests are made by a combination of hosts (e.g., at least partially in software running on the host And by the input / output device (e.g., by firmware running at least partially on the input / output device).

몇몇 실시예들에서, 플래시 변환 계층들(예컨대, FTL들)은 (예컨대, 입/출력 디바이스에 대한 입/출력 동작들을 수행하기 위해 호스트에 의해 사용되는) 논리 블록 어드레스 공간 내의 논리 블록 어드레스들(예컨대, LBA들)을, NAND 플래시 비휘발성 메모리와 같은 비휘발성 메모리 내의 물리적 위치들(예컨대, 물리적 어드레스 공간 내의 물리적 저장 어드레스들)로 맵핑(변환)할 수 있다. 각종 실시예들에 따르면, 논리 블록 어드레스 공간 내의 논리 블록 어드레스의 맵핑은 1-레벨 맵; 2-레벨 맵; 멀티-레벨 맵; 다이렉트 맵; 연관 맵; 해시 테이블; B-트리; 트라이(trie); 맵의 일부분의 캐시; 및 논리 블록 어드레스들을 비휘발성 메모리 내의 물리적 위치들에 연관시키는 임의의 다른 수단 중의 하나 이상을 통한 것이다. 다른 실시예들에서, 맵은 예컨대, 하나의 엔트리가 논리 블록 어드레스 공간 내의 각 논리 블록 어드레스에 대한 것인, 복수의 엔트리들을 포함한다.In some embodiments, flash translation layers (e.g., FTLs) may be used to provide logical block addresses (e. G., FTLs) within a logical block address space (e. G., Used by a host to perform input / output operations on input / (E.g., LBAs) to physical locations (e.g., physical storage addresses within a physical address space) in a non-volatile memory such as a NAND flash non-volatile memory. According to various embodiments, the mapping of the logical block address within the logical block address space is performed by a one-level map; Two-level map; Multi-level map; Direct Map; Association map; Hash table; B-tree; Trie; Cache of a portion of the map; And any other means of associating the logical block addresses with the physical locations in the non-volatile memory. In other embodiments, the map includes a plurality of entries, e.g., one entry is for each logical block address in the logical block address space.

다른 실시예들에서, 플래시 변환 계층들은 각각의 데이터에 대한 라벨들 또는 그 밖의 고유의 식별자들을, 비휘발성 메모리 내의 물리적 위치들로 맵핑한다. 예를 들어, 라벨은 각각의 데이터에 대한 해시(예컨대, SHA-256 또는 SHA-512 해시), 또는 각각의 데이터로서 또는 그에 저장된 각각의 객체에 대한 객체 식별자, 또는 각각의 데이터에 대한 파일 시스템 식별자(예컨대, 아이노드)(각각의 데이터가 파일 시스템 객체인 경우)일 수 있다. 각종 실시예들에 따르면, 각각의 데이터의 라벨들 또는 다른 고유 식별자들의 맵핑은, 1-레벨 맵; 2-레벨 맵; 멀티-레벨 맵; 다이렉트 맵; 연관 맵; 해시 테이블; B-트리; 트라이; 맵의 일부분의 캐시; 및 이 라벨들 또는 다른 고유 식별자들을 비휘발성 메모리의 물리적 위치들 내에 연관시키는 임의의 다른 수단 중의 하나 이상을 통한 것이다. 다른 실시예들에서, 맵은 예컨대, 하나의 엔트리가 각각의 현존 라벨 또는 다른 고유 식별자에 대한 것인, 복수의 엔트리들을 포함한다. 또 다른 실시예들에서, 맵은 크기가 동적이며, 현존 라벨들 또는 다른 고유 식별자들이 증가하거나 감소함에 따라, 커지거나 작아진다. 일 예에서는, 현존 라벨들 또는 다른 고유 식별자들의 수가 증가하거나 감소함에 따라, 맵 사이즈는 선형적으로 커지거나 작아진다. 다른 예에서, 현존 라벨들 또는 다른 고유 식별자들의 수가 각각의 임계값보다 많이 증가하거나 감소함에 따라, 단계적-방식으로(개별 양으로) 커지거나 작아진다.In other embodiments, the flash translation layers map the labels or other unique identifiers for each piece of data to physical locations in the non-volatile memory. For example, the label may be a hash for each data (e.g., SHA-256 or SHA-512 hash), or an object identifier for each object stored as or as each data, or a file system identifier (E.g., an inode) (if each piece of data is a filesystem object). According to various embodiments, the mapping of the labels or other unique identifiers of each data may be performed using a one-level map; Two-level map; Multi-level map; Direct Map; Association map; Hash table; B-tree; try; Cache of a portion of the map; And any other means of associating these labels or other unique identifiers within the physical locations of the non-volatile memory. In other embodiments, the map includes a plurality of entries, e.g., one entry is for each existing label or other unique identifier. In yet other embodiments, the map is dynamic in size and increases or decreases as existing labels or other unique identifiers increase or decrease. In one example, as the number of existing labels or other unique identifiers increases or decreases, the map size linearly increases or decreases. In another example, the number of existing labels or other unique identifiers is increased or decreased (in a discrete amount) in a step-by-step manner as the number of individual thresholds increases or decreases.

각종 실시예들에서, 멀티-레벨 맵은 고유 식별자들을 제공하고/하거나 고유 식별자들의 범위를 제한하는데 사용된다. 예를 들어, 제 1 연관 맵에서 라벨을 조회하여 그 라벨보다 길이가 짧은 고유 식별자를 생성한다. 이어서, 제 2 맵에서 고유 식별자를 조회하여, 비휘발성 메모리 내의 물리적 위치를 생성한다. 다른 실시예들에서, 제 2 맵은 예컨대, 하나의 맵이 비휘발성 메모리의 복수의 물리적으로 분리된 부분들(예컨대, 상이한 솔리드-스테이트 디스크들에 존재하는) 및/또는 기능적으로 상이한 부분들(예컨대, 상이한 타입들)의 각각에 대한 것인, 복수의 맵들이다.In various embodiments, the multi-level map is used to provide unique identifiers and / or to limit the range of unique identifiers. For example, a label is searched in the first association map, and a unique identifier having a shorter length than the label is generated. Then, a unique identifier is inquired in the second map, and a physical location in the nonvolatile memory is generated. In other embodiments, the second map may include, for example, a map that includes a plurality of physically separate portions of non-volatile memory (e.g., residing in different solid-state disks) and / or functionally different portions For example, different types). ≪ / RTI >

복수의 라벨들(또는 핸들들 또는 논리 블록 어드레스들 또는 식별자들 또는 그 밖의 유사한 용어들)의 각각은 일반적으로 각각의 데이터 객체(또는 섹터 또는 블록 또는 아이템 또는 그 밖의 유사한 용어들)에 대응하고, 플래시 변환 계층은 그 라벨들 각각을 대응하는 데이터 객체의 비휘발성 메모리 내 물리적 위치와 연관시킨다. 라벨과 대응하는 데이터 객체의 비휘발성 메모리 내 물리적 위치의 연관은 그 연관이 수행되는 방식과 관계없이, 맵을 통해 이루어지는 것으로 알려져 있다. 본 명세서의 각종 예들이 논리 블록 어드레스들의 맵핑을 사용하고 또한 다른 예들이 객체 라벨들이나 객체 식별자들의 맵핑을 사용하지만, 다수의 유사한 데이터 라벨링 기술들이 관련 맵핑 기술들과 함께 본원의 교시의 사상 내에서 사용될 수 있다.Each of a plurality of labels (or handles or logical block addresses or identifiers or other similar terms) generally corresponds to each data object (or sector or block or item or other similar terms) The flash translation layer associates each of its labels with the physical location in the non-volatile memory of the corresponding data object. It is known that the association of the label with the physical location of the corresponding data object in the non-volatile memory is made through the map, regardless of the manner in which the association is performed. While various examples herein use mapping of logical block addresses and also other examples use object labels or mapping of object identifiers, a number of similar data labeling techniques, along with associated mapping techniques, may be used within the teachings of the present teachings .

본 명세서에서 사용되는 용어 "맵핑 유닛(mapping unit)"은 플래시 변환 계층에 의해 맵핑되어 있는 데이터 객체들의 사이즈를 지칭한다. 몇몇 실시예들에서, 맵핑 유닛은 고정 사이즈이며, 다른 실시예들에서, 데이터 객체들은 가변 사이즈이다(따라서 이 맵핑 유닛들은 고정 사이즈가 아니다).As used herein, the term "mapping unit" refers to the size of data objects that are mapped by the flash translation layer. In some embodiments, the mapping unit is of fixed size, and in other embodiments, the data objects are of variable size (thus, these mapping units are not of fixed size).

몇몇 실시예들에서, 맵핑은 하나 이상의 논리 섹터들 또는 블록들의 정렬된 유닛들 상에서 동작한다. 각 맵핑 유닛은 하나 이상의 논리 섹터들 또는 블록들의 정렬된 유닛이다. 각각의 맵핑 유닛은 그 맵핑 유닛의 데이터가 저장되는(맵핑 유닛이 기록되지 않았거나 트리밍(trimming)된 경우의 NULL 물리적 위치 가능성을 포함) 대응하는 물리적 위치를 갖는다. 예를 들어, 4 킬로바이트(예컨대, KB) 맵핑 유닛들에 있어서, 8개의 인접한(및 통상적으로 8개-섹터가 정렬된) SATA(Serial Advanced Technology Attachment) 512 바이트 섹터들이 단일 유닛으로서 맵핑된다. 일반적으로, 논리 블록 어드레스들에 대한 맵은, 맵핑 유닛과 연관된 논리 블록 어드레스로부터 비휘발성 메모리 내의 물리적 어드레스로의 각각의 변환 및/또는 제어 정보를 저장하기 위하여, 맵핑 유닛마다 하나의 엔트리를 갖는다.In some embodiments, the mapping operates on aligned units of one or more logical sectors or blocks. Each mapping unit is an aligned unit of one or more logical sectors or blocks. Each mapping unit has a corresponding physical location in which the data of the mapping unit is stored (including the NULL physical location possibility when the mapping unit is not recorded or trimming). For example, for 4 kilobyte (e.g., KB) mapping units, eight adjacent (and typically eight-sector aligned) SATA (Serial Advanced Technology Attachment) 512 byte sectors are mapped as a single unit. Generally, a map for logical block addresses has one entry per mapping unit, to store each translation and / or control information from a logical block address associated with the mapping unit to a physical address in the non-volatile memory.

각종 실시예들에서, 맵핑되어 있는 데이터 객체들의 사이즈(각 맵핑 유닛의 사이즈) 및/또는 비휘발성 메모리에 저장되는 데이터 객체들의 사이즈는 달라진다. 일 예에서, 맵 내의 각 엔트리들은 각각의 데이터 객체의 사이즈를 저장한다. 이 예에 대해 계속하면, 키/값 저장에서, 키에 따라 저장된 맵의 엔트리에 액세스하기 위하여 라벨이 사용되며, 이 값은 각각의 데이터 객체로서, 키들의 상이한 객체들 간에서 사이즈가 달라진다. 다른 예에서, 맵 내의 각각의 엔트리들은 저장된 데이터 객체를 검색하기 위하여 판독할 비휘발성 메모리에 대한 양의 표시를 저장한다. 다른 예의 변형에서, 맵의 엔트리에 의해 명시된 양의 비휘발성 메모리는, 상기 맵의 엔트리에 의해 명시된 양의 비휘발성 메모리 내의 하나 이상의 저장되어 있는 데이터 객체들 또는 그 일부들 중에서 각각의 저장되어 있는 데이터 객체의 위치를 탐색하는 헤더(header)들을 포함한다. 다른 예의 다른 변형에서, 각각의 데이터 객체를 검색하기 위하여 판독할 상기 양의 비휘발성 메모리는, 비휘발성 메모리의 페이지 내의 각각의 저장되어 있는 데이터 객체에 대한 정확한 사이즈 및 위치를 명시하지만, 비휘발성 메모리 오류 정정과는 관계가 없다. 추가적인 연산들이 사용되어 각각의 저장되어 있는 데이터 객체 및 비휘발성 메모리로부터 데이터 판독에 대한 오류 정정을 수행하는데 충분한 다른 정보를 검색하기 위하여 판독할 더 큰 양의 비휘발성 메모리를 결정한다.In various embodiments, the size of the mapped data objects (the size of each mapping unit) and / or the size of the data objects stored in the non-volatile memory are different. In one example, each entry in the map stores the size of each data object. Continuing with this example, in key / value storage, a label is used to access an entry of the saved map according to the key, which is the size of each data object, among different objects of the keys. In another example, each entry in the map stores a positive indication of the non-volatile memory to read to retrieve the stored data object. In a variation on another example, the amount of non-volatile memory specified by an entry in the map may be determined based on the stored data of each of the one or more stored data objects or portions thereof in the amount of non-volatile memory specified by the entry in the map And includes headers that search for the location of the object. In another variation of the other example, the positive non-volatile memory to read to retrieve each data object specifies the exact size and location for each stored data object in the page of non-volatile memory, It has nothing to do with error correction. Additional operations are used to determine a larger amount of nonvolatile memory to read to retrieve each stored data object and other information sufficient to perform error correction for reading data from the nonvolatile memory.

각종 실시예들에 따르면, 비휘발성 메모리는 셀당 1 비트(예컨대, 단일-레벨 셀), 2 비트(예컨대, 멀티-레벨 셀), 3 비트(예컨대, 트리플-레벨 셀), 또는 그 이상의 비트를 저장하며, 평면형(2-차원) 또는 3-차원형(예컨대, 3D)인 NAND 플래시; NOR 플래시; 임의의 다른 타입의 플래시 메모리 또는 전기적 소거가능 메모리; PCM(phase change memory); MRAM(magnetic random access memory); 레이스트랙 메모리; ReRAM(resistive random access memory); 배터리 구동형(battery-backed) SRAM(static random access memory) 또는 DRAM(dynamic random access memory); 임의의 자기 또는 광 저장 매체; 또는 임의의 다른 비휘발성 메모리 중의 하나 이상이다.According to various embodiments, a non-volatile memory may store one bit per cell (e.g., a single-level cell), two bits (e.g., a multi-level cell), three bits NAND flash, which is planar (two-dimensional) or three-dimensional (e.g., 3D); NOR Flash; Any other type of flash memory or electrically erasable memory; Phase change memory (PCM); Magnetic random access memory (MRAM); Race track memory; Resistive random access memory (ReRAM); Battery-backed static random access memory (SRAM) or dynamic random access memory (DRAM); Any magnetic or optical storage medium; Or any other non-volatile memory.

몇몇 실시예들에서, 비휘발성 메모리는, 예를 들어 상이한 입/출력 디바이스들에서(예컨대, 상이한 솔리드-스테이트 디스크들에서) 물리적으로 분리되는 것에 의해, 또는 상이한 물리적 위치들이나 액세스 메커니즘들을 갖는 것(예컨대, 비휘발성 메모리의 일부분이 NAND 플래시이고, 제 2 부분이 상 변화 메모리)에 의해, 하나 이상의 그룹들로 구성된다. 이 실시예들의 일부에서는, 맵은, 각 엔트리가 해당 입/출력 디바이스의 입/출력 디바이스 식별자(예컨대, ID) 및 물리적 위치를 명시하는 글로벌 맵(global map)이다. 다른 실시예들에서, 맵은 복수의 부분들, 예를 들어 입/출력 디바이스마다 하나의 부분으로 파티셔닝되며, 각각의 라벨의 기능 및/또는 상위-레벨 맵은 입/출력 디바이스들 중의 선택된 것을 결정한다.In some embodiments, the non-volatile memory may be physically separated, e.g., in different I / O devices (e.g., in different solid-state disks), or with different physical locations or access mechanisms For example, a portion of non-volatile memory is a NAND flash, and a second portion is a phase change memory). In some of these embodiments, the map is a global map in which each entry specifies an input / output device identifier (e.g., ID) and physical location of the corresponding input / output device. In other embodiments, the map is partitioned into a plurality of portions, e.g., one portion per input / output device, and the function and / or top-level map of each label determines the selected one of the input / output devices do.

NAND 플래시와 같은 일부 비휘발성 메모리들은 비휘발성 메모리 페이지로 호칭되는 기록가능한(또는 프로그램가능한) 유닛(또는 예를 들어 NAND 플래시를 지칭하는 경우에는 플래시 페이지)를 제공한다. 일반적으로, 비휘발성 메모리 페이지는 비휘발성 메모리의 최소 기록가능한 유닛이다. 몇몇 실시예들 및/또는 사용 시나리오들에서, 비휘발성 메모리 페이지는 다량의 사용자(비-오류 정정 코드) 데이터 바이트들 및 메타-데이터와 오류 정정 코딩(예컨대, ECC)을 위한 스페어 공간의 양을 포함한다. 통상적인 NAND 플래시 페이지 사이즈는 8 KB 또는 16 KB 또는 32 KB의 사용자 데이터인 반면, 논리 블록 어드레스들을 위한 통상적인 맵핑 유닛 사이즈는 4 KB 또는 8 KB이다. (용어 "사용자" 데이터는 비휘발성 메모리 페이지에 대해 사용되며, 일부 비휘발성 메모리 페이지들은 맵 데이터 및/또는 체크포인트 데이터와 같은 "시스템" 데이터를 저장한다. 사용자 데이터는 일반적으로 비휘발성 메모리 페이지의 비-오류 정정 코딩 부분들을 지칭하는 것으로 의도된다.) NAND 플래시 페이지들은 블록들로 구성되며, 통상적으로는 블록당 128, 256, 또는 512 플래시 페이지들이다. 블록은 소거가능한 최소-사이즈 유닛이며, NAND 플래시 페이지는 그 페이지가 (재)기록될 수 있기 이전에 소거된다.Some non-volatile memories, such as NAND flash, provide a writable (or programmable) unit called a non-volatile memory page (or a flash page if referring to, for example, NAND flash). Typically, the non-volatile memory page is the least writable unit of the non-volatile memory. In some embodiments and / or usage scenarios, the non-volatile memory page may be configured to store a large amount of user (non-error correcting code) data bytes and meta data and the amount of spare space for error correction coding (e.g., ECC) . A typical NAND flash page size is 8 KB or 16 KB or 32 KB of user data, while a typical mapping unit size for logical block addresses is 4 KB or 8 KB. (The term "user" data is used for non-volatile memory pages, and some non-volatile memory pages store "system" data such as map data and / or checkpoint data. NAND flash pages are made up of blocks, typically 128, 256, or 512 flash pages per block. The block is an erasable minimum-size unit, and the NAND flash page is erased before the page can be (re) written.

NAND 플래시와 같은 일부 비휘발성 메모리들은 복수의 플레인(plane)들 및/또는 뱅크(bank)들을 구비하며, 2개 이상의 플레인들 각각으로부터 동시에 페이지 및/또는 블록에 액세스하는 "멀티-플레인(multi-plane)" 동작들을 허용한다. 멀티-플레인 프로그래밍의 사용은 기록 대역폭을 유리하게 증가시키며, 기록의 기본 유닛이 단일의, 1-플레인 페이지가 아닌 멀티-플레인 페이지가 되게 한다. 본 명세서에서 사용되는 용어 비휘발성 메모리 페이지(또는 비휘발성 메모리 블록)는 비휘발성 메모리가 사용되는 방식에 따라, 단일 비휘발성 메모리 페이지(또는 블록) 또는 멀티-플레인 비휘발성 메모리 페이지(또는 블록)을 나타낸다.Some non-volatile memories, such as NAND flash, have a plurality of planes and / or banks and are referred to as "multi-planes ", which access pages and / or blocks simultaneously from each of two or more planes. plane "operations. The use of multi-plane programming advantageously increases the recording bandwidth, making the basic unit of recording a multi-plane page rather than a single, one-plane page. The term non-volatile memory page (or non-volatile memory block) as used herein refers to a single non-volatile memory page (or block) or a multi-plane non-volatile memory page (or block), depending on the manner in which the non- .

본 명세서에서는 용어 "플래시" 변환 계층(예컨대, FTL)이 사용되지만, 논리적 어드레스와 물리적 어드레스 간의 변환 계층의 개념은 복수 타입의 비휘발성 메모리에 적용될 수 있다. 일 예에서, 소정 타입의 비휘발성 메모리, 예컨대 NAND 플래시는 재기록되기 이전에 큰 유닛들로 소거된다. 다른 예에서, 몇몇 타입의 비휘발성 메모리는 웨어링(wearing) 처리되어, 웨어-레벨링(wear-leveling)(비휘발성 메모리의 보다 많이 마모된 부분들에서 덜 마모된 부분들로 데이터를 이동시킴)을 발생시킨다. 또 다른 예에서, 새로운 형태의 하드 디스크 자기 기록, 예컨대 싱글드 자기 기록(shingled magnetic recording)은 이전에 기록된 데이터를 갱신 기록하는 능력을 갖지 않으며, 훨씬 더 큰 양의 다른 데이터를 소거하지 않는다. 각종 실시예들에서, 코어스-그레인형(coarse-grained)이거나 유한 내구성을 갖는 비휘발성 메모리가 (플래시) 변환 계층으로부터 혜택을 받을 수 있다.Although the term "flash" translation layer (e.g., FTL) is used herein, the concept of a translation layer between a logical address and a physical address can be applied to multiple types of non-volatile memory. In one example, certain types of non-volatile memory, such as a NAND flash, are erased into larger units before being rewritten. In another example, some types of non-volatile memory may be worn-in and subjected to wear-leveling (moving data from less worn portions of the non-volatile memory to less worn portions) . In another example, a new type of hard disk magnetic recording, such as shingled magnetic recording, does not have the ability to update and record previously recorded data and does not erase much larger amounts of other data. In various embodiments, non-volatile memory with coarse-grained or finite durability may benefit from a (flash) translation layer.

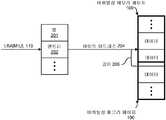

도 1을 참조하면, 비휘발성 메모리 페이지 내의 고정-사이즈 영역들에 논리 블록 어드레스를 맵핑하는 일 실시예의 선택된 상세 도면이 도시되어 있다. 몇몇 전통적 플래시 변환 계층들은 비휘발성 메모리 페이지(예컨대, 비휘발성 메모리 페이지(100)) 내의 사용자 데이터 바이트들의 수는 2의 거듭제곱(및/또는 섹터 사이즈의 배수)이며, 비휘발성 메모리 페이지를 정수 개의 맵핑 유닛들(도 1에 그 각각의 데이터가 도시됨)로 나눈 것으로 가정한다. 예를 들어, 비휘발성 메모리 페이지당 16 KB의 사용자 데이터 및 4 KB 맵핑 유닛들을 가진 경우에 있어서, 각각의 비휘발성 메모리 페이지는 4개의 맵핑 유닛을 포함하고, 플래시 변환 계층은 각 맵핑 유닛의 어드레스(예컨대, LBA[M:U](110))를 각각의 비휘발성 메모리 페이지에 맵핑하며, 이 4개의 맵핑 유닛 중의 하나는 각각의 비휘발성 메모리 페이지 내에 존재한다. 즉, 각 맵 엔트리는 다음과 같은 각각의 필드들을 포함한다:Referring to FIG. 1, there is shown selected detailed views of one embodiment for mapping logical block addresses to fixed-size regions within a non-volatile memory page. Some conventional flash translation layers are those where the number of user data bytes in a non-volatile memory page (e.g., non-volatile memory page 100) is a power of two (and / or a multiple of the sector size) Is assumed to be divided by the mapping units (each of which is shown in Fig. 1). For example, in the case of 16 KB of user data and 4 KB mapping units per non-volatile memory page, each non-volatile memory page includes 4 mapping units, and the flash translation layer stores the address of each mapping unit For example, LBA [M: U] 110) to each non-volatile memory page, one of which is in each non-volatile memory page. That is, each map entry contains the following fields:

nonvolatile_memory_page_address[n-1:0], mapping_unit_within_nonvolatile_memory_page[k-1:0]nonvolatile_memory_page_address [n-1: 0], mapping_unit_within_nonvolatile_memory_page [k-1: 0]

여기서, nonvolatile_memory_page_address는 비휘발성 메모리 내의 고유의 비휘발성 메모리 페이지를 지칭하고, mapping_unit_within_nonvolatile_memory_page는 각 비휘발성 메모리 페이지의 2k 맵핑-유닛-사이즈 부분들 중의 하나를 지칭한다(k는 전체 비휘발성 메모리에 대해 고정되어 있음). 서브-페이지 어드레스(104)는 nonvolatile_memory_page_address과 mapping_unit_within_nonvolatile_memory_page의 조합이다. 섹터-기반(예컨대, 맵핑 유닛보다 정교한 입도(granularity)) 어드레싱에 있어서, 논리 블록 어드레스(예컨대, LBA[U-1:0](111))의 하위(lower-order) 비트들은, 서브-부분, 예를 들어 맵핑 유닛 내의 섹터들(예컨대, 서브-페이지(113) 내의 섹터(들))의 개수를 명시한다.Where nonvolatile_memory_page_address refers to a unique nonvolatile memory page in the nonvolatile memory and mapping_unit_within_nonvolatile_memory_page refers to one of the 2k mapping-unit-size portions of each nonvolatile memory page, where k is fixed for the entire nonvolatile memory has exist). The sub-page address 104 is a combination of nonvolatile_memory_page_address and mapping_unit_within_nonvolatile_memory_page. The lower-order bits of a logical block address (e.g., LBA [U-1: 0] 111), for sector-based (e.g., granularity than the mapping unit) For example, the number of sectors (e.g., sector (s) in sub-page 113) in the mapping unit.

도 2를 참조하면, 선택적으로 비휘발성 메모리 페이지들을 스패닝하는 가변-사이즈 영역에 논리 블록 어드레스를 맵핑하는 일 실시예의 선택된 상세 도면이 도시되어 있다. 가변-사이즈 플래시 변환 계층(예컨대, VFTL)들은 하나 이상의 비휘발성 메모리 페이지들의 가변-사이즈 영역에 대하여 맵핑 유닛(예컨대, LBA[M:U](110)) 중의 하나의 어드레스(또는 라벨)을 개념적 맵핑한다(예를 들어, 맵핑 유닛은 비휘발성 메모리에 저장되기 이전에 압축되기 때문, 및/또는, 다른 예에서, 맵핑 유닛들은 호스트에 의해서 예컨대 객체 저장소(object store)용의 가변-사이즈 조각들로 기록되기 때문임). 그러나, 각 맵 엔트리에 완전한 바이트 어드레스(204) 및 바이트 데이터 길이(206)를 제공하는 것은, 전통적 플래시 변환 계층들과 비교할 때 맵 엔트리들을 커지게 만든다.Referring to FIG. 2, there is shown a selected detail view of one embodiment for mapping a logical block address to a variable-size area that optionally spans non-volatile memory pages. The variable-size flash translation layer (e.g., VFTLs) may associate the address (or label) of one of the mapping units (e.g., LBA [M: U] 110) with respect to the variable-size area of one or more non- (E.g., because the mapping unit is compressed before being stored in the non-volatile memory and / or, in another example, the mapping units may be modified by the host, for example, As shown in FIG. Providing a complete byte address 204 and a byte data length 206 to each map entry, however, makes the map entries larger as compared to traditional flash translation layers.

도 3을 참조하면, 정수 개의 판독 유닛들을 포함하는 비휘발성 메모리 페이지에 대한 일 실시예의 도면이 도시되어 있다. 몇몇 실시예들에서, 가변-사이즈 플래시 변환 계층들은, E페이지(예컨대, 오류 정정 코딩 페이지) 어드레스("판독 유닛" 어드레스로도 불림)에 대한 맵핑에 의해서 맵핑 유닛들의 어드레스들(또는 라벨들)에서 물리적 어드레스들로의 맵핑을 수행한다. E페이지(또는 판독 유닛)는 비휘발성 메모리로부터 판독될 수 있고 또한 비휘발성 메모리의 콘텐츠들을 보호하는데 사용되는 오류 정정 코드에 의해 정정될 수 있는 최소 데이터의 양이다. 즉, 각 판독 유닛은 데이터 및 해당 데이터를 보호하는 대응하는 오류 정정 코딩 체크 바이트들의 양을 포함한다. 몇몇 실시예들에서, 비휘발성 메모리 페이지(예컨대, 비휘발성 메모리 페이지(100)), 또는 다른 실시예들에서, 기록을 위해 하나의 유닛으로 처리되는 비휘발성 메모리 페이지들의 그룹은, 도 3에 도시된 바와 같이, 정수 개의 판독 유닛들로 분할된다.Referring to FIG. 3, a diagram of an embodiment of a non-volatile memory page including an integer number of read units is shown. In some embodiments, the variable-size flash translation layers may include addresses (or labels) of mapping units by mapping to an E page (e.g., error correction coding page) address (also referred to as a " Lt; / RTI > to physical addresses. The E page (or reading unit) is the amount of minimum data that can be read from the non-volatile memory and can be corrected by the error correcting code used to protect the contents of the non-volatile memory. That is, each reading unit contains the data and the amount of corresponding error correction coding check bytes protecting that data. In some embodiments, in a non-volatile memory page (e.g., non-volatile memory page 100), or other embodiments, the group of non-volatile memory pages that are processed as a unit for writing, And is divided into an integer number of read units, as shown.

NAND 플래시와 같은 몇몇 타입의 비휘발성 메모리에 있어서, 비휘발성 메모리에 저장되는 데이터는 사용자 데이터 바이트들과 오류 정정 코드 바이트들(오류 정정 정보)의 혼합이며, 비휘발성 메모리에 액세스하는 상위-레벨 컨트롤러는 비휘발성 메모리의 어느 바이트들 및 얼마나 많은 바이트들이 사용자 데이터를 위해 사용될지 및 어느 바이트들 및 얼마나 많은 바이트들이 오류 정정 코딩을 위해 사용될지를 결정한다. 각종 실시예들에서, 비휘발성 메모리 페이지당 판독 유닛들의 수는 달라질 수 있다. 예를 들어, 비휘발성 메모리의 일부 부분들은 다른 것보다 강한 오류 정정 코드들을 사용(오류 정정 코딩 정보를 위하여 비휘발성 메모리 페이지에 더 많은 바이트들을 사용)하며, 더 적은 판독 유닛들 및/또는 판독 유닛당 더 적게 사용될 수 있는 데이터를 갖는다. 다른 예에서, 프로그램/소거 사이클들은 비휘발성 메모리를 약하게 만들기 때문에, 비휘발성 메모리 페이지당 판독 유닛들이 수는 비휘발성 메모리가 사용됨에 따라 달라질 수 있으며, 이로 인해 비휘발성 메모리가 더 사용(마모)됨에 따라 더 강한 오류 정정 코드들을 야기한다.In some types of non-volatile memory, such as NAND flash, the data stored in the non-volatile memory is a mixture of user data bytes and error correcting code bytes (error correction information) Determines which bytes of non-volatile memory and how many bytes will be used for user data and which bytes and how many bytes are to be used for error correcting coding. In various embodiments, the number of read units per non-volatile memory page may vary. For example, some portions of the non-volatile memory use stronger error correction codes (use more bytes for non-volatile memory pages for error correction coding information) and fewer read units and / Data that can be used less. In another example, the number of read units per non-volatile memory page may vary as non-volatile memory is used because the program / erase cycles weaken the non-volatile memory, which causes the non-volatile memory to become more usable Resulting in stronger error correcting codes.

각종 실시예들에 따르면, 사용되는 오류 정정 코드는 RS(Reed-Solomon) 코드; BCH(Bose Chaudhuri Hocquenghem) 코드; 터보 코드; 경판정(hard-decision) 및/또는 연판정(soft-decision) LDPC(low-density parity-check) 코드; 폴라 코드; 비이진(non-binary) 코드; RAID(redundant array of inexpensive/independent disks) 코드; 소거 코드; 임의의 다른 오류 정정 코드; 구성들, 연결들, 및 인터리빙을 포함하는 전술의 것들의 임의의 조합 중의 하나 이상의 것이다. 통상적인 코드워드 사이즈들의 범위는 512 바이트(플러스 오류 정정 코딩 바이트들)로부터 2176 바이트(플러스 오류 정정 코딩 바이트들)까지가 된다. 통상적인 오류 정정 코딩 바이트들의 수의 범위는 단지 몇 바이트로부터 수백 바이트까지가 된다. 몇몇 멀티-레벨 셀 NAND 플래시 디바이스들에서, 오류 정정 기준들은 1 KB의 사용자 데이터당 40비트이다. 몇몇 멀티-레벨 셀 NAND 플래시 디바이스들에서, 코드 레이트(판독 유닛에서의 전체 바이트에 대한 사용자 바이트의 비율)는 통상적으로 94% 미만이다. 예를 들어, MLC NAND 플래시 디바이스는 17664 바이트 사이즈의 플래시 페이지들을 가지며, 이 중의 16384 바이트는 맵핑된 데이터를 명목상 저장하는데 사용되고, 1280 바이트는 메타-데이터 및 오류 정정 코딩 바이트들을 명목상 저장하는데 사용되는 "스페어(spare)" 바이트이다. MLC NAND 플래시 디바이스용으로 권고되는 오류 정정 코딩 크기는 1 킬로바이트당 40비트의 정정이며, 이것은 1 킬로바이트의 맵핑된 데이터 바이트당 70바이트의 스페어 바이트를 사용한다.According to various embodiments, the error correction code used is an RS (Reed-Solomon) code; Bose (Bose Chaudhuri Hocquenghem) code; Turbo code; Hard-decision and / or soft-decision LDPC (low-density parity-check) codes; Polar code; Non-binary code; Redundant array of inexpensive / independent disks (RAID) code; An erase code; Any other error correcting code; One or more of any combination of the foregoing, including configurations, connections, and interleaving. The range of typical codeword sizes ranges from 512 bytes (plus error correction coding bytes) to 2176 bytes (plus error correction coding bytes). The range of the number of conventional error correction coding bytes is only a few bytes to several hundred bytes. In some multi-level cell NAND flash devices, the error correction criteria are 40 bits per kilobyte of user data. In some multi-level cell NAND flash devices, the code rate (the ratio of user bytes to total bytes in the read unit) is typically less than 94%. For example, an MLC NAND flash device has flash pages of 17664 bytes in size, of which 16384 bytes are used for nominally storing the mapped data, 1280 bytes are used for naming metadata and error correction coding bytes, Quot; spare "bytes. The recommended error correction coding size for MLC NAND flash devices is a correction of 40 bits per kilobyte, which uses 70 bytes of spare bytes per kilobyte of mapped data bytes.

도 4를 참조하면, 하나 이상의 판독 유닛들을 스패닝하는 가변-사이즈 영역으로 논리 블록 어드레스를 맵핑한 일 실시예의 선택된 상세 도면이 도시되어 있다. 몇몇 실시예들에서, VFTL 맵핑은 가변-사이즈(예컨대, 압축된) 맵핑 유닛의 어드레스(또는 라벨)(예컨대, LBA[M:U](110))을, 다수의 판독 유닛들로 맵핑시키며, 이 맵의 각 엔트리에서는 판독 유닛들이 판독 유닛 어드레스(404) 및 스팬(span)(판독 유닛들의 수)(406)으로서 나타나 있다. 맵 엔트리들 중의 하나에 의해 참조되는 판독 유닛들은, 하나 이상의 (논리적 및/또는 물리적) 순차적 비휘발성 메모리 페이지들, 예를 들어, 비휘발성 메모리 페이지 바운더리에 임의적 및/또는 선택적으로 걸쳐있는 다수의 판독 유닛들이다. 판독 유닛들 내에 데이터를 패킹(packing)하는 각종 실시예들에서는, 일반적으로 맵의 엔트리 단독만으로는 연관된 데이터의 위치를 탐색하는데 충분하지 않으며(왜냐하면, 엔트리는 판독 유닛들만을 표시하며, 판독 유닛들 내의 데이터를 위치를 표시하는 것은 아니기 때문임), 참조되는 판독 유닛들 내의 다른 정보(예컨대, 헤더들)를 사용하여, 그 연관된 데이터의 위치를 정확하게 탐색하게 된다.Referring to FIG. 4, there is shown a selected detailed view of an embodiment mapping a logical block address to a variable-size area that spans one or more read units. In some embodiments, the VFTL mapping maps the address (or label) (e.g., LBA [M: U] 110) of a variable-sized (e.g., compressed) mapping unit to a plurality of read units, In each entry of this map, the read units are shown as a read unit address 404 and a span (number of read units) 406. The read units referenced by one of the map entries may be associated with one or more (logical and / or physical) sequential nonvolatile memory pages, e.g., multiple reads that arbitrarily and / or selectively span the nonvolatile memory page boundary Units. In various embodiments of packing data within the read units, the entry alone of the map is generally not sufficient to search for the location of the associated data (because the entry represents only the read units, (E.g., because the data is not indicative of location), other information in the referenced reading units (e.g., headers) is used to accurately locate the associated data.

몇몇 실시예들에서, 데이터는, 비휘발성 메모리의 복수의 다이(die)들에 걸쳐 스트라이핑(Striping)되는 방식으로, 비휘발성 메모리 페이지들에 기록된다. 복수의 다이들에 걸쳐 기록 데이터를 스트라이핑하는 것은, 유리하게도, 비휘발성 메모리 페이지를 스트라이프당 한번씩 소정 다이에 기록하는 것만으로 더 큰 기록 대역폭을 가능하게 한다. 복수의 다이들에 걸친 블록들의 스트라이프는, 다른 실시예들 및/또는 사용 시나리오들에서, RAID-유사 리던던시가 예를 들어 하나의 리던던트 다이(redundant die)를 사용하여 리던던시 블록 단위로 부가되기 때문에, 리던던시 블록으로 지칭된다. 각종 실시예들에서, 비휘발성 메모리의 몇몇 블록들은 기록시에 결함이 존재하여 스킵(skip)되며, 이에 따라 스트라이핑은 때때로, 그 다이 중의 하나가 스킵되는 "홀(holes)"을 갖는다. 이러한 실시예들에서, "순차적" 비휘발성 메모리 페이지들은 비휘발성 메모리 페이지가 기록되는 순서에 의해 결정되는 논리 순서로 순차적이다.In some embodiments, data is written to non-volatile memory pages in a manner that is striped across a plurality of dies of the non-volatile memory. Striping write data across a plurality of dies advantageously enables a larger write bandwidth by simply writing non-volatile memory pages to a given die once per stripe. The stripes of blocks across the plurality of dies can be used in other embodiments and / or in use scenarios, since RAID-like redundancy is added in redundancy block units using, for example, one redundant die, Referred to as a redundancy block. In various embodiments, some blocks of the non-volatile memory are skipped due to the presence of defects at the time of writing, and thus the striping sometimes has "holes" where one of the die is skipped. In these embodiments, the "sequential" nonvolatile memory pages are sequential in logical order, which is determined by the order in which the nonvolatile memory pages are written.

도 5를 참조하면, 헤더들 및 데이터를 포함하는 판독 유닛에 대한 일 실시예의 선택된 상세 도면이 도시되어 있다. 각종 실시예들에서, 도 4에 도시된 맵핑은 판독 유닛들 내의 가변-사이즈 데이터의 위치를 탐색하는 기준을 발생시킨다. 도 5에 도시된 바와 같이, 각 판독 유닛(예컨대, 판독 유닛들(500 및 510))은 0개 이상의 헤더들(501)의 세트를 가지며, 통상적으로 헤더들은, 가변-사이즈 데이터가 하나 이상의 판독 유닛들로 "타일링(tiled)"됨(예컨대, 낭비되는 공간 없이 조밀하게 패킹됨)에 따라 하드웨어에 의해 기록된다. 통상적으로, 헤더들은 비휘발성 메모리가 판독될 시에, 다른 하드웨어에 의해 해석되어서 가변-사이즈 데이터를 추출한다. 가변-사이즈 데이터는 매칭 논리 블록 어드레스(또는 라벨)를 가진 헤더들 중의 하나에서 각각의 오프셋들 및 길이로 위치되며, 데이터는 판독 유닛들(예컨대, "DATA, START" 및 "DATA, CONTINUE"로 예시된 가변-사이즈 데이터)을 임의적으로 및/또는 선택적으로 스패닝한다.Referring to FIG. 5, there is shown selected detailed views of an embodiment of a read unit that includes headers and data. In various embodiments, the mapping shown in Figure 4 generates a criterion for locating the variable-size data in the read units. As shown in Figure 5, each read unit (e.g., read

각종 실시예들에서, 또한 헤더들은 판독 유닛 내의 논리 블록 어드레스(또는 동등하게는, 맵핑 유닛 어드레스나 라벨)를 포함하는 리사이클링(예컨대, 가비지 컬렉션(garbage collection) 및/또는 웨어-레벨링(wear-leveling))의 일부로서 사용되며, 이들 모두는 판독 유닛 내의 가변-사이즈 데이터를 탐색을 가능하게 하고, 가변-사이즈 데이터가 계속 유효하거나 갱신 기록된 경우에는, 판독 유닛들 중의 특정의 것이 판독될 시점을 결정하는 방식을 제공한다(맵에서 논리 블록 어드레스 또는 라벨을 조회하고, 그 맵이 특정 판독 유닛의 물리적 어드레스를 계속 참조하고 있는지 또는 판독 유닛들 중의 다른 것을 참조하도록 업데이트되었는지를 결정하는 것에 의해). 따라서, 헤더들은, 판독 유닛들의 물리적 위치와 조합된 헤더들이, 맵 내의 것과 유사하되 물리적 위치로부터 논리 블록 어드레스(또는 라벨)로 연관되어 있는 정보를 갖는다는 점에서 "리버스 맵(reverse map)"을 형성한다고 한다.In various embodiments, the headers may also be recycled (e.g., garbage collection and / or wear-leveling), including logical block addresses (or equivalently, mapping unit addresses or labels) ), All of which enable the search of the variable-size data in the reading unit, and when the variable-size data is continuously valid or updated, the point in time when the specific one of the reading units is read (By querying the logical block address or label in the map and determining whether the map continues to reference the physical address of a particular read unit or whether it has been updated to refer to another of the read units). Thus, the headers are referred to as a " reverse map "in that the headers combined with the physical locations of the read units have information that is similar to that in the map but is associated with the logical block address (or label) .

몇몇 실시예들에서, 논리 블록 어드레스들(또는 라벨들)에 기초하여 판독 유닛들로부터 데이터를 추출하는 전용 하드웨어가 실행되어 랜덤 판독을 위한 고효율로 동작한다. 전용 하드웨어는 하나 이상의 판독 유닛들 내에 있는 헤더들을 파싱하여 소정의 논리 블록 어드레스(또는 라벨)를 가진 헤더들 중의 하나를 탐색하며, 이어서 그 각각의 길이 및 오프셋을 사용하여 연관된 가변-사이즈 데이터를 추출한다. 그러나, 하드웨어-기반 솔루션은 (실리콘 면적 및 전력)에 비용이 많이 든다. 순차적 성능이 랜덤 성능보다 더욱 중요한 로우-엔드 및/또는 모바일 환경에서는, 실리콘 면적을 줄여, 전력을 절약하고, 높은 순차적 스루풋 레이트(throughput rate)들을 달성하기 위해 가변-사이즈 플래시 변환 계층에 대한 변경들이 실행된다.In some embodiments, dedicated hardware is implemented that extracts data from the read units based on logical block addresses (or labels) and operates with high efficiency for random reading. Dedicated hardware parses headers in one or more read units to search for one of the headers with a given logical block address (or label), and then uses the respective length and offset to extract the associated variable-size data do. However, hardware-based solutions (silicon area and power) are costly. In a low-end and / or mobile environment where sequential performance is more important than random performance, changes to the variable-size flash translation layer to reduce silicon area, save power, and achieve high sequential throughput rates .

몇몇 실시예들에서, 순차적-판독-최적화된 가변-사이즈 플래시 변환 계층(예컨대, SRO-VFTL)은 데이터 내의 헤더들에 대한 임의의 갭(gap)들 없이 비휘발성 메모리 페이지들(또는, 몇몇 실시예들에서는, 기록 목적으로 하나의 유닛으로 취급되는 비휘발성 메모리 페이지들의 그룹)로, (밀집 패킹된) 데이터를 타일링한다 - 모든 헤더들은 비휘발성 메모리 페이지의 한 부분으로 그룹화됨. 다른 실시예들에서, 헤더들은 데이터에 액세스하기 위해 동적으로 사용되지 않으며, 리사이클링 및 복구를 위해(예컨대, 예상치 못한 전력 손실로부터의)서만 사용된다. 대신에, 맵의 엔트리들은 비휘발성 메모리 페이지들 내의 가변-사이즈 (예컨대, 압축된) 데이터를 탐색하는데 사용되는 완전한 정보를 포함한다. 헤더들 및 데이터를 비휘발성 메모리 페이지의 상이한 부분들로 분리시키는 것으로 인해, 헤더들만 포함하는 판독 유닛들, 헤더들 및 데이터의 혼합(그러나, 도 6에서와 같이, 비휘발성 메모리 페이지당 단 하나의 판독 유닛)을 포함하는 판독 유닛들, 및 데이터만을 포함하는 판독 유닛들이 발생된다.In some embodiments, the sequential-read-optimized variable-size flash translation layer (e.g., SRO-VFTL) may include non-volatile memory pages (or some implementations) without any gaps for headers in the data (In the example, a group of non-volatile memory pages that are treated as one unit for recording purposes) - all headers are grouped as part of a non-volatile memory page. In other embodiments, the headers are not used dynamically to access the data and are only used for recycling and recovery (e.g., from unexpected power loss). Instead, entries in the map contain complete information used to search for variable-sized (e.g., compressed) data in non-volatile memory pages. By separating the headers and data into different parts of the non-volatile memory page, a mixture of read units, headers and data, including only headers (however, only one Reading units), and reading units containing only data are generated.

저비용의 순차적 판독 스루풋으로 구성되었지만, 순차적-판독-최적화된-가변-사이즈 플래시 변환 계층은 초당 랜덤 판독 입/출력 동작들(예컨대, IOP들), 초당 랜덤 기록 입/출력 동작들, 및 순차적 기록 스루풋과 같은 다른 메트릭스에 대하여 비교적 잘 수행할 수 있다. 그러나, 각 판독 유닛의 헤더들과의 VFTL-스타일 데이터 타일링과 같은 기능들에 대한 하드웨어 보조들을 제거하는 것은, 제어 프로세서에게 더 큰 부담을 지우게 된다. 다르게는, 몇몇 실시예들에서, 순차적-판독-최적화된-가변-사이즈 플래시 변환 계층은 데이터 타일링, 데이터 추출, 또는 그 밖의 동작들에 대한 하드웨어 보조들을 사용한다.The flash-to-serial conversion read-write operations are performed at a rate of one or more times per second. The sequential-read-optimized-variable- It can perform relatively well for other metrics such as throughput. However, eliminating hardware aids for functions such as VTLL-style data tiling with the headers of each read unit places a greater burden on the control processor. Alternatively, in some embodiments, the sequential-read-optimized-variable-size flash translation layer uses hardware aids for data tiling, data extraction, or other operations.

도 6을 참조하면, SRO-VFTL 비휘발성 메모리 페이지에 대한 일 실시예의 도면이 도시되어 있다. 도 7을 참조하면, SRO-VFTL 비휘발성 메모리 페이지에 대한 다른 실시예의 도면이 도시되어 있다. 도 6과 도 7의 실시예들 간의 차이점은 이전의 비휘발성 메모리 페이지(640)로부터의 연속 데이터가 헤더들의 앞에 있는지 뒤에 있는지의 여부이다. 비휘발성 메모리 페이지 내의 데이터에 대한 다양한 실시예들 및 구성들이 고려된다.Referring to FIG. 6, a diagram of an embodiment of a SRO-VFTL non-volatile memory page is shown. Referring to FIG. 7, a diagram of another embodiment of an SRO-VFTL non-volatile memory page is shown. The difference between the embodiments of FIGS. 6 and 7 is whether continuous data from the previous

각종 실시예들에 따르면, 비휘발성 메모리 페이지는 다음 중의 하나 이상을 포함한다:According to various embodiments, the non-volatile memory page includes one or more of the following:

- 마스터 헤더(610), 임의적 및/또는 선택적으로는 리던던시 블록 헤더(620)(예컨대, 리던던시 블록에서 각 블록의 첫번째 페이지에 부가된 헤더), 및 0개 이상의 추가적인 패킹된 헤더들(630)을 포함하는, 헤더들. 각 비휘발성 메모리 페이지는 (헤더들과 연관된) 데이터가, 적어도 일 카운트 개수의 다음의 헤더들 및 비휘발성 메모리 페이지에서 시작하는 위치에 대한 포인터를 갖는다. 몇몇 실시예들에서, 헤더들은 바이트-정렬될 수 있으며, 각기 6 바이트(예컨대, B)만일 수 있다. 헤더들은 데이터 헤더들, 에포크(epoch) 헤더들 및 패딩(padding)을 포함할 수 있으며, 이에 한정되지 않는다. 데이터 헤더들은 맵핑 유닛 어드레스 및 길이를 이용한다. 모든 데이터는 연속적으로 패킹되기 때문에, 오프셋이 나타난다.- a

- 임의적 및/또는 선택적으로는, 이전의 비휘발성 메모리 페이지(맵핑 유닛의 가변-사이즈 데이터의 일부)(640)로부터의 연속 데이터.- optionally and / or alternatively, contiguous data from a previous non-volatile memory page (part of the variable-size data of the mapping unit) 640.

- 비휘발성 메모리 페이지에 채워지는 하나 이상의 맵핑 유닛들(650)의 패킹된(예컨대, 임의적 및/또는 선택적으로는 압축된) 데이터, 임의적 및/또는 선택적으로는 이것의 마지막이 후속의 비휘발성 메모리 페이지에서 계속된다.Packed (e.g., arbitrary and / or optionally compressed) data of one or

- (650에 포함된) 비휘발성 메모리 페이지의 끝 부분에서의 임의적 패딩.- random padding at the end of non-volatile memory pages (included in 650).

각종 실시예들에서, 고도로 압축되어 있는 경우(예컨대, 매우 많은 헤더들), 데이터는, 비휘발성 메모리 페이지의 끝 부분에서 패딩되는 것이 가능하더라도, 바이트-패킹된다(예컨대, 홀이 없음). 패딩은, 예를 들어, (i) 비휘발성 메모리 페이지에 부가되는 마지막 가변-사이즈 데이터 조각에 헤더의 사이즈보다 적게 사용된 바이트가 남아 있는 경우(이에 따라 새로운 헤더가, 다른 가변-사이즈 데이터 조각을 시작시키기 위해 부가될 수 없는 경우) 및 (ii) 임의적 및/또는 선택적으로는, 명시된 개수의 비휘발성 메모리 페이지당 헤더들이 초과된 경우(이에 따라 비휘발성 메모리 페이지들에 저장되는 맵핑 유닛들의 수가, 맵핑 유닛들의 데이터 사이즈가 아닌, 명시된 개수의 헤더들로 제한되는 경우)에 사용된다.In various embodiments, where highly compressed (e.g., very many headers), the data is byte-packed (e. G., No holes), although it is possible to be padded at the end of non-volatile memory pages. The padding may, for example, include: (i) if there is less than the size of the header used in the last variable-size data fragment being added to the non-volatile memory page (thereby causing the new header to be replaced by another variable- (Ii) optionally and / or alternatively, if the number of headers per a specified number of non-volatile memory pages is exceeded (thus the number of mapping units stored in non- Is limited to a specified number of headers rather than the data size of the mapping units).

몇몇 실시예들에서, 순차적-판독-최적화된-가변-사이즈 플래시 변환 계층을 이용한 복구 및/또는 리사이클링(예컨대, 가비지 컬렉션)은, 유리하게도 비-순차적-판독-최적화된-가변-사이즈 플래시 변환 계층에서와 같은 모든 판독 유닛이 아닌, 각각의 비휘발성 메모리 페이지들의 헤더 부분만을 판독 및/또는 오류 정정 및/또는 검사할 수 있다. 비휘발성 메모리 페이지의 데이터가 재기록될 수 있는 것으로 리사이클링이 결정한 경우, 해당 데이터가 또한 판독될 수 있으며, 오류 정정될 수도 있다. 몇몇 실시예들에서는, 리사이클링을 위해 전체 비휘발성 메모리 페이지가 판독되지만, 비휘발성 메모리 페이지 내의 일부 데이터가 리사이클링되어야 하는 것으로 결정될 때까지는 헤더 부분만이 오류 정정된다.In some embodiments, recovery and / or recycling (e.g., garbage collection) using a sequential-read-optimized-variable-size flash translation layer may advantageously be performed using a non-sequential-read- It is possible to read and / or error correct and / or check only the header portion of each non-volatile memory pages, rather than all read units as in the hierarchy. If the recycling determines that the data in the non-volatile memory page can be rewritten, the data may also be read and error corrected. In some embodiments, the entire non-volatile memory page is read for recycling, but only the header portion is error corrected until some data in the non-volatile memory page is determined to be recycled.

각종 실시예들에서, 비휘발성 메모리 페이지당 헤더들의 수는 모든 헤더들이 비휘발성 메모리로부터 판독되는 것을 보장하도록 판독될 수 있는 확실한 비휘발성 메모리 페이지당 판독 유닛들의 수로 제한된다. 도 6의 실시예에서는, 최대 개수의 헤더들을 포함하기에 충분한 개수의 판독 유닛들만이 판독된다. 도 7의 실시예에서는, 추가 개수의 판독 유닛들이 판독되어 이전의 비휘발성 메모리 페이지(예컨대, 연속 데이터(640))로부터 완료된 가장 큰 데이터 사이즈를 처리한다. 그러나, 도 7의 실시예는 연관된 맵 엔트리에 대한 각각의 오프셋과 길이, 및 이전의 비휘발성 메모리 페이지에서의 사용자(비-오류 정정 코드) 데이터의 바이트들의 수에 기초하여 완료된 데이터의 바이트들의 수가 결정가능함에 따라, 다수의 판독 유닛들이 연관된 맵 엔트리로부터 결정되는 이전의 비휘발성 메모리 페이지(예컨대, 연속 데이터(640))로부터 완료된 데이터에 액세스하는 것을 가능하게 한다. 또한, 완료된 데이터 이전의 헤더들만이 임의적 리던던시 블록 헤더(각 블록의 첫 번째 페이지와 같은, 명시된 비휘발성 메모리 페이지들에만 존재함) 및 마스터 헤더(각 비휘발성 메모리 페이지에 항시 존재함)이다. 도 6의 실시예에서, 비휘발성 메모리에 두 번 액세스할 필요없이 완료된 데이터를 판독하기 위해, 최대 개수의 헤더들이 존재하는 것으로(또는 전체 비휘발성 메모리 페이지가 판독되는 것으로) 가정된다.In various embodiments, the number of headers per non-volatile memory page is limited to the number of reliable nonvolatile memory pages per page that can be read to ensure that all headers are read from non-volatile memory. In the embodiment of FIG. 6, only a sufficient number of read units are read to contain the maximum number of headers. In the FIG. 7 embodiment, an additional number of read units are read and processed from the previous non-volatile memory page (e. G., Contiguous data 640) to the largest completed data size. However, the embodiment of FIG. 7 is based on the number of bytes of completed data based on the respective offset and length for the associated map entry and the number of bytes of user (non-error correcting code) data in the previous non-volatile memory page As it is determinable, it enables multiple read units to access the completed data from a previous non-volatile memory page (e.g., contiguous data 640) determined from the associated map entry. Also, only the headers before the completed data are arbitrary redundancy block headers (present in the specified nonvolatile memory pages, such as the first page of each block) and master headers (always present in each nonvolatile memory page). In the embodiment of FIG. 6, it is assumed that a maximum number of headers are present (or the entire non-volatile memory page is read) to read the completed data without having to access the non-volatile memory twice.

몇몇 실시예들에서, 순차적-판독-최적화된-가변-사이즈 플래시 변환 계층은 복수의 맵 엔트리들을 가진 단일-레벨 맵을 사용한다. 다른 실시예들에서, 순차적-판독-최적화된-가변-사이즈 플래시 변환 계층은 제2-레벨 맵(예컨대, SLM) 페이지들을 가리키는 제1-레벨 맵(예컨대, FLM)을 구비한 2-레벨 맵과 같은 멀티-레벨 맵을 사용하며, 여기서 각각의 제2-레벨 맵 페이지들은 복수의 리프(leaf)-레벨 맵 엔트리들을 포함한다. 다른 실시예들에서, 멀티-레벨 맵은 2개보다 많은 레벨들, 예컨대 3개의 레벨들을 갖는다. 몇몇 실시예들 및/또는 사용 시나리오들에서, 멀티-레벨 맵의 사용은 맵 중의 관련 부분(예컨대, 사용에)만이 로컬 메모리(예컨대, 솔리드-스테이트 드라이브 컨트롤러의 온-칩 SRAM, 또는 호스트의 로컬 DRAM)에 저장되는 것(예컨대, 캐싱되는 것)을 가능하게 하며, 이에 따라 맵의 유지 비용을 감소시킨다. 예를 들어, 일반적 사용 패턴들이 어느 한 시점에서 1 기가바이트(예컨대, GB)의 논리 블록 어드레스 공간 활성 상태를 갖는 경우, 그 활성 상태인 1 GB 부분의 논리 블록 어드레스 공간에 액세스하는데 충분한 맵의 부분만이, 비휘발성 메모리에 저장되는 것에 대한 고속 액세스를 위해 로컬로 저장된다. 논리 블록 어드레스 공간 중의 활성 상태인 부분 이외의 참조들은, 비휘발성 메모리로부터 하나 이상 레벨의 멀티-레벨 맵의 요청된 부분들을 페칭하며, 임의적 및/또는 선택적으로는 그 맵의 다른 로컬-저장된 부분들을 대체한다.In some embodiments, the sequential-read-optimized-variable-size flash translation layer uses a single-level map with a plurality of map entries. In other embodiments, the sequential-read-optimized-variable-size flash translation layer includes a two-level map (e.g., FLM) with a first-level map (e.g., FLM) Level map, wherein each second-level map page includes a plurality of leaf-level map entries. In other embodiments, the multi-level map has more than two levels, e.g., three levels. In some embodiments and / or use scenarios, the use of a multi-level map may be such that only relevant portions of the map (e.g., for use) are local memory (e.g., on-chip SRAM of a solid- (E. G., Cached) in the DRAM, thereby reducing the cost of maintaining the map. For example, if the common usage patterns have a logical block address space active of one gigabyte (e.g., GB) at any one time, then a portion of the map sufficient to access the logical block address space of the active 1 GB portion Are stored locally for fast access to being stored in non-volatile memory. References other than the active portion of the logical block address space may fetch the requested portions of the one or more levels of the multi-level map from the non-volatile memory and optionally and / or optionally other local- Replace.

각각의 리프-레벨 맵 엔트리들은 복수의 맵핑 유닛들 중의 하나의 어드레스(또는 라벨)과 연관된다(대응한다). 일 예에서, 논리 블록 어드레스는 예컨대, 논리 블록 어드레스 중의 0개 이상의 최하위 비트(least-significant bit)(예컨대, LSB)를 제거하고/하거나 정렬 목적으로 논리 블록 어드레스에 상수를 부가하는 것에 의해 맵핑 유닛 어드레스로 변환되며, 이 맵핑 유닛 어드레스이 맵 내에서 조회됨으로써 대응하는 맵의 엔트리를 결정하게 된다. 다른 예에서는, 해시 테이블(또는 다른 연관 데이터 구조)에서 라벨이 조회됨으로써 맵핑 유닛 어드레스로서 사용되는 고유 식별자를 결정하게 된다.Each leaf-level map entry is associated with (corresponding to) the address (or label) of one of the plurality of mapping units. In one example, the logical block address may be determined, for example, by removing zero or more least significant bits (e.g., LSBs) of the logical block address and / or by adding a constant to the logical block address for alignment purposes Address, and this mapping unit address is inquired in the map to determine an entry of the corresponding map. In another example, a label is looked up in a hash table (or other associated data structure) to determine the unique identifier to be used as the mapping unit address.

도 8을 참조하면, 각종 타입의 헤더들에 대한 일 실시예의 상세 도면이 도시되어 있다. 도 8의 예에서, 헤더들은 각기 6 바이트로 피팅(fiting)되도록 포맷되어 있다. 각종 실시예들에 따르면, 각종 타입의 헤더들은 다음들 중의 하나 이상의 헤더이다: 모두 동일한 사이즈를 가짐; 임의적 및/또는 선택적으로는 상이한 사이즈를 가짐; 각각의 헤더들은 헤더의 사이즈를 명시한 각각의 필드를 포함함; 상이한 비휘발성 메모리 페이지들에서는 사이즈가 달라짐; 및 전술한 것들의 임의의 조합.Referring to Figure 8, a detailed view of one embodiment of various types of headers is shown. In the example of FIG. 8, the headers are formatted to fit into 6 bytes each. According to various embodiments, headers of various types are one or more of the following: all of the same size; Optionally and / or alternatively of different sizes; Each header including a respective field specifying a size of a header; The size varies in different nonvolatile memory pages; And any combination of the foregoing.

각종 실시예들에 따르면, 비휘발성 메모리 페이지의 헤더들은 다음 중의 하나 이상을 포함한다:According to various embodiments, the headers of the non-volatile memory page include one or more of the following:

- 가변-사이즈 데이터 부분과 연관된 정보를 표시하는 데이터 헤더들(810). 데이터 헤더와 연관된 데이터는 데이터 헤더가 나나타나는 것과 동일한 비휘발성 메모리 페이지에서 시작된다. 다른 실시예들 및/또는 사용 시나리오들에서, 비휘발성 메모리 페이지가 데이터 헤더용의 잔존 공간만을 가진 경우에는, 모든 연관된 데이터가 후속의 비휘발성 메모리 페이지에서 시작된다.Data headers 810 that display information associated with the variable-size data portion. The data associated with the data header begins with the same nonvolatile memory page as the data header appears. In other embodiments and / or use scenarios, if the non-volatile memory page has only the remaining space for the data header, then all associated data is initiated in the subsequent non-volatile memory page.

- 맵 헤더들, 예를 들어 제2-레벨 맵(예컨대, SLM) 헤더들(820). 제2-레벨 맵 헤더들은 어떤 제2-레벨 맵 페이지가 저장되어 있는지를 나타내는(예컨대, 제2-레벨 맵 리사이클링 및/또는 복구를 위한) 제1-레벨 맵 인덱스(예컨대, FLMI)를 포함한다.Map headers, e.g., second-level map (e.g., SLM) headers 820; The second-level map headers include a first-level map index (e.g., FLMI) indicating which second-level map page is stored (e.g., for second-level map recycling and / or recovery) .

- 로그/체크포인트 헤더들(820). 로그/체크포인트 헤더들은 리사이클링, 복구, 오류 처리, 디버깅, 또는 그 밖의 특수한 상황들을 위해 사용되는 데이터를 나타낸다.Log / checkpoint headers 820. Log / checkpoint headers represent data used for recycling, recovery, error handling, debugging, or other special situations.

- 데이터를 대응하는 맵/체크포인트 정보와 연관시키는 복구의 부분으로서 사용되는, 에포크 헤더들(830). 통상적으로는, 비휘발성 메모리 페이지당 적어도 하나의 에포크 헤더가 존재한다.Epoch headers 830, which are used as part of recovery to associate data with corresponding map / checkpoint information. Typically, there is at least one epoch header per non-volatile memory page.

- 비휘발성 메모리 페이지에 있는 헤더들의 개수 및 비-헤더 데이터가 비휘발성 메모리 페이지 내에서 시작되는 위치에 관한 정보를 제공하도록 비휘발성 메모리 페이지당 한번 사용되는 마스터 헤더들(870). 도 6 및 도 7의 실시예들에서 도시된 바와 같은, 각종 기술들이 비-헤더 데이터의 시작을 결정한다.- Master headers 870 that are used once per non-volatile memory page to provide information about the number of headers in the non-volatile memory page and where the non-header data begins within the non-volatile memory page. Various techniques, as shown in the embodiments of Figures 6 and 7, determine the beginning of the non-header data.

- 소정의 비휘발성 메모리 페이지들, 예를 들어 리던던시 블록의 각 블록에 있는 첫 번째 비휘발성 메모리 페이지에서 사용되는 리던던시 블록 헤더들(880).Redundant block headers 880 used in the first non-volatile memory page in each non-volatile memory pages, e.g., each block of the redundancy block.

- 그 밖의 타입의 헤더들 (840), 예를 들어, 패딩 헤더들, 더 큰 길이를 지원하는 체크포인트 헤더들 등.Other types of headers 840, e.g., padding headers, checkpoint headers supporting a larger length, and so on.

몇몇 실시예들에서, 일부 헤더들은 헤더에 대한 복수의 하위타입들을 제공하는 TYPE 필드를 포함한다. 각종 실시예들에서, 일부 헤더들은 헤더와 연관된 데이터의 길이를 포함하는 LEN(길이) 필드를 포함한다. 각종 실시예들에서, LEN 필드 이외에, 또는 그에 부가하여, 일부 헤더들은 헤더와 연관된 데이터의 끝 부분에 대한 오프셋(비휘발성 메모리 페이지 내의)을 포함하는 OFFSET(오프셋) 필드(미도시)를 포함한다. (몇몇 실시예들에서, 가변-사이즈 데이터 조각들 중의 마지막 조각이 비휘발성 메모리 페이지를 스패닝하는 경우, OFFSET은 후속의 비휘발성 메모리 페이지 내의 오프셋 또는 후속의 비휘발성 메모리 페이지 내의 바이트들의 수이다.) 낭비되는 공간 없이 패킹된 가변-사이즈 데이터 조각들을 이용하여, 비휘발성 메모리 페이지 내의 각 가변-사이즈 데이터 조각들의 시작 위치 및 끝 위치가, 비휘발성 메모리 페이지 내의 첫 번째 가변-사이즈 데이터 조각들의 시작 위치(예컨대, 도 7에서와 같이 헤더들의 직후의), 및 LEN 또는 OFFSET 필드들에 의해 나타낼 수 있기 때문에, 일반적으로 LEN 필드 또는 OFFSET 필드 중의 하나 만이 실행된다.In some embodiments, some headers include a TYPE field that provides a plurality of subtypes for the header. In various embodiments, some headers include a LEN (length) field that includes the length of the data associated with the header. In various embodiments, in addition to or in addition to the LEN field, some headers include an OFFSET field (not shown) that contains an offset (in a non-volatile memory page) for the end of the data associated with the header . (In some embodiments, if the last piece of variable-size data pieces spans a non-volatile memory page, OFFSET is the offset in the subsequent non-volatile memory page or the number of bytes in the subsequent non-volatile memory page.) Size data pieces that are packed without wasted space, the starting and ending positions of each variable-size data piece in the non-volatile memory page are aligned with the starting position of the first variable-size data pieces in the non-volatile memory page (E.g., immediately after the headers as in FIG. 7), and LEN or OFFSET fields, generally only one of the LEN field or the OFFSET field is executed.

도 9를 참조하면, 맵 엔트리(900)에 대한 일 실시예의 선택된 상세 도면이 도시되어 있다. 각종 실시예들에 따르면, 맵 엔트리들은 다음 중의 하나 이상을 포함한다:Referring to FIG. 9, a selected detailed view of an embodiment of a

- 물리적 비휘발성 메모리 페이지 어드레스,- physical non-volatile memory page address,

- 가변-사이즈 데이터 아이템에 대한 비휘발성 메모리 페이지 내의 오프셋(예컨대, OFFSET),- Offset in the non-volatile memory page (e.g., OFFSET) for the variable-size data item,

- 가변-사이즈 데이터 아이템(예컨대, LEN_M128)의 길이, 및The length of the variable-size data item (e.g., LEN_M 128), and

- 그 밖의 제어 정보.- Other control information.

몇몇 실시예들에서, 길이는 예를 들어, 0의 값이 명시된 최소 길이에 대응하게 되도록 오프셋되는 것에 의해 인코딩된다. 예를 들어, 최소 길이가 128 바이트인 경우, LEN_M128 값 0은 128 바이트를 나타낸다. 다른 실시예들에서, 명시된 최소 길이 미만으로 압축되는 데이터는 적어도 명시된 최소 길이 사이즈까지 패딩된다.In some embodiments, the length is encoded by being offset, for example, such that a value of zero corresponds to the specified minimum length. For example, if the minimum length is 128 bytes, a LEN_M128 value of 0 represents 128 bytes. In other embodiments, data compressed below the specified minimum length is padded to at least the specified minimum length size.

각종 실시예들에서, SRO-VFTL 맵 엔트리들은 풀(full) 오프셋 및 대응하는 데이터의 바이트 길이를 저장하기 때문에, SRO-VFTL 맵 엔트리들은 VFTL 맵 엔트리들보다 크다. 이에 따라, 비휘발성 메모리에 저장시에 맵 엔트리들의 사이즈를 감소시키는 것은 유리할 수 있다. 통상적인 사용에 있어서, 흔히 데이터는 적어도 일부 입도(granularity) 및/또는 하나보다 많은 평균 개수의 순차적 맵핑 유닛들로, 순차적으로 판독 및 기록된다. 또한, 기록의 순차적 성질을 이용하는 맵 엔트리 압축 포맷은 높은 맵 압축율을 구현 및 생성함에 있어서 상대적으로 저가이다. 맵 엔트리들의 압축은, 비휘발성 메모리 페이지 바운더리가 크로스(crossing)될 때까지 동일한 비휘발성 페이지들로 들어가는 순차적-기록된 데이터에 의해 또한 도움을 받는다.In various embodiments, the SRO-VFTL map entries are larger than the VFTL map entries because the SRO-VFTL map entries store the full offset and the byte length of the corresponding data. Accordingly, it may be advantageous to reduce the size of the map entries upon storage in non-volatile memory. In normal use, often the data is sequentially read and written with at least some granularity and / or an average number of sequential mapping units of more than one. In addition, the map entry compression format that utilizes the sequential nature of recording is relatively inexpensive in implementing and creating a high map compression ratio. Compression of the map entries is also assisted by sequential-written data entering the same non-volatile pages until the non-volatile memory page boundary is crossed.

도 10을 참조하면, 각종 압축된 맵 엔트리들에 대한 일 실시예의 선택된 상세 도면이 도시되어 있다. 각종 맵 엔트리들은 압축되지 않은 부분(1010), 이전의 맵 엔트리와 동일한 비휘발성 메모리 페이지 어드레스를 갖는 부분(1020), 이전의 맵 엔트리와 동일한 비휘발성 메모리 페이지 어드레스를 가지면서 이전의 데이터가 끝난 오프셋에서 시작하는 부분(1030), 및 이전의 맵 엔트리와 동일한 비휘발성 메모리 페이지 어드레스를 가지면서 이전의 데이터가 끝난 오프셋에서 시작하며 또한 이전의 맵 엔트리와 동일한 길이를 갖는 부분(1040)을 포함한다.Referring to FIG. 10, there is shown selected detailed views of one embodiment of various compressed map entries. The various map entries include an uncompressed portion 1010, a portion 1020 having the same non-volatile memory page address as the previous map entry, a non-volatile memory page address identical to the previous map entry, And a portion 1040 having a same nonvolatile memory page address as the previous map entry and starting at the offset from the previous data and having the same length as the previous map entry.

멀티-레벨 맵을 갖는 몇몇 실시예들에서, 캐시(cache)는 하위-레벨(예를 들면, 리프-레벨) 맵 페이지들로 유지된다. 캐싱된 맵 페이지들 압축되지 않은 형태이며, 프로세서(예를 들면, 솔리드-스테이트 드라이브 컨트롤러의 호스트 또는 제어 프로세서)에 의한 신속한 액세스를 제공한다. 맵 페이지들이 캐시로 이동하는 경우(예를 들면, 비휘발성 메모리 또는 DRAM(dynamic random access memory)으로부터), 맵 페이지들은 압축되지 않는다. 맵 페이지들이 캐시로부터 플러싱(flushing)되는 경우(예를 들면, 수정으로 인해), 맵 페이지들은 저장소(예를 들면, 비휘발성 메모리)에 압축된다. 동적 랜덤 액세스 메모리에 맵 페이지들의 일부 또는 전부를 저장하는 것에 의해 레이턴시를 감소시키는데 DRAM이 사용되는 각종 실시예들에 따르면, 동적 랜덤 액세스 메모리 내의 맵 페이지들은 다음 중의 하나 이상으로 저장된다: 압축된 형태; 압축되지 않은 형태; 선택적으로 압축되거나 압축되지 않은 형태; 및 동적 랜덤 액세스 메모리 내의 맵 페이지들의 (가변-사이즈) 압축 버젼들에 액세스하는데 사용되는 인디렉션 테이블(indirection table)을 구비한 형태.In some embodiments with multi-level maps, the cache is maintained as low-level (e.g., leaf-level) map pages. Cached map pages are in an uncompressed form and provide rapid access by a processor (e.g., a host or control processor of a solid-state drive controller). When the map pages are moved to a cache (e.g., from non-volatile memory or dynamic random access memory (DRAM)), the map pages are not compressed. When map pages are flushed from the cache (e.g., due to modification), the map pages are compressed into a repository (e.g., non-volatile memory). According to various embodiments in which the DRAM is used to reduce latency by storing some or all of the map pages in the dynamic random access memory, the map pages in the dynamic random access memory are stored in one or more of the following: ; Uncompressed form; Optionally compressed or uncompressed form; And an indirection table used to access (variable-size) compressed versions of map pages in the dynamic random access memory.

몇몇 실시예들에서, 호스트 기록 커맨드의 호스트 기록 데이터는, 그 호스트 기록 데이터가 솔리드-스테이트 드라이브 컨트롤러에 도달하여 로컬(예를 들면, 온-칩) 메모리에 FIFO(first-in-first-out)-유사 방식으로 저장됨에 따라, 임의적 및/또는 선택적으로 압축된다. 예를 들어, 몇몇 실시예들에서, 호스트 기록 데이터는 펌웨어 데이터 구조들, 플래시 통계, 맵의 일부들(예를 들면, 하나 이상의 맵 페이지들을 담당하는 캐시), 리사이클링 판독 데이터를 포함하는 비휘발성 메모리로부터의 판독 데이터, 비휘발성 메모리에 기록될 데이터의 헤더들, 소프트웨어 코드, 펌웨어 코드, 및 그 밖의 사용들과 함께, 통합 버퍼(예컨대, 도 11a의 UBUF)에 저장된다. 각종 실시예들에서, 하나 이상의 전용 메모리들이 각종 솔리드-스테이트 드라이브의 로컬 저장 기준들을 위해 사용된다.In some embodiments, the host write data of the host write command is stored in a first-in-first-out (FIFO) memory in the local (e.g., on- As it is stored in a similar manner, it is compressed arbitrarily and / or selectively. For example, in some embodiments, the host write data may include firmware data structures, flash statistics, portions of the map (e.g., cache for one or more map pages), non-volatile memory (E.g., UBUF in FIG. 11A), along with read data from the nonvolatile memory, headers of data to be written to the nonvolatile memory, software code, firmware code, and other uses. In various embodiments, one or more dedicated memories are used for local storage criteria of various solid-state drives.

몇몇 실시예들에서, 호스트 기록 커맨드의 호스트 기록 데이터는 솔리드-스테이트 드라이브 컨트롤러로 전송되기 이전에 호스트에서 임의적 및/또는 선택적으로 압축된다. 예를 들어, 데이터베이스 레코드들이 입/출력 디바이스로 기록되기 이전에 호스트 데이터베이스에 의해 압축된다.In some embodiments, the host write data of the host write command is arbitrarily and / or optionally compressed at the host prior to being sent to the solid-state drive controller. For example, database records are compressed by the host database before being written to the input / output device.

각종 실시예들에서, 호스트로부터 도달한 각 데이터의 맵핑 유닛에 있어서, 솔리드-스테이트 드라이브의 제어 프로세서(예컨대, 도 11a의 CPU(central 프로세싱 유닛))에는 다음 중의 하나 이상이 통지된다: 각각의 맵핑 유닛 어드레스, 이 각각의 맵핑 유닛 어드레스와 연관된 데이터가 저장되는 각각의 로컬 메모리 어드레스, 및/또는 가변-사이즈 (예컨대, 압축된) 호스트 데이터의 각 맵핑-유닛에 대한 각각의 길이. 제어 프로세서는 비휘발성 메모리 페이지들의 기록 순서, 및 비휘발성 메모리 페이지들 각각에서 사용가능한 비-오류 정정 코딩 바이트의 전체 개수를 결정할 수 있다. 비휘발성 메모리 페이지들 중의 소정의 비휘발성 메모리 페이지에서 사용가능한 비-오류 정정 코딩 바이트의 전체 개수에 따라, 제어 프로세서는 그 소정의 비휘발성 메모리 페이지에 배치된 헤더들의 양 및 데이터의 양을 결정할 수 있다. 예를 들어, 제어 프로세서는 그 소정의 비휘발성 메모리 페이지에 대한 헤더들을 축적하며(또한 지금까지 사용된 헤더들의 바이트의 개수를 추적), 그 소정의 비휘발성 메모리 페이지가 완전히 채워질 때까지 한번에 하나씩 맵핑 유닛들 및 헤더들의 가변-사이즈 데이터를 그 소정의 비휘발성 메모리 페이지에 부가한다. 그 소정의 비휘발성 메모리 페이지가 완전히 채워진 경우, 그 소정의 비휘발성 메모리 페이지에 부가된 맵핑 유닛들 중의 마지막 유닛의 마지막 부분은 그 소정의 비휘발성 메모리 페이지에 정합되지 않을 수도 있고, 비휘발성 메모리 페이지들 중의 후속의 것(예컨대, 연속 데이터(640))의 데이터 완료 부분으로서 사용되며, 이에 따라 새로운 헤더들 및 데이터를 위한 후속의 비휘발성 메모리 페이지에서 사용가능한 비-오류 정정 코딩 바이트의 전체 개수를 감소시키게 된다.In various embodiments, in a mapping unit of each data arriving from a host, a control processor of the solid-state drive (e.g., CPU (central processing unit) in Figure 11A) is notified of one or more of the following: A unit address, a respective local memory address at which data associated with each of the mapping unit addresses is stored, and / or a respective length for each mapping unit of variable-size (e.g., compressed) host data. The control processor may determine the recording order of the non-volatile memory pages and the total number of non-error correcting coding bytes available in each of the non-volatile memory pages. Depending on the total number of non-errata correction coding bytes available in a given non-volatile memory page of the non-volatile memory pages, the control processor may determine the amount of headers and amount of data disposed in the given non-volatile memory page have. For example, the control processor accumulates headers for the given non-volatile memory page (and also tracks the number of bytes in the headers used so far), and maps them one at a time until the given non-volatile memory page is fully populated Size data of the units and headers to the predetermined non-volatile memory page. If the predetermined non-volatile memory page is completely filled, the last portion of the last of the mapping units added to the predetermined non-volatile memory page may not be matched to the predetermined non-volatile memory page, (E. G., Contiguous data 640) in the subsequent non-volatile memory page for new headers and data, thereby increasing the total number of non-error correcting coding bytes available in subsequent non-volatile memory pages .

몇몇 실시예들에서, 특정 시점에서, 0개 이상의 비휘발성 메모리 페이지들은 호스트 기록 데이터로 채워질 수 있으며, 0개 이상의 비휘발성 메모리 페이지들은 리사이클링된 데이터로 채워질 수 있다. 예를 들어, 적어도 2개의 밴드(band)들(예컨대, FIFO-유사한 일련의 리던던시 블록들)이 각기 채워지되, 하나의 밴드는 "핫(hot)" 데이터(예컨대, 호스트로부터 갓 나온)로 채워지고, 다른 밴드는 "콜드(cold)" 데이터(예컨대, 리사이클링된)로 채워질 수 있으며, 0개 이상의 비휘발성 메모리 페이지들 가치의 공간이 버퍼로부터 각 밴드로 할당된다. 이 예에 대해 계속 설명하면, 각종 실시예들에서, 호스트 기록 데이터는 임의적 및/또는 선택적으로 핫 밴드 또는 콜드 밴드로 향할 수 있으며, 리사이클링된 데이터는 임의적 및/또는 선택적으로 핫 밴드 또는 콜드 밴드로 향할 수 있다.In some embodiments, at a particular point in time, zero or more non-volatile memory pages may be populated with host write data, and zero or more non-volatile memory pages may be filled with recycled data. For example, at least two bands (e.g., a FIFO-like series of redundancy blocks) are each filled, one band is filled with "hot" data (eg, fresh from the host) Other bands may be filled with "cold" data (e.g., recycled), and the space of zero or more nonvolatile memory pages values is allocated to each band from the buffer. Continuing with this example, in various embodiments, the host write data may be directed arbitrarily and / or alternatively to a hot band or a cold band, and the recycled data may be randomly and / or alternatively switched to a hot band or a cold band You can head.

몇몇 실시예들에서, 제어 프로세서는 일련의 각각의 맵핑 유닛 어드레스들, 로컬 메모리 어드레스들 및 각각의 길이들을 다음 중의 하나 이상으로 변환할 수 있다: 비휘발성 메모리 페이지의 헤더 부분으로서 비휘발성 메모리 페이지에 기록될 일련의 헤더들; 비휘발성 메모리 페이지의 사용자 데이터 부분으로서 비휘발성 메모리 페이지에 기록될 로컬 메모리의 순차적 부분의 첫 번째 시작 어드레스 및 첫 번째 길이로서, 상기 비휘발성 메모리 페이지의 사용자 데이터 부분은 적어도 하나의 맵핑 유닛의 적어도 일부분을 포함함; 후속의 비휘발성 메모리 페이지의 사용자 데이터 완료 부분으로서 후속의 비휘발성 메모리 페이지에 기록될 로컬 메모리의 순차적 부분의 두 번째 시작 주소 및 두 번째 길이로서, 상기 사용자 데이터 완료 부분은 하나의 맵핑 유닛의 데이터의 부분 또는 비어 있는(empty) 부분을 포함함; 비휘발성 메모리 페이지에 기록될 0개 이상의 패딩 바이트의 개수, 여기서 상기 패딩 바이트는 예를 들어, 사용자 데이터 완료 부분이 비어있고 비휘발성 메모리 페이지가 채워져 있지 않은 경우에 사용됨. 유리하게는, 제어 프로세서는 재포맷(reformatting)에 의해 일련의 각각의 맵핑 유닛 어드레스들, 각각의 로컬 메모리 어드레스들 및 각각의 길이들을 일련의 헤더들로 간단히 변환하고, 작은 개수의 DMA(direct memory access) 커맨드들을 생성하여 비휘발성 메모리 페이지를 포함하는 부분들(이전의 비휘발성 메모리 페이지의 일련의 헤더들, 완료 부분, 사용자 데이터 부분, 및 임의의 패딩 바이트들)을 비휘발성 메모리로 전송할 수 있다.In some embodiments, the control processor may convert a series of respective mapping unit addresses, local memory addresses, and respective lengths into one or more of the following: a non-volatile memory page as a header portion of a non-volatile memory page A series of headers to be recorded; A first start address and a first length of a sequential portion of a local memory to be written to a non-volatile memory page as a user data portion of the non-volatile memory page, wherein the user data portion of the non-volatile memory page comprises at least a portion / RTI > A second start address and a second length of a sequential portion of a local memory to be written to a subsequent nonvolatile memory page as a user data completion portion of a subsequent nonvolatile memory page, Contains a portion or an empty portion; The number of zero or more padding bytes to be written to the non-volatile memory page, where the padding byte is used, for example, if the user data completion portion is empty and the non-volatile memory page is not filled. Advantageously, the control processor simply reformats each of the mapping unit addresses, each of the local memory addresses and their respective lengths into a series of headers by reformatting, and uses a small number of direct memory access commands to transfer portions of the nonvolatile memory page (a series of headers, a complete portion, a user data portion, and any padding bytes of a previous nonvolatile memory page) to non-volatile memory .