KR20060101898A - Nonvolatile Memory Device and Its Program Method - Google Patents

Nonvolatile Memory Device and Its Program MethodDownload PDFInfo

- Publication number

- KR20060101898A KR20060101898AKR1020050023477AKR20050023477AKR20060101898AKR 20060101898 AKR20060101898 AKR 20060101898AKR 1020050023477 AKR1020050023477 AKR 1020050023477AKR 20050023477 AKR20050023477 AKR 20050023477AKR 20060101898 AKR20060101898 AKR 20060101898A

- Authority

- KR

- South Korea

- Prior art keywords

- program

- voltage

- word lines

- offset

- word line

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

- G11C16/12—Programming voltage switching circuits

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0483—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells having several storage transistors connected in series

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/08—Address circuits; Decoders; Word-line control circuits

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/26—Sensing or reading circuits; Data output circuits

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/30—Power supply circuits

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Read Only Memory (AREA)

Abstract

Translated fromKoreanDescription

Translated fromKorean도 1은 종래의 낸드형 플래시 메모리 장치를 도시한 회로도이다.1 is a circuit diagram illustrating a conventional NAND flash memory device.

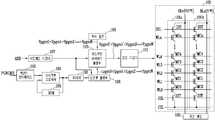

도 2는 본 발명의 바람직한 제1 실시예에 따른 낸드형 플래시 메모리 장치를 도시한 블록도이다.2 is a block diagram illustrating a NAND flash memory device according to a first embodiment of the present invention.

도 3은 도 1의 낸드 플래시 메모리 장치의 프로그램 전압의 파형을 도시한 파형도이다.FIG. 3 is a waveform diagram illustrating waveforms of program voltages of the NAND flash memory device of FIG. 1.

도 4는 본 발명의 바람직한 제2 실시예에 따른 낸드형 플래시 메모리 장치를 도시한 블록도이다.4 is a block diagram illustrating a NAND flash memory device according to a second embodiment of the present invention.

도 5는 도 2의 낸드형 플래시 메모리 장치의 프로그램 전압의 파형을 도시한 파형도이다.FIG. 5 is a waveform diagram illustrating waveforms of program voltages of the NAND flash memory device of FIG. 2.

< 도면의 주요 부분에 대한 부호의 설명 ><Description of Symbols for Main Parts of Drawings>

101, 121 : 메모리 셀 블록102, 122 : 센스앰프101, 121:

103, 123 : 커맨드 인터페이스104, 124 : 마이크로프로세서103, 123:

105, 125 : ROM106, 127 : 어드레스 디코더105, 125:

108, 126 : 타이머107, 129 : 오프셋 발생부108, 126:

109, 128 : 챠지 펌프110, 130 : 워드라인 바이어스 발생부109, 128:

111, 131 : 로오 디코더111, 131: roo decoder

본 발명은 불휘발성 메모리 장치 및 그것의 프로그램 방법에 관한 것으로, 특히 프로그램 동작시 각 워드라인에 따라 프로그램 전압을 다르게 인가하는 낸드형 플래시 메모리 장치 및 그것의 프로그램 방법에 관한 것이다.BACKGROUND OF THE INVENTION 1. Field of the Invention The present invention relates to a nonvolatile memory device and a program method thereof, and more particularly, to a NAND flash memory device and a program method thereof that apply a program voltage differently according to each word line during a program operation.

전기적으로 소거 및 프로그램이 가능한 불휘발성 메모리 장치 중 하나인 낸드형(NAND) 플래시 메모리 장치의 메모리 셀은 노트북, PDA(Personal Digital Assistants), 셀룰러 폰 등의 휴대 전화기, 컴퓨터 바이오스(BIOS), 프린터, USB(Universal Serial Bus) 드라이브 등에 사용되는 반도체 소자이다. 플래시 메모리 셀은 전기적으로 프로그램/소거가 가능한 소자로서 약 100Å의 얇은 터널 산화막으로 강한 전기장에 의해 전자가 이동하면서 셀의 문턱전압(Vt)을 변화시켜 프로그램/소거 기능을 수행한다.Memory cells in NAND flash memory devices, one of the electrically erasable and programmable nonvolatile memory devices, include mobile phones such as laptops, personal digital assistants (PDAs), cellular phones, computer BIOSes, printers, A semiconductor device used for a USB (Universal Serial Bus) drive. The flash memory cell is an electrically programmable / eraseable device, which is a thin tunnel oxide film of about 100 kW, and performs a program / erase function by changing the threshold voltage Vt of the cell while electrons are moved by a strong electric field.

도 1은 기존의 낸드형 플래시 메모리 장치의 메모리 셀 블록을 도시한 것이다.1 illustrates a memory cell block of a conventional NAND flash memory device.

도 1을 참조하면, 메모리 셀 블록(11)은 비트라인(BLe)에 연결된 셀 스트링(11a)과 비트라인(BLo)에 연결된 셀 스트링(11b)을 포함하고, 셀 스트링(11a, 11b) 은 메모리 셀(MC0~MCn)을 포함한다.Referring to FIG. 1, the

여기서, 타겟 문턱전압(Vt)이 같으면 메모리 셀(MC0~MCn)의 위치에 상관없이 동일한 펄스 폭과 동일한 전압 값을 갖는 프로그램 전압이 각 워드라인(WL0~WLn)에 인가되어 프로그램 동작이 수행되었다.Here, when the target threshold voltages Vt are the same, a program voltage having the same pulse width and the same voltage value is applied to each word line WL0 to WLn regardless of the positions of the memory cells MC0 to MCn to perform a program operation. .

그러나, 상술한 프로그램 전압으로 프로그램 동작을 수행하면, 센스앰프(12)를 기준으로 메모리 셀(MC0~MCn)의 위치에 따라 프로그램된 메모리 셀의 문턱전압(Vt)이 약간씩 다르게 되어 프로그램된 셀의 문턱전압 분포가 균일하지 않은 문제점이 있다.However, when the program operation is performed using the above-described program voltage, the threshold voltage Vt of the programmed memory cell is slightly different according to the positions of the memory cells MC0 to MCn based on the

본 발명은 프로그램하려는 메모리 셀들의 각 워드라인에 따라 프로그램 전압을 다르게 인가하여 프로그램된 메모리 셀의 문턱전압 분포를 균일하게 하는 것을 목적으로 한다.An object of the present invention is to equalize the threshold voltage distribution of a programmed memory cell by applying a different program voltage to each word line of memory cells to be programmed.

상술한 목적을 달성하기 위하여, 본 발명의 바람직한 실시예에 따른 불휘발성 메모리 장치는, 비트라인쌍을 이루는 비트라인들과 워드라인들의 교차영역에 배치되는 메모리 셀들로 이루어진 스트링을 복수개 포함하는 메모리 셀 블록; 프로그램 동작시에 프로그램 타임 정보를 제공하는 타임 제어부; 상기 워드라인들의 위치 정보를 제공하는 어드레스 디코더; 상기 워드라인들의 위치 정보와 상기 프로그램 타임 정보를 이용해서 서로 다른 펄스 구간을 갖는 오프셋 프로그램 펄스 신호들을 발생시키는 오프셋 발생부; 펌핑동작을 수행하여 고전압을 발생시키는 챠지 펌프; 및 상기 서로 다른 펄스 구간을 갖는 오프셋 프로그램 펄스 신호들에 의해 지정되는 구간에서만 상기 고전압을 전달하여 상기 워드라인들의 위치에 따라 서로 다른 값을 갖는 프로그램 전압을 발생시키고, 상기 워드라인들 중 해당 워드라인에 해당 프로그램 전압을 인가하는 로오(row) 경로 제어부를 포함한다.In order to achieve the above object, a nonvolatile memory device according to a preferred embodiment of the present invention, a memory cell including a plurality of strings consisting of memory cells arranged in the intersection of the bit lines and word lines forming a pair of bit lines block; A time controller for providing program time information during a program operation; An address decoder providing position information of the word lines; An offset generator for generating offset program pulse signals having different pulse intervals by using the position information of the word lines and the program time information; A charge pump generating a high voltage by performing a pumping operation; And transmitting the high voltage only in a section designated by offset program pulse signals having different pulse sections to generate program voltages having different values according to positions of the word lines, and corresponding word lines among the word lines. It includes a row path control unit for applying a corresponding program voltage to.

본 발명의 바람직한 다른 실시예에 따른 불휘발성 메모리 장치는 비트라인쌍을 이루는 비트라인들과 워드라인들의 교차영역에 배치되는 메모리 셀들로 이루어진 스트링을 복수개 포함하는 메모리 셀 블록; 프로그램 동작시에 프로그램 타임 정보를 이용해서 동일한 펄스 구간을 갖는 프로그램 펄스 신호를 제공하는 타임 제어부; 상기 워드라인들의 위치 정보를 제공하는 어드레스 디코더; 상기 워드라인들의 위치 정보을 이용해서 서로 다른 값을 갖는 오프셋 프로그램 전압을 발생시키는 오프셋 전압 발생부; 및 상기 동일한 펄스 구간을 갖는 프로그램 펄스 신호들에 의해 지정되는 구간에서만 상기 서로 다른 값을 갖는 오프셋 프로그램 전압을 전달하여 상기 워드라인들의 위치에 따라 다른 값을 갖는 프로그램 전압을 발생시키고, 상기 워드라인들 중 해당 워드라인에 해당 프로그램 전압을 인가하는 로오(row) 경로 제어부를 포함한다.A nonvolatile memory device according to another exemplary embodiment of the present invention may include a memory cell block including a plurality of strings of memory cells disposed in an intersection region of bit lines and word lines forming a pair of bit lines; A time controller for providing a program pulse signal having the same pulse duration by using program time information during a program operation; An address decoder providing position information of the word lines; An offset voltage generator configured to generate offset program voltages having different values using position information of the word lines; And transmitting the offset program voltage having different values only in a period designated by the program pulse signals having the same pulse period to generate a program voltage having a different value according to the position of the word lines. And a row path controller for applying a corresponding program voltage to a corresponding word line.

본 발명의 바람직한 또 다른 실시예에 따른, 비트라인쌍을 이루는 비트라인들과 워드라인들의 교차영역에 배치되는 메모리 셀들로 이루어진 스트링을 복수개 포함하는 메모리 셀 블록을 포함하는 불휘발성 메모리 장치의 프로그램 방법은 기 워드라인들의 위치에 따라 다른 값을 갖는 프로그램 전압을 발생시키는 단계; 및 상기 워드라인들 중 해당 워드라인에 상기 다른 값을 갖는 프로그램 전압 중 해당 프로그램 전압을 인가하는 단계를 포함한다.According to still another preferred embodiment of the present invention, a program method of a nonvolatile memory device including a memory cell block including a plurality of strings of memory cells disposed in an intersection of bit lines forming a pair of bit lines and word lines. Generating a program voltage having a different value depending on the position of the existing word lines; And applying a corresponding program voltage among program voltages having the different value to corresponding word lines among the word lines.

이하, 첨부된 도면을 참조하여 본 발명의 바람직한 실시예들을 상세히 설명하기로 한다. 그러나, 본 발명은 이하에서 개시되는 실시예에 한정되는 것이 아니라 서로 다른 다양한 형태로 구현될 수 있으며, 단지 본 실시예는 본 발명의 개시가 완전하도록 하며 통상의 지식을 가진자에게 발명의 범주를 완전하게 알려주기 위해 제공되는 것이다.Hereinafter, exemplary embodiments of the present invention will be described in detail with reference to the accompanying drawings. However, the present invention is not limited to the embodiments disclosed below, but can be implemented in various forms, and only the present embodiments are intended to complete the disclosure of the present invention and to those skilled in the art. It is provided for complete information.

도 2는 본 발명의 바람직한 제1 실시예에 따른 낸드형 플래시 메모리 장치를 나타내고, 도 3은 낸드 플래시 메모리 장치의 각 워드라인에 인가되는 프로그램 전압의 파형을 나타낸다.2 illustrates a NAND flash memory device according to a first exemplary embodiment of the present invention, and FIG. 3 illustrates waveforms of program voltages applied to respective word lines of the NAND flash memory device.

이하, 도 2 및 도 3을 참조하면서 각 워드라인에 따라 프로그램 전압을 다르게 인가하기 위한 제1 실시예를 설명하기로 한다.Hereinafter, a first embodiment for differently applying a program voltage according to each word line will be described with reference to FIGS. 2 and 3.

도 2를 참조하면, 낸드형 플래시 메모리 장치는 메모리 셀 블록(101), 센스앰프(102), 커맨드 인터페이스(103), 마이크로프로세서(104), ROM(105), 타이머(106), 어드레스 디코더(107), 오프셋 발생부(108), 챠지 펌프(109), 워드라인 바이어스 발생부(110), 및 로오 디코더(111)를 포함한다.2, a NAND flash memory device includes a

메모리 셀 블록(101)은 셀 스트링들(101a, 101b)을 포함하는데, 이들 셀 스트링은 도시하지 않았지만 N개가 존재한다. 셀 스트링 내에 있는 메모리 셀 (MC0~MCn)들은 드레인 선택 트랜지스터(DST)와 소스 선택 트랜지스터(SST) 사이에 직렬로 접속되며, 드레인 선택 트랜지스터(DST)는 각 비트라인(BLe, BLo)에 접속되고, 소스 선택 트랜지스터(SST)는 공통 소스 라인(CSL)에 접속된다. BLe는 짝수번째 비트라인을 나타내고, BLo는 홀수번째 비트라인을 나타낸다. 메모리 셀들(예컨대, M1)은 하나의 워드라인(예컨대, WL1)에 의해 제어되며, 하나의 페이지를 형성한다.The

센스앰프(102)는 이븐 비트라인(BLe)과 오드 비트라인(BLo)에 연결되어 비트라인을 통해서 전달되는 데이터를 증폭하여 출력한다. 메모리 셀들(MC0~MCn)은 센스앰프(102)쪽에서 봤을 때 메모리 셀(MC0)이 가장 가깝고 메모리 셀(MCn)이 가장 멀다.The

본 발명의 제1 실시예에서는, 센스앰프(102)에서 가장 가까운 곳에 위치한 메모리 셀(MCO)의 워드라인(WL0)에 인가되는 고전압, 즉 프로그램 전압의 펄스 폭(tpgm0)을 가장 좁게 하고, 센스앰프(102)에서 가장 먼 곳에 위치한 메모리 셀(MCn)의 워드라인(WLn)에 인가되는 프로그램 전압의 펄스 폭(tpgmN)을 가장 넓게 함으로써, 각 메모리 셀(MC0~MCn)에 저장된 데이터를 센싱(독출 또는 검증할 때)할 때 발생하는 프로그램 문턱전압 분포를 균일하게 할 수 있다.In the first embodiment of the present invention, the pulse voltage tpgm0 of the high voltage applied to the word line WL0 of the memory cell MCO located closest to the

우선, 커맨드 인터페이스(103)는 프로그램 명령(PGMCOM)이 입력되면 마이크로프로세서(104)로 하여금 프로그램 알고리즘을 수행하도록 하게 한다. 프로그램 명령을 인가받은 마이크로프로세서(104)가, ROM(105)에게 프로그램을 수행해야 한다는 것을 알려주면, ROM(105)은 저장되어 있던 프로그램 타임 정보를 마이크로프 로세서(104)로 전달한다. 그러면, 마이크로프로세서(104)는 ROM(105)로부터 전달된 프로그램 타임 정보를 읽어서 타이머(106)에 로딩시키고, 타이머(106)는 프로그램 타임 정보를 이용해서 프로그램 펄스 구간을 결정한다.First, the

어드레스 디코더(106)는 어드레스(ADD)를 입력받아 오프셋 발생부(107)와 워드라인 바이어스 발생부(110)에 워드라인 위치 정보를 전달한다.The

오프셋 발생부(108)는 어드레스 디코더(106)로부터 전달받은 워드라인 위치 정보와 타이머(106)로부터 전달받은 프로그램 펄스 구간 정보를 이용해서 워드라인의 위치에 따라 프로그램 펄스 구간을 다르게 지정하는 오프셋 프로그램 펄스 신호(tpgm0<tpgm1<...tpgmN)를 발생시킨다(도 3 참조).The

챠지 펌프(109)는 펌핑 동작을 수행해서 고전압(Vpgm0=Vpgm1..=VpgmN)을 발생시킨다.The

워드라인 바이어스 발생부(110)는 오프셋 프로그램 펄스 신호(tpgm0<tpgm1<..<tpgmN)가 지정하는 구간동안에만 챠지 펌프(109)에서 발생된 고전압(Vpgm0=Vpgm1..=VpgmN)을 전달하여 최종 프로그램 전압, 즉 워드라인 바이어스 전압(Vpgm0'<Vpgm1'...<VpgmN')을 발생시킨다.The word

이러한 워드라인 바이어스 발생부(110)는 여러개의 고전압 스위치(글로벌 워드라인 수만큼)로 구성되며, 그 고전압 스위치의 인에이블 신호로서 오프셋 발생부(108)로부터 발생된 오프셋 프로그램 펄스 신호(tpgm0<tpgm1<..<tpgmN)와 어드레스 디코더(107)로부터 발생된 워드라인 위치 정보를 조합한 신호를 사용하고, 공급전압으로서는 챠지 펌프(109)로부터 발생된 고전압(Vpgm0=Vpgm1..=VpgmN)을 사용한 다.The word

로우 디코더(111)는 블록 어드레스(미도시)로부터 해당 블록만을 인에이블시켜서, 워드라인 바이어스 발생부(110)로부터 출력되는 워드라인 바이어스 전압(Vpgm0'<Vpgm1'...<VpgmN')을 해당 로컬 워드라인(WL0~WLn)에 전달한다.The

구체적으로 설명하면, 워드라인(WL0)이 프로그램될 대상이면, 워드라인 바이어스 발생부(110)가 오프셋 프로그램 펄스 신호(tpgm0)가 지정하는 펄스구간동안에만 고전압(Vpgm0)을 인가하여 워드라인 바이어스 전압(Vpgm0')을 발생시키고, 로우 디코더(111)는 워드라인 바이어스 전압(Vpgm0')을 입력받아 해당 워드라인(WL0)에 인가한다. 만약, 워드라인(WLn)이 프로그램될 대상이면, 워드라인 바이어스 발생부(110)가 오프셋 프로그램 펄스 신호(tpgmN)가 지정하는 펄스구간동안에만 고전압(VpgmN)를 인가하여 워드라인 바이어스 전압(VpgmN')을 발생시키고, 로우 디코더(111)는 워드라인 바이어스 전압(VpgmN')을 입력받아 해당 로컬 워드라인(WLn)에 인가한다.In detail, if the word line WL0 is to be programmed, the word

상술한 바와 같이, 센스앰프(102)를 기준으로 가장 가까운 워드라인(WL0)에 가장 작은 값을 갖는 워드라인 바이어스 전압(Vpgm0')을 인가하고, 가장 먼 워드라인(WLn)에 가장 큰 값을 갖는 워드라인 바이어스 전압(VpgmN')을 인가하면, 즉 워드라인의 위치에 따라 워드라인 바이어스 전압을 다르게 인가하면, 프로그램된 셀의 문턱전압 분포를 균일하게 할 수 있다.As described above, the word line bias voltage Vpgm0 'having the smallest value is applied to the word line WL0 closest to the

도 4는 본 발명의 바람직한 제2 실시예에 따른 낸드형 플래시 메모리 장치를 나타내고, 도 5는 도 4의 낸드형 플래시 메모리 장치의 프로그램 전압의 파형을 나 타낸다.4 illustrates a NAND flash memory device according to a second exemplary embodiment of the present invention, and FIG. 5 illustrates waveforms of program voltages of the NAND flash memory device of FIG. 4.

도 4를 참조하면, 낸드형 플래시 메모리 장치는 메모리 셀 블록(121), 센스앰프(122), 커맨드 인터페이스(123), 마이크로프로세서(124), ROM(125), 타이머(126), 어드레스 디코더(127), 챠지 펌프(128), 오프셋 전압 발생부(129), 워드라인 바이어스 발생부(130), 및 로오 디코더(131)를 포함한다.Referring to FIG. 4, a NAND flash memory device may include a

여기서, 메모리 셀 블록(121)은 도 2에 도시한 메모리 셀 블록(111)과 동일한 구성을 가지므로 도 2의 메모리 셀 블록(101)에 대한 구성설명을 참조하기 바란다.Here, since the

본 발명의 제2 실시예에서는, 센스앰프(122)에서 가장 가까운 곳에 위치한 메모리 셀(MCO)의 워드라인(WL0)에 인가되는 고전압, 즉 프로그램 전압(Vpgm0)의 값을 도 5에 도시한 바와 같이 가장 작게 하고, 센스앰프(102)에서 가장 먼 곳에 위치한 메모리 셀(MCn)의 워드라인(WLn)에 인가되는 고전압(VpgmN)의 값을 가장 크게 함으로써, 각 메모리 셀에 저장된 데이터를 센싱(독출 및 검증할 때)할 때 발생하는 프로그램 문턱전압 분포를 균일하게 할 수 있다.In the second embodiment of the present invention, the high voltage applied to the word line WL0 of the memory cell MCO located closest to the

우선, 커맨드 인터페이스(123)는 프로그램 명령(PGMCOM)이 입력되면 마이크로프로세서(124)로 하여금 프로그램 알고리즘을 수행하도록 하게 한다. 이러한 프로그램 명령을 인가받은 마이크로프로세서(124)가 ROM(125)에게 프로그램을 수행해야 한다는 것을 알려주면, ROM(125)은 저장되어 있던 프로그램 타임 정보를 마이크로프로세서(124)로 전달하고, 마이크로프로세서(124)는 ROM(125)로부터 전달받은 프로그램 타임 정보를 타이머(126)로 전달한다. 타이머(126)는 프로그램 타임 정보 를 이용해서 프로그램 펄스 구간을 지정하는 프로그램 펄스 신호(tpgm0=tpgm1...=tpgmN)를 발생한다. 프로그램 펄스 신호들(tpgm0=tpgm1...=tpgmN)의 펄스 폭은 모두 동일하다.First, the

어드레스 디코더(127)는 어드레스(ADD)를 입력받아 오프셋 전압 발생부(129)와 워드라인 바이어스 발생부(130)에 워드라인 위치 정보를 전달한다.The

챠지 펌프(128)는 핌핑동작을 수행하여 고전압, 즉 프로그램 전압을 발생시킨다.The

오프셋 전압 발생부(129)는 어드레스 디코더(127)로부터 발생된 워드라인 위치 정보와 챠지 펌프(128)에서 발생된 고전압을 이용해서 오프셋 프로그램 전압(Vpgm0<Vpgm1...<VpgmN)을 발생시킨다.The offset

워드라인 바이어스 발생부(130)는 프로그램 펄스 신호(tpgm0~tpgmN)가 지정하는 구간동안에만 오프셋 프로그램 전압(Vpgm0<Vpgm1...<VpgmN)을 전달하여 최종 프로그램 전압, 즉 워드라인 바이어스 전압(Vpgm0'<Vpgm1'...<VpgmN')을 발생시킨다.The word

이러한 워드라인 바이어스 발생부(130)는 여러개의 고전압 스위치(글로벌 워드라인 개수만큼)로 구성되며, 그 고전압 스위치의 인에이블 신호로서 타이머(126)로부터 발생된 프로그램 펄스 신호(tpgm0=tpgm1...=tpgmN)와 어드레스 디코더(127)로부터 발생된 워드라인 위치 정보를 조합한 신호를 사용하고, 공급전압으로서는 오프셋 전압 발생부(129)로부터 발생된 오프셋 프로그램 전압(Vpgm0<Vpgm1...<VpgmN)을 사용한다.The word line

로우 디코더(131)는 블록 어드레스(미도시)로부터 해당 블록만을 인에이블시켜서, 워드라인 바이어스 전압(Vpgm0'<Vpgm1'<..VpgmN')를 해당 로컬 워드라인(WL0~WLn)에 전달한다.The

구체적으로 설명하면, 워드라인(WL0)이 프로그램될 대상이면, 워드라인 바이어스 발생부(130)가 프로그램 펄스 신호(tpgm0)가 지정하는 구간동안에만 오프셋 프로그램 전압(Vpgm0)을 인가하여 워드라인 바이어스 전압(Vpgm0')을 발생시키고, 로우 디코더(131)는 워드라인 바이어스 전압(Vpgm0')을 입력받아 해당 워드라인(WL0)에 인가한다. 만약, 워드라인(WLn)이 프로그램될 대상이면, 워드라인 바이어스 발생부(130)가 프로그램 펄스 신호(tpgmN)가 지정하는 구간동안에만 오프셋 프로그램 전압(VpgmN)을 인가하여 워드라인 바이어스 전압(VpgmN')을 발생시키고, 로우 디코더(131)는 워드라인 바이어스 전압(VpgmN')을 입력받아 해당 워드라인(WLn)에 인가한다.In detail, if the word line WL0 is to be programmed, the word

상술한 바와 같이, 센스앰프(122)를 기준으로 가장 가까운 워드라인(WL0)에 가장 작은 값을 갖는 워드라인 바이어스 전압(Vpgm0')을 인가하고, 가장 먼 워드라인(WLn)에 가장 큰 값을 갖는 워드라인 바이어스 전압(VpgmN')을 인가하면, 즉 워드라인의 위치에 따라 워드라인 바이어스 전압을 다르게 인가하면, 프로그램된 셀의 문턱전압 분포를 균일하게 할 수 있다.As described above, the word line bias voltage Vpgm0 'having the smallest value is applied to the word line WL0 closest to the

상기에서 설명한 본 발명의 기술적 사상은 바람직한 실시예에서 구체적으로 기술되었으나, 상기한 실시예는 그 설명을 위한 것이며, 그 제한을 위한 것이 아님을 주의하여야 한다. 또한, 본 발명은 본 발명의 기술 분야에서 통상의 지식을 가 진 자라면 본 발명의 기술적 사상의 범위 내에서 다양한 실시예가 가능함을 이해할 수 있을 것이다.Although the technical spirit of the present invention described above has been described in detail in a preferred embodiment, it should be noted that the above embodiment is for the purpose of description and not of limitation. In addition, the present invention will be understood by those of ordinary skill in the art that various embodiments are possible within the scope of the technical idea of the present invention.

상술한 바와 같이, 본 발명에 따르면, 워드라인의 위치에 따라 워드라인 바이어스 전압을 다르게 인가할 수 있어, 프로그램된 셀의 문턱전압 분포를 균일하게 할 수 있는 이점이 있다.As described above, according to the present invention, the word line bias voltage may be differently applied according to the position of the word line, thereby making it possible to uniformize the threshold voltage distribution of the programmed cell.

Claims (11)

Translated fromKoreanPriority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020050023477AKR100672151B1 (en) | 2005-03-22 | 2005-03-22 | Nonvolatile Memory Device and Its Program Method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020050023477AKR100672151B1 (en) | 2005-03-22 | 2005-03-22 | Nonvolatile Memory Device and Its Program Method |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20060101898Atrue KR20060101898A (en) | 2006-09-27 |

| KR100672151B1 KR100672151B1 (en) | 2007-01-19 |

Family

ID=37632843

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020050023477AExpired - Fee RelatedKR100672151B1 (en) | 2005-03-22 | 2005-03-22 | Nonvolatile Memory Device and Its Program Method |

Country Status (1)

| Country | Link |

|---|---|

| KR (1) | KR100672151B1 (en) |

Cited By (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100699852B1 (en)* | 2005-07-14 | 2007-03-27 | 삼성전자주식회사 | Word Line Decoder of Nonvolatile Memory Device Using HPMOOS |

| US7778084B2 (en) | 2007-02-27 | 2010-08-17 | Samsung Electronics Co., Ltd. | Non-volatile memory devices and operating methods thereof |

| US8942046B2 (en) | 2012-04-26 | 2015-01-27 | Samsung Electronics Co., Ltd. | Method of programming a 3-dimensional nonvolatile memory device based on a program order of a selected page and a location of a string selection line |

| US8964476B2 (en) | 2010-02-17 | 2015-02-24 | Samsung Electronics Co., Ltd. | Non-volatile memory devices, operating methods thereof and memory systems including the same |

| KR20160035443A (en)* | 2014-09-23 | 2016-03-31 | 에스케이하이닉스 주식회사 | 3d nonvolatile semiconductor memory device, data storage device and user device using variable incremental step pulse programming |

| US9378831B2 (en) | 2010-02-09 | 2016-06-28 | Samsung Electronics Co., Ltd. | Nonvolatile memory devices, operating methods thereof and memory systems including the same |

| US9881685B2 (en) | 2010-08-26 | 2018-01-30 | Samsung Electronics Co., Ltd. | Nonvolatile memory device, operating method thereof and memory system including the same |

| CN107945831A (en)* | 2016-10-12 | 2018-04-20 | 北京京存技术有限公司 | Reduce the circuit and nand flash memory of nand flash memory programming settling time |

| US10217516B2 (en) | 2010-02-09 | 2019-02-26 | Samsung Electronics Co., Ltd. | Nonvolatile memory devices, operating methods thereof and memory systems including the same |

| CN110021331A (en)* | 2018-01-08 | 2019-07-16 | 三星电子株式会社 | Memory device |

| CN114121095A (en)* | 2020-08-31 | 2022-03-01 | 美光科技公司 | memory cell programming |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9324440B2 (en) | 2010-02-09 | 2016-04-26 | Samsung Electronics Co., Ltd. | Nonvolatile memory devices, operating methods thereof and memory systems including the same |

| US8908431B2 (en) | 2010-02-17 | 2014-12-09 | Samsung Electronics Co., Ltd. | Control method of nonvolatile memory device |

| US8923060B2 (en) | 2010-02-17 | 2014-12-30 | Samsung Electronics Co., Ltd. | Nonvolatile memory devices and operating methods thereof |

| JP5788183B2 (en) | 2010-02-17 | 2015-09-30 | 三星電子株式会社Samsung Electronics Co.,Ltd. | Nonvolatile memory device, method of operating the same, and memory system including the same |

| JP2011170956A (en) | 2010-02-18 | 2011-09-01 | Samsung Electronics Co Ltd | Nonvolatile memory device, programming method thereof and memory system including the same |

| US8792282B2 (en) | 2010-03-04 | 2014-07-29 | Samsung Electronics Co., Ltd. | Nonvolatile memory devices, memory systems and computing systems |

| US8553466B2 (en) | 2010-03-04 | 2013-10-08 | Samsung Electronics Co., Ltd. | Non-volatile memory device, erasing method thereof, and memory system including the same |

| KR101762828B1 (en) | 2011-04-05 | 2017-07-31 | 삼성전자주식회사 | Nonvolatile memory device and operating method of nonvolatile memory device |

| KR102242022B1 (en) | 2013-09-16 | 2021-04-21 | 삼성전자주식회사 | Nonvolatile memory device and program method using thereof |

| KR102634418B1 (en)* | 2016-12-07 | 2024-02-06 | 에스케이하이닉스 주식회사 | Semiconductor memory device and operating method thereof |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100463194B1 (en)* | 2001-02-16 | 2004-12-23 | 삼성전자주식회사 | Method for programming a nand-type flash memory |

| JP2003109389A (en) | 2001-09-28 | 2003-04-11 | Fujitsu Ltd | Semiconductor storage device |

| KR20050075548A (en)* | 2004-01-15 | 2005-07-21 | 주식회사 테라반도체 | Non-volatile semiconductor memory device with program start voltage control circuit |

| KR100632942B1 (en)* | 2004-05-17 | 2006-10-12 | 삼성전자주식회사 | How to Program a Nonvolatile Memory Device |

- 2005

- 2005-03-22KRKR1020050023477Apatent/KR100672151B1/ennot_activeExpired - Fee Related

Cited By (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100699852B1 (en)* | 2005-07-14 | 2007-03-27 | 삼성전자주식회사 | Word Line Decoder of Nonvolatile Memory Device Using HPMOOS |

| US7778084B2 (en) | 2007-02-27 | 2010-08-17 | Samsung Electronics Co., Ltd. | Non-volatile memory devices and operating methods thereof |

| US9378831B2 (en) | 2010-02-09 | 2016-06-28 | Samsung Electronics Co., Ltd. | Nonvolatile memory devices, operating methods thereof and memory systems including the same |

| US10217516B2 (en) | 2010-02-09 | 2019-02-26 | Samsung Electronics Co., Ltd. | Nonvolatile memory devices, operating methods thereof and memory systems including the same |

| US10650903B2 (en) | 2010-02-17 | 2020-05-12 | Samsung Electronics Co., Ltd. | Non-volatile memory devices, operating methods thereof and memory systems including the same |

| US11062784B2 (en) | 2010-02-17 | 2021-07-13 | Samsung Electronics Co., Ltd. | Non-volatile memory devices, operating methods thereof and memory systems including the same |

| US12322457B2 (en) | 2010-02-17 | 2025-06-03 | Samsung Electronics Co., Ltd. | Nonvolatile memory devices, operating methods thereof and memory systems including the same |

| US9390803B2 (en) | 2010-02-17 | 2016-07-12 | Samsung Electronics Co., Ltd. | Non-volatile memory devices, operating methods thereof and memory systems including the same |

| US9747995B2 (en) | 2010-02-17 | 2017-08-29 | Samsung Electronics Co., Ltd. | Nonvolatile memory devices, operating methods thereof and memory systems including the same |

| US11715537B2 (en) | 2010-02-17 | 2023-08-01 | Samsung Electronics Co., Ltd. | Non-volatile memory devices, operating methods thereof and memory systems including the same |

| US9330770B2 (en) | 2010-02-17 | 2016-05-03 | Samsung Electronics Co., Ltd. | Non-volatile memory devices, operating methods thereof and memory systems including the same |

| US8964476B2 (en) | 2010-02-17 | 2015-02-24 | Samsung Electronics Co., Ltd. | Non-volatile memory devices, operating methods thereof and memory systems including the same |

| US10199116B2 (en) | 2010-02-17 | 2019-02-05 | Samsung Electronics Co., Ltd. | Non-volatile memory devices, operating methods thereof and memory systems including the same |

| US9947416B2 (en) | 2010-08-26 | 2018-04-17 | Samsung Electronics Co., Ltd. | Nonvolatile memory device, operating method thereof and memory system including the same |

| US9881685B2 (en) | 2010-08-26 | 2018-01-30 | Samsung Electronics Co., Ltd. | Nonvolatile memory device, operating method thereof and memory system including the same |

| US8942046B2 (en) | 2012-04-26 | 2015-01-27 | Samsung Electronics Co., Ltd. | Method of programming a 3-dimensional nonvolatile memory device based on a program order of a selected page and a location of a string selection line |

| KR20160035443A (en)* | 2014-09-23 | 2016-03-31 | 에스케이하이닉스 주식회사 | 3d nonvolatile semiconductor memory device, data storage device and user device using variable incremental step pulse programming |

| CN107945831A (en)* | 2016-10-12 | 2018-04-20 | 北京京存技术有限公司 | Reduce the circuit and nand flash memory of nand flash memory programming settling time |

| CN107945831B (en)* | 2016-10-12 | 2020-09-18 | 北京兆易创新科技股份有限公司 | Circuit for reducing programming setup time of NAND flash memory and NAND flash memory |

| CN110021331A (en)* | 2018-01-08 | 2019-07-16 | 三星电子株式会社 | Memory device |

| CN114121095A (en)* | 2020-08-31 | 2022-03-01 | 美光科技公司 | memory cell programming |

Also Published As

| Publication number | Publication date |

|---|---|

| KR100672151B1 (en) | 2007-01-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100672151B1 (en) | Nonvolatile Memory Device and Its Program Method | |

| JP4170682B2 (en) | Nonvolatile semiconductor memory device | |

| KR100855963B1 (en) | Program, Read, and Eraser Methods of Nonvolatile Memory Devices and Nonvolatile Memory Devices | |

| KR100967000B1 (en) | How to Program Nonvolatile Memory Devices | |

| KR20130139598A (en) | Semiconductor memory device and method of operating the same | |

| KR20130098643A (en) | Nonvolatile memory device and embeded memory system comprising the same | |

| KR20090121984A (en) | Erasing Method of Nonvolatile Memory Device | |

| KR101185552B1 (en) | Non-volatile memory and method of verify the same | |

| KR100845530B1 (en) | Flash memory device and its operation method | |

| US8743620B2 (en) | Nonvolatile memory device and program verify method thereof | |

| KR20090054125A (en) | Flash memory device and its reading method | |

| JP4007909B2 (en) | Method for erasing data in nonvolatile semiconductor memory device | |

| CN103578557B (en) | Nonvolatile semiconductor memory device and reading method thereof | |

| JP2012069203A (en) | Nonvolatile semiconductor memory device and driving method for nonvolatile semiconductor memory device | |

| KR20090086819A (en) | Flash memory device | |

| KR102211220B1 (en) | Semiconductor device and operating method thereof | |

| US8767474B2 (en) | Nonvolatile memory device and method for controlling the same | |

| KR102153017B1 (en) | Semiconductor memory device and operation method thereof | |

| US8773901B2 (en) | Nonvolatile memory device preventing shift in threshold voltage of erase cell and program method thereof | |

| KR100972715B1 (en) | Flash memory device and program operation method thereof | |

| US20120140572A1 (en) | Semiconductor memory device and method of operating the same | |

| KR20120088451A (en) | Semiconductor memory apparatus and method of erasing data | |

| TWI451417B (en) | Method and apparatus for reducing read disturb in nand nonvolatile memory | |

| KR20120005836A (en) | Semiconductor memory device and erase method thereof | |

| KR20120078839A (en) | Semiconductor memory device and erase method thereof |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| PA0109 | Patent application | St.27 status event code:A-0-1-A10-A12-nap-PA0109 | |

| PA0201 | Request for examination | St.27 status event code:A-1-2-D10-D11-exm-PA0201 | |

| D13-X000 | Search requested | St.27 status event code:A-1-2-D10-D13-srh-X000 | |

| D14-X000 | Search report completed | St.27 status event code:A-1-2-D10-D14-srh-X000 | |

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection | St.27 status event code:A-1-2-D10-D21-exm-PE0902 | |

| P11-X000 | Amendment of application requested | St.27 status event code:A-2-2-P10-P11-nap-X000 | |

| P13-X000 | Application amended | St.27 status event code:A-2-2-P10-P13-nap-X000 | |

| PG1501 | Laying open of application | St.27 status event code:A-1-1-Q10-Q12-nap-PG1501 | |

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration | St.27 status event code:A-1-2-D10-D22-exm-PE0701 | |

| PR1002 | Payment of registration fee | St.27 status event code:A-2-2-U10-U11-oth-PR1002 Fee payment year number:1 | |

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment | St.27 status event code:A-2-4-F10-F11-exm-PR0701 | |

| PG1601 | Publication of registration | St.27 status event code:A-4-4-Q10-Q13-nap-PG1601 | |

| PR1001 | Payment of annual fee | St.27 status event code:A-4-4-U10-U11-oth-PR1001 Fee payment year number:4 | |

| FPAY | Annual fee payment | Payment date:20101224 Year of fee payment:5 | |

| PR1001 | Payment of annual fee | St.27 status event code:A-4-4-U10-U11-oth-PR1001 Fee payment year number:5 | |

| LAPS | Lapse due to unpaid annual fee | ||

| PC1903 | Unpaid annual fee | St.27 status event code:A-4-4-U10-U13-oth-PC1903 Not in force date:20120116 Payment event data comment text:Termination Category : DEFAULT_OF_REGISTRATION_FEE | |

| PN2301 | Change of applicant | St.27 status event code:A-5-5-R10-R13-asn-PN2301 St.27 status event code:A-5-5-R10-R11-asn-PN2301 | |

| PC1903 | Unpaid annual fee | St.27 status event code:N-4-6-H10-H13-oth-PC1903 Ip right cessation event data comment text:Termination Category : DEFAULT_OF_REGISTRATION_FEE Not in force date:20120116 | |

| PN2301 | Change of applicant | St.27 status event code:A-5-5-R10-R13-asn-PN2301 St.27 status event code:A-5-5-R10-R11-asn-PN2301 | |

| PN2301 | Change of applicant | St.27 status event code:A-5-5-R10-R13-asn-PN2301 St.27 status event code:A-5-5-R10-R11-asn-PN2301 | |

| P22-X000 | Classification modified | St.27 status event code:A-4-4-P10-P22-nap-X000 | |

| P22-X000 | Classification modified | St.27 status event code:A-4-4-P10-P22-nap-X000 |