KR102806630B1 - 3d nand 구조체들에 텅스텐 및 다른 금속들을 증착하는 방법 - Google Patents

3d nand 구조체들에 텅스텐 및 다른 금속들을 증착하는 방법Download PDFInfo

- Publication number

- KR102806630B1 KR102806630B1KR1020207034800AKR20207034800AKR102806630B1KR 102806630 B1KR102806630 B1KR 102806630B1KR 1020207034800 AKR1020207034800 AKR 1020207034800AKR 20207034800 AKR20207034800 AKR 20207034800AKR 102806630 B1KR102806630 B1KR 102806630B1

- Authority

- KR

- South Korea

- Prior art keywords

- pulses

- metal precursor

- tungsten

- inert gas

- pulse

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/04—Coating on selected surface areas, e.g. using masks

- C23C16/045—Coating cavities or hollow spaces, e.g. interior of tubes; Infiltration of porous substrates

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/285—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation

- H01L21/28506—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers

- H01L21/28512—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table

- H01L21/28556—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table by chemical means, e.g. CVD, LPCVD, PECVD, laser CVD

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/02—Pretreatment of the material to be coated

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/02—Pretreatment of the material to be coated

- C23C16/0272—Deposition of sub-layers, e.g. to promote the adhesion of the main coating

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/06—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the deposition of metallic material

- C23C16/08—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the deposition of metallic material from metal halides

- C23C16/14—Deposition of only one other metal element

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/44—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/44—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating

- C23C16/455—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating characterised by the method used for introducing gases into reaction chamber or for modifying gas flows in reaction chamber

- C23C16/45523—Pulsed gas flow or change of composition over time

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/44—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating

- C23C16/455—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating characterised by the method used for introducing gases into reaction chamber or for modifying gas flows in reaction chamber

- C23C16/45523—Pulsed gas flow or change of composition over time

- C23C16/45525—Atomic layer deposition [ALD]

- C23C16/45527—Atomic layer deposition [ALD] characterized by the ALD cycle, e.g. different flows or temperatures during half-reactions, unusual pulsing sequence, use of precursor mixtures or auxiliary reactants or activations

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/44—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating

- C23C16/54—Apparatus specially adapted for continuous coating

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02205—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/0226—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process

- H01L21/02263—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase

- H01L21/02271—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition

- H01L21/0228—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition deposition by cyclic CVD, e.g. ALD, ALE, pulsed CVD

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/28008—Making conductor-insulator-semiconductor electrodes

- H01L21/28017—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon

- H01L21/28158—Making the insulator

- H01L21/28167—Making the insulator on single crystalline silicon, e.g. using a liquid, i.e. chemical oxidation

- H01L21/28194—Making the insulator on single crystalline silicon, e.g. using a liquid, i.e. chemical oxidation by deposition, e.g. evaporation, ALD, CVD, sputtering, laser deposition

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/285—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation

- H01L21/28506—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers

- H01L21/28512—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table

- H01L21/28556—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table by chemical means, e.g. CVD, LPCVD, PECVD, laser CVD

- H01L21/28562—Selective deposition

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/67005—Apparatus not specifically provided for elsewhere

- H01L21/67011—Apparatus for manufacture or treatment

- H01L21/67017—Apparatus for fluid treatment

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/20—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by three-dimensional arrangements, e.g. with cells on different height levels

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/30—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region

- H10B41/35—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region with a cell select transistor, e.g. NAND

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76841—Barrier, adhesion or liner layers

- H01L21/76871—Layers specifically deposited to enhance or enable the nucleation of further layers, i.e. seed layers

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01074—Tungsten [W]

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B43/00—EEPROM devices comprising charge-trapping gate insulators

- H10B43/20—EEPROM devices comprising charge-trapping gate insulators characterised by three-dimensional arrangements, e.g. with cells on different height levels

- H10B43/23—EEPROM devices comprising charge-trapping gate insulators characterised by three-dimensional arrangements, e.g. with cells on different height levels with source and drain on different levels, e.g. with sloping channels

- H10B43/27—EEPROM devices comprising charge-trapping gate insulators characterised by three-dimensional arrangements, e.g. with cells on different height levels with source and drain on different levels, e.g. with sloping channels the channels comprising vertical portions, e.g. U-shaped channels

Landscapes

- Chemical & Material Sciences (AREA)

- Engineering & Computer Science (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Materials Engineering (AREA)

- Mechanical Engineering (AREA)

- Metallurgy (AREA)

- Organic Chemistry (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Crystallography & Structural Chemistry (AREA)

- Chemical Vapour Deposition (AREA)

- Electrodes Of Semiconductors (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

Abstract

Description

참조로서 인용

PCT 신청 양식이 본 출원의 일부로서 본 명세서와 동시에 제출되었다. 본 출원이 동시에 제출된 PCT 신청 양식에서 식별된 바와 같이 우선권 또는 이익을 주장하는 출원 각각은 전체가 모든 목적들을 위해 참조로서 인용되었다.

텅스텐-함유 재료들의 증착은 많은 반도체 제조 프로세스들의 필수적인 부분이다. 이들 재료들은 수평 상호접속부들, 인접한 금속 층들 사이의 비아들, 및 금속 층들과 디바이스들 사이의 콘택트들일 수도 있다. 종래의 텅스텐 증착 프로세스에서, 기판은 진공 챔버의 프로세스 온도로 가열되고 시드 층 (또한 핵생성 층이라고 함) 으로서 역할을 하는 텅스텐 막의 매우 박형의 부분이 증착된다. 그 후, 텅스텐 막의 나머지 (벌크 층으로 지칭됨) 는 CVD (chemical vapor deposition) 프로세스에서 동시에 2 개의 반응물질들에 기판을 노출함으로써 핵생성 층 상에 증착된다. 벌크 층은 일반적으로 핵생성 층보다 신속하게 증착된다. 그러나, 디바이스들이 축소되고 보다 복잡한 패터닝 스킴들이 산업계에서 활용됨에 따라, 박형의 텅스텐 막들의 증착이 어려워진다. 3D NAND 구조체들과 같은 복잡한 고 종횡비 구조체들의 증착이 특히 어렵다.

피처들을 금속-함유 재료들로 충진하기 위한 방법들 및 장치들이 본 명세서에 제공된다. 본 개시의 일 양태는 금속-함유 재료로 구조체들을 충진하기 위한 방법들에 관한 것이고, 방법은 금속-함유 재료로 충진될 구조체를 제공하는 단계, 구조체를 복수의 증착 사이클들에 노출하는 단계를 포함하고, 증착 사이클 각각은 하나 이상의 교번하는 환원제 (예를 들어 수소 (H2)) 도즈 / 불활성 가스 퍼지 펄스들로의 노출에 이어서 하나 이상의 교번하는 금속 전구체 도즈 펄스들 및 불활성 가스 퍼지 펄스들로의 노출을 포함한다. 금속은 일부 실시예들에서 텅스텐 (W) 또는 몰리브덴 (Mo) 일 수도 있다.

일부 실시예들에서, 구조체는 측벽들 및 개구부들을 통해 유체적으로 액세스가능한 복수의 내부 영역들을 갖는 복수의 피처들로 이어지는 측벽들의 복수의 개구부들을 포함하는 부분적으로 제조된 3차원 (3-D) NAND 구조체이다. 일부 실시예들에서, 금속 전구체는 텅스텐 헥사클로라이드, 텅스텐 펜타클로라이드, 텅스텐 테트라클로라이드, 몰리브덴 펜타클로라이드, 몰리브덴 디클로라이드 다이옥사이드, 및 몰리브덴 테트라클로라이드 옥사이드, 및 이들의 혼합물들과 같은 염소-함유 금속 전구체이다. 일부 실시예들에서, 염소-함유 금속 전구체의 펄스는 체적으로 약 0.1 % 내지 약 5.0 %의 염소-함유 텅스텐 전구체를 포함한다. 일부 실시예들에서, 복수의 교번하는 금속 전구체 펄스들 및 불활성 가스 퍼지 펄스들로의 노출은 금속 전구체 펄스들 동안 불활성 가스 퍼지 플로우를 턴오프하는 것을 포함한다. 일부 실시예들에서, 불활성 가스 퍼지 펄스의 지속기간은 금속 전구체 펄스들의 적어도 1.5 배이다. 일부 실시예들에서, 증착 사이클 각각은 적어도 5 또는 적어도 10 개의 교번하는 금속 전구체 펄스들 및 불활성 가스 퍼지 펄스들을 포함한다. 일부 실시예들에서, 증착 사이클 각각은 일 H2 펄스만을 포함한다. 다른 실시예들에서, 증착 사이클 각각은 복수의 교번하는 H2 및 불활성 가스 펄스들을 포함한다.

본 개시의 또 다른 양태는 금속-함유 재료로 구조체들을 충진하기 위한 방법들에 관한 것이고, 방법은 금속-함유 재료로 충진될 구조체를 제공하는 단계, 구조체를 복수의 증착 사이클들에 노출하는 단계를 포함하고, 증착 사이클 각각은 환원제 (예를 들어 수소 (H2)) 도즈 펄스로의 노출에 이어서 불활성 가스 펄스로의 노출 및 복수의 교번하는 금속 전구체 도즈 펄스들 및 불활성 가스 퍼지 펄스들로의 노출을 포함한다. 일부 실시예들에서, 구조체는 측벽들 및 개구부들을 통해 유체적으로 액세스가능한 복수의 내부 영역들을 갖는 복수의 피처들로 이어지는 측벽들의 복수의 개구부들을 포함하는 부분적으로 제조된 3차원 (3-D) NAND 구조체이다. 일부 실시예들에서, 금속 전구체는 텅스텐 헥사클로라이드, 텅스텐 펜타클로라이드, 텅스텐 테트라클로라이드, 몰리브덴 펜타클로라이드, 몰리브덴 디클로라이드 다이옥사이드, 및 몰리브덴 테트라클로라이드 옥사이드, 및 이들의 혼합물들과 같은 염소-함유 금속 전구체이다. 일부 실시예들에서, 염소-함유 금속 전구체의 펄스는 체적으로 약 0.1 % 내지 약 5.0 %의 염소-함유 텅스텐 전구체를 포함한다. 일부 실시예들에서, 복수의 교번하는 금속 전구체 펄스들 및 불활성 가스 퍼지 펄스들로의 노출은 금속 전구체 펄스들 동안 불활성 가스 퍼지 플로우를 턴오프하는 것을 포함한다. 일부 실시예들에서, 불활성 가스 퍼지 펄스의 지속기간은 금속 전구체 펄스들의 적어도 1.5 배이다. 일부 실시예들에서, 증착 사이클 각각은 적어도 5 또는 적어도 10 개의 교번하는 금속 전구체 펄스들 및 불활성 가스 퍼지 펄스들을 포함한다.

본 개시의 또 다른 양태는 각각 기판을 홀딩하도록 구성된 하나 이상의 프로세스 챔버들; 환원제 (예를 들어, 수소 (H2)) 가스 소스, 금속 전구체 가스 소스, 및 불활성 퍼지 가스 소스에 커플링하기 위한 하나 이상의 프로세스 가스 유입구들; 및 복수의 증착 사이클들을 수행하기 위한 머신-판독가능 인스트럭션들을 포함하는 장치의 동작들을 제어하기 위한 제어기를 포함하고, 증착 사이클 각각은 하나 이상의 프로세스 가스 유입구들을 통해 하나 이상의 프로세스 챔버들에 수소 (H2) 펄스를 주입하는 단계; H2 펄스 주입 후, 하나 이상의 프로세스 가스 유입구들을 통해 불활성 퍼지 가스 펄스를 하나 이상의 프로세스 챔버로 주입하는 단계; 불활성 퍼지 가스 펄스 주입 후, 하나 이상의 퍼지 가스 유입구들을 통해 복수의 교번하는 금속 전구체 펄스들 및 불활성 가스 퍼지 펄스들을 하나 이상의 프로세스 챔버들로 주입하는 단계를 포함하는, 장치에 관한 것이다. 일부 실시예들에서, 금속 전구체는 염소-함유 금속 전구체이다. 일부 실시예들에서, 인스트럭션들은 금속 전구체 펄스들 동안 불활성 가스 퍼지 플로우를 턴 오프하기 위한 인스트럭션들을 포함한다. 일부 실시예들에서, 불활성 가스 퍼지 펄스의 지속기간은 금속 전구체 펄스들의 적어도 1.5 배이다. 일부 실시예들에서, 증착 사이클 각각은 적어도 5 개의 교번하는 금속 전구체 펄스들 및 불활성 가스 퍼지 펄스들을 포함한다. 일부 실시예들에서, 증착 사이클 각각은 적어도 10 개의 교번하는 금속 전구체 펄스들 및 불활성 가스 퍼지 펄스들을 포함한다.

본 개시의 또 다른 양태는 금속-함유 재료로 구조체들을 충진하기 위한 방법들에 관한 것이고, 방법은 금속-함유 재료로 충진될 구조체를 제공하는 단계, 구조체를 복수의 증착 사이클들에 노출하는 단계를 포함하고, 증착 사이클 각각은 복수의 교번하는 수소 (H2) 펄스들 및 불활성 가스 펄스로의 노출에 이어서 그리고 금속 전구체 펄스에 이어서 불활성 가스 퍼지 펄스로의 노출을 포함한다. 일부 실시예들에서, 구조체는 측벽들 및 개구부들을 통해 유체적으로 액세스가능한 복수의 내부 영역들을 갖는 복수의 피처들로 이어지는 측벽들의 복수의 개구부들을 포함하는 부분적으로 제조된 3차원 (3-D) NAND 구조체이다. 일부 실시예들에서, 금속 전구체는 염소-함유 금속 전구체이다. 일부 실시예들에서, 염소-함유 금속 전구체의 펄스는 체적으로 약 0.1 % 내지 약 5.0 %의 염소-함유 텅스텐 전구체를 포함한다. 일부 실시예들에서, 복수의 교번하는 H2 펄스들 및 불활성 가스 퍼지 펄스들로의 노출은 금속 전구체 펄스들 동안 불활성 가스 퍼지 플로우를 턴오프하는 것을 포함한다. 일부 실시예들에서, 증착 사이클 각각은 일 금속 전구체 펄스만을 포함한다. 다른 실시예들에서, 증착 사이클 각각은 복수의 교번하는 금속 전구체 및 불활성 가스 펄스들을 포함한다.

본 개시의 또 다른 양태는 각각 기판을 홀딩하도록 구성된 하나 이상의 프로세스 챔버들; 수소 (H2) 가스 소스, 금속 전구체 가스 소스, 및 불활성 퍼지 가스 소스에 커플링하기 위한 하나 이상의 프로세스 가스 유입구들; 및 복수의 증착 사이클들을 수행하기 위한 머신-판독가능 인스트럭션들을 포함하는 장치의 동작들을 제어하기 위한 제어기를 포함하고, 증착 사이클 각각은 하나 이상의 프로세스 가스 유입구들을 통해 하나 이상의 프로세스 챔버들에 복수의 교번하는 H2 펄스들 및 불활성 가스 퍼지 펄스들을 주입하는 단계; 및 금속 전구체 펄스에 이어서 불활성 가스 펄스를 주입하는 단계를 포함하는, 장치에 관한 것이다. 일부 실시예들에서, 금속 전구체는 염소-함유 금속 전구체이다. 일부 실시예들에서, 인스트럭션들은 H2 펄스들 동안 불활성 가스 퍼지 플로우를 턴 오프하기 위한 인스트럭션들을 포함한다.

이들 및 다른 양태들은 도면들을 참조하여 이하에 더 기술된다.

도 1a는 기판 상의 예시적인 막들의 개략적인 예시이다.

도 1b 내지 도 1j는 특정한 개시된 실시예들에 따른, 텅스텐 또는 몰리브덴이 증착될 수도 있는 다양한 구조체들의 개략적인 예들이다.

도 2a 내지 도 2c는 특정한 개시된 실시예들에 따른, 방법들에 대한 동작들을 도시하는 프로세스 흐름도이다.

도 3은 특정한 개시된 실시예들에 따른, 막들을 증착하기 위한 방법들의 예시적인 사이클들을 도시하는 타이밍 시퀀스도이다.

도 4a 내지 도 4j는 특정한 개시된 실시예들에 따른, 막들을 증착하기 위한 메커니즘의 일 예의 개략도들이다.

도 5는 H2/Ar/WClx/Ar 시퀀스 및 H2/Ar/n (WClx/Ar) 시퀀스를 사용하여 3-D NAND 구조체들의 텅스텐 충진을 비교하는 실험 결과들의 예시를 도시한다.

도 6은 특정한 개시된 실시예들을 수행하기 위한 예시적인 프로세스 툴의 개략도이다.

도 7은 특정한 개시된 실시예들을 수행하기 위한 예시적인 스테이션의 개략도이다.

도 8은 특정한 실시예들에 따라 사용될 수도 있는 매니폴드 시스템의 기본 피처들을 도시하는 개략도이다.

도 1b 내지 도 1j는 특정한 개시된 실시예들에 따른, 텅스텐 또는 몰리브덴이 증착될 수도 있는 다양한 구조체들의 개략적인 예들이다.

도 2a 내지 도 2c는 특정한 개시된 실시예들에 따른, 방법들에 대한 동작들을 도시하는 프로세스 흐름도이다.

도 3은 특정한 개시된 실시예들에 따른, 막들을 증착하기 위한 방법들의 예시적인 사이클들을 도시하는 타이밍 시퀀스도이다.

도 4a 내지 도 4j는 특정한 개시된 실시예들에 따른, 막들을 증착하기 위한 메커니즘의 일 예의 개략도들이다.

도 5는 H2/Ar/WClx/Ar 시퀀스 및 H2/Ar/n (WClx/Ar) 시퀀스를 사용하여 3-D NAND 구조체들의 텅스텐 충진을 비교하는 실험 결과들의 예시를 도시한다.

도 6은 특정한 개시된 실시예들을 수행하기 위한 예시적인 프로세스 툴의 개략도이다.

도 7은 특정한 개시된 실시예들을 수행하기 위한 예시적인 스테이션의 개략도이다.

도 8은 특정한 실시예들에 따라 사용될 수도 있는 매니폴드 시스템의 기본 피처들을 도시하는 개략도이다.

이하의 기술 (description) 에서, 제시된 실시예들의 완전한 이해를 제공하기 위해 수많은 구체적 상세들이 제시되었다. 개시된 실시예들은 이들 구체적인 상세들 중 일부 또는 전부가 없이 실시될 수도 있다. 다른 예들에서, 공지된 프로세스 동작들은 개시된 실시예들을 불필요하게 모호하게 하지 않기 위해 상세히 기술되지 않았다. 개시된 실시예들이 구체적인 실시예들과 함께 기술될 것이지만, 이는 개시된 실시예들을 제한하는 것으로 의도되지 않았다는 것이 이해될 것이다.

피처들의 텅스텐 (W) 충진은 전기적 콘택트들을 형성하기 위해 반도체 디바이스 제조에 자주 사용된다. 텅스텐 막들을 증착하는 종래의 방법들에서, 핵생성 텅스텐 층이 비아 또는 콘택트 내로 먼저 증착된다. 일반적으로, 핵생성 층은 그 위에 벌크 재료의 후속 형성을 용이하게 하도록 역할하는 박형의 컨포멀한 (conformal) 층이다. 텅스텐 핵생성 층은 피처의 측벽들 및 하단부를 컨포멀하게 코팅하도록 증착될 수도 있다. 아래에 놓인 피처 하단부 및 측벽들에 컨폼하는 (conform) 것은 고 품질 증착을 지지하는데 중요할 수 있다. 핵생성 층들은 종종 원자 층 증착 (atomic layer deposition; ALD) 또는 펄싱된 핵생성 층 (pulsed nucleation layer; PNL) 방법들을 사용하여 증착된다.

PNL 기법에서, 반응물질의 펄스들은 반응물질들 사이에 퍼지 가스의 펄스에 의해 반응 챔버로부터 순차적으로 주입되고 퍼지된다. 제 1 반응물질이 기판 상에 흡착될 수 있어, 다음 반응물질과 반응하는데 이용가능하다. 프로세스는 목표된 두께가 달성될 때까지 순환적 방식으로 반복된다. PNL 기법들은 ALD 기법들과 유사하다. PNL은 일반적으로 (1 Torr보다 큰) 보다 높은 동작 압력 범위 및 (사이클 당 1보다 큰 모노레이어 막 성장) 사이클 당 보다 높은 성장 레이트에 의해 ALD로부터 구별된다. PNL 증착 동안 챔버 압력은 약 1 Torr 내지 약 400 Torr의 범위일 수도 있다. 본 명세서에 제공된 기술 (description) 의 맥락에서, PNL은 반도체 기판 상의 반응을 위해 순차적으로 반응물질들을 부가하는 임의의 순환적 프로세스를 광범위하게 구현한다. 따라서, 이 개념은 종래에 ALD로 지칭된 기법들을 구현한다. 개시된 실시예들의 맥락에서, 화학적 기상 증착 (chemical vapor deposition; CVD) 은 반응물질들이 함께 증기-상 또는 표면 반응을 위해 반응기로 도입되는, 프로세스들을 구현한다. PNL 프로세스 및 ALD 프로세스는 CVD 프로세스들과 구별되고 그 반대도 된다.

텅스텐 핵생성 층이 증착된 후, 벌크 텅스텐은 통상적으로 수소 (H2) 와 같은 환원제를 사용하여 텅스텐 헥사플루오라이드 (WF6) 를 환원함으로써 CVD 프로세스에 의해 증착된다. 벌크 텅스텐은 텅스텐 핵생성 층과 상이하다. 본 명세서에서 사용된 바와 같은 벌크 텅스텐은 피처의 적어도 약 50 %와 같은 피처의 대부분 또는 전부를 충진하도록 사용된 텅스텐을 지칭한다. 그 위에 벌크 재료의 후속 형성을 용이하게 하도록 역할하는 박형의 컨포멀한 막인 핵생성 층과 달리, 벌크 텅스텐은 전류를 반송하도록 사용된다. 이는 핵생성 막과 비교하여 보다 큰 입자 크기 및 보다 낮은 저항률로 특징화될 수도 있다. 다양한 실시예들에서, 벌크 텅스텐은 적어도 50 Å의 두께로 증착된 텅스텐이다.

디바이스들이 보다 작은 기술 노드들로 스케일링되고 보다 복잡한 패터닝 구조체들이 사용되기 때문에, 텅스텐 충진에서 다양한 문제들이 있다. 종래의 텅스텐의 증착은 불소-함유 전구체 텅스텐 헥사플루오라이드 (WF6) 의 사용을 수반하였다. 그러나, WF6의 사용은 증착된 텅스텐 막 내로 불소의 어느 정도 통합을 발생시킨다. 불소의 존재는 인접한 컴포넌트들 내로 전자마이그레이션 (electromigration) 및/또는 불소 확산을 유발할 수 있고 콘택트들을 손상시킬 수 있어서, 디바이스의 성능을 저하시킨다. 일 과제는 증착된 텅스텐 막에서 불소 함량이 감소하는 것이다. 피처 사이즈가 감소됨에 따라 특정한 불소 농도의 효과는 상승한다. 이는 보다 박형의 막들이 보다 박형의 막들을 통해 확산하기 보다 쉬운 증착된 텅스텐 막의 불소와 함께 보다 작은 피처들 내에 증착되기 때문이다.

불소 확산을 방지하는 일 방법은 텅스텐으로부터 옥사이드 층과 같은 기판의 다른 층들로 불소가 확산하는 것을 방지하도록 텅스텐을 증착하기 전 하나 이상의 배리어 층들을 증착하는 단계를 포함한다. 예를 들어, 도 1a는 기판 상에 증착된 층들의 예시적인 스택을 도시한다. 기판 (190) 은 실리콘 층 (192), 옥사이드 층 (194) (예를 들어, 티타늄 옥사이드 (TiOx), 테트라에틸 오소실리케이트 (TEOS) 옥사이드, 등), 배리어 층 (196) (예를 들어, 티타늄 나이트라이드 (TiN)), 텅스텐 핵생성 층 (198), 및 벌크 텅스텐 층 (199) 을 포함한다. 배리어 층 (196) 은 벌크 텅스텐 층 (199) 및 텅스텐 핵생성 층 (198) 으로부터 옥사이드 층으로 불소 확산을 방지하도록 증착된다. 그러나, 디바이스들이 축소됨에 따라, 배리어 층들은 보다 박형이 되고, 불소는 여전히 증착된 텅스텐 층들로부터 확산할 수도 있다. 보다 고온에서 수행된 벌크 텅스텐의 화학적 기상 증착이 보다 낮은 불소 함량을 발생시키지만, 이러한 막들은 불량한 단차 커버리지 (step coverage) 를 가질 수도 있다.

또 다른 과제는 증착된 막들 상의 응력이 감소하는 것이다. 보다 박형의 텅스텐 막들은 상승된 인장 응력을 갖는 경향이 있다. CVD에 의해 벌크 텅스텐 막들을 증착하기 위한 종래의 기법들은 200 Å 막에 대해 2.5 GPa보다 큰 인장 응력을 갖는다. 고 열적 인장 응력은 기판으로 하여금 말리게 (curl) 하고, 이는 후속 프로세싱을 어렵게 한다. 예를 들어, 후속 프로세스들은 챔버에서 프로세스들을 수행하기 위해 화학적 기계적 평탄화, 재료들의 증착, 및/또는 기판 홀더로 기판의 클램핑을 포함할 수도 있다. 그러나, 이들 프로세스들은 종종 편평한 기판에 의존하고, 말린 기판은 불균일한 프로세싱 또는 기판 프로세싱 불능을 발생시킨다. 어닐링과 같이 다른 재료들의 막들의 응력을 감소시키기 위한 기존 방법들이 있지만, 텅스텐은 고 융점으로 인해 한번 증착되면 입자들로 하여금 이동되거나 변경되게 하는 표면 이동성을 갖지 않는다.

불소-프리 텅스텐 (FFW) 전구체들이 이러한 신뢰성 및 통합 문제들 또는 디바이스 성능 문제들을 방지하는데 유용하다. 현재 FFW 전구체들은 금속 유기 전구체들을 포함하지만, 금속 유기 전구체들로부터 탄소, 수소, 질소, 및 산소와 같은 원소들의 바람직하지 않은 추적들이 텅스텐 막에도 통합될 수도 있다. 일부 금속 유기 불소-프리 전구체들은 또한 텅스텐 증착 프로세스들로 용이하게 구현 또는 통합되지 않는다.

본 명세서에 기술된 일부 구현예들은 텅스텐 클로라이드 (WClx) 전구체를 사용한 텅스텐의 증착과 관련한다. 텅스텐 클로라이드는 텅스텐 펜타클로라이드 (WCl5), 텅스텐 헥사클로라이드 (WCl6), 텅스텐 테트라클로라이드 (WCl4), 텅스텐 디클로라이드 (WCl2), 및 이들의 혼합물들을 포함한다. 본 명세서의 예들이 예들로서 WCl5 및 WCl6를 참조하지만, 다른 텅스텐 클로라이드들이 개시된 실시예들과 함께 사용될 수도 있다는 것이 이해된다. 특정한 개시된 실시예들을 사용하여 증착된 막들은 불소-프리이다. 특정한 개시된 실시예들은 염소-함유 텅스텐 전구체 및 수소의 교번하는 펄스들을 사용하여 벌크 텅스텐을 증착하는 것으로 지향된다.

WCl5 및 WCl6에 의한 증착은 텅스텐 클로라이드들에 의해 가능한 에칭으로 인해 WF6와 함께 존재하지 않는 과제들을 제공한다. 텅스텐 클로라이드들은 보다 적은 반응성이고, 그 결과, 증착은 WF6를 사용한 증착보다 높은 온도에서 수행된다. 증발된 WCl6는 텅스텐 증착 챔버 내로 반송하는 것을 인에이블하도록 충분히 높은 증기압을 갖는다. 그러나, WCl6 는 WCl5보다 기판을 에칭할 가능성이 높을 수도 있다. WCl5가 기판을 에칭할 가능성이 보다 낮지만, WCl5는 또한 WCl6보다 높은 증기압을 갖는다. 보다 낮은 증기압이 저 저항률을 갖는 텅스텐 막들을 증착하는데 유용하지만, 일부 증착 동작들은 불량한 단차 커버리지를 가질 수도 있다.

본 명세서에 기술된 방법들은 몰리브덴 클로라이드 또는 몰리브덴 옥시클로라이드 전구체들에 의한 몰리브덴 (Mo) 의 증착을 위해 또한 사용될 수도 있다. 몰리브덴은 저 저항 금속화 스택 구조체들을 형성하도록 사용될 수도 있고 텅스텐의 자리를 취할 수도 있다.

개시된 실시예들은 광범위한 다양한 적용예들을 갖는다. 방법들은 고 단차 커버리지를 갖는 피처들 내로 텅스텐 또는 몰리브덴을 증착하도록 사용될 수도 있고, 3D NAND 구조체들 내로 텅스텐을 증착하도록 또한 사용될 수도 있다.

본 명세서에 기술된 방법들은 챔버에 하우징될 수도 있는 기판 상에서 수행된다. 기판은 유전체, 도전 또는 반도전 재료와 같은 재료의 하나 이상의 층들이 그 위에 증착된 웨이퍼들을 포함하는, 실리콘 또는 다른 반도체 웨이퍼, 예를 들어, 200-㎜ 웨이퍼, 300-㎜ 웨이퍼, 또는 450-㎜ 웨이퍼일 수도 있다. 방법들은 반도체 기판들로 제한되지 않고, 텅스텐과 같은 금속으로 임의의 피처를 충진하도록 수행될 수도 있다.

기판들은 좁은 그리고/또는 재차 들어간 (re-entrant) 개구부들, 피처 내 협폭부들 (constrictions), 및 고 종횡비들 중 하나 이상을 특징으로 할 수도 있는, 비아 또는 콘택트 홀들과 같은 피처들을 가질 수도 있다. 피처가 상기 기술된 층들 중 하나 이상에 형성될 수도 있다. 예를 들어, 피처는 유전체 층에 적어도 부분적으로 형성될 수도 있다. 일부 실시예들에서, 피처는 적어도 약 2:1, 적어도 약 4:1, 적어도 약 6:1, 적어도 약 10:1, 적어도 약 25:1, 이상의 종횡비를 가질 수도 있다. 피처의 일 예는 반도체 기판 또는 기판 상의 층 내의 홀 또는 비아이다.

도 1b 내지 도 1h는 개시된 실시예들에 따른, 금속이 증착될 수도 있는 다양한 구조체들의 개략적인 예들이다. 도 1b는 텅스텐 또는 몰리브덴과 같은 금속으로 충진될 수직 피처 (101) 의 단면도의 일 예를 도시한다. 피처는 기판 (103) 내에 피처 홀 (105) 을 포함할 수 있다. 홀 (105) 또는 다른 피처는 개구부 근방 치수, 예를 들어, 약 10 ㎚ 내지 500 ㎚, 예를 들어 약 25 ㎚ 내지 약 300 ㎚의 개구부 직경 또는 라인 폭을 가질 수도 있다. 피처 홀 (105) 은 충진되지 않은 피처 또는 단순히 피처로 지칭될 수 있다. 피처 (101), 및 임의의 피처가 수직 축들을 갖는 수직으로 배향된 피처들 및 수평 축들을 갖는 수평으로 배향된 피처들을 갖는 피처의 길이를 통해 연장하는 축 (118) 에 의해 부분적으로 특징화될 수도 있다.

일부 실시예들에서, 피처들은 3D NAND 구조체의 워드라인 피처들이다. 예를 들어, 기판이 적어도 200 Å 깊이의 수직 채널들을 갖는 임의의 수의 워드라인들 (예를 들어, 50 내지 150) 을 갖는 워드라인 구조체를 포함할 수도 있다. 또 다른 예는 기판 또는 층의 트렌치이다. 피처들은 임의의 깊이일 수도 있다. 다양한 실시예들에서, 피처는 배리어 층 또는 접착 층과 같은, 하부 층을 가질 수도 있다. 하부 층들의 비제한적인 예들은 유전체 층들 및 도전 층들, 예를 들어, 실리콘 옥사이드들, 실리콘 나이트라이드들, 실리콘 카바이드들, 금속 옥사이드들, 금속 나이트라이드들, 금속 카바이드들, 및 금속 층들을 포함한다.

도 1c는 재차 들어간 프로파일을 갖는 피처 (101) 의 일 예를 도시한다. 재차 들어간 프로파일은 피처의 하단부, 폐쇄된 단부, 또는 내부로부터 피처 개구부로 좁아지는 프로파일이다. 다양한 구현예들에 따라, 프로파일은 점진적으로 좁아질 수도 있고 그리고/또는 피처 개구부에서 오버행 (overhang) 을 포함할 수도 있다. 도 1c는 피처 홀 (105) 의 측벽 또는 내부 표면들을 라이닝하는 하부 층 (113) 을 갖는, 후자의 예를 도시한다. 하부 층 (113) 은 예를 들어, 확산 배리어 층, 접착 층, 핵생성 층, 이의 조합, 또는 임의의 다른 적용가능한 재료일 수 있다. 하부 층들의 비제한적인 예들은 유전체 층들 및 도전 층들, 예를 들어, 실리콘 옥사이드들, 실리콘 나이트라이드들, 실리콘 카바이드들, 금속 옥사이드들, 금속 나이트라이드들, 금속 카바이드들, 및 금속 층들을 포함할 수 있다. 특정한 구현예들에서 하부 층은 티타늄, 티타늄 나이트라이드, 텅스텐 나이트라이드, 티타늄 알루미나이드, 텅스텐, 및 몰리브덴 중 하나 이상일 수 있다. 일부 실시예들에서, 하부 층은 텅스텐-프리이다. 일부 실시예들에서, 하부 층은 몰리브덴-프리이다. 하부 층 (113) 은 하부 층 (113) 이 피처 (101) 내부보다 피처 (101) 의 개구부에서 보다 두껍도록 오버행 (115) 을 형성한다.

일부 구현예들에서, 피처 내부에 하나 이상의 협폭부들을 갖는 피처들이 충진될 수도 있다. 도 1d는 협폭부들을 갖는 다양한 충진된 피처들의 도면들의 예들을 도시한다. 도 1d의 예들 (a), (b) 및 (c) 각각은 피처 내 중간지점에 협폭부들 (109) 을 포함한다. 협폭부들 (109) 은 예를 들어, 약 15 ㎚ 내지 20 ㎚ 넓이일 수 있다. 협폭부들은 종래의 기법들을 사용하여 피처 내 텅스텐 또는 몰리브덴의 증착 동안 핀치 오프 (pinch off) 를 유발할 수 있고, 추가 증착을 차단하는 증착된 금속이 피처의 일부가 충진되기 전 협폭부를 넘어가 (past), 피처 내 보이드들을 발생시킨다. 예 (b) 는 피처 개구부에서 라이너/배리어 오버행 (115) 을 더 포함한다. 이러한 오버행은 잠재적인 핀치 오프 지점일 수 있다. 예 (c) 는 예 (b) 의 오버행 (115) 보다 필드 영역으로부터 더 먼 협폭부 (112) 를 포함한다.

3-D 메모리 구조체들 내와 같이, 수평 피처들이 또한 충진될 수 있다. 도 1e는 협폭부 (151) 를 포함하는 수평 피처 (150) 의 일 예를 도시한다. 예를 들어, 수평 피처 (150) 는 3D NAND 구조체의 워드라인일 수도 있다. 일부 구현예들에서, 협폭부들은 3D NAND 또는 다른 구조체의 필라들 (pillars) 의 존재로 인한 것일 수 있다. 예를 들어, 도 1f는 VNAND 스택들 (좌측 (125) 및 우측 (126)), 중앙 수직 구조체 (130), 및 중앙 수직 구조체 (130) 의 마주보는 측벽들 (140) 상의 개구부들 (122) 을 갖는 복수의 스택된 수평 피처들 (120) 을 갖는 3-D NAND (또한 수직 NAND 또는 VNAND로 지칭됨) 구조체 (110) (반도체 기판 (103) 상에 형성된) 의 측단면도를 제공한다. 도 1f는 함께 "트렌치-유사 (trench-like)" 중앙 수직 구조체 (130) 를 형성하는 표현된 3-D NAND 구조체 (110) 의 2 개의 "스택들"을 디스플레이하지만, 특정한 실시예들에서, 차례로 배치되고 서로 공간적으로 평행하게 진행하는 3 개 이상의 "스택들"이, 도 1f에 명시적으로 예시된 것과 같은, 중앙 수직 구조체 (130) 를 형성하는 인접한 "스택들"의 쌍 각각 사이의 갭이 있을 수도 있다는 것을 주의하라. 이 실시예에서, 수평 피처들 (120) 은 개구부들 (122) 을 통해 중앙 수직 구조체 (130) 로부터 유체적으로 액세스가능한 3-D 메모리 워드라인 피처들이다. 도면에 명시적으로 나타나지 않지만, 도 1f에 도시된 3-D NAND 스택들 (125 및 126) 모두 (즉, 좌측 3-D NAND 스택 (125) 및 우측 3-D NAND 스택 (126)) 에 존재하는 수평 피처들 (120) 은 또한 스택들 (각각 극좌측 및 극우측) 의 다른 측면들로부터 부가적인 3-D NAND 스택들 (극좌측 및 극우측으로, 미도시) 에 의해 형성된 유사한 수직 구조체들을 통해 액세스가능하다. 달리 말하면, 3-D NAND 스택 (125, 126) 각각은 중앙 수직 구조체 (130) 를 통해 3-D NAND 스택의 양 측면들로부터 유체적으로 액세스가능한 워드라인 피처들의 스택을 포함한다. 도 1f에 개략적으로 예시된 특정한 예에서, 3-D NAND 스택 각각은 6 쌍의 스택된 워드라인들을 포함하지만, 다른 실시예들에서, 3-D NAND 메모리 레이아웃은 임의의 수의 수직으로 스택된 쌍들의 워드라인들을 포함할 수도 있다.

3-D NAND 스택의 워드라인 피처들은 통상적으로 실리콘 옥사이드 층 및 실리콘 나이트라이드 층의 교번하는 스택을 증착하고, 이어서 사이에 갭들을 갖는 옥사이드들 층들의 스택을 남기면서 나이트라이드 층들을 선택적으로 제거함으로써 형성된다. 이들 갭들은 워드라인 피처들이다. 임의의 수의 워드라인들이 이들을 형성하는데 이용가능한 기법, 뿐만 아니라 수직 피처들의 (실질적으로) 보이드-프리 충진들을 성공적으로 달성하도록 이용가능한 기법이 있는 한, 이러한 3-D NAND 구조체에 수직으로 스택될 수도 있다. 따라서, 예를 들어, VNAND 스택이 2 내지 256 개의 수평 워드라인 피처들, 또는 8 내지 128 개의 수평 워드라인 피처들, 또는 16 내지 64 개의 수평 워드라인 피처들, 등을 포함할 수도 있다 (열거된 범위들은 언급된 엔드포인트들을 포함하는 것으로 이해됨).

도 1g는 도 1f의 측면에 도시된 동일한 3-D NAND 구조체 (110) 의 단면 톱-다운 (top-down) 도를 도 1f의 점선 수평 라인으로 나타낸 바와 같은 수평 섹션 (160) 을 통해 취해진 단면과 함께 제공한다. 도 1g의 단면도는 반도체 기판 (103) 의 베이스 (base) 로부터 3-D NAND 스택 (110) 의 상단부로 수직으로 진행하는 것으로 도 1f에 도시된 몇몇 행들의 필라들 (155) 을 예시한다. 일부 실시예들에서, 이들 필라들 (155) 은 폴리실리콘 재료로부터 형성되고 3-D NAND 구조체 (110) 에 구조적으로 그리고 기능적으로 중요하다. 일부 실시예들에서, 이러한 폴리실리콘 필라들이 필라들 내에 형성된 스택된 메모리 셀들에 대해 게이트 전극들로서 역할을 할 수도 있다. 도 1g의 상면도는 필라들 (155) 이 워드라인 피처들 (120) 로 개구부들 (122) 내에 협폭부들을 형성한다는 것을 예시한다 - 즉 중앙 수직 구조체 (130) 로부터 개구부들 (122) (도 1g의 화살표들로 나타낸 바와 같이) 을 통한 워드라인 피처들 (120) 의 유체 액세스가능성이 필라들 (155) 에 의해 억제된다. 일부 실시예들에서, 인접한 폴리실리콘 필라들 사이의 수평 갭의 사이즈는 약 1 내지 20 ㎚이다. 이 유체 액세스가능성의 감소는 텅스텐 재료로 워드라인 피처들 (120) 을 균일하게 충진하는 것의 어려움을 증가시킨다. 워드라인 피처들 (1) 의 구조체 및 필라들 (155) 의 존재로 인한 텅스텐 재료 또는 몰리브덴 재료로 이들을 균일하게 충진하는 것의 어려움은 도 1h, 도 1i 및 도 1j에 더 예시된다.

도 1h는 도 1f에 도시된 것과 유사하지만, 이 도면에서는 단일 쌍의 워드라인 피처들 (120) 에 포커싱하고, 부가적으로 충진된 워드라인 피처들 (120) 의 보이드 (175) 의 형성을 발생시키는, 금속 충진 프로세스를 개략적으로 예시하는, 수직으로 절단된 (cut through) 3-D NAND 구조체를 나타낸다. 도 1i는 또한 보이드 (175) 를 개략적으로 예시하지만, 이 도면에서 도 1g에 나타낸 수평 절단도와 유사한, 수평 절단 필라들 (155) 을 통해 예시된다. 도 1j는 협폭부 형성 필라들 (155) 주변에 텅스텐 또는 몰리브덴 재료의 축적을 예시하고, 축적은 부가적인 텅스텐 또는 몰리브덴 재료가 보이드들 (175) 의 영역 내에 증착될 수 없도록 개구부들 (122) 의 핀치 오프를 발생시킨다. 보이드-프리 텅스텐 또는 몰리브덴 충진이 개구부들 (122) 의 핀치 오프를 유발하고 워드라인 피처들 (120) 내로 추가 전구체 마이그레이션을 방지하는, 필라들 (155) 주변 텅스텐의 축적된 증착 전에, 수직 구조체 (130) 를 통해, 개구부들 (122) 을 통해, 협폭 필라들 (155) 을 넘어, 워드라인 피처들 (120) 의 가장 먼 범위까지 아래로 충분한 양의 증착 전구체의 마이그레이션에 의존한다는 것이 도 1h 및 도 1i로부터 자명하다. 유사하게, 도 1j는 위에서 단면으로 본 단일 워드라인 피처 (120) 를 나타내고, 상당한 폭의 필라들 (155) 이 그렇지 않으면 워드라인 피처 (120) 를 통한 개방 경로일 수 있는 워드라인 피처 (120) 를 부분적으로 차단, 그리고/또는 좁히고 (narrow), 그리고/또는 협폭화하도록 작용한다는 사실로 인해, 대체로 컨포멀한 텅스텐 또는 몰리브덴 재료의 증착이 워드라인 피처 (120) 의 내부를 핀치 오프하기 시작하는 지 예시한다. (도 1j의 예는 도 1i에 도시된 필라 협폭부들의 구조체의 3-D 피처들의 2-D 렌더링으로 이해될 수 있어서, 단면도가 아니라 평면도에서 볼 수 있는 협폭부들을 예시한다는 것이 이해되어야 한다.)

3D 구조체들이 최내측 영역 및 최하측 영역으로 하여금 충진되게 하도록 전구체들로 보다 길고 그리고/또는 보다 집중된 노출을 필요로 할 수도 있다. 3D 구조체들은 WClx 전구체들을 채용할 때 구조체의 부분들로서 보다 많은 에칭을 허용하는 보다 길고 보다 집중된 노출과 함께, 이들의 에칭 성향으로 인해, 특히 어려울 수 있다. 이들 과제들은 또한 몰리브덴 클로라이드 전구체들을 사용해도 존재할 수도 있다.

수평으로 배향된 및 수직으로 배향된 피처들에 대한 피처 충진의 예들은 이하에 기술된다. 대부분의 경우, 이 예들은 수평으로 배향된 또는 수직으로 배향된 피처들 모두에 적용가능하다는 것을 주의해야 한다. 게다가, 이하의 기술에서, 용어 "측방향 (lateral)"은 피처 축에 일반적으로 직교하는 방향을 지칭하고 용어 "수직 (vertical)"은 일반적으로 피처 축을 따른 방향을 지칭하도록 사용될 수도 있다는 것을 또한 주의해야 한다.

다양한 실시예들에 따라, 이하에 기술된 방법들은 ALD 사이클의 복수의 환원제/퍼지 사이클들 및/또는 복수의 금속-전구체/퍼지 사이클들에 구조체를 노출하는 것을 수반한다. 일부 구현예들에서, 다음의 장점들 중 하나 이상이 달성될 수도 있다. 일부 실시예들에서, 퍼지 가스 펄싱과 함께 배치된 복수의 텅스텐-함유 전구체 도즈들 (예를 들어, W/Ar/W/Ar/W/Ar/W/Ar, W는 텅스텐-함유 전구체의 펄스이고 Ar은 아르곤 퍼지 가스의 펄스를 나타냄) 은 3-D NAND 워드라인 구조체 내로 깊이 텅스텐-함유 전구체의 전달을 인에이블하거나 구조체로 충진하는 것을 어렵게 한다. 일부 구현예들에서, 다음의 장점들 중 하나 이상이 달성될 수도 있다. 일부 실시예들에서, 퍼지 가스 펄싱과 함께 배치된 복수의 몰리브덴-함유 전구체 도즈들 (예를 들어, Mo/Ar/Mo/Ar/Mo/Ar/Mo/Ar, Mo는 몰리브덴-함유 전구체의 펄스이고 Ar은 아르곤 퍼지 가스의 펄스를 나타냄) 은 3-D NAND 워드라인 구조체 내로 깊이 몰리브덴-함유 전구체의 전달을 인에이블하거나 구조체로 충진하는 것을 어렵게한다.

금속-함유 펄스 각각 후 불활성 가스 퍼지 펄스는 금속-함유 전구체의 모노레이어가 구조체 전반에 흡착된다는 것을 보장할 수 있다. 일부 실시예들에서, 각각 퍼지 가스가 이어지는, 복수의 펄스들은 금속-함유 전구체의 복수의 모노레이어들이 보다 액세스가능한 구조체의 부분들에서 축적 (build up) 되지 않는다는 것을 보장한다. 이는 구조체의 원치 않은 에칭을 방지할 수 있다. 일부 실시예들에서, 교번하는 펄스들을 갖는 것은 펄스 각각 전에 금속 전구체 저장부의 가압을 인에이블한다. 이는 피처의 하단부로의 플럭스를 보조할 수 있다. 일부 실시예들에서, 퍼지 가스 펄스들 펄싱과 함께 배치된 복수의 환원제 도즈들 (예를 들어, H2/Ar/H2/Ar/W/Ar/W/Ar, 여기서 H2는 환원제이고, W는 텅스텐-함유 전구체의 펄스 그리고 Ar은 아르곤 퍼지 가스의 펄스이고 또는 H2/Ar/H2/Ar/Mo/Ar/Mo/Ar 여기서 Mo는 몰리브덴-함유 전구체의 펄스를 나타냄) 은 흡착된 클로라이드들과 반응하도록 환원제에 충분한 시간을 제공하는 한편, 반응 생성물 (예를 들어, HCl) 로 하여금 표면을 떠나고 다음 펄스의 환원제를 위한 공간을 만들게 한다.

이하의 기술은 텅스텐 피처 충진 및 몰리브덴 피처 충진에 포커싱하지만, 본 개시의 양태들은 다른 재료들로 피처들을 충진시 또한 구현될 수도 있다. 예를 들어, 본 명세서에 기술된 하나 이상의 기법들을 사용한 피처 충진은 다른 텅스텐 함유 재료들 (예를 들어, 텅스텐 나이트라이드 (WN) 및 텅스텐 카바이드 (WC)), 티타늄 함유 재료들 (예를 들어, 티타늄 (Ti), 티타늄 나이트라이드 (TiN), 티타늄 실리사이드 (TiSi), 티타늄 카바이드 (TiC) 및 티타늄 알루미나이드 (TiAl)), 탄탈룸 함유 재료들 (예를 들어, 탄탈룸 (Ta), 및 탄탈룸 나이트라이드 (TaN)), 및 니켈 함유 재료들 (예를 들어, 니켈 (Ni) 및 니켈 실리사이드 (NiSi)) 을 포함하는 다른 재료들로 피처들을 충진하도록 사용될 수도 있다. 또한, 본 명세서에 개시된 방법들 및 장치는 피처 충진으로 제한되지 않고, 평면형 표면들 상에 블랭킷 (blanket) 막들을 형성하는 것을 포함하여 임의의 적절한 표면 상에 텅스텐을 증착하도록 사용될 수 있다.

도 2a 내지 도 2c는 개시된 실시예들에 따라 수행된 방법들에 대한 프로세스 흐름도들을 제공한다. 이하에 기술된 바와 같이, 방법은 텅스텐으로 기판 상의 구조체를 충진하도록 수행된다. 구조체들의 예들은 도 1b 내지 도 1h를 참조하여 상기 기술되었다.

온도는 채용된 화학물질에 따라 가변할 수도 있다. WClx 및 WOxCl4 전구체들에 대해, 특정한 개시된 실시예들은 약 400 ℃ 내지 약 600 ℃, 예컨대 약 525 ℃의 기판 온도에서 수행될 수도 있다. 기판 온도는 기판을 홀딩하는 페데스탈이 설정되는 온도를 지칭한다.

MoClx 및 MoOxCly 전구체들에 대해, 특정한 개시된 실시예들은 약 400 ℃ 내지 약 600 ℃, 예컨대 약 525 ℃의 기판 온도에서 수행될 수도 있다. 기판 온도는 기판을 홀딩하는 페데스탈이 설정되는 온도를 지칭한다.

특정한 개시된 실시예들은 약 3 Torr 내지 약 60 Torr의 챔버 압력에서 수행될 수도 있다. 일부 실시예들에서, WClx 전구체들을 사용한 텅스텐 증착을 위한 챔버 압력은 5 Torr 내지 20 Torr, 예를 들어, 10 Torr이다.

도 2a를 참조하면, 동작 200에서, 텅스텐 또는 몰리브덴으로 충진될 구조체가 환원제 펄스에 노출된다. 일부 실시예들에서, 환원제 펄스는 수소 (H2) 이다. 실란들, 보란들, 게르만들, 포스핀들, 수소-함유 가스들, 및 이들의 조합들을 포함하는, 다른 환원제들이 사용될 수도 있다. 다양한 실시예들에서, 벌크 텅스텐 증착 또는 벌크 몰리브덴 증착이 환원제로서 수소를 사용하여 수행된다. 환원제는 또 다른 반응물질을 흘리지 않고 펄싱된다. 일부 실시예들에서, 캐리어 가스가 흐를 수도 있다. 일부 실시예들에서, 캐리어 가스, 예컨대 질소 (N2), 아르곤 (Ar), 헬륨 (He), 또는 다른 불활성 가스들이 동작 200 동안 흐를 수도 있다.

동작 200은 임의의 적합한 지속기간 동안 수행될 수도 있다. 예시적인 지속기간들은 약 0.25 초 내지 약 30 초, 약 0.25 초 내지 약 20 초, 약 0.25 초 내지 약 5 초, 또는 약 0.5 초 내지 약 3 초를 포함한다.

동작 202에서, 챔버는 기판의 표면에 흡착되지 않은 과잉 수소를 제거하도록 퍼지된다. 퍼지가 고정된 압력으로 불활성 가스를 흘리고, 이에 따라 챔버의 압력을 감소시키고 또 다른 반응물질 가스 노출을 개시하기 전 챔버를 재-가압함으로써 수행될 수도 있다. 예시적인 불활성 가스들은 질소 (N2), 아르곤 (Ar), 헬륨 (He), 및 이들의 혼합물들을 포함한다. 퍼지는 약 0.25 초 내지 약 30 초, 약 0.25 초 내지 약 20 초, 약 0.25 초 내지 약 5 초, 또는 약 0.5 초 내지 약 3 초의 지속기간 동안 수행될 수도 있다.

동작 200 및 동작 202는 이어서k 회 수행될 때까지 반복되고, 여기서k는 적어도 21의 정수이다. 일 예에서, 동작 200은 0.5 초의 지속기간, 그리고 동작 202는 환원제 펄스들 사이에 1 초의 지속기간을 가질 수도 있다.k= 10에 대해, 1 × 10 = 10 초의 총 퍼지 시간과 함께, 총 텅스텐 전구체 시간은 0.5 × 10 = 5 초이다.

동작 204에서, 기판은 텅스텐 전구체에 또는 몰리브덴 전구체에 노출된다. 예시적인 전구체들은 텅스텐 클로라이드들 및 텅스텐 옥시클로라이드들과 같은 염소-함유 텅스텐 전구체들을 포함한다. 텅스텐 클로라이드들은 WClx일 수도 있고, 여기서 x는 2 이상 6 이하의 정수, 예컨대 2, 3, 4, 5, 또는 6이다. 예들은 WCl5 및 WCl6를 포함한다. 염소-함유 텅스텐 전구체는 WClx 화합물들의 혼합물을 포함할 수도 있다. 텅스텐 옥시클로라이드들은 WOxCly를 포함하고, x 및 y는 0보다 큰 수이다. 몰리브덴 클로라이드들 및 몰리브덴 옥시클로라이드들을 포함하는 몰리브덴 전구체들은 몰리브덴을 증착하도록 사용된다. 이들은 몰리브덴 펜타클로라이드 (MoCl5), 몰리브덴 디클로라이드 다이옥사이드 (MoO2Cl2), 몰리브덴 테트라클로라이드 옥사이드 (MoOCl4) 를 포함한다.

일부 실시예들에서, 캐리어 가스, 예컨대 질소 (N2), 아르곤 (Ar), 헬륨 (He), 또는 다른 불활성 가스들이 동작 206 동안 흐를 수도 있다.

동작 204는 임의의 적합한 지속기간 동안 그리고 임의의 적합한 온도로 수행될 수도 있다. 일부 예들에서, 동작 206은 약 0.25 초 내지 약 30 초, 약 0.25 초 내지 약 20 초, 약 0.25 초 내지 약 5 초, 또는 약 0.5 초 내지 약 3 초의 지속기간 동안 수행될 수도 있다. 이 동작은 일부 실시예들에서 기판의 표면 상의 활성 사이트들 (active sites) 을 포화시키기 충분한 지속기간 동안 수행될 수도 있다. 일부 실시예들에서, 전구체는 가스 라인을 충진하고 도징 전 라인 변화를 위해 방향전환 (divert) 될 수도 있다. 캐리어 가스는 동작 202에 대해 상기 기술된 것들 중 임의의 가스일 수도 있다.

다양한 실시예들에 따라, 동작 204 동안, 일부 WClx는 동작 200으로부터 표면 상에 남아 있는 H2와 반응할 수도 있고 일부 WClx는 표면 상에 남아 있는 H2와 완전히 반응하지 않을 수도 있다. 또한 다양한 실시예들에서, 일부 H2는 WClx와 전혀 반응하지 않을 수도 있고 WClx는 대신 H2가 기판 표면 상에 물리흡착 또는 남지 않는, 기판의 표면 상에 물리흡착될 수도 있다. 일부 실시예들에서, H2는 기판 표면 상에 남아 있을 수도 있지만 표면 상에 물리흡착 또는 화학흡착하지 않을 수도 있다. 도 2a의 동작 204는 이에 따라 일부 실시예들에서 텅스텐의 반-모노레이어 (sub-monolayer) 를 형성할 수도 있다. 유사하게, 동작 204는 일부 실시예들에서 몰리브덴의 반-모노레이어를 형성할 수도 있다.

동작 206에서, 피처의 표면 상의 수소 또는 다른 환원제와 반응하지 않은 여전히 가스 상인 과도한 전구체를 퍼지가 퍼지하도록 수행된다. 퍼지가 고정된 압력으로 불활성 가스를 흘리고, 이에 따라 챔버의 압력을 감소시키고 또 다른 가스 노출을 개시하기 전 챔버를 재-가압함으로써 수행될 수도 있다.

챔버는 임의의 적합한 지속기간 동안 퍼지될 수도 있다. 챔버는 약 0.25 초 내지 약 30 초, 약 0.25 초 내지 약 20 초, 약 0.25 초 내지 약 5 초, 또는 약 0.5 초 내지 약 3 초의 지속기간 동안 퍼지될 수도 있다. 일부 실시예들에서, 퍼지 지속기간은 약 0.1 초 내지 약 2 초이고 텅스텐의 표면으로 WClx의 저 흡착 레이트로 인해 기판 표면으로부터 WClx 또는 다른 전구체 모두를 제거하는 것을 방지할 수도 있다. 일부 실시예들에서, 퍼지 지속기간은 약 0.1 초 내지 약 15 초, 예컨대 약 7 초이다. 예를 들어, 3D NAND 구조체의 제조 동안, 챔버는 동작 206 동안 약 2 초 동안 퍼지될 수도 있다. 퍼지 가스는 동작 202에 대해 상기 기술된 가스들 중 임의의 가스일 수도 있다.

동작 204 및 동작 206은 이어서n 회 수행될 때까지 반복되고, 여기서k는 적어도 2의 정수이다. 이하에 더 기술된 바와 같이, 증착 시퀀스에서 퍼지들에 의해 분리된 복수의 텅스텐 펄스들을 수행함으로써, 원치 않은 에칭이 구조체들의 상단부들 및 에지들에서 감소될 수도 있다. 일 예에서, 동작 204는 0.7 초의 지속기간, 그리고 동작 206은 텅스텐 전구체 펄스들 사이에 2 초의 지속기간을 가질 수도 있다.n= 10에 대해, 2 × 10 = 20 초의 총 퍼지 시간과 함께, 총 텅스텐 전구체 시간은 0.7 × 10 = 7 초이다.

동작 208에서, 텅스텐 또는 몰리브덴 층이 적절한 두께로 증착되었는지 여부가 결정된다. 그렇지 않으면, 동작 200 내지 동작 206은 텅스텐 또는 몰리브덴 층의 목표된 두께는 피처의 표면 상에 증착될 때까지 반복된다. 동작 200 내지 동작 206의 반복 각각은 "사이클"로 지칭될 수도 있다. 일부 실시예들에서, 동작들 200/202 및 동작들 204/206의 순서는 텅스텐 또는 몰리브덴 전구체가 환원제의 도입 전에 도입되도록 반전될 수도 있다.

도 2b는 동작 200 및 동작 202가 사이클 동안 반복되지 않도록 ALD 사이클 각각이 단일 환원제 펄스 및 복수의 텅스텐 또는 몰리브덴 전구체 펄스들을 포함하는 실시예들에 대한 프로세스 흐름도를 제공한다. 도 2c는 동작 204 및 동작 206이 사이클 동안 반복되지 않도록 ALD 사이클 각각이 단일 텅스텐 또는 몰리브덴 전구체 펄스 및 복수의 환원제 펄스들을 포함하는 실시예들에 대한 프로세스 흐름도를 제공한다. 도 2b 및 도 2c의 프로세스 블록들은 그 외에는 도 2a에 대해 상기 기술된 바와 같다.

도 3은 H2 및 WClx를 사용하여 텅스텐을 증착하기 위한 프로세스에서 예시적인 증착 사이클들 311A 및 311B를 도시하는 타이밍 시퀀스도를 제공한다. 도 3은 도 2a 내지 도 2c의 동작 200의 일 실시예의 일 예인, 증착 사이클 311A에서의 H2펄스를 도시한다. 도 3의 예에서, H2펄스 동안, Ar 및 WClx 플로우들은 턴오프된다. 다른 실시예들에서, 퍼지 가스가 환원제 펄스 동안 계속해서 흐를 수도 있다. 일부 실시예들에서, 환원제 펄스 동안 퍼지 가스를 턴오프하는 것은 환원제로의 노출을 증가시키는데 유리하다. H2 직후, Ar 펄스가 도시된다. 이는 도 2a 내지 도 2c의 동작 202의 일 실시예의 일 예이다. 퍼지 펄스 동안, H2 및 WClx 플로우들은 턴오프된다. 320에서, 점선 박스는 이어서 텅스텐 전구체 펄스를 개입시키지 않고 수행되는, 임의의 수의 H2/Ar 퍼지 펄스들을 나타낸다. 이는 도 2a 및 도 2c의 동작 200 및 동작 202의 일 실시예의 일 예이다. 5 개의 H2/Ar 펄스 시퀀스들이 도시되지만, H2/Ar 펄스 시퀀스들의 수는 상기 기술된 바와 같이 1 내지k의 범위일 수 있다. 340에서 점선 박스는 환원제 펄스를 개입시키지 않고 수행되는 반복된 WClx/Ar 퍼지 펄스들을 나타낸다. 이는 도 2a 및 도 2b의 동작 204 및 동작 206의 일 실시예의 일 예이다. WClx 펄스 동안, Ar 밸브는 폐쇄되고 Ar 펄스 동안, WClx 밸브는 폐쇄된다. 수소 플로우는 프로세스 전반에 오프된다. 4 개의 WClx/Ar 펄스 시퀀스들이 도시되지만, WClx/Ar 펄스 시퀀스들의 수는 상기 기술된 바와 같이 1 내지n의 범위일 수 있다.

일부 실시예들에서, Ar 플로우는 H2 및/또는 WClx 펄스들 동안 온으로 남아 있을 수도 있고, Ar 펄스들은 H2 및 WClx 플로우들 없이, 일부 실시예들에서, 증가된 Ar 플로우를 특징으로 한다는 것을 주의해야 한다. 그러나, 텅스텐 전구체 펄스 동안 (희석되어 전달될 수도 있는) 텅스텐 전구체 가스의 희석을 더 방지하기 위해 퍼지 가스를 턴오프하는 것이 유리할 수 있다. 3-D NAND 구조체들의 충진은 웨이퍼에서 보다 높은 W 농도로부터 유리하고; 희석은 불량한 충진을 발생시킬 것이다. 게다가, 텅스텐 전구체 펄스 동안 퍼지 가스를 턴오프하고 퍼지 매니폴드를 가압하는 것은 그 사이에 W 펄스들을 갖는 연속적인 퍼지 플로우보다 효율적인 챔버의 퍼지를 인에이블한다. 유사하게, 이는 환원제 가스의 희석을 방지하기 위해 환원제 펄스 동안 퍼지 가스를 턴오프하는데 유리할 수도 있다. 도 3에 도시된 바와 같이, Ar 펄스는 증착 사이클 311A를 종료한다.

WClx가 도 3의 예에서 예시적 목적들로 도시되었지만, 도 3의 타이밍 시퀀스는 텅스텐 옥시클로라이드 전구체들 및 몰리브덴 클로라이드 및 몰리브덴 옥시클로라이드 전구체들을 포함하는 다른 전구체들에 대해 사용될 수도 있다. 유사하게, 다른 퍼지 가스들 및/또는 다른 환원제들이 Ar 및 H2 대신 사용될 수도 있다.

도 2a 내지 도 2c에 기술된 프로세스들 및 도 3을 참조하여 기술된 펄스 시퀀스는 펄스 시퀀스의 일 예이다. 당업자는 이루어질 수도 있는 다양한 수정들이 있다는 것을 이해할 것이다. 예를 들어, 일부 실시예들에서, 상이한 퍼지 가스가 상기 기술된 바와 같이 사용될 수도 있다. 유사하게, 기술된 프로세스가 염소-함유 텅스텐 또는 몰리브덴 전구체들에 특히 유용하지만 고 농도에서 기판들을 에칭하는 이들의 성향으로 인해, 프로세스는 또한 불소-함유 W 및 Mo 전구체들을 포함하는, 다른 전구체들 및 재료들을 사용하여 구조체들을 충진하기 위해 사용될 수도 있다. 특히, 프로세스는 고 종횡비 구조체들 및/또는 3D 구조체들의 충진에 유리할 수도 있다.

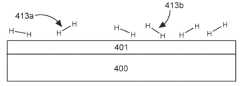

도 4a 내지 도 4j는 WCl6로부터 텅스텐의 증착에서 증착 사이클의 예시적인 메커니즘의 개략적인 예시들이다. 도 4a는 H2가 그 위에 증착된 하부 층 (401) 을 갖는 기판 (400) 에 도입되는 예시적인 메커니즘을 도시한다. 하부 층 (401) 은 일부 실시예들에서 배리어 층일 수도 있다. 예를 들어, 일부 실시예들에서, 하부 층 (401) 은 티타늄 나이트라이드 (TiN) 층이다. 일부 실시예들에서, 기판 (400) 은 텅스텐 핵생성 층을 포함하지 않는다는 것을 주의한다. 다른 실시예들에서, 이는 텅스텐 핵생성 층을 포함할 수도 있다. 수소가 가스 상 (411a 및 411b) 으로 도입되고 일부 H2 (413a 및 413b) 는, 금속 표면들 (예를 들어 H2) 상에 화학적으로 활성 흡착되고 비활성 표면들 (예를 들어 TiN) 상에 촉매로 물리흡착된 원자 수소로 촉매로 해리될 수도 있는, 하부 층 (401) 의 표면 상에 있다. 예를 들어, H2는 하부 층 (401) 상에 화학흡착할 필요가 없을 수도 있고, 일부 실시예들에서, 하부 층 (401) 의 표면 상에 물리흡착할 수도 있다.

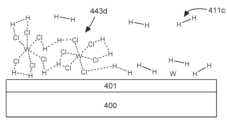

도 4b는 이전에 가스 상인 H2 (도 4a의 411a 및 411b) 가 챔버로부터 퍼지되고, 이전에 표면 (443a 및 413b) 상의 H2가 하부 층 (401) 의 표면 상에 남아 있는 예시적인 예시를 도시한다.

도 4c는 기판이 WCl6에 노출되고, 이들 중 일부는 가스 상 (431a 및 431b) 이고 이들 중 일부는 기판의 표면에 있거나 근방에 (423a 및 423b) 있는 예시적인 예시를 도시한다.

동작 200 동안, 일부 H2는 이전 도즈로부터 표면 상에 남아 있는 WCl6와 반응할 수도 있다. 도 4d에서, WCl6는 중간물 (443b) 을 일시적으로 형성하도록 H2와 반응할 수도 있고, 도 4e에서, 중간물 (443b) 은 하부 층 (401) 상에 기판 (400) 의 표면 상에 텅스텐 (490), 그리고 가스 상의 HCl (451a 및 451b, 예를 들어) 을 남기도록 완전히 반응한다. 이 예에서, 텅스텐 (490) 은 텅스텐을 증착하기 전, 하부 층 (401) 을 처리하지 않고 핵생성 층을 증착하지 않고 하부 층 (401) 직상에 성장한다는 것을 주의한다. 일부 실시예들에서, 하부 층 (401) 을 수소 또는 염소-함유 텅스텐 전구체에 노출하기 전, 하부 층 (401) 은, 예컨대 디보란에 노출함으로써 소킹 처리에 노출될 수도 있다는 것이 이해될 것이다. 일부 예들에서 하부 층 (401) 은 후속하는 WClx-H2 노출들 동안 희생적으로 반응할 수 있는 단단한 Si-B-H 계면 표면 층을 형성하도록 SiH4, B2H6, 및 H2의 혼합물로 이전에 처리되었다. Si-B-H 층들의 화학량론은 저 붕소 농도 (10 %) 로부터 고 붕소 농도 (95 %) 로 크게 가변할 수 있다.

도 2a 내지 도 2c의 동작 200 동안, 일부 H2 는 이전 도즈로부터 표면 상에 남아 있는 WCl6 (또는 다른 W 클로라이드들) 과 완전히 반응하지 않을 수도 있다. 도 4d에 도시된 바와 같이, WCl6는 중간물 (443a) 을 형성하도록 H2와 부분적으로 반응할 수도 있고, 도 4e에서, 나머지 중간물 (443a) 은 하부 층 (401) 상의 기판 (400) 의 표면 상에서 부분적으로 반응한다. 다양한 실시예들에서, 염소-함유 텅스텐 전구체 및 수소를 사용하여 증착된 막은 약 50 Å까지의 증착 두께들에 대해 보란, 실란 또는 게르만을 사용하여 증착된 막보다 낮은 저항률을 갖는다. 예를 들어, 특정한 이론에 제한되지 않고, WCl6의 화학량론은 일 분자의 WCl6와 적어도 3 개의 H2 분자들을 사용할 수도 있다. WCl6는 텅스텐을 형성하는 대신 중간물이 형성되는, H2의 분자들과 부분적으로 반응하는 것이 가능하다. 예를 들어, 이는 화학량론 원리들에 기초하여 (예를 들어, 3 개의 H2 분자들이 일 분자의 WCl6와 반응하도록 사용된) WCl6와 반응하도록 인접하여 충분한 H2가 없으면 발생할 수도 있어, 기판의 표면 상에 중간물 (443a) 을 남긴다. 텅스텐 클로라이드들은 분자 H2 에 화학적으로 불활성일 수도 있고 분자 H2의 촉매 해리에 의해 생성된 흡착된 원자 수소의 존재를 필요로 할 수도 있다. 이 경우 과도한 분자 H2는 텅스텐 클로라이드들을 금속성 텅스텐으로 완전히 환원하기 위해 필요할 수도 있는 단순한 화학량론 비를 넘는다 (100 대 1의 분자 H2 / WClx 비).

도 4f는 챔버가 퍼지될 때 기판의 예시적인 개략도를 제공한다. 이는 도 2a 내지 도 2c의 동작 202에 대응할 수도 있다. 도 4f의 화합물 (443c) 은 완전히 반응하지 않은 형성된 중간물일 수도 있지만, 일부 텅스텐 (490) 이 기판 상에 형성될 수도 있다는 것을 주의한다. 이에 따라 사이클 각각은 기판 상에 텅스텐의 반-모노레이어를 형성한다.

예로서, 도 4g는 사이클이 반복될 때, 가스 상의 H2(411c) 가 증착된 텅스텐 (490) 및 그 위에 부분적으로 반응된 중간물 (443d) 을 갖는 기판에 도입되는 예시를 도시한다. 이는 텅스텐이 적절한 두께로 증착되지 않았다고 동작 208에서 결정된 후 반복된 사이클에서 도 2a 내지 도 2c의 동작 200에 대응할 수도 있다. 도 4g에 도시된 바와 같이, 도입된 H2는 이제 도 4h에 도시된 바와 같이, 반복된 화합물 (443d) 은 증착된 텅스텐 (490b 및 490c) 을 넘어 떠나고, 그리고 생성물들 HCl (451c 및 451d) 에 의해 가스 상에 형성되도록 기판 상의 중간물 (443d) 과 완전히 반응할 수도 있다는 것을 주의한다. 일부 H2(411c) 가 가스 상으로 남을 수도 있지만, 일부 H2(413c) 는 텅스텐 층 (490a) 상에 남아 있을 수도 있다.

도 4i에서, (도 2a 내지 도 2c의 동작 202에 대응하여) 챔버는 퍼지되어, 텅스텐 (490a, 490b, 및 490c), 및 일부 H2(413c) 를 넘어 떠난다. 도 4j에서, WCl6는 분자들 (431c 및 423c) 이 H2 및 기판에 흡착 및/또는 퍼지할 수도 있도록 도즈로 다시 도입된다. 도 4j는 도 2a 내지 도 2c의 동작 204에 대응할 수도 있다. WCl6 도즈 후, 챔버는 다시 퍼지될 수도 있고 사이클들이 목표된 두께의 텅스텐이 증착될 때까지 다시 반복될 수도 있다.

특정한 개시된 실시예들을 사용하여 증착된 텅스텐 막들은 불소 함량을 갖지 않는다. 몰리브덴 막들이 또한 불소 함량을 갖지 않을 수도 있다. 막들의 전체 인장 응력이 약 0.2 GPa보다 작을 수도 있다. 불소-프리 텅스텐 전구체들은 텅스텐 펜타클로라이드 (WCl5) 및 텅스텐 헥사클로라이드 (WCl6) 와 같은 텅스텐 카르보닐 (W(CO)6) 및 텅스텐 클로라이드들 (WClx) 을 포함할 수도 있다. 불소-프리 몰리브덴 전구체들은 본 명세서에 기술된 몰리브덴 옥시클로라이드 및 몰리브덴 클로라이드 전구체들 뿐만 아니라 몰리브덴 헥사카르보닐 (Mo(CO)6) 을 포함한다.

개시된 실시예들은 텅스텐 및 몰리브덴 증착 프로세스들의 다양한 적용예들을 가질 수도 있다. 본 명세서에 기술된 적용예들의 다양한 조합들은 텅스텐 또는 몰리브덴을 증착하도록 사용될 수도 있고 방법들은 본 명세서에 제공된 예들로 제한되지 않는다는 것이 이해될 것이다.

예를 들어, 일부 실시예들에서, 피처가 환원제 (예를 들어, 수소와 보론, 실란, 또는 게르만) 및 텅스텐 전구체 예컨대 WCl6의 교번하는 펄스들의 ALD 사이클들에 의해 텅스텐 핵생성 층을 증착하고, 이어서 도 2 및 도 3에 대해 상기 기술된 바와 같이 수소 및 염소-함유 텅스텐 전구체의 교번하는 펄스들에 의해 벌크 텅스텐을 증착함으로써 충진될 수도 있다. 유사하게, 일부 실시예들에서, 피처가 환원제 및 몰리브덴 전구체의 교번하는 펄스들의 ALD 사이클들에 의해 몰리브덴 층을 증착함으로써 충진될 수도 있다. 텅스텐 클로라이드 전구체 및 수소 환원제의 교번하는 펄스들을 사용하는 프로세스에 의한 벌크 텅스텐의 증착은 반응물질들의 교번하는 펄스들로 인해 ALD 프로세스들로서 지칭될 수도 있다. 본 명세서에 기술된 방법들은 통상적으로 CVD 메커니즘으로부터 컴포넌트 성장이 없다는 것을 보장하도록 반응물질 사이클들 사이에 퍼지를 수반한다.

그러나, 일부 실시예들에서, 방법들은 미국 특허 공개 번호 제 20170117155 호 및 미국 특허 제 9,613,818 호에 기술된 바와 같이 "순차적 CVD" 프로세스들과 함께 사용될 수도 있고, 양자는 참조로서 본 명세서에 인용된다.

단일 증착 사이클 동안 교번하는 전구체 및 퍼지 가스 펄스들의 복수의 사이클들을 채용함으로써, 전구체는 구조체들의 상단부 및 측방향 에지들에서 에칭을 최소화하여 3D NAND 워드라인들 내로 깊이 전달될 수 있다. 전구체의 모노레이어 또는 반-모노레이어는 구조체 전반에 흡착될 수 있다. 일부 실시예들에서, 교번하는 전구체 및 퍼지 펄스들을 갖는 것은 전구체 도즈 전달 전 가압될 전구체 저장부를 인에이블한다. 이는 구조체로 보다 우수한 이송을 발생시킬 수 있다.

표 1은 H2/Ar/WClx/Ar 시퀀스 및 H2/Ar/n(WClx/Ar) 시퀀스에 노출된 300 Å PVD TiN 블랭킷 막들에 대한 조건들 및 발생하는 TiN 하부 층을 도시하고,n은 10과 같다.

| 프로세스 | 하부 층 | W 도즈 시간 | Ar 퍼지 시간 | 사이클들 | 분압 * 지속기간 (W Torr-S)* 1000 | TiN 에칭 (Å) |

| FFW 10 W/Ar 펄스들 0.5 % W | 300A PVD TiN | x | y | 10z | 250 | 144 |

| FFW 1 W/Ar 펄스들 0.5 % W | 300A PVD TiN | 10x | 10y | z | 250 | 300 |

표 1의 조건들 및 결과들은 동일한 전체 텅스텐 전구체 노출에 대해, 에칭된 TiN의 양은 복수의 펄스들의 텅스텐 전구체를 사용하여 상당히 낮다는 것을 도시한다. 특히, TiN 전체는 단일 텅스텐 전구체 펄스를 갖는 시퀀스 동안 에칭된다.

도 5는 H2/Ar/WClx/Ar 시퀀스 및 H2/Ar/n(WClx/Ar) 시퀀스를 사용하여 3-D NAND 구조체들의 텅스텐 충진을 비교하는 실험 결과들의 개략적 예시를 도시한다. 핵생성 층이 이들 시퀀스들 전에 구조체 각각에 증착된다. 도 5의 예시들은 3-D NAND 구조체들의 중간 섹션들로부터 단면의 표현이다. 3-D NAND 구조체 (503) 는 H2/Ar/WClx/Ar 시퀀스 후 이미지이고, 511에 나타낸 바와 같이, 중심 워드라인들에서 불량한 텅스텐 증착을 도시한다. 균일한 텅스텐 증착은 H2/Ar/n(WClx/Ar) 에 노출되는, 3-D NAND 구조체 (503) 전반에서 관찰되고,n= 10이다. Torr-s의 총 텅스텐 전구체 노출이 501 및 503 모두에 동일하다.

n텅스텐 펄스들 각각은 짧고 일정한 압력으로 전달될 수도 있다. 텅스텐 전구체의 총 양은 텅스텐 전구체가 구조체의 하단부에 도달하고 전체 구조체를 측방향으로 코팅하도록 충분한 재료를 제공하는데 충분하다. 개입되는 불활성 가스 퍼지는 구조체의 상단부 및 에지들에서 텅스텐 전구체를 제거할 수도 있어, 기판 에칭을 감소시키거나 제거한다. 충분한 불활성 가스 퍼지가 없다면, 이 유리한 효과는 관찰되지 않을 수도 있다. 또한, 주변 개구부들에서 핀치 효과가 복수의 텅스텐 펄스들 사이 불충분한 퍼지에 대해 관찰될 수도 있다.

이에 따라, 일부 실시예들에서, 불활성 가스 퍼지의 지속기간은 적어도 텅스텐 또는 몰리브덴 전구체 지속기간만큼 길다. 일부 실시예들에서, 불활성 가스 퍼지는 텅스텐 또는 몰리브덴 전구체 펄스의 지속기간의 적어도 1.5 배 또는 적어도 2 배 또는 적어도 3 배이다. 전구체 노출에 대한 퍼지 가스는 또한 분압 × 지속기간의 면에서 특징화될 수도 있다. 퍼지는 플로우의 1 % 내지 5 %로 희석된 전구체와 함께, 100 % 퍼지 가스로 수행될 수도 있다.

상기 기술은 텅스텐 클로라이드들로부터 텅스텐 및 텅스텐-함유 층들의 증착에 포커싱하지만, 도 2 및 도 3을 참조하여 상기 기술된 프로세스들은 다른 전구체들 및/또는 다른 재료들을 사용한 피처 충진과 함께 수행될 수도 있다. 상기 나타낸 바와 같이, 방법은 구조체를 에칭할 수 있는 화학물질들에 대해 유리하다. 이에 더하여, 복수의 전구체 펄스/퍼지 사이클들을 포함하는 방법은 흡착되지 않은 분자들을 퍼지함으로써 CVD-타입 특성 없이 성장을 달성하는데 유리할 수도 있다.

개시된 실시예들은 임의의 적합한 압력, 약 10 Torr보다 큰 압력들, 또는 약 10 Torr보다 작은 압력들에서 수행될 수도 있다. 멀티-스테이션 챔버에 대해, 페데스탈 각각은 상이한 온도들로 설정될 수도 있다. 일부 실시예들에서, 페데스탈 각각은 동일한 온도로 설정된다. 기판들은 개시된 실시예들에 따른 상기 기술된 동작들 중 임의의 동작 또는 임의의 모든 동작들 동안 스테이션간 (from station to station) 순환될 수도 있다. 챔버 압력은 또한 특정한 개시된 실시예들의 하나 이상의 동작들에서 조절될 수도 있다. 일부 실시예들에서, 핵생성 증착 동안 챔버 압력은 벌크 증착 동안 챔버 압력과 상이하다. 일부 실시예들에서, 핵생성 증착 동안 챔버 압력은 벌크 증착 동안 챔버 압력과 동일하다.

장치

임의의 적합한 챔버가 개시된 실시예들을 구현하도록 사용될 수도 있다. 예시적인 증착 장치들은 다양한 시스템들, 예를 들어, California, Fremont 소재의 Lam Research Corp.로부터 입수가능한 ALTUS® 및 ALTUS® Max 또는 임의의 다양한 다른 상업적으로 입수가능한 프로세싱 시스템들을 포함한다. 일부 실시예들에서, 순차 CVD가 단일 증착 챔버 내에 위치된 2, 5 또는 훨씬 보다 많은 증착 스테이션들 중 하나인 제 1 스테이션에서 수행될 수도 있다. 따라서, 예를 들어, 수소 (H2) 및 텅스텐 헥사클로라이드 (WCl6) 는 기판 표면에서 국부화된 대기를 생성하는 개별 가스 공급 시스템을 사용하여 제 1 스테이션에서 반도체 기판의 표면에 교번하는 펄스들로 도입될 수도 있다. 또 다른 스테이션이 불소-프리 텅스텐 증착, 또는 CVD를 위해 사용될 수도 있다. 2 이상의 스테이션들이 병렬 프로세싱으로 텅스텐을 증착하도록 사용될 수도 있다. 대안적으로, 웨이퍼가 순차적 CVD 동작들이 2 이상의 스테이션들에 걸쳐 순차적으로 수행되게 하도록 인덱싱될 수도 있다.

도 6은 실시예들에 따른 증착 프로세스들을 수행하기 적합한 프로세스 시스템의 개략도이다. 시스템 (600) 은 이송 모듈 (603) 을 포함한다. 이송 모듈 (603) 은 다양한 반응 모듈들 사이에서 이동될 때 프로세싱될 기판들의 오염 위험을 최소화하도록 클린, 가압된 분위기를 제공한다. 다양한 실시예들에 따라 ALD 및 CVD를 수행할 수 있는 멀티-스테이션 반응기 (609) 가 이송 모듈 (603) 상에 장착된다. 멀티-스테이션 반응기 (609) 는 개시된 실시예들에 따른 동작들을 순차적으로 수행할 수도 있는 복수의 스테이션들 (611, 613, 615, 및 617) 을 포함할 수도 있다. 예를 들어, 멀티-스테이션 반응기 (609) 는 스테이션 (611) 이 염소-함유 텅스텐 전구체 또는 불소-함유 전구체를 사용하여 PNL 텅스텐 핵생성 층 증착을 수행하고, 그리고 스테이션 (613) 은 다양한 실시예들에 따른 ALD 텅스텐 증착 동작을 수행하도록 구성될 수도 있다. 일부 실시예들에서, 스테이션 (615) 은 ALD 텅스텐 증착 동작을 수행할 수도 있고, 그리고 스테이션 (617) 은 비순차적 CVD 동작을 수행할 수도 있다. 일부 실시예들에서, 텅스텐 전구체 펄스들의 수 (n) 는 스테이션 (613 내지 615) 으로부터 가변할 수도 있다.

스테이션들은 가열된 페데스탈 또는 기판 지지부, 하나 이상의 가스 유입구들 또는 샤워헤드 또는 확산 플레이트를 포함할 수도 있다. 기판 지지부 (702) 및 샤워헤드 (703) 를 포함하는, 증착 스테이션 (700) 의 일 예가 도 7에 도시된다. 히터가 페데스탈 부분 (701) 에 제공될 수도 있다.

도 6을 다시 참조하면, 플라즈마 또는 화학적 (비플라즈마) 사전-세정, 다른 증착 동작들, 또는 에칭 동작들을 수행할 수 있는 하나 이상의 단일 스테이션 모듈 또는 멀티-스테이션 모듈들 (607) 이 또한 이송 모듈 (503) 상에 장착될 수도 있다. 모듈은 또한 예를 들어, 증착 프로세스를 위해 기판을 준비하도록 다양한 처리들에 사용될 수도 있다. 시스템 (600) 은 또한 웨이퍼들이 프로세싱 전 후에 저장되는, 하나 이상의 웨이퍼 소스 모듈들 (601) 을 포함한다. 대기 이송 챔버 (619) 의 대기 로봇 (미도시) 이 소스 모듈들 (601) 로부터 로드록 (621) 으로 웨이퍼들을 먼저 제거할 수도 있다. 이송 모듈 (603) 의 웨이퍼 이송 디바이스 (일반적으로 로봇 암 유닛) 는 로드록 (621) 으로부터 이송 모듈 (603) 상에 장착된 모듈들 사이에 웨이퍼들을 이동시킨다.

다양한 실시예들에서, 시스템 제어기 (629) 가 증착 동안 프로세스 조건들을 제어하기 위해 채용된다. 제어기 (629) 는 통상적으로 하나 이상의 메모리 디바이스들 및 하나 이상의 프로세서들을 포함할 것이다. 프로세서는 CPU 또는 컴퓨터, 아날로그 입력/출력 연결부 및/또는 디지털 입력/출력 연결부, 스텝퍼 모터 제어 보드들, 등을 포함할 수도 있다.

제어기 (629) 는 증착 장치의 모든 액티비티들을 제어할 수도 있다. 시스템 제어기 (629) 는 타이밍, 가스들의 혼합물, 챔버 압력, 챔버 온도, 웨이퍼 온도, RF (radio frequency) 전력 레벨들, 웨이퍼 척 또는 페데스탈 위치, 및 특정한 프로세스의 다른 파라미터들을 제어하기 위한 인스트럭션들의 세트들을 포함하는, 시스템 제어 소프트웨어를 실행한다. 일부 실시예들에서 제어기 (629) 와 연관된 메모리 디바이스들 상에 저장된 다른 컴퓨터 프로그램들이 채용될 수도 있다.

통상적으로, 제어기 (629) 와 연관된 사용자 인터페이스가 있을 것이다. 사용자 인터페이스는 디스플레이 스크린, 장치 및/또는 프로세스 조건들의 그래픽 소프트웨어 디스플레이들, 포인팅 디바이스들, 키보드들, 터치 스크린들, 마이크로폰들, 등과 같은 사용자 입력 디바이스들을 포함할 수도 있다.

시스템 제어 로직은 임의의 적합한 방식으로 구성될 수도 있다. 일반적으로, 로직은 하드웨어 및/또는 소프트웨어로 구성되거나 설계될 수 있다. 구동 회로를 제어하기 위한 인스트럭션들은 하드코딩될 수도 있고 또는 소프트웨어로서 제공될 수도 있다. 인스트럭션들은 "프로그래밍"에 의해 제공될 수도 있다. 이러한 프로그래밍은 DSPs (digital signal processors), ASICs (application-specific integrated circuits), 및 하드웨어로서 구현된 특정한 알고리즘들을 갖는 다른 디바이스들을 포함하는 임의의 형태의 로직을 포함하는 것으로 이해된다. 프로그래밍은 또한 범용 프로세서 상에서 실행될 수도 있는 소프트웨어 또는 펌웨어 인스트럭션들을 포함하는 것으로 이해된다. 시스템 제어 소프트웨어가 임의의 적합한 컴퓨터 판독가능 프로그램 언어로 코딩될 수도 있다.

프로세스 시퀀스의 게르마늄-함유 환원제 펄스들, 수소 플로우, 및 텅스텐-함유 전구체 펄스들, 및 다른 프로세스들을 제어하기 위한 컴퓨터 프로그램 코드는 임의의 종래의 컴퓨터 판독가능 프로그래밍 언어: 예를 들어, 어셈블리어, C, C++, Pascal, Fortran, 등으로 작성될 수 있다. 컴파일링된 객체 코드 또는 스크립트가 프로그램에서 식별된 태스크들을 수행하도록 프로세서에 의해 실행된다. 또한 나타낸 바와 같이, 프로그램 코드는 하드코딩될 수도 있다.

제어기 파라미터들은, 예를 들어, 프로세스 가스 조성 및 플로우 레이트들, 온도, 압력, 냉각 가스 압력, 기판 온도, 및 챔버 벽 온도와 같은 프로세스 조건들에 관련된다. 이들 파라미터들은 사용자 인터페이스를 활용하여 입력될 수도 있고 레시피의 형태로 사용자들에게 제공된다.

프로세스를 모니터링하기 위한 신호들은 시스템 제어기 (629) 의 아날로그 입력 연결부 및/또는 디지털 입력 연결부에 의해 제공될 수도 있다. 프로세스를 제어하기 위한 신호들은 증착 장치 (600) 의 아날로그 출력 연결부 및 디지털 출력 연결부 상에 출력된다.

시스템 소프트웨어는 많은 다양한 방식들로 설계되거나 구성될 수도 있다. 예를 들어, 다양한 챔버 컴포넌트 서브루틴들 또는 제어 객체들이 개시된 실시예들에 따른 증착 프로세스들을 수행하기 위해 필요한 챔버 컴포넌트들의 동작을 제어하도록 작성될 수도 있다. 이 목적을 위한 프로그램들 또는 프로그램들의 섹션들의 예들은 기판 포지셔닝 코드, 프로세스 가스 제어 코드, 압력 제어 코드, 및 히터 제어 코드를 포함한다.

일부 구현예들에서, 제어기 (629) 는 상기 기술된 예들의 일부일 수도 있는 시스템의 일부이다. 이러한 시스템들은, 프로세싱 툴 또는 툴들, 챔버 또는 챔버들, 프로세싱용 플랫폼 또는 플랫폼들, 및/또는 특정 프로세싱 컴포넌트들 (웨이퍼 페데스탈, 가스 플로우 시스템, 등) 을 포함하는, 반도체 프로세싱 장비를 포함할 수 있다. 이들 시스템들은 반도체 웨이퍼 또는 기판의 프로세싱 이전에, 프로세싱 동안에 그리고 프로세싱 이후에 그들의 동작을 제어하기 위한 전자장치에 통합될 수도 있다. 전자장치는 시스템 또는 시스템들의 다양한 컴포넌트들 또는 하위부분들을 제어할 수도 있는 "제어기"로서 지칭될 수도 있다. 제어기 (629) 는, 시스템의 프로세싱 요건들 및/또는 타입에 따라서, 프로세싱 가스들의 전달, 온도 설정사항들 (예를 들어, 가열 및/또는 냉각), 압력 설정사항들, 진공 설정사항들, 전력 설정사항들, 일부 시스템들에서 무선 주파수 (RF) 생성기 설정사항들, RF 매칭 회로 설정사항들, 주파수 설정사항들, 플로우 레이트 설정사항들, 유체 전달 설정사항들, 위치 및 동작 설정사항들, 툴 및 다른 이송 툴들 및/또는 특정 시스템과 연결되거나 인터페이싱된 로드록들 내외로의 웨이퍼 이송들을 포함하는, 본 명세서에 개시된 프로세스들 중 임의의 프로세스들을 제어하도록 프로그래밍될 수도 있다.

일반적으로 말하면, 제어기는 인스트럭션들을 수신하고, 인스트럭션들을 발행하고, 동작을 제어하고, 세정 동작들을 인에이블하고, 엔드 포인트 측정들을 인에이블하는, 등을 하는 다양한 집적 회로들, 로직, 메모리, 및/또는 소프트웨어를 갖는 전자장치로서 규정될 수도 있다. 집적 회로들은 프로그램 인스트럭션들을 저장하는 펌웨어의 형태의 칩들, 디지털 신호 프로세서들 (DSP), ASICs (Application Specific Integrated Circuits) 로서 규정되는 칩들, 및/또는 프로그램 인스트럭션들 (예를 들어, 소프트웨어) 을 실행하는 하나 이상의 마이크로프로세서들, 또는 마이크로제어기들을 포함할 수도 있다. 프로그램 인스트럭션들은 반도체 웨이퍼 상에서 또는 반도체 웨이퍼에 대한 특정 프로세스를 실행하기 위한 동작 파라미터들을 규정하는, 다양한 개별 설정사항들 (또는 프로그램 파일들) 의 형태로 제어기로 또는 시스템으로 전달되는 인스트럭션들일 수도 있다. 일부 실시예들에서, 동작 파라미터들은 하나 이상의 층들, 재료들, 금속들, 옥사이드들, 실리콘, 실리콘 다이옥사이드, 표면들, 회로들, 및/또는 웨이퍼의 다이들의 제조 동안에 하나 이상의 프로세싱 단계들을 달성하도록 프로세스 엔지니어들에 의해서 규정된 레시피의 일부일 수도 있다.

제어기 (629) 는, 일부 구현예들에서, 시스템에 포함되거나, 시스템에 커플링되거나, 이와 달리 시스템에 네트워킹되거나, 또는 이들의 조합으로 될 수 있는 컴퓨터에 커플링되거나 이의 일부일 수도 있다. 예를 들어, 제어기 (629) 는 웨이퍼 프로세싱의 원격 액세스를 가능하게 할 수 있는 공장 (fab) 호스트 컴퓨터 시스템의 전부 또는 일부이거나 "클라우드" 내에 있을 수도 있다. 컴퓨터는 제조 동작들의 현 진행을 모니터링하고, 과거 제조 동작들의 이력을 조사하고, 복수의 제조 동작들로부터 경향들 또는 성능 계측치들을 조사하고, 현 프로세싱의 파라미터들을 변경하고, 현 프로세싱을 따르는 프로세싱 단계들을 설정하고, 또는 새로운 프로세스를 시작하기 위해서 시스템으로의 원격 액세스를 인에이블할 수도 있다. 일부 예들에서, 원격 컴퓨터 (예를 들어, 서버) 는 로컬 네트워크 또는 인터넷을 포함할 수도 있는 네트워크를 통해서 프로세스 레시피들을 시스템에 제공할 수 있다. 원격 컴퓨터는 차후에 원격 컴퓨터로부터 시스템으로 전달될 파라미터들 및/또는 설정사항들의 입력 또는 프로그래밍을 인에이블하는 사용자 인터페이스를 포함할 수도 있다. 일부 예들에서, 제어기는 하나 이상의 동작들 동안에 수행될 프로세스 단계들 각각에 대한 파라미터들을 특정하는, 데이터의 형태의 인스트럭션들을 수신한다. 파라미터들은 제어기가 제어하거나 인터페이싱하도록 구성되는 툴의 타입 및 수행될 프로세스의 타입에 특정적일 수도 있다는 것이 이해되어야 한다. 따라서 상기 기술된 바와 같이, 제어기는 예컨대 본 명세서에 기술된 프로세스들 및 제어들과 같은, 공동의 목적을 향해 함께 네트워킹되고 작동되는 하나 이상의 개별 제어기들을 포함함으로써 분산될 수도 있다. 이러한 목적들을 위한 분산형 제어기의 예는 챔버 상의 프로세스를 제어하도록 조합되는 (예컨대 플랫폼 레벨에서 또는 원격 컴퓨터의 일부로서) 원격으로 위치한 하나 이상의 집적 회로들과 통신하는 챔버 상의 하나 이상의 집적 회로들일 것이다.

비한정적으로, 예시적인 시스템들은 플라즈마 에칭 챔버 또는 모듈, 증착 챔버 또는 모듈, 스핀-린스 챔버 또는 모듈, 금속 도금 챔버 또는 모듈, 세정 챔버 또는 모듈, 베벨 에지 에칭 챔버 또는 모듈, PVD 챔버 또는 모듈, CVD 챔버 또는 모듈, ALD 챔버 또는 모듈, ALE (Atomic Layer Etch) 챔버 또는 모듈, 이온 주입 챔버 또는 모듈, 트랙 (track) 챔버 또는 모듈, 및 반도체 웨이퍼들의 제조 및/또는 제작 시에 사용되거나 연관될 수도 있는 임의의 다른 반도체 프로세싱 시스템들을 포함할 수도 있다.

상술한 바와 같이, 툴에 의해서 수행될 프로세스 단계 또는 단계들에 따라서, 제어기는, 반도체 제작 공장 내의 툴 위치들 및/또는 로드 포트들로부터/로드 포트들로 웨이퍼들의 컨테이너들을 이동시키는 재료 이송 시에 사용되는, 다른 툴 회로들 또는 모듈들, 다른 툴 컴포넌트들, 클러스터 툴들, 다른 툴 인터페이스들, 인접 툴들, 이웃하는 툴들, 공장 도처에 위치한 툴들, 메인 컴퓨터, 또 다른 제어기, 또는 툴들 중 하나 이상과 통신할 수도 있다.

제어기 (629) 는 다양한 프로그램들을 포함할 수도 있다. 기판 포지셔닝 프로그램은 기판을 페데스탈 또는 척 상으로 로딩하도록 그리고 기판과 가스 유입구 및/또는 타깃과 같은 챔버의 다른 부분들 사이의 간격을 제어하도록 사용되는 챔버 컴포넌트들을 제어하기 위한 프로그램 코드를 포함할 수도 있다. 프로세스 가스 제어 프로그램은 가스 조성, 플로우 레이트들, 펄스 시간들을 제어하기 위한, 그리고 선택가능하게 챔버 내 압력을 안정화하기 위해 증착 전에 챔버 내로 가스를 흘리기 위한 코드를 포함할 수도 있다. 압력 제어 프로그램은 예를 들어, 챔버의 배기 시스템의 쓰로틀 밸브를 조절함으로써 챔버의 압력을 제어하기 위한 코드를 포함할 수도 있다. 히터 제어 프로그램은 기판을 가열하도록 사용되는 가열 유닛으로 전류를 제어하기 위한 코드를 포함할 수도 있다. 대안적으로, 히터 제어 프로그램은 웨이퍼 척으로 (헬륨과 같은) 열 전달 가스의 전달을 제어할 수도 있다.

증착 동안 모니터링될 수도 있는 챔버 센서들의 예들은 질량 유량 제어기들, 마노미터들 (manometers) 과 같은 압력 센서들, 및 페데스탈 또는 척에 위치된 써모커플들 (thermocouples) 을 포함한다. 적절하게 프로그래밍된 피드백 및 제어 알고리즘들이 목표된 프로세스 조건들을 유지하기 위해 이들 센서들로부터 데이터로 사용될 수도 있다.

장치는 도 8에서 개략적으로 도시된 바와 같이 다양한 가스 분배 라인들에 라인 전하들을 제공하는, 가스 매니폴드 시스템을 포함할 수도 있다. 매니폴드 (804) 는 텅스텐-함유 또는 몰리브덴-함유 전구체 가스 (미도시) 의 소스로부터 입력 (802) 을 갖고, 매니폴드 (811) 는 수소 또는 다른 환원 가스 (미도시) 의 소스로부터 입력 (809) 을 갖고 매니폴드 (821) 는 불활성 퍼지 가스 (미도시) 의 소스로부터 입력 (819) 을 갖는다. 매니폴드들 (804, 811 및 821) 은 전구체 가스, 환원 가스 및 퍼지 가스를 각각 밸브 연결된 (valved) 분배 라인들 (805, 813 및 825) 을 통해 증착 챔버로 제공한다. 다양한 밸브들은 라인 전하를 제공하도록, 즉, 분배 라인들을 가압하도록 개방되거나 폐쇄된다. 예를 들어, 분배 라인 (805) 을 가압하기 위해, 밸브 (806) 는 진공에 대해 폐쇄되고, 밸브 (808) 는 폐쇄된다. 적합한 시간 증분 후, 밸브 (808) 가 개방되고 전구체 가스는 챔버로 전달된다. 가스의 전달을 위한 적합한 시간 후, 밸브 (808) 가 폐쇄된다. 이어서 챔버는 진공으로 밸브 (806) 의 개방에 의해 진공으로 퍼지될 수 있다.

유사한 프로세스들이 환원 가스 및 퍼지 가스를 전달하도록 사용된다. 환원 가스를 도입하기 위해, 예를 들어, 분배 라인 (813) 은 진공으로 밸브 (815) 를 폐쇄하고 밸브 (817) 를 폐쇄함으로써 대전된다. 밸브 (815) 의 개방은 챔버로 환원 가스의 전달을 허용한다. 유사하게, 퍼지 가스를 도입하기 위해, 분배 라인 (825) 은 진공으로 밸브 (827) 를 폐쇄하고 밸브 (823) 를 폐쇄함으로써 대전된다. 밸브 (827) 의 개방은 챔버로 아르곤 또는 다른 불활성 퍼지 가스의 전달을 허용한다. 라인 전하들에 대해 허용된 시간 양은 가스의 최초 전달의 양 및 타이밍을 변화시킨다.

도 6은 또한 밸브들 (806, 817 및 823) 각각이 시스템을 퍼지하도록 개방될 수 있는, 진공 펌프들을 도시한다. 다양한 분배 라인들을 통한 가스의 공급은 플로우 레이트들, 플로우의 지속기간, 및 프로세스들의 시퀀스로 프로그래밍되는 마이크로프로세서, 디지털 신호 프로세서, 등에 의해 제어되는 질량 유량 제어기와 같은 제어기에 의해 제어된다.

상기 기술된 프로세스들은 증착 동안 반도체 기판에 시약의 펄스들을 공급하는 밸브들 및 질량 유량 제어기들 (MFCs) 의 정밀한 타이밍을 필요로 할 수도 있다는 것을 주의한다. 이를 가능하게 하는 일 방법에서, 밸브 및 MFC 커맨드들이 PNL 증착 시퀀스의 전부 또는 일부에 대해 모든 시간 임계 커맨드들에 대한 인스트럭션들을 포함하는 정보의 이산 패킷들로 임베딩된 (embedded) 디지털 입력-출력 제어기들 (IOC) 에 전달된다. Lam Research의 ALTUS 시스템은 적어도 하나의 IOC 시퀀스를 제공한다. IOC들은 장치 내의 다양한 지점들; 예를 들어, 프로세스 모듈 내 또는 프로세스 모듈로부터 어느 정도 거리에 서 있는 독립형 전력 랙 상에 물리적으로 위치될 수 있다. 통상적으로 모듈 각각에 복수의 IOC들 (예를 들어, 모듈 당 3) 이 있다. 시퀀스에 포함된 실제 인스트럭션들에 대해, 밸브들을 제어하고 (모든 캐리어 및 반응물질 가스들을 위해) MFCs에 대한 플로우를 설정하기 위한 모든 커맨드들이 단일 IOC 시퀀스에 포함될 수도 있다. 이는 모든 디바이스들의 타이밍이 절대 시각으로부터 그리고 또한 서로 상대적으로 엄격하게 제어된다는 것을 보장한다. 통상적으로 임의의 주어진 시간에 실행하는 복수의 IOC 시퀀스들이 있다. 이는 말하자면, PNL로 하여금 이들 스테이션들에서 PNL-W 핵생성 층을 증착하기 위해 필요한 모든 하드웨어 컴포넌트들에 대해 제어된 모든 타이밍으로 스테이션 1 및 스테이션 2에서 실행되게 한다. 제 2 시퀀스가 동일한 모듈의 다른 증착 스테이션들에서 상기 기술된 타이밍 시퀀스를 사용하여 텅스텐 벌크를 증착하도록 동시에 실행될 수도 있다. 스테이션 3 및 스테이션 4로 시약들의 전달을 제어하는 디바이스들의 상대적인 타이밍은 디바이스들의 그룹에서 중요하지만, 스테이션 1 및 스테이션 2에서 PNL 프로세스의 상대적인 타이밍이 스테이션 3 및 스테이션 4의 상대적인 타이밍으로부터 오프셋될 수 있다. IOC는 패킷화된 시퀀스로 정보를 변환하고 디지털 또는 아날로그 커맨드 신호들을 밸브들을 제어하는 MFC 또는 공압 솔레노이드 뱅크들에 직접 전달한다.

텅스텐-함유 가스의 펄스는 다음과 같이 생성될 수도 있다. 처음에, 시스템은 MFC 또는 다른 플로우-제어 디바이스가 안정화되는 동안 시간의 기간 동안 진공 펌프로 WClx를 방향전환한다. 이는 일 예에서 약 0.5 내지 5 초의 기간 동안 이루어질 수도 있다. 다음에, 시스템은 방향전환 유출구 (606) 및 유출구 (608) 모두를 증착 챔버에 대해 폐쇄함으로써 텅스텐 가스 전달 매니폴드를 가압한다. 이는 예를 들어, 증착 챔버로의 유출구가 개방될 때 시약의 최초 버스트 (burst) 를 생성하기 위해 약 0.1 내지 5 초의 기간 동안 이루어질 수도 있다. 이는 일 예에서 약 0.1 내지 10 초 동안 개구부 유출구 밸브 (808) 에 의해 달성된다. 그 후, 텅스텐-함유 가스는 적합한 퍼지 가스를 사용하여 증착 챔버로부터 퍼지된다. 다른 시약들의 펄싱된 플로우는 유사한 방식으로 이루어질 수도 있다. 몰리브덴-함유 가스의 펄스가 유사한 방식으로 생성될 수도 있다.

전술한 바는 단일 또는 멀티-챔버 반도체 프로세싱 툴의 개시된 실시예들의 구현예를 기술한다. 본 명세서에 기술된 장치 및 프로세스는 예를 들어, 반도체 디바이스들, 디스플레이들, LED들, 광전 패널들 등의 제조 또는 제작을 위해 리소그래픽 패터닝 툴들 또는 프로세스들과 함께 사용될 수도 있다. 통상적으로, 반드시 그러한 것은 아니지만, 이러한 툴들/프로세스들은 공통 제조 설비에서 함께 사용되거나 수행될 것이다. 막의 리소그래픽 패터닝은 통상적으로 단계 각각이 다수의 가능한 툴들과 함께 제공된, 이하의 단계들: (1) 스핀온 (spin-on) 툴 또는 스프레이온 (spray-on) 툴을 사용하여 워크피스, 즉, 기판 상에 포토레지스트를 도포하는 단계; (2) 핫 플레이트 또는 노 또는 UV 경화 툴을 사용하여 포토레지스트를 경화하는 단계; (3) 웨이퍼 스텝퍼와 같은 툴을 사용하여 가시광선 또는 UV 또는 x-선 광에 포토레지스트를 노출시키는 단계; (4) 습식 벤치와 같은 툴을 사용하여 레지스트를 선택적으로 제거하여 레지스트를 패터닝하도록 레지스트를 현상하는 단계; (5) 건식 또는 플라즈마 보조 에칭 툴을 사용함으로써 아래에 놓인 막 또는 워크피스 내로 레지스트 패턴을 전사하는 단계; 및 (6) RF 또는 마이크로파 플라즈마 레지스트 스트립퍼와 같은 툴을 사용하여 레지스트를 제거하는 단계 중 일부 또는 전부를 포함한다.

결론

전술한 실시예들이 이해의 명확성의 목적들을 위해 다소 상세히 기술되었지만, 특정한 변화들 및 수정들이 첨부된 청구항들의 범위 내에서 실시될 수도 있다는 것이 자명할 것이다. 본 실시예들의 프로세스들, 시스템들, 및 장치를 구현하는 많은 대안적인 방식들이 있다는 것에 유의해야 한다. 이에 따라, 본 실시예들은 예시적이고, 제한적이지 않은 것으로 간주될 것이며, 실시예들은 본 명세서에 주어진 세부사항들로 한정되지 않을 것이다.

Claims (38)

- 금속-함유 재료로 충진될 구조체를 제공하는 단계;

상기 구조체를 복수의 증착 사이클들에 노출하는 단계를 포함하고, 증착 사이클 각각은,

복수의 교번하는 수소 (H2) 펄스들 및 불활성 가스 퍼지 펄스들로의 노출로서, 상기 복수의 교번하는 수소 (H2) 펄스들 및 불활성 가스 퍼지 펄스들은 금속 전구체 펄스를 개입시키지 않고 수행되는, 노출; 및

금속 전구체 펄스에 이어 불활성 가스 퍼지 펄스로의 노출을 포함하는, 방법. - 제 1 항에 있어서,

상기 금속은 텅스텐 (W) 또는 몰리브덴 (Mo) 인, 방법. - 제 1 항에 있어서,

상기 금속 전구체는 염소-함유 금속 전구체인, 방법. - 제 3 항에 있어서,

상기 염소-함유 금속 전구체는 텅스텐 클로라이드 또는 텅스텐 옥시클로라이드를 포함하는, 방법. - 제 3 항에 있어서,

상기 염소-함유 금속 전구체는 몰리브덴 클로라이드 또는 몰리브덴 옥시클로라이드를 포함하는, 방법. - 제 3 항에 있어서,

염소-함유 금속 전구체는 WCl5, WCl6, MoCl5, MoO2Cl2, 및 MoOCl4 중 적어도 하나를 포함하는, 방법. - 제 3 항에 있어서,

상기 염소-함유 금속 전구체의 펄스는 체적으로 0.1 % 내지 1.5 %의 염소-함유 텅스텐 금속 전구체를 포함하는, 방법. - 제 1 항에 있어서,

상기 복수의 교번하는 H2 펄스들 및 불활성 가스 퍼지 펄스들로의 노출은 상기 H2 펄스들 동안 상기 불활성 가스 퍼지 플로우를 턴오프하는 것을 포함하는, 방법. - 제 1 항에 있어서,

상기 불활성 가스 퍼지 펄스의 지속기간은 상기 H2 펄스들의 지속기간의 적어도 1.5 배인, 방법. - 제 1 항에 있어서,

증착 사이클 각각은 금속 전구체 펄스를 개입시키지 않고 적어도 5 개의 교번하는 H2 펄스들 및 불활성 가스 퍼지 펄스들을 포함하는, 방법. - 제 1 항에 있어서,

증착 사이클 각각은 금속 전구체 펄스를 개입시키지 않고 적어도 10 개의 교번하는 금속 전구체 펄스들 및 불활성 가스 퍼지 펄스들을 포함하는, 방법. - 제 1 항에 있어서,

증착 사이클 각각은 단일 금속 전구체 펄스만을 포함하는, 방법. - 제 1 항에 있어서,

증착 사이클 각각은 수소 (H2) 펄스를 개입시키지 않고 복수의 교번하는 금속 전구체 펄스들 및 불활성 가스 퍼지 펄스들을 포함하는, 방법. - 제 1 항에 있어서,

상기 구조체는 측벽들 및 개구부들을 통해 유체적으로 액세스가능한 복수의 내부 영역들을 갖는 복수의 피처들로 이어지는 상기 측벽들의 상기 복수의 개구부들을 포함하는 부분적으로 제조된 3차원 (3-D) NAND 구조체인, 방법. - 각각 기판을 홀딩하도록 구성된 하나 이상의 프로세스 챔버들;

수소 (H2) 가스 소스, 금속 전구체 가스 소스, 및 불활성 퍼지 가스 소스에 커플링하기 위한 하나 이상의 프로세스 가스 유입구들; 및

복수의 증착 사이클들을 수행하기 위한 머신-판독가능 인스트럭션들을 포함하는, 장치의 동작들을 제어하기 위한 제어기를 포함하고, 증착 사이클 각각은,

상기 하나 이상의 프로세스 가스 유입구들을 통해 상기 하나 이상의 프로세스 챔버들로 복수의 교번하는 수소 (H2) 펄스들 및 불활성 가스 퍼지 펄스들을 주입하는 단계로서, 상기 복수의 교번하는 수소 (H2) 펄스들 및 불활성 가스 퍼지 펄스들은 금속 전구체 펄스를 개입시키지 않고 수행되는, 상기 복수의 교번하는 수소 (H2) 펄스들 및 불활성 가스 퍼지 펄스들을 주입하는 단계;

상기 하나 이상의 프로세스 가스 유입구들을 통해 상기 하나 이상의 프로세스 챔버들로 금속 전구체 펄스를 주입하는 단계; 및

상기 하나 이상의 프로세스 가스 유입구들을 통해 상기 하나 이상의 프로세스 챔버들로 퍼지 가스 펄스를 주입하는 단계를 포함하는, 장치. - 제 15 항에 있어서,

상기 금속 전구체는 염소-함유 전구체인, 장치. - 제 16 항에 있어서,

상기 금속 전구체는 텅스텐 클로라이드, 텅스텐 옥시클로라이드, 몰리브덴 클로라이드, 및 몰리브덴 옥시클로라이드 중 적어도 하나를 포함하는, 장치. - 금속-함유 재료로 충진될 구조체를 제공하는 단계;

상기 구조체를 복수의 증착 사이클들에 노출하는 단계를 포함하고, 증착 사이클 각각은,

수소 (H2) 펄스로의 노출에 이어 불활성 가스 퍼지 펄스로의 노출; 및

복수의 교번하는 금속 전구체 펄스들 및 불활성 가스 퍼지 펄스들로의 노출을 포함하고,

상기 복수의 교번하는 금속 전구체 펄스들 및 불활성 가스 퍼지 펄스들은 수소 (H2) 펄스를 개입시키지 않고 수행되는, 방법. - 제 18 항에 있어서,

상기 금속은 텅스텐 (W) 또는 몰리브덴 (Mo) 인, 방법. - 제 18 항에 있어서,

상기 금속 전구체는 염소-함유 금속 전구체인, 방법. - 제 20 항에 있어서,

상기 염소-함유 금속 전구체는 텅스텐 클로라이드 또는 텅스텐 옥시클로라이드를 포함하는, 방법. - 제 21 항에 있어서,

상기 염소-함유 금속 전구체는 WCl5 및 WCl6 중 적어도 하나를 포함하는, 방법. - 제 20 항에 있어서,

상기 염소-함유 금속 전구체는 몰리브덴 클로라이드 또는 몰리브덴 옥시클로라이드를 포함하는, 방법. - 제 23 항에 있어서,

염소-함유 금속 전구체는 MoCl5, MoO2Cl2, 및 MoOCl4 중 적어도 하나를 포함하는, 방법. - 제 20 항에 있어서,

상기 염소-함유 금속 전구체의 펄스는 체적으로 0.1 % 내지 1.5 %의 염소-함유 텅스텐 전구체를 포함하는, 방법. - 제 18 항에 있어서,

상기 복수의 교번하는 금속 전구체 펄스들 및 불활성 가스 퍼지 펄스들로의 노출은 상기 금속 전구체 펄스들 동안 상기 불활성 가스 퍼지 플로우를 턴오프하는 것을 포함하는, 방법. - 제 18 항에 있어서,

상기 불활성 가스 퍼지 펄스의 지속기간은 상기 금속 전구체 펄스들의 지속기간의 적어도 1.5 배인, 방법. - 제 18 항에 있어서,

증착 사이클 각각은 수소 (H2) 펄스를 개입시키지 않고 적어도 5 개의 교번하는 금속 전구체 펄스들 및 불활성 가스 퍼지 펄스들을 포함하는, 방법. - 제 18 항에 있어서,

증착 사이클 각각은 수소 (H2) 펄스를 개입시키지 않고 적어도 10 개의 교번하는 금속 전구체 펄스들 및 불활성 가스 퍼지 펄스들을 포함하는, 방법. - 제 18 항에 있어서,

증착 사이클 각각은 단일 H2 펄스만을 포함하는, 방법. - 제 18 항에 있어서,

증착 사이클 각각은 금속 전구체 펄스를 개입시키지 않고 복수의 교번하는 H2 펄스들 및 불활성 가스 퍼지 펄스들을 포함하는, 방법. - 제 18 항에 있어서,

상기 구조체는 측벽들 및 개구부들을 통해 유체적으로 액세스가능한 복수의 내부 영역들을 갖는 복수의 피처들로 이어지는 상기 측벽들의 상기 복수의 개구부들을 포함하는 부분적으로 제조된 3차원 (3-D) NAND 구조체인, 방법. - 각각 기판을 홀딩하도록 구성된 하나 이상의 프로세스 챔버들;

수소 (H2) 가스 소스, 금속 전구체 가스 소스, 및 불활성 퍼지 가스 소스에 커플링하기 위한 하나 이상의 프로세스 가스 유입구들; 및

복수의 증착 사이클들을 수행하기 위한 머신-판독가능 인스트럭션들을 포함하는, 장치의 동작들을 제어하기 위한 제어기를 포함하고, 증착 사이클 각각은,

상기 하나 이상의 프로세스 가스 유입구들을 통해 상기 하나 이상의 프로세스 챔버들로 수소 (H2) 펄스를 주입하는 단계;

상기 H2 펄스를 주입한 후, 상기 하나 이상의 프로세스 가스 유입구들을 통해 상기 하나 이상의 프로세스 챔버로 불활성 퍼지 가스 펄스를 주입하는 단계;

상기 불활성 퍼지 가스 펄스를 주입한 후, 상기 하나 이상의 프로세스 가스 유입구들을 통해 상기 하나 이상의 프로세스 챔버들로 복수의 교번하는 금속 전구체 펄스들 및 불활성 가스 퍼지 펄스들을 주입하는 단계를 포함하고,

상기 복수의 교번하는 금속 전구체 펄스들 및 불활성 가스 퍼지 펄스들은 수소 (H2) 펄스를 개입시키지 않고 수행되는, 장치. - 제 33 항에 있어서,

상기 금속 전구체는 염소-함유 전구체인, 장치. - 제 34 항에 있어서,

상기 금속 전구체는 텅스텐 클로라이드, 텅스텐 옥시클로라이드, 몰리브덴 클로라이드, 및 몰리브덴 옥시클로라이드 중 적어도 하나를 포함하는, 장치. - 제 33 항에 있어서,

상기 인스트럭션들은 상기 금속 전구체 펄스들 동안 상기 불활성 가스 퍼지 플로우를 턴 오프하기 위한 인스트럭션들을 포함하는, 장치. - 제 33 항에 있어서,

상기 불활성 가스 퍼지 펄스들의 지속기간은 상기 금속 전구체 펄스들의 지속기간의 적어도 1.5 배인, 장치. - 제 33 항에 있어서,

증착 사이클 각각은 수소 (H2) 펄스를 개입시키지 않고 적어도 5 개의 교번하는 금속 전구체 펄스들 및 불활성 가스 퍼지 펄스들을 포함하는, 장치.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201862666588P | 2018-05-03 | 2018-05-03 | |

| US62/666,588 | 2018-05-03 | ||

| PCT/US2019/030712WO2019213604A1 (en) | 2018-05-03 | 2019-05-03 | Method of depositing tungsten and other metals in 3d nand structures |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20200140391A KR20200140391A (ko) | 2020-12-15 |

| KR102806630B1true KR102806630B1 (ko) | 2025-05-12 |

Family

ID=68386126

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020207034800AActiveKR102806630B1 (ko) | 2018-05-03 | 2019-05-03 | 3d nand 구조체들에 텅스텐 및 다른 금속들을 증착하는 방법 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US11549175B2 (ko) |

| JP (2) | JP2021523292A (ko) |

| KR (1) | KR102806630B1 (ko) |

| CN (1) | CN112262457A (ko) |

| WO (1) | WO2019213604A1 (ko) |

Families Citing this family (250)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20130023129A1 (en) | 2011-07-20 | 2013-01-24 | Asm America, Inc. | Pressure transmitter for a semiconductor processing environment |

| US20160376700A1 (en) | 2013-02-01 | 2016-12-29 | Asm Ip Holding B.V. | System for treatment of deposition reactor |

| US10941490B2 (en) | 2014-10-07 | 2021-03-09 | Asm Ip Holding B.V. | Multiple temperature range susceptor, assembly, reactor and system including the susceptor, and methods of using the same |

| US10276355B2 (en) | 2015-03-12 | 2019-04-30 | Asm Ip Holding B.V. | Multi-zone reactor, system including the reactor, and method of using the same |

| US11139308B2 (en) | 2015-12-29 | 2021-10-05 | Asm Ip Holding B.V. | Atomic layer deposition of III-V compounds to form V-NAND devices |

| US10529554B2 (en) | 2016-02-19 | 2020-01-07 | Asm Ip Holding B.V. | Method for forming silicon nitride film selectively on sidewalls or flat surfaces of trenches |

| US10343920B2 (en) | 2016-03-18 | 2019-07-09 | Asm Ip Holding B.V. | Aligned carbon nanotubes |

| US11453943B2 (en) | 2016-05-25 | 2022-09-27 | Asm Ip Holding B.V. | Method for forming carbon-containing silicon/metal oxide or nitride film by ALD using silicon precursor and hydrocarbon precursor |

| US10612137B2 (en) | 2016-07-08 | 2020-04-07 | Asm Ip Holdings B.V. | Organic reactants for atomic layer deposition |

| US9859151B1 (en) | 2016-07-08 | 2018-01-02 | Asm Ip Holding B.V. | Selective film deposition method to form air gaps |

| US9887082B1 (en) | 2016-07-28 | 2018-02-06 | Asm Ip Holding B.V. | Method and apparatus for filling a gap |

| US9812320B1 (en) | 2016-07-28 | 2017-11-07 | Asm Ip Holding B.V. | Method and apparatus for filling a gap |

| US10573522B2 (en) | 2016-08-16 | 2020-02-25 | Lam Research Corporation | Method for preventing line bending during metal fill process |

| US11532757B2 (en) | 2016-10-27 | 2022-12-20 | Asm Ip Holding B.V. | Deposition of charge trapping layers |

| US10714350B2 (en) | 2016-11-01 | 2020-07-14 | ASM IP Holdings, B.V. | Methods for forming a transition metal niobium nitride film on a substrate by atomic layer deposition and related semiconductor device structures |

| KR102546317B1 (ko) | 2016-11-15 | 2023-06-21 | 에이에스엠 아이피 홀딩 비.브이. | 기체 공급 유닛 및 이를 포함하는 기판 처리 장치 |

| US11581186B2 (en) | 2016-12-15 | 2023-02-14 | Asm Ip Holding B.V. | Sequential infiltration synthesis apparatus |

| US11447861B2 (en) | 2016-12-15 | 2022-09-20 | Asm Ip Holding B.V. | Sequential infiltration synthesis apparatus and a method of forming a patterned structure |

| US11390950B2 (en) | 2017-01-10 | 2022-07-19 | Asm Ip Holding B.V. | Reactor system and method to reduce residue buildup during a film deposition process |

| US10468261B2 (en) | 2017-02-15 | 2019-11-05 | Asm Ip Holding B.V. | Methods for forming a metallic film on a substrate by cyclical deposition and related semiconductor device structures |

| US10770286B2 (en) | 2017-05-08 | 2020-09-08 | Asm Ip Holdings B.V. | Methods for selectively forming a silicon nitride film on a substrate and related semiconductor device structures |

| US12040200B2 (en) | 2017-06-20 | 2024-07-16 | Asm Ip Holding B.V. | Semiconductor processing apparatus and methods for calibrating a semiconductor processing apparatus |

| US11306395B2 (en) | 2017-06-28 | 2022-04-19 | Asm Ip Holding B.V. | Methods for depositing a transition metal nitride film on a substrate by atomic layer deposition and related deposition apparatus |

| KR20190009245A (ko) | 2017-07-18 | 2019-01-28 | 에이에스엠 아이피 홀딩 비.브이. | 반도체 소자 구조물 형성 방법 및 관련된 반도체 소자 구조물 |

| US11374112B2 (en) | 2017-07-19 | 2022-06-28 | Asm Ip Holding B.V. | Method for depositing a group IV semiconductor and related semiconductor device structures |

| US10590535B2 (en) | 2017-07-26 | 2020-03-17 | Asm Ip Holdings B.V. | Chemical treatment, deposition and/or infiltration apparatus and method for using the same |

| TWI815813B (zh) | 2017-08-04 | 2023-09-21 | 荷蘭商Asm智慧財產控股公司 | 用於分配反應腔內氣體的噴頭總成 |

| US10770336B2 (en) | 2017-08-08 | 2020-09-08 | Asm Ip Holding B.V. | Substrate lift mechanism and reactor including same |

| US10692741B2 (en) | 2017-08-08 | 2020-06-23 | Asm Ip Holdings B.V. | Radiation shield |

| US11769682B2 (en) | 2017-08-09 | 2023-09-26 | Asm Ip Holding B.V. | Storage apparatus for storing cassettes for substrates and processing apparatus equipped therewith |

| WO2019036292A1 (en) | 2017-08-14 | 2019-02-21 | Lam Research Corporation | METHOD FOR METAL CASTING FOR THREE-DIMENSIONAL NAND AND VERTICAL WORDS LINE |

| US11830730B2 (en) | 2017-08-29 | 2023-11-28 | Asm Ip Holding B.V. | Layer forming method and apparatus |

| US11295980B2 (en) | 2017-08-30 | 2022-04-05 | Asm Ip Holding B.V. | Methods for depositing a molybdenum metal film over a dielectric surface of a substrate by a cyclical deposition process and related semiconductor device structures |

| US10658205B2 (en) | 2017-09-28 | 2020-05-19 | Asm Ip Holdings B.V. | Chemical dispensing apparatus and methods for dispensing a chemical to a reaction chamber |

| US10403504B2 (en) | 2017-10-05 | 2019-09-03 | Asm Ip Holding B.V. | Method for selectively depositing a metallic film on a substrate |

| US10923344B2 (en) | 2017-10-30 | 2021-02-16 | Asm Ip Holding B.V. | Methods for forming a semiconductor structure and related semiconductor structures |

| CN111344522B (zh) | 2017-11-27 | 2022-04-12 | 阿斯莫Ip控股公司 | 包括洁净迷你环境的装置 |

| WO2019103613A1 (en) | 2017-11-27 | 2019-05-31 | Asm Ip Holding B.V. | A storage device for storing wafer cassettes for use with a batch furnace |

| US10872771B2 (en) | 2018-01-16 | 2020-12-22 | Asm Ip Holding B. V. | Method for depositing a material film on a substrate within a reaction chamber by a cyclical deposition process and related device structures |

| TWI799494B (zh) | 2018-01-19 | 2023-04-21 | 荷蘭商Asm 智慧財產控股公司 | 沈積方法 |

| KR102695659B1 (ko) | 2018-01-19 | 2024-08-14 | 에이에스엠 아이피 홀딩 비.브이. | 플라즈마 보조 증착에 의해 갭 충진 층을 증착하는 방법 |

| US11081345B2 (en) | 2018-02-06 | 2021-08-03 | Asm Ip Holding B.V. | Method of post-deposition treatment for silicon oxide film |

| WO2019158960A1 (en) | 2018-02-14 | 2019-08-22 | Asm Ip Holding B.V. | A method for depositing a ruthenium-containing film on a substrate by a cyclical deposition process |

| US10896820B2 (en) | 2018-02-14 | 2021-01-19 | Asm Ip Holding B.V. | Method for depositing a ruthenium-containing film on a substrate by a cyclical deposition process |

| US10731249B2 (en) | 2018-02-15 | 2020-08-04 | Asm Ip Holding B.V. | Method of forming a transition metal containing film on a substrate by a cyclical deposition process, a method for supplying a transition metal halide compound to a reaction chamber, and related vapor deposition apparatus |

| KR102636427B1 (ko) | 2018-02-20 | 2024-02-13 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 방법 및 장치 |

| US10975470B2 (en) | 2018-02-23 | 2021-04-13 | Asm Ip Holding B.V. | Apparatus for detecting or monitoring for a chemical precursor in a high temperature environment |

| US11473195B2 (en) | 2018-03-01 | 2022-10-18 | Asm Ip Holding B.V. | Semiconductor processing apparatus and a method for processing a substrate |

| KR102646467B1 (ko) | 2018-03-27 | 2024-03-11 | 에이에스엠 아이피 홀딩 비.브이. | 기판 상에 전극을 형성하는 방법 및 전극을 포함하는 반도체 소자 구조 |

| KR102600229B1 (ko) | 2018-04-09 | 2023-11-10 | 에이에스엠 아이피 홀딩 비.브이. | 기판 지지 장치, 이를 포함하는 기판 처리 장치 및 기판 처리 방법 |