KR102669279B1 - Semiconductor device and method for manufacturing same - Google Patents

Semiconductor device and method for manufacturing sameDownload PDFInfo

- Publication number

- KR102669279B1 KR102669279B1KR1020177019786AKR20177019786AKR102669279B1KR 102669279 B1KR102669279 B1KR 102669279B1KR 1020177019786 AKR1020177019786 AKR 1020177019786AKR 20177019786 AKR20177019786 AKR 20177019786AKR 102669279 B1KR102669279 B1KR 102669279B1

- Authority

- KR

- South Korea

- Prior art keywords

- layer

- oxide semiconductor

- insulating layer

- film

- semiconductor layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/62—Fin field-effect transistors [FinFET]

- H10D30/6212—Fin field-effect transistors [FinFET] having fin-shaped semiconductor bodies having non-rectangular cross-sections

- H10D30/6213—Fin field-effect transistors [FinFET] having fin-shaped semiconductor bodies having non-rectangular cross-sections having rounded corners

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

- H01L29/7869—

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02172—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing at least one metal element, e.g. metal oxides, metal nitrides, metal oxynitrides or metal carbides

- H01L21/02175—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing at least one metal element, e.g. metal oxides, metal nitrides, metal oxynitrides or metal carbides characterised by the metal

- H01L21/02178—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing at least one metal element, e.g. metal oxides, metal nitrides, metal oxynitrides or metal carbides characterised by the metal the material containing aluminium, e.g. Al2O3

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/0226—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process

- H01L21/02263—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase

- H01L21/02266—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by physical ablation of a target, e.g. sputtering, reactive sputtering, physical vapour deposition or pulsed laser deposition

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/285—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation

- H01L21/28506—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers

- H01L21/28512—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table

- H01L21/2855—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table by physical means, e.g. sputtering, evaporation

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/324—Thermal treatment for modifying the properties of semiconductor bodies, e.g. annealing, sintering

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/34—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies not provided for in groups H01L21/18, H10D48/04 and H10D48/07, with or without impurities, e.g. doping materials

- H01L21/38—Diffusion of impurity materials, e.g. doping materials, electrode materials, into or out of a semiconductor body, or between semiconductor regions

- H01L21/385—Diffusion of impurity materials, e.g. doping materials, electrode materials, into or out of a semiconductor body, or between semiconductor regions using diffusion into or out of a solid from or into a solid phase, e.g. a doped oxide layer

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/29—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the material, e.g. carbon

- H01L23/291—Oxides or nitrides or carbides, e.g. ceramics, glass

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/31—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape

- H01L23/3157—Partial encapsulation or coating

- H01L23/3171—Partial encapsulation or coating the coating being directly applied to the semiconductor body, e.g. passivation layer

- H01L29/78618—

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6755—Oxide semiconductors, e.g. zinc oxide, copper aluminium oxide or cadmium stannate

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6757—Thin-film transistors [TFT] characterised by the structure of the channel, e.g. transverse or longitudinal shape or doping profile

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/80—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0165—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs the components including complementary IGFETs, e.g. CMOS devices

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/02—Manufacture or treatment characterised by using material-based technologies

- H10D84/03—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology

- H10D84/038—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology using silicon technology, e.g. SiGe

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/80—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs

- H10D84/82—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs of only field-effect components

- H10D84/83—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs of only field-effect components of only insulated-gate FETs [IGFET]

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/80—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs

- H10D84/82—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs of only field-effect components

- H10D84/83—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs of only field-effect components of only insulated-gate FETs [IGFET]

- H10D84/85—Complementary IGFETs, e.g. CMOS

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/421—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer

- H10D86/423—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer comprising semiconductor materials not belonging to the Group IV, e.g. InGaZnO

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/481—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs integrated with passive devices, e.g. auxiliary capacitors

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D99/00—Subject matter not provided for in other groups of this subclass

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/10—Integrated devices

- H10F39/12—Image sensors

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Ceramic Engineering (AREA)

- Optics & Photonics (AREA)

- Thin Film Transistor (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Semiconductor Memories (AREA)

- Electroluminescent Light Sources (AREA)

- Non-Volatile Memory (AREA)

- Solid State Image Pick-Up Elements (AREA)

Abstract

Translated fromKoreanDescription

Translated fromKorean본 발명은, 물건, 방법, 또는 제조 방법에 관한 것이다. 또는, 본 발명은 공정(process), 기계(machine), 제품(manufacture), 또는 조성물(composition of matter)에 관한 것이다. 특히, 본 발명은, 예를 들어, 반도체 장치, 표시 장치, 발광 장치, 축전 장치, 촬상 장치, 그들의 구동 방법, 또는 그들의 제조 방법에 관한 것이다. 특히, 본 발명의 일 형태는, 반도체 장치 또는 그 제작 방법에 관한 것이다.The present invention relates to an article, method, or manufacturing method. Alternatively, the invention relates to a process, machine, manufacture, or composition of matter. In particular, the present invention relates to, for example, semiconductor devices, display devices, light-emitting devices, power storage devices, imaging devices, methods of driving them, or methods of manufacturing them. In particular, one aspect of the present invention relates to a semiconductor device or a manufacturing method thereof.

또한, 본 명세서 등에 있어서 반도체 장치란, 반도체 특성을 이용함으로써 기능할 수 있는 장치 전반을 가리킨다. 트랜지스터, 반도체 회로는 반도체 장치의 일 형태이다. 또한, 기억 장치, 표시 장치, 전자 기기는, 반도체 장치를 가지는 경우가 있다.In addition, in this specification and the like, a semiconductor device refers to a general device that can function by utilizing semiconductor characteristics. A transistor or semiconductor circuit is a type of semiconductor device. Additionally, memory devices, display devices, and electronic devices sometimes include semiconductor devices.

절연 표면을 가지는 기판 위에 형성된 반도체막을 사용하여 트랜지스터를 구성하는 기술이 주목되고 있다. 당해 트랜지스터는 집적 회로(IC)나 화상 표시 장치(표시 장치)와 같은 전자 디바이스에 널리 응용되고 있다. 트랜지스터에 적용 가능한 반도체 박막으로서 실리콘계 반도체 재료가 널리 알려져 있지만, 그 외의 재료로서 산화물 반도체가 주목되고 있다.Technology for constructing a transistor using a semiconductor film formed on a substrate with an insulating surface is attracting attention. The transistor is widely applied to electronic devices such as integrated circuits (ICs) and image display devices (display devices). Silicon-based semiconductor materials are widely known as semiconductor thin films applicable to transistors, but oxide semiconductors are attracting attention as other materials.

예를 들어, 트랜지스터의 활성층으로서, 인듐(In), 갈륨(Ga), 및 아연(Zn)을 포함하는 비정질 산화물 반도체를 사용한 트랜지스터가 특허문헌 1에 개시(開示)되어 있다.For example,

반도체 소자를 미세화하는 데 있어서, 트랜지스터 근방의 기생 용량이 큰 문제가 된다.In miniaturizing semiconductor devices, parasitic capacitance near transistors becomes a major problem.

트랜지스터의 동작에 있어서, 채널 근방(예를 들어, 소스 전극-드레인 전극 간)에 기생 용량이 존재하는 경우, 기생 용량의 충전에 요하는 시간이 필요하게 되어, 트랜지스터의 응답성, 나아가서는 반도체 장치의 응답성을 저하시킨다.In the operation of a transistor, when a parasitic capacitance exists near the channel (for example, between the source electrode and the drain electrode), time is required to charge the parasitic capacitance, which affects the responsiveness of the transistor and, by extension, the semiconductor device. Decreases responsiveness.

또한, 트랜지스터를 형성하는 각종 공정(특히 성막, 가공 등)은, 미세화가 진행될수록 그 제어성은 어려움이 늘어나고 있으며, 제조 공정에 기인한 편차가, 트랜지스터 특성, 나아가서는 신뢰성에 큰 영향을 미친다.In addition, the controllability of various processes for forming transistors (particularly film formation, processing, etc.) becomes increasingly difficult as miniaturization progresses, and deviations due to the manufacturing process have a significant impact on transistor characteristics and, by extension, reliability.

또한, 미세화에 수반하여 노광 장치의 해상 한계 때문에 패턴 형성이 어려워지는 등, 트랜지스터 제조상의 문제도 나타나고 있고, 설비 투자에 따른 비용도 막대해지고 있다.In addition, with miniaturization, problems in transistor manufacturing are appearing, such as pattern formation becoming difficult due to the resolution limit of exposure equipment, and the cost of facility investment is also becoming enormous.

따라서, 본 발명의 일 형태는, 트랜지스터 근방의 기생 용량을 저감하는 것을 목적 중 하나로 한다. 또는, 전기 특성이 양호한 반도체 장치를 제공하는 것을 목적 중 하나로 한다. 또는, 신뢰성이 높은 반도체 장치를 제공하는 것을 목적 중 하나로 한다. 또는, 노광 장치의 해상 한계 이하의 패턴 형성이 가능한 트랜지스터, 또는 반도체 장치의 제조 방법을 제공하는 것을 목적 중 하나로 한다. 또는, 트랜지스터 또는 반도체 장치의, 제조 공정에 기인한 특성의 편차를 저감하는 것을 목적 중 하나로 한다. 또는, 산소 결손이 적은 산화물 반도체층을 가지는 반도체 장치를 제공하는 것을 목적 중 하나로 한다. 또는, 간단한 공정으로 형성할 수 있는 반도체 장치를 제공하는 것을 목적 중 하나로 한다. 또는, 산화물 반도체층 근방의 계면 준위를 저감할 수 있는 구성의 반도체 장치를 제공하는 것을 목적 중 하나로 한다. 또는, 저소비전력의 반도체 장치를 제공하는 것을 목적 중 하나로 한다. 또한, 개발 비용을 억제한 신규 반도체 장치의 제조법을 제공하는 것을 목적 중 하나로 한다. 또는, 신규 반도체 장치 등을 제공하는 것을 목적 중 하나로 한다. 또는 상기 반도체 장치의 제작 방법을 제공하는 것을 목적 중 하나로 한다.Accordingly, one of the purposes of one embodiment of the present invention is to reduce parasitic capacitance near the transistor. Alternatively, one of the purposes is to provide a semiconductor device with good electrical characteristics. Alternatively, one of the purposes is to provide a highly reliable semiconductor device. Alternatively, one of the purposes is to provide a method for manufacturing a transistor or semiconductor device capable of forming a pattern below the resolution limit of an exposure apparatus. Alternatively, one of the purposes is to reduce variation in the characteristics of transistors or semiconductor devices due to the manufacturing process. Alternatively, one of the purposes is to provide a semiconductor device having an oxide semiconductor layer with few oxygen vacancies. Alternatively, one of the purposes is to provide a semiconductor device that can be formed through a simple process. Alternatively, one of the purposes is to provide a semiconductor device configured to reduce the interface level near the oxide semiconductor layer. Alternatively, one of the purposes is to provide a semiconductor device with low power consumption. Additionally, one of the purposes is to provide a manufacturing method for a new semiconductor device that reduces development costs. Alternatively, one of the purposes is to provide new semiconductor devices, etc. Alternatively, one of the purposes is to provide a method for manufacturing the semiconductor device.

또한, 이들 과제의 기재는, 다른 과제의 존재를 방해하는 것은 아니다. 또한, 본 발명의 일 형태는, 이들 과제의 모두를 해결할 필요는 없는 것으로 한다. 또한, 이들 이외의 과제는, 명세서, 도면, 청구항 등의 기재로부터 저절로 명백해질 것이며, 명세서, 도면, 청구항 등의 기재로부터, 이들 이외의 과제를 추출하는 것이 가능하다.Additionally, the description of these problems does not prevent the existence of other problems. Additionally, one embodiment of the present invention does not necessarily solve all of these problems. Additionally, issues other than these will naturally become clear from descriptions in the specification, drawings, claims, etc., and it is possible to extract issues other than these from descriptions in the specification, drawings, claims, etc.

본 발명의 일 형태는, 제 1 절연층과, 제 1 절연층 위의 제 1 산화물 반도체층과, 제 1 산화물 반도체층 위의 제 2 산화물 반도체층과, 제 2 산화물 반도체층 위의 소스 전극층 및 드레인 전극층과, 제 1 절연층, 소스 전극층, 및 드레인 전극층 위의 제 2 절연층과, 제 2 절연층 위의 제 3 절연층과, 제 2 산화물 반도체층 위의 제 3 산화물 반도체층과, 제 3 산화물 반도체층 위의 게이트 절연층과, 게이트 절연층 위의 게이트 전극층을 가지고, 제 2 절연층은, 산소 배리어층이며, 제 1 산화물 반도체층, 제 2 산화물 반도체층, 소스 전극층 및 드레인 전극층의 측면과 접촉하는 영역을 가지고, 제 3 산화물 반도체층은, 제 2 산화물 반도체층, 소스 전극층, 드레인 전극층, 제 2 절연층, 및 제 3 절연층의 측면과 접촉하는 영역을 가지는 것을 특징으로 하는 반도체 장치이다.One form of the present invention includes a first insulating layer, a first oxide semiconductor layer on the first insulating layer, a second oxide semiconductor layer on the first oxide semiconductor layer, a source electrode layer on the second oxide semiconductor layer, and A drain electrode layer, a first insulating layer, a source electrode layer, and a second insulating layer on the drain electrode layer, a third insulating layer on the second insulating layer, a third oxide semiconductor layer on the second oxide semiconductor layer, and a third insulating layer on the second oxide semiconductor layer. 3. It has a gate insulating layer on the oxide semiconductor layer, a gate electrode layer on the gate insulating layer, the second insulating layer is an oxygen barrier layer, and the first oxide semiconductor layer, the second oxide semiconductor layer, the source electrode layer, and the drain electrode layer. A semiconductor having a region in contact with the side surface, wherein the third oxide semiconductor layer has a region in contact with the side surface of the second oxide semiconductor layer, the source electrode layer, the drain electrode layer, the second insulating layer, and the third insulating layer. It is a device.

본 발명의 다른 일 형태는, 제 1 절연층과, 제 1 절연층 위의 제 1 산화물 반도체층과, 제 1 산화물 반도체층 위의 제 2 산화물 반도체층과, 제 2 산화물 반도체층 위의 소스 전극층 및 드레인 전극층과, 제 2 산화물 반도체층의 측면과 접촉하는 영역을 가지는 제 1 도전층 및 제 2 도전층과, 제 1 절연층, 소스 전극층, 및 드레인 전극층 위의 제 2 절연층과, 제 2 절연층 위의 제 3 절연층과, 제 2 산화물 반도체층 위의 제 3 산화물 반도체층과, 제 3 산화물 반도체층 위의 게이트 절연층과, 게이트 절연층 위의 게이트 전극층을 가지고, 제 2 절연층은, 산소 배리어층이며, 제 1 전극층 및 제 2 전극층은, 측면부에 있어서 제 2 절연층과 접촉하고, 제 3 산화물 반도체층은, 제 1 절연층, 제 1 산화물 반도체층, 제 2 산화물 반도체층, 소스 전극층, 드레인 전극층, 제 2 절연층, 및 제 3 절연층의 측면부에 접촉하는 영역을 가지는 것을 특징으로 하는 반도체 장치이다.Another aspect of the present invention includes a first insulating layer, a first oxide semiconductor layer on the first insulating layer, a second oxide semiconductor layer on the first oxide semiconductor layer, and a source electrode layer on the second oxide semiconductor layer. and a drain electrode layer, a first conductive layer and a second conductive layer having a region in contact with a side surface of the second oxide semiconductor layer, a second insulating layer on the first insulating layer, the source electrode layer, and the drain electrode layer, and a second A third insulating layer on the insulating layer, a third oxide semiconductor layer on the second oxide semiconductor layer, a gate insulating layer on the third oxide semiconductor layer, and a gate electrode layer on the gate insulating layer, the second insulating layer is an oxygen barrier layer, the first electrode layer and the second electrode layer are in contact with the second insulating layer at the side surface, and the third oxide semiconductor layer is a first insulating layer, a first oxide semiconductor layer, and a second oxide semiconductor layer. A semiconductor device characterized by having regions in contact with side surfaces of a source electrode layer, a drain electrode layer, a second insulating layer, and a third insulating layer.

본 발명의 다른 일 형태는, 제 1 절연층과, 제 1 절연층 위의 제 1 산화물 반도체층과, 제 1 산화물 반도체층 위의 제 2 산화물 반도체층과, 제 2 산화물 반도체층 위의 소스 전극층 및 드레인 전극층과, 제 1 절연층, 소스 전극층, 및 드레인 전극층 위의 제 2 절연층과, 제 2 절연층 위의 제 3 절연층과, 소스 전극층 및 드레인 전극층 위에 있고, 또한 제 2 절연층, 및 제 3 절연층의 측면에 접촉하도록 형성된 제 4 절연층과, 제 2 산화물 반도체층 위의 제 3 산화물 반도체층과, 제 3 산화물 반도체층 위의 게이트 절연층과, 게이트 절연층 위의 게이트 전극층을 가지고, 제 2 절연층은, 산소 배리어층이며, 제 1 산화물 반도체층, 제 2 산화물 반도체층, 소스 전극층, 및 드레인 전극층의 측면과 접촉하는 영역을 가지고, 제 3 산화물 반도체층은, 제 1 절연층, 제 1 산화물 반도체층, 제 2 산화물 반도체층, 소스 전극층, 드레인 전극층, 및 제 4 절연층의 측면에 접촉하는 영역을 가지는 것을 특징으로 하는 반도체 장치이다.Another aspect of the present invention includes a first insulating layer, a first oxide semiconductor layer on the first insulating layer, a second oxide semiconductor layer on the first oxide semiconductor layer, and a source electrode layer on the second oxide semiconductor layer. and a drain electrode layer, a second insulating layer on the first insulating layer, the source electrode layer, and the drain electrode layer, a third insulating layer on the second insulating layer, and a second insulating layer on the source electrode layer and the drain electrode layer, and a fourth insulating layer formed to contact the side surface of the third insulating layer, a third oxide semiconductor layer on the second oxide semiconductor layer, a gate insulating layer on the third oxide semiconductor layer, and a gate electrode layer on the gate insulating layer. The second insulating layer is an oxygen barrier layer and has a region in contact with the side surfaces of the first oxide semiconductor layer, the second oxide semiconductor layer, the source electrode layer, and the drain electrode layer, and the third oxide semiconductor layer has a first oxide semiconductor layer. A semiconductor device characterized by having regions in contact with side surfaces of an insulating layer, a first oxide semiconductor layer, a second oxide semiconductor layer, a source electrode layer, a drain electrode layer, and a fourth insulating layer.

또한, 제 2 절연층으로서, 산화 알루미늄층을 사용하는 것이 바람직하다.Additionally, as the second insulating layer, it is preferable to use an aluminum oxide layer.

본 발명의 다른 일 형태는, 제 1 도전층과, 제 1 도전층 위의 제 1 절연층과, 제 1 절연층 위의 제 1 산화물 반도체층과, 제 1 산화물 반도체층 위의 제 2 산화물 반도체층과, 제 2 산화물 반도체층 위의 소스 전극층 및 드레인 전극층과, 제 1 절연층, 소스 전극층, 및 드레인 전극층 위의 제 2 절연층과, 제 2 절연층 위의 제 3 절연층과, 제 2 산화물 반도체층 위의 제 3 산화물 반도체층과, 제 3 산화물 반도체층 위의 게이트 절연층과, 게이트 절연층 위의 게이트 전극층과, 제 3 절연층, 제 3 산화물 반도체층, 게이트 절연층, 및 게이트 전극층 위의 제 4 절연층을 가지고, 제 2 절연층은, 산소 배리어층이며, 제 1 산화물 반도체층, 제 2 산화물 반도체층, 소스 전극층, 및 드레인 전극층의 측면부와 접촉하고, 제 3 산화물 반도체층은, 제 1 절연층, 제 1 산화물 반도체층, 제 2 산화물 반도체층, 소스 전극층, 드레인 전극층, 제 2 절연층, 제 3 절연층의 측면부 측면에 접촉하는 영역을 가지고, 제 4 절연층은, 산소 배리어층인 것을 특징으로 하는 반도체 장치이다.Another aspect of the present invention includes a first conductive layer, a first insulating layer on the first conductive layer, a first oxide semiconductor layer on the first insulating layer, and a second oxide semiconductor layer on the first oxide semiconductor layer. a layer, a source electrode layer and a drain electrode layer on the second oxide semiconductor layer, a second insulating layer on the first insulating layer, the source electrode layer, and the drain electrode layer, a third insulating layer on the second insulating layer, and a second insulating layer. A third oxide semiconductor layer on the oxide semiconductor layer, a gate insulating layer on the third oxide semiconductor layer, a gate electrode layer on the gate insulating layer, a third insulating layer, a third oxide semiconductor layer, a gate insulating layer, and a gate. It has a fourth insulating layer on the electrode layer, the second insulating layer is an oxygen barrier layer, is in contact with the side surfaces of the first oxide semiconductor layer, the second oxide semiconductor layer, the source electrode layer, and the drain electrode layer, and the third oxide semiconductor layer has a region in contact with the side surfaces of the first insulating layer, the first oxide semiconductor layer, the second oxide semiconductor layer, the source electrode layer, the drain electrode layer, the second insulating layer, and the third insulating layer, and the fourth insulating layer is: It is a semiconductor device characterized by an oxygen barrier layer.

또한, 제 2 절연층 및 제 4 절연층으로서, 산화 알루미늄막을 사용하는 것이 바람직하다.Additionally, it is preferable to use an aluminum oxide film as the second and fourth insulating layers.

본 발명의 다른 일 형태는, 제 1 절연층을 형성하고, 제 1 절연층 위에 제 1 산화물 반도체막을 형성하고, 제 1 산화물 반도체막 위에 제 2 산화물 반도체막을 형성하고, 제 1 가열 처리를 행하고, 제 2 산화물 반도체막 위에 제 1 도전막을 형성하고, 제 1 마스크 및 제 1 도전막을 사용하여, 제 1 산화물 반도체막 및 제 2 산화물 반도체막의 일부를 에칭하는 것에 의하여, 제 1 산화물 반도체층과, 제 2 산화물 반도체층을 섬 형상으로 형성하고, 제 1 절연층 및 제 1 도전막 위에 제 2 절연층을 형성하고, 제 2 절연층 형성 시에, 제 1 절연층과 제 2 절연막의 혼합층을 형성하고, 그와 동시에 혼합층 또는 제 1 절연층 내에 산소를 첨가하고, 제 2 가열 처리를 행하여, 산소를 제 2 산화물 반도체층 내로 확산시키고, 제 2 절연층 위에 제 3 절연막을 형성하고, 제 3 절연층에 평탄화 처리를 행하여 제 3 절연층을 형성하고, 제 2 마스크를 사용하여 제 3 절연층 및 제 2 절연층을 선택적으로 에칭하고, 제 2 마스크 및 제 2 절연층을 사용하여, 제 1 도전막을 선택적으로 에칭하는 것에 의하여, 소스 전극층 및 드레인 전극층을 형성하고, 제 3 절연층 및 제 2 산화물 반도체층 위에 제 3 산화물 반도체막을 형성하고, 제 3 산화물 반도체막 위에 제 4 절연막을 형성하고, 제 4 절연막 위에 제 2 도전막을 형성하고, 제 2 도전막, 제 3 절연막, 및 제 3 산화물 반도체막에 화학적 기계적 연마 처리를 행하는 것에 의하여, 제 3 산화물 반도체층, 게이트 절연층 및 게이트 전극층을 형성하는 것을 특징으로 하는 반도체 장치의 제조 방법이다.In another aspect of the present invention, a first insulating layer is formed, a first oxide semiconductor film is formed on the first insulating layer, a second oxide semiconductor film is formed on the first oxide semiconductor film, and a first heat treatment is performed, By forming a first conductive film on the second oxide semiconductor film and etching a portion of the first oxide semiconductor film and the second oxide semiconductor film using the first mask and the first conductive film, the first oxide semiconductor layer and the second oxide semiconductor film are formed. A bioxide semiconductor layer is formed in an island shape, a second insulating layer is formed on the first insulating layer and the first conductive film, and when forming the second insulating layer, a mixed layer of the first insulating layer and the second insulating film is formed, , At the same time, oxygen is added into the mixed layer or the first insulating layer, a second heat treatment is performed, oxygen is diffused into the second oxide semiconductor layer, and a third insulating film is formed on the second insulating layer, and the third insulating layer A planarization process is performed to form a third insulating layer, the third insulating layer and the second insulating layer are selectively etched using a second mask, and the first conductive film is etched using the second mask and the second insulating layer. By selective etching, a source electrode layer and a drain electrode layer are formed, a third oxide semiconductor film is formed on the third insulating layer and the second oxide semiconductor layer, a fourth insulating film is formed on the third oxide semiconductor film, and a fourth insulating film is formed on the third insulating layer and the second oxide semiconductor layer. Forming a second conductive film on the insulating film, and subjecting the second conductive film, the third insulating film, and the third oxide semiconductor film to a chemical and mechanical polishing treatment, thereby forming a third oxide semiconductor layer, a gate insulating layer, and a gate electrode layer. A manufacturing method of a semiconductor device characterized by this.

본 발명의 다른 일 형태는, 제 1 절연층을 형성하고, 제 1 절연층 위에 제 1 산화물 반도체막을 형성하고, 제 1 산화물 반도체막 위에 제 2 산화물 반도체막을 형성하고, 제 1 가열 처리를 행하고, 제 2 산화물 반도체막 위에 제 1 도전막을 형성하고, 제 1 마스크 및 제 1 도전막을 사용하여 제 1 산화물 반도체막 및 제 2 산화물 반도체막을 선택적으로 에칭하는 것에 의하여, 제 1 산화물 반도체층과, 제 2 산화물 반도체층을 섬 형상으로 형성하고, 제 1 절연층 및 제 1 도전막 위에 제 2 절연막을 형성하고, 제 2 절연막 형성 시에 제 1 절연층과 제 2 절연막의 혼합층을 형성하고, 혼합층 또는 제 1 절연층 내에 산소를 첨가하고, 제 2 가열 처리를 행하여, 산소를 제 2 산화물 반도체층 내로 확산시켜, 제 2 산화물 반도체층 내의 산소 결손을 저감시키고, 제 2 절연막 위에 제 3 절연막을 형성하고, 제 3 절연막에 평탄화 처리를 행하고, 제 2 마스크를 사용하여 제 3 절연막, 및 제 2 절연막의 일부를 에칭하는 것에 의하여 제 3 절연층 및 제 2 절연층을 형성하고, 제 1 도전층, 제 3 절연층 위에 제 4 절연막을 형성하고, 이방성 에칭하는 것에 의하여, 제 2 절연층, 및 제 3 절연층의 측면에 접촉하는 제 4 절연층을 형성하고, 제 4 절연층을 마스크로서 사용하여, 제 1 도전막의 일부를 에칭하는 것에 의하여, 소스 전극 및 드레인 전극을 형성하고, 제 3 절연층 및 제 2 산화물 반도체층 위에 제 3 산화물 반도체막을 형성하고, 제 3 산화물 반도체막 위에 제 5 절연막을 형성하고, 제 5 절연막 위에 제 2 도전막을 형성하고, 제 2 도전막, 제 3 절연막 및 제 3 산화물 반도체막에 화학적 기계적 연마 처리를 행하는 것에 의하여, 제 3 산화물 반도체층, 게이트 절연층, 게이트 전극층을 형성하는 것을 특징으로 하는 반도체 장치의 제조 방법이다.In another aspect of the present invention, a first insulating layer is formed, a first oxide semiconductor film is formed on the first insulating layer, a second oxide semiconductor film is formed on the first oxide semiconductor film, and a first heat treatment is performed, By forming a first conductive film on the second oxide semiconductor film and selectively etching the first oxide semiconductor film and the second oxide semiconductor film using the first mask and the first conductive film, the first oxide semiconductor layer and the second oxide semiconductor film are formed. An oxide semiconductor layer is formed in an island shape, a second insulating film is formed on the first insulating layer and the first conductive film, and when forming the second insulating film, a mixed layer of the first insulating layer and the second insulating film is formed, and the mixed layer or the second insulating film is formed. Oxygen is added to the first insulating layer, a second heat treatment is performed, oxygen diffuses into the second oxide semiconductor layer, oxygen vacancies in the second oxide semiconductor layer are reduced, and a third insulating film is formed on the second insulating film, A third insulating layer and a second insulating layer are formed by performing planarization treatment on the third insulating film and etching the third insulating film and a portion of the second insulating film using a second mask, and forming the first conductive layer and the third insulating layer. A fourth insulating film is formed on the insulating layer, and anisotropic etching is performed to form a fourth insulating layer in contact with the side surfaces of the second and third insulating layers, and using the fourth insulating layer as a mask, 1 By etching a part of the conductive film, a source electrode and a drain electrode are formed, a third oxide semiconductor film is formed on the third insulating layer and the second oxide semiconductor layer, and a fifth insulating film is formed on the third oxide semiconductor film. , forming a second conductive film on the fifth insulating film, and subjecting the second conductive film, the third insulating film, and the third oxide semiconductor film to a chemical mechanical polishing treatment to form a third oxide semiconductor layer, a gate insulating layer, and a gate electrode layer. A method of manufacturing a semiconductor device characterized by the following.

또한, 제 2 절연막을, 스퍼터링법에 의하여 산소 가스를 사용하여 형성하는 것이 바람직하다.Additionally, it is preferable to form the second insulating film using oxygen gas by a sputtering method.

또한, 제 2 절연막을, 스퍼터링법에 의하여, 산화 알루미늄 타깃을 사용하여, 산소를 50체적% 이상 가진 조건으로, 산화 실리콘막 위에 형성하는 것이 바람직하다.Additionally, it is preferable to form the second insulating film on the silicon oxide film by a sputtering method using an aluminum oxide target under the condition of having 50% by volume or more of oxygen.

또한, 제 2 가열 처리를 300 이상 450 이하에서 처리하는 것이 바람직하다.Additionally, it is preferable to carry out the second heat treatment at a temperature of 300°C or more and 450°C or less.

또한, 반도체 장치와, 마이크로폰과, 스피커와, 하우징을 사용한 구성으로 할 수 있다.Additionally, it can be configured using a semiconductor device, a microphone, a speaker, and a housing.

본 발명의 일 형태를 사용하는 것에 의하여, 트랜지스터 근방의 기생 용량을 저감할 수 있다. 또는, 전기 특성이 양호한 반도체 장치를 제공할 수 있다. 또는, 신뢰성이 높은 반도체 장치를 제공할 수 있다. 또는, 노광 장치의 해상 한계 이하의 패턴 형성이 가능한 트랜지스터, 또는 반도체 장치의 제조 방법을 제공할 수 있다. 또는, 트랜지스터 또는 반도체 장치의, 제조 공정에 기인한 특성의 편차를 저감할 수 있다. 또는, 산소 결손이 적은 산화물 반도체층을 가지는 반도체 장치를 제공할 수 있다. 또는, 간단한 공정으로 형성할 수 있는 반도체 장치를 제공할 수 있다. 또는, 산화물 반도체층 근방의 계면 준위를 저감할 수 있는 구성의 반도체 장치를 제공할 수 있다. 또는, 저소비전력의 반도체 장치를 제공할 수 있다. 또한, 개발 비용을 억제한 신규 반도체 장치의 제조법을 제공할 수 있다. 또는, 신규 반도체 장치 등을 제공할 수 있다. 또는 상기 반도체 장치의 제작 방법을 제공할 수 있다.By using one embodiment of the present invention, parasitic capacitance near the transistor can be reduced. Alternatively, a semiconductor device with good electrical characteristics can be provided. Alternatively, a highly reliable semiconductor device can be provided. Alternatively, a method for manufacturing a transistor or semiconductor device capable of forming a pattern below the resolution limit of an exposure apparatus can be provided. Alternatively, variation in the characteristics of a transistor or semiconductor device due to the manufacturing process can be reduced. Alternatively, a semiconductor device having an oxide semiconductor layer with few oxygen vacancies can be provided. Alternatively, a semiconductor device that can be formed through a simple process can be provided. Alternatively, a semiconductor device configured to reduce the interface level near the oxide semiconductor layer can be provided. Alternatively, a semiconductor device with low power consumption can be provided. Additionally, it is possible to provide a manufacturing method for a new semiconductor device with reduced development costs. Alternatively, a new semiconductor device, etc. can be provided. Alternatively, a method of manufacturing the semiconductor device may be provided.

또한, 이들 효과의 기재는, 다른 효과의 존재를 방해하는 것은 아니다. 또한, 본 발명의 일 형태는, 반드시 이들 효과의 모두를 가질 필요는 없다. 또한, 이들 이외의 효과는, 명세서, 도면, 청구항 등의 기재로부터, 저절로 명백해질 것이며, 명세서, 도면, 청구항 등의 기재로부터, 이들 이외의 효과를 추출하는 것이 가능하다.Additionally, the description of these effects does not prevent the existence of other effects. Additionally, one embodiment of the present invention does not necessarily have all of these effects. In addition, effects other than these will naturally become apparent from the description, drawings, claims, etc., and it is possible to extract effects other than these from the description, drawings, claims, etc.

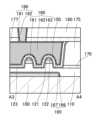

도 1은 트랜지스터를 설명하는 상면도 및 단면도.

도 2는 트랜지스터를 설명하는 상면도 및 단면도.

도 3은 트랜지스터를 설명하는 상면도 및 단면도.

도 4는 산화물 반도체층의 밴드도. 트랜지스터의 확대 단면도.

도 5는 ALD 성막 원리.

도 6은 ALD 장치의 개요도.

도 7은 트랜지스터의 제작 방법을 설명하는 상면도 및 단면도.

도 8은 트랜지스터의 제작 방법을 설명하는 상면도 및 단면도.

도 9는 트랜지스터의 제작 방법을 설명하는 상면도 및 단면도.

도 10은 트랜지스터의 제작 방법을 설명하는 상면도 및 단면도.

도 11은 트랜지스터의 제작 방법을 설명하는 상면도 및 단면도.

도 12는 트랜지스터의 제작 방법을 설명하는 상면도 및 단면도.

도 13은 트랜지스터의 제작 방법을 설명하는 상면도 및 단면도.

도 14는 트랜지스터를 설명하는 상면도 및 단면도.

도 15는 트랜지스터를 설명하는 상면도 및 단면도.

도 16은 트랜지스터의 제작 방법을 설명하는 상면도 및 단면도.

도 17은 트랜지스터를 설명하는 상면도 및 단면도.

도 18은 트랜지스터를 설명하는 상면도 및 단면도.

도 19는 트랜지스터를 설명하는 상면도 및 단면도.

도 20은 트랜지스터의 제작 방법을 설명하는 상면도 및 단면도.

도 21은 트랜지스터의 제작 방법을 설명하는 상면도 및 단면도.

도 22는 트랜지스터의 제작 방법을 설명하는 상면도 및 단면도.

도 23은 트랜지스터의 제작 방법을 설명하는 상면도 및 단면도.

도 24는 CAAC-OS의 단면에서의 Cs 보정 고분해능 TEM 이미지, 및 CAAC-OS의 단면 모식도.

도 25는 CAAC-OS의 평면에서의 Cs 보정 고분해능 TEM 이미지.

도 26은 CAAC-OS 및 단결정 산화물 반도체의 XRD에 의한 구조 해석을 설명하는 도면.

도 27은 CAAC-OS의 전자 회절 패턴을 나타낸 도면.

도 28은 In-Ga-Zn 산화물의 전자 조사에 의한 결정부의 변화를 나타낸 도면.

도 29는 반도체 장치의 단면도 및 회로도.

도 30은 반도체 장치의 단면도 및 회로도.

도 31은 촬상 장치를 도시한 평면도.

도 32는 촬상 장치의 화소를 도시한 평면도.

도 33은 촬상 장치를 도시한 단면도.

도 34는 촬상 장치를 도시한 단면도.

도 35는 RF 태그의 구성예를 설명하는 도면.

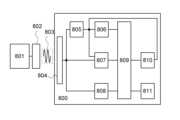

도 36은 CPU의 구성예를 설명하는 도면.

도 37은 기억 소자의 회로도.

도 38은 표시 장치의 구성예를 설명하는 도면 및 화소의 회로도.

도 39는 표시 모듈을 설명하는 도면.

도 40은 리드 프레임형의 인터포저를 사용한 패키지의 단면 구조를 나타낸 사시도.

도 41은 전자 기기를 설명하는 도면.

도 42는 전자 기기를 설명하는 도면.

도 43은 전자 기기를 설명하는 도면.

도 44는 전자 기기를 설명하는 도면.1 is a top view and cross-sectional view illustrating a transistor.

Figure 2 is a top view and cross-sectional view illustrating a transistor.

3 is a top view and cross-sectional view illustrating a transistor.

Figure 4 is a band diagram of an oxide semiconductor layer. Enlarged cross-sectional view of a transistor.

Figure 5 shows the principle of ALD film formation.

6 is a schematic diagram of an ALD device.

7 is a top view and cross-sectional view illustrating a method of manufacturing a transistor.

8 is a top view and cross-sectional view illustrating a method of manufacturing a transistor.

9 is a top view and cross-sectional view illustrating a method of manufacturing a transistor.

10 is a top view and cross-sectional view illustrating a method of manufacturing a transistor.

11 is a top view and cross-sectional view illustrating a method of manufacturing a transistor.

12 is a top view and cross-sectional view illustrating a method of manufacturing a transistor.

13 is a top view and cross-sectional view illustrating a method of manufacturing a transistor.

14 is a top view and cross-sectional view illustrating a transistor.

15 is a top view and cross-sectional view illustrating a transistor.

16 is a top view and cross-sectional view illustrating a method of manufacturing a transistor.

17 is a top view and cross-sectional view illustrating a transistor.

18 is a top view and cross-sectional view illustrating a transistor.

19 is a top view and cross-sectional view illustrating a transistor.

20 is a top view and cross-sectional view illustrating a method of manufacturing a transistor.

21 is a top view and cross-sectional view illustrating a method of manufacturing a transistor.

22 is a top view and cross-sectional view illustrating a method of manufacturing a transistor.

23 is a top view and cross-sectional view illustrating a method of manufacturing a transistor.

Figure 24 is a Cs-corrected high-resolution TEM image of a cross-section of CAAC-OS, and a cross-sectional schematic diagram of CAAC-OS.

Figure 25 is a Cs-corrected high-resolution TEM image in the plane of CAAC-OS.

Figure 26 is a diagram explaining structural analysis of CAAC-OS and single crystal oxide semiconductor by XRD.

Figure 27 is a diagram showing the electron diffraction pattern of CAAC-OS.

Figure 28 is a diagram showing changes in crystal parts of In-Ga-Zn oxide due to electron irradiation.

29 is a cross-sectional view and circuit diagram of a semiconductor device.

30 is a cross-sectional view and circuit diagram of a semiconductor device.

31 is a plan view showing an imaging device.

32 is a top view showing pixels of an imaging device.

Fig. 33 is a cross-sectional view showing the imaging device.

Fig. 34 is a cross-sectional view showing the imaging device.

35 is a diagram explaining an example of the configuration of an RF tag.

Fig. 36 is a diagram explaining a configuration example of a CPU.

37 is a circuit diagram of a memory element.

38 is a diagram illustrating a configuration example of a display device and a circuit diagram of a pixel.

39 is a diagram explaining the display module.

Figure 40 is a perspective view showing the cross-sectional structure of a package using a lead frame type interposer.

41 is a diagram explaining electronic devices.

42 is a diagram explaining electronic devices.

43 is a diagram explaining electronic devices.

44 is a diagram explaining electronic devices.

실시형태에 대하여, 도면을 사용하여 자세히 설명한다. 다만, 본 발명은 이하의 설명에 한정되지 않고, 본 발명의 취지 및 그 범위에서 벗어남이 없이 그 형태 및 자세한 사항을 다양하게 변경할 수 있는 것은 당업자라면 용이하게 이해할 것이다. 따라서, 본 발명은 이하에 기재된 실시형태의 기재 내용에 한정하여 해석되는 것은 아니다. 또한, 이하에서 설명하는 발명의 구성에 있어서, 동일 부분 또는 마찬가지의 기능을 가지는 부분에는 동일한 부호를 상이한 도면 간에서 공통적으로 사용하고, 그 반복되는 설명은 생략하는 경우가 있다. 또한, 도면을 구성하는 같은 요소의 해칭을 상이한 도면 간에서 적절히 생략 또는 변경하는 경우도 있다.Embodiments will be described in detail using drawings. However, the present invention is not limited to the following description, and those skilled in the art will easily understand that the form and details can be changed in various ways without departing from the spirit and scope of the present invention. Accordingly, the present invention should not be construed as limited to the description of the embodiments described below. In addition, in the structure of the invention described below, the same symbols are commonly used in different drawings for identical parts or parts having similar functions, and repeated descriptions thereof may be omitted. Additionally, there are cases where the hatching of the same elements constituting the drawings is appropriately omitted or changed between different drawings.

예를 들어, 본 명세서 등에 있어서, X와 Y가 접속되어 있다고 명시적으로 기재되어 있는 경우는, X와 Y가 전기적으로 접속되어 있는 경우와, X와 Y가 기능적으로 접속되어 있는 경우와, X와 Y가 직접 접속되어 있는 경우가, 본 명세서 등에 개시되어 있는 것으로 한다. 따라서, 소정의 접속 관계, 예를 들어, 도면 또는 문장에 나타난 접속 관계에 한정되지 않고, 도면 또는 문장에 나타난 접속 관계 이외의 것도, 도면 또는 문장에 기재되어 있는 것으로 한다.For example, in this specification, etc., when it is explicitly stated that X and Y are connected, the case where X and Y are electrically connected, the case where The case where and Y are directly connected is assumed to be disclosed in this specification and the like. Therefore, it is not limited to the predetermined connection relationship, for example, the connection relationship shown in the drawing or text, and connection relationships other than those shown in the drawing or text are also described in the drawing or text.

여기서, X, Y는, 대상물(예를 들어, 장치, 소자, 회로, 배선, 전극, 단자, 도전막, 층 등)인 것으로 한다.Here, X and Y are assumed to be objects (e.g., devices, elements, circuits, wiring, electrodes, terminals, conductive films, layers, etc.).

X와 Y가 직접적으로 접속되어 있는 경우의 일례로서는, X와 Y의 전기적인 접속을 가능하게 하는 소자(예를 들어, 스위치, 트랜지스터, 용량 소자, 인덕터, 저항 소자, 다이오드, 표시 소자, 발광 소자, 부하 등)가, X와 Y 사이에 접속되어 있지 않은 경우이며, X와 Y의 전기적인 접속을 가능하게 하는 소자(예를 들어, 스위치, 트랜지스터, 용량 소자, 인덕터, 저항 소자, 다이오드, 표시 소자, 발광 소자, 부하 등)를 통하지 않고, X와 Y가 접속되어 있는 경우이다.An example of a case where X and Y are directly connected is an element that enables electrical connection between , load, etc.) is not connected between X and Y, and elements that enable electrical connection between This is the case where X and Y are connected without passing through an element, light-emitting element, load, etc.).

X와 Y가 전기적으로 접속되어 있는 경우의 일례로서는, X와 Y의 전기적인 접속을 가능하게 하는 소자(예를 들어, 스위치, 트랜지스터, 용량 소자, 인덕터, 저항 소자, 다이오드, 표시 소자, 발광 소자, 부하 등)가, X와 Y 사이에 1개 이상 접속되는 것이 가능하다. 또한, 스위치는, 온 오프가 제어되는 기능을 가지고 있다. 즉, 스위치는, 도통 상태(온 상태), 또는 비도통 상태(오프 상태)가 되어, 전류를 흘릴지 흘리지 않을지를 제어하는 기능을 가지고 있다. 또는, 스위치는, 전류를 흘리는 경로를 선택하여 전환하는 기능을 가지고 있다. 또한, X와 Y가 전기적으로 접속되어 있는 경우는, X와 Y가 직접적으로 접속되어 있는 경우를 포함하는 것으로 한다.An example of a case where X and Y are electrically connected is an element that enables electrical connection between , load, etc.) can be connected between X and Y. Additionally, the switch has a function to control on and off. In other words, the switch has the function of controlling whether or not to flow current by being in a conductive state (on state) or non-conductive state (off state). Alternatively, a switch has the function of selecting and switching a path through which current flows. Additionally, the case where X and Y are electrically connected includes the case where X and Y are directly connected.

X와 Y가 기능적으로 접속되어 있는 경우의 일례로서는, X와 Y의 기능적인 접속을 가능하게 하는 회로(예를 들어, 논리 회로(인버터, NAND 회로, NOR 회로 등), 신호 변환 회로(DA 변환 회로, AD 변환 회로, 감마 보정 회로 등), 전위 레벨 변환 회로(전원 회로(승압 회로, 강압 회로 등), 신호의 전위 레벨을 바꾸는 레벨 시프터 회로 등), 전압원, 전류원, 전환 회로, 증폭 회로(신호 진폭 또는 전류량 등을 크게 할 수 있는 회로, 연산 증폭기, 차동 증폭 회로, 소스 폴로어 회로, 버퍼 회로 등), 신호 생성 회로, 기억 회로, 제어 회로 등)가, X와 Y 사이에 1개 이상 접속되는 것이 가능하다. 또한, 일례로서, X와 Y 사이에 다른 회로를 개재(介在)하더라도, X로부터 출력된 신호가 Y로 전달되는 경우에는, X와 Y는 기능적으로 접속되어 있는 것으로 한다. 또한, X와 Y가 기능적으로 접속되어 있는 경우는, X와 Y가 직접적으로 접속되어 있는 경우와, X와 Y가 전기적으로 접속되어 있는 경우를 포함하는 것으로 한다.An example of a case where X and Y are functionally connected include circuits that enable functional connection of circuit, AD conversion circuit, gamma correction circuit, etc.), potential level conversion circuit (power circuit (boosting circuit, step-down circuit, etc.), level shifter circuit that changes the potential level of the signal, etc.), voltage source, current source, switching circuit, amplification circuit ( At least one circuit (operational amplifier, differential amplifier circuit, source follower circuit, buffer circuit, etc.) that can increase the signal amplitude or current amount, signal generation circuit, memory circuit, control circuit, etc.) between X and Y It is possible to connect. Additionally, as an example, even if another circuit is interposed between X and Y, when a signal output from X is transmitted to Y, X and Y are assumed to be functionally connected. In addition, the case where X and Y are functionally connected includes the case where X and Y are directly connected and the case where X and Y are electrically connected.

또한, X와 Y가 전기적으로 접속되어 있다고 명시적으로 기재되어 있는 경우는, X와 Y가 전기적으로 접속되어 있는 경우(즉, X와 Y 사이에 다른 소자 또는 다른 회로를 개재하여 접속되어 있는 경우)와, X와 Y가 기능적으로 접속되어 있는 경우(즉, X와 Y 사이에 다른 회로를 개재하여 기능적으로 접속되어 있는 경우)와, X와 Y가 직접 접속되어 있는 경우(즉, X와 Y 사이에 다른 소자 또는 다른 회로를 개재하지 않고 접속되어 있는 경우)가, 본 명세서 등에 개시되어 있는 것으로 한다. 즉, 전기적으로 접속되어 있다고 명시적으로 기재되어 있는 경우는, 단순히, 접속되어 있다고만 명시적으로 기재되어 있는 경우와 마찬가지의 내용이, 본 명세서 등에 개시되어 있는 것으로 한다.In addition, when it is explicitly stated that X and Y are electrically connected, it means that ), a case where X and Y are functionally connected (i.e., a case where they are functionally connected through another circuit between X and Y), and a case where X and Y are directly connected (i.e., (connected without intervening other elements or other circuits) is assumed to be disclosed in this specification, etc. In other words, when it is explicitly stated that they are electrically connected, the same content as when it is explicitly stated that they are simply connected is assumed to be disclosed in this specification, etc.

또한, 예를 들어, 트랜지스터의 소스(또는 제 1 단자 등)가, Z1을 통하여(또는 통하지 않고), X와 전기적으로 접속되고, 트랜지스터의 드레인(또는 제 2 단자 등)이, Z2를 통하여(또는 통하지 않고), Y와 전기적으로 접속되어 있는 경우나, 트랜지스터의 소스(또는 제 1 단자 등)가, Z1의 일부와 직접적으로 접속되고, Z1의 다른 일부가 X와 직접적으로 접속되고, 트랜지스터의 드레인(또는 제 2 단자 등)이, Z2의 일부와 직접적으로 접속되고, Z2의 다른 일부가 Y와 직접적으로 접속되어 있는 경우에는, 이하와 같이 표현할 수 있다.Additionally, for example, the source (or first terminal, etc.) of the transistor is electrically connected to X through (or not through) Z1, and the drain (or second terminal, etc.) of the transistor is electrically connected to or not), when electrically connected to Y, or when the source (or first terminal, etc.) of the transistor is directly connected to part of Z1, and another part of Z1 is directly connected to In the case where the drain (or the second terminal, etc.) is directly connected to part of Z2, and the other part of Z2 is directly connected to Y, it can be expressed as follows.

예를 들어, "X와 Y와 트랜지스터의 소스(또는 제 1 단자 등)와 드레인(또는 제 2 단자 등)은, 서로 전기적으로 접속되어 있고, X, 트랜지스터의 소스(또는 제 1 단자 등), 트랜지스터의 드레인(또는 제 2 단자 등), Y의 순서로 전기적으로 접속되어 있다."라고 표현할 수 있다. 또는, "트랜지스터의 소스(또는 제 1 단자 등)는, X와 전기적으로 접속되고, 트랜지스터의 드레인(또는 제 2 단자 등)은 Y와 전기적으로 접속되고, X, 트랜지스터의 소스(또는 제 1 단자 등), 트랜지스터의 드레인(또는 제 2 단자 등), Y는, 이 순서로 전기적으로 접속되어 있다"라고 표현할 수 있다. 또는, "X는, 트랜지스터의 소스(또는 제 1 단자 등)와 드레인(또는 제 2 단자 등)을 통하여, Y와 전기적으로 접속되고, X, 트랜지스터의 소스(또는 제 1 단자 등), 트랜지스터의 드레인(또는 제 2 단자 등), Y는, 이 접속 순서로 제공되어 있다"라고 표현할 수 있다. 이들 예와 마찬가지의 표현 방법을 사용하여, 회로 구성에서의 접속의 순서에 대하여 규정하는 것에 의하여, 트랜지스터의 소스(또는 제 1 단자 등)와, 드레인(또는 제 2 단자 등)을, 구별하여, 기술적 범위를 결정할 수 있다.For example, "X and Y and the source (or first terminal, etc.) and drain (or second terminal, etc.) of the transistor are electrically connected to each other, It can be expressed as “they are electrically connected in that order: the drain (or second terminal, etc.) of the transistor, and Y.” Or, "the source (or first terminal, etc.) of the transistor is electrically connected to X, the drain (or second terminal, etc.) of the transistor is electrically connected to Y, and etc.), the drain (or second terminal, etc.) of the transistor, and Y are electrically connected in this order.” Or, "X is electrically connected to Y through the source (or first terminal, etc.) and drain (or second terminal, etc.) of the transistor, and It can be expressed as “the drain (or second terminal, etc.), Y, is provided in this connection order.” Using the same expression method as in these examples, the source (or first terminal, etc.) and drain (or second terminal, etc.) of the transistor are distinguished by specifying the order of connection in the circuit configuration. The technical scope can be determined.

또는, 다른 표현 방법으로서, 예를 들어, "트랜지스터의 소스(또는 제 1 단자 등)는, 적어도 제 1 접속 경로를 통하여, X와 전기적으로 접속되고, 상기 제 1 접속 경로는, 제 2 접속 경로를 가지지 않고, 상기 제 2 접속 경로는, 트랜지스터를 통하는, 트랜지스터의 소스(또는 제 1 단자 등)와 트랜지스터의 드레인(또는 제 2 단자 등) 사이의 경로이고, 상기 제 1 접속 경로는, Z1을 통하는 경로이고, 트랜지스터의 드레인(또는 제 2 단자 등)은, 적어도 제 3 접속 경로를 통하여, Y와 전기적으로 접속되고, 상기 제 3 접속 경로는, 상기 제 2 접속 경로를 가지지 않고, 상기 제 3 접속 경로는, Z2를 통하는 경로이다."라고 표현할 수 있다. 또는, "트랜지스터의 소스(또는 제 1 단자 등)는, 적어도 제 1 접속 경로에 의하여, Z1을 통하여, X와 전기적으로 접속되고, 상기 제 1 접속 경로는, 제 2 접속 경로를 가지지 않고, 상기 제 2 접속 경로는, 트랜지스터를 통하는 접속 경로를 가지고, 트랜지스터의 드레인(또는 제 2 단자 등)은, 적어도 제 3 접속 경로에 의하여, Z2를 통하여, Y와 전기적으로 접속되고, 상기 제 3 접속 경로는, 상기 제 2 접속 경로를 가지지 않는다."라고 표현할 수 있다. 또는, "트랜지스터의 소스(또는 제 1 단자 등)는, 적어도 제 1 전기적 패스에 의하여, Z1을 통하여, X와 전기적으로 접속되고, 상기 제 1 전기적 패스는, 제 2 전기적 패스를 가지지 않고, 상기 제 2 전기적 패스는, 트랜지스터의 소스(또는 제 1 단자 등)로부터 트랜지스터의 드레인(또는 제 2 단자 등)으로의 전기적 패스이고, 트랜지스터의 드레인(또는 제 2 단자 등)은, 적어도 제 3 전기적 패스에 의하여, Z2를 통하여, Y와 전기적으로 접속되고, 상기 제 3 전기적 패스는, 제 4 전기적 패스를 가지지 않고, 상기 제 4 전기적 패스는, 트랜지스터의 드레인(또는 제 2 단자 등)으로부터 트랜지스터의 소스(또는 제 1 단자 등)로의 전기적 패스이다."라고 표현할 수 있다. 이들 예와 마찬가지의 표현 방법을 사용하여, 회로 구성에서의 접속 경로에 대하여 규정하는 것에 의하여, 트랜지스터의 소스(또는 제 1 단자 등)와, 드레인(또는 제 2 단자 등)을, 구별하여, 기술적 범위를 결정할 수 있다.Or, as another way of expressing it, for example, "the source (or first terminal, etc.) of the transistor is electrically connected to X through at least a first connection path, and the first connection path is a second connection path. Without having, the second connection path is a path between the source (or first terminal, etc.) of the transistor and the drain (or second terminal, etc.) of the transistor through the transistor, and the first connection path is Z1. It is a path that connects the transistor, and the drain (or second terminal, etc.) of the transistor is electrically connected to Y through at least a third connection path, and the third connection path does not have the second connection path, and the third connection path The connection path can be expressed as “the path through Z2.” Or, "the source (or first terminal, etc.) of the transistor is electrically connected to The second connection path has a connection path through the transistor, and the drain (or second terminal, etc.) of the transistor is electrically connected to Y through Z2 by at least a third connection path, and the third connection path It can be expressed as “does not have the second connection path.” Or, "the source (or first terminal, etc.) of the transistor is electrically connected to The second electrical path is an electrical path from the source (or first terminal, etc.) of the transistor to the drain (or second terminal, etc.) of the transistor, and the drain (or second terminal, etc.) of the transistor is at least a third electrical path. is electrically connected to Y through Z2, wherein the third electrical path does not have a fourth electrical path, and the fourth electrical path extends from the drain (or second terminal, etc.) of the transistor to the source of the transistor. (or the first terminal, etc.) is an electrical pass." Using the same expression method as these examples, by specifying the connection path in the circuit configuration, the source (or first terminal, etc.) and drain (or second terminal, etc.) of the transistor are distinguished and described technically. The scope can be determined.

또한, 이들 표현 방법은, 일례이며, 이들 표현 방법에 한정되지 않는다. 여기서, X, Y, Z1, Z2는, 대상물(예를 들어, 장치, 소자, 회로, 배선, 전극, 단자, 도전막, 층 등)인 것으로 한다.Additionally, these expression methods are examples and are not limited to these expression methods. Here, X, Y, Z1, and Z2 are assumed to be objects (e.g., devices, elements, circuits, wiring, electrodes, terminals, conductive films, layers, etc.).

또한, 회로도상에서 독립되어 있는 구성 요소들이 전기적으로 접속되어 있는 것처럼 도시된 경우라도, 하나의 구성 요소가, 복수의 구성 요소의 기능을 겸비하는 경우도 있다. 예를 들어 배선의 일부가 전극으로도 기능하는 경우, 하나의 도전막이, 배선의 기능, 및 전극의 기능의 모든 구성 요소의 기능을 겸비하고 있다. 따라서, 본 명세서에서 전기적으로 접속이란, 이 같은, 하나의 도전막이, 복수의 구성 요소의 기능을 겸비하고 있는 경우도, 그 범주에 포함한다.Additionally, even when independent components are shown as electrically connected on a circuit diagram, there are cases where one component has the functions of multiple components. For example, when a part of the wiring also functions as an electrode, one conductive film combines the functions of all components of the wiring function and the electrode function. Therefore, in this specification, electrical connection also includes cases where a single conductive film functions as a plurality of components.

실시형태에 대하여, 도면을 사용하여 자세히 설명한다. 다만, 본 발명은 이하의 설명에 한정되지 않고, 본 발명의 취지 및 그 범위에서 벗어남이 없이 그 형태 및 자세한 사항을 다양하게 변경할 수 있는 것은 당업자라면 용이하게 이해할 것이다. 따라서, 본 발명은 이하에 기재된 실시형태의 기재 내용에 한정하여 해석되는 것은 아니다. 또한, 이하에서 설명하는 발명의 구성에 있어서, 동일 부분 또는 마찬가지의 기능을 가지는 부분에는 동일한 부호를 상이한 도면 간에서 공통적으로 사용하고, 그 반복되는 설명은 생략한다.Embodiments will be described in detail using drawings. However, the present invention is not limited to the following description, and those skilled in the art will easily understand that the form and details can be changed in various ways without departing from the spirit and scope of the present invention. Accordingly, the present invention should not be construed as limited to the description of the embodiments described below. In addition, in the structure of the invention described below, the same symbols are commonly used in different drawings for identical parts or parts having similar functions, and repeated descriptions thereof are omitted.

<도면을 설명하는 기재에 관한 부기><Additional note regarding description of drawing>

본 명세서에 있어서, "위에", "아래에" 등의 배치를 나타내는 어구는, 구성들끼리의 위치 관계를, 도면을 참조하여 설명하기 위하여, 편의상 사용하고 있다. 또한, 구성들끼리의 위치 관계는, 각 구성을 묘사하는 방향에 따라 적절히 변화하는 것이다. 따라서, 명세서에서 설명한 어구에 한정되지 않고, 상황에 따라 적절히 바꿔 말할 수 있다.In this specification, phrases indicating arrangement such as “above” and “below” are used for convenience to describe the positional relationship between components with reference to the drawings. Additionally, the positional relationship between components changes appropriately depending on the direction in which each component is depicted. Therefore, it is not limited to the phrases described in the specification and can be appropriately rephrased depending on the situation.

또한, "위"나 "아래"의 용어는, 구성 요소의 위치 관계가 직상 또는 직하이고, 또한 직접 접촉하고 있는 것을 한정하는 것은 아니다. 예를 들어, "절연층 A 위의 전극 B"의 표현이라면, 절연층 A 위에 전극 B가 직접 접촉하여 형성되어 있을 필요는 없고, 절연층 A와 전극 B 사이에 다른 구성 요소를 포함하는 것을 제외하지 않는다.Additionally, the terms “above” and “below” do not limit the positional relationship of the components to being directly above or below or in direct contact. For example, if the expression is “electrode B on insulating layer A,” electrode B does not need to be formed in direct contact with insulating layer A, except for including other components between insulating layer A and electrode B. I never do that.

본 명세서에 있어서, "평행"이란, 두 직선이 -10° 이상 10° 이하의 각도로 배치되어 있는 상태를 말한다. 따라서, -5° 이상 5° 이하의 경우도 포함된다. 또한, "대략 평행"이란, 두 직선이 -30° 이상 30° 이하의 각도로 배치되어 있는 상태를 말한다. 또한, "수직"이란, 두 직선이 80° 이상 100° 이하의 각도로 배치되어 있는 상태를 말한다. 따라서, 85° 이상 95° 이하의 경우도 포함된다. 또한, "대략 수직"이란, 두 직선이 60° 이상 120° 이하의 각도로 배치되어 있는 상태를 말한다.In this specification, “parallel” refers to a state in which two straight lines are arranged at an angle of -10° or more and 10° or less. Therefore, cases of -5° or more and 5° or less are also included. Additionally, “approximately parallel” refers to a state in which two straight lines are arranged at an angle of -30° or more and 30° or less. In addition, “perpendicular” refers to a state in which two straight lines are arranged at an angle of 80° or more and 100° or less. Therefore, cases of 85° or more and 95° or less are also included. Additionally, “approximately perpendicular” refers to a state in which two straight lines are arranged at an angle of 60° or more and 120° or less.

또한, 본 명세서에 있어서, 결정이 삼방정 또는 능면체정인 경우, 육방정계로서 나타낸다.Additionally, in this specification, when the crystal is trigonal or rhombohedral, it is indicated as hexagonal.

또한, 도면에 있어서, 크기, 층의 두께, 또는 영역은, 설명의 편의상 임의의 크기로 나타낸 것이다. 따라서, 반드시 그 스케일에 한정되지는 않는다. 또한 도면은 명확성을 기하기 위하여 모식적으로 나타낸 것이며, 도면에 나타난 형상 또는 값 등에 한정되지 않는다.In addition, in the drawings, the size, layer thickness, or area are shown at arbitrary sizes for convenience of explanation. Therefore, it is not necessarily limited to that scale. Additionally, the drawings are schematically shown for clarity and are not limited to the shapes or values shown in the drawings.

또한, 도면에 있어서, 상면도(평면도, 레이아웃 도면이라고도 함)나 사시도 등에 있어서, 도면의 명확성을 기하기 위하여, 일부의 구성 요소의 기재를 생략하고 있는 경우가 있다.Additionally, in the drawings, in top views (also called plan views, layout drawings), perspective views, etc., description of some components may be omitted to ensure clarity of the drawings.

또한, "동일"이란, 동일한 면적을 가져도 좋고, 동일한 형상을 가져도 좋다. 또한, 제조 공정의 관계상, 완전히 동일한 형상이 되지 않는 것도 상정되기 때문에, 대략 동일하더라도 동일하다고 바꿔 발할 수 있다.In addition, “same” may have the same area or may have the same shape. Additionally, due to the manufacturing process, it is assumed that the shapes may not be completely the same, so even if they are substantially the same, they can be called the same.

<바꿔 말할 수 있는 기재에 관한 부기><Additional note regarding paraphrase>

본 명세서 등에 있어서, 트랜지스터의 접속 관계를 설명할 때, 소스와 드레인 중 한쪽을, "소스 또는 드레인의 한쪽"(또는 제 1 전극, 또는 제 1 단자)이라고 표기하고, 소스와 드레인 중 다른 쪽을 "소스 또는 드레인의 다른 쪽"(또는 제 2 전극, 또는 제 2 단자)이라고 표기하였다. 이는, 트랜지스터의 소스와 드레인은, 트랜지스터의 구조 또는 동작 조건 등에 따라 바뀌기 때문이다. 또한 트랜지스터의 소스와 드레인의 호칭에 대해서는, 소스(드레인) 단자나, 소스(드레인) 전극 등, 상황에 따라 적절히 바꿔 말할 수 있다.In this specification, etc., when explaining the connection relationship of a transistor, one of the source and the drain is referred to as "one of the source or the drain" (or the first electrode, or the first terminal), and the other of the source and the drain is referred to as "one of the source and the drain." It is indicated as “the other side of the source or drain” (or second electrode, or second terminal). This is because the source and drain of the transistor change depending on the structure or operating conditions of the transistor. Additionally, the names of the source and drain of a transistor can be appropriately changed depending on the situation, such as the source (drain) terminal or the source (drain) electrode.

또한, 본 명세서 등에 있어서 "전극"이나 "배선"의 용어는, 이들 구성 요소를 기능적으로 한정하는 것은 아니다. 예를 들어, "전극"은 "배선"의 일부로서 사용되는 경우가 있고, 그 반대도 마찬가지이다. 또한, "전극"이나 "배선"의 용어는, 복수의 "전극"이나 "배선"이 일체가 되어 형성되어 있는 경우 등도 포함한다.Additionally, the terms “electrode” and “wiring” in this specification and elsewhere do not functionally limit these components. For example, “electrode” may be used as part of “wiring” and vice versa. Additionally, the terms “electrode” and “wiring” also include cases where a plurality of “electrodes” or “wiring” are formed as one body.

또한, 본 명세서 등에 있어서, 트랜지스터란, 게이트와, 드레인과, 소스를 포함하는 적어도 3개의 단자를 가지는 소자이다. 그리고, 드레인(드레인 단자, 드레인 영역 또는 드레인 전극)과 소스(소스 단자, 소스 영역 또는 소스 전극) 사이에 채널 영역을 가지고 있고, 드레인과 채널 영역과 소스를 통하여 전류를 흘릴 수 있는 것이다.Additionally, in this specification and the like, a transistor is an element having at least three terminals including a gate, drain, and source. Additionally, it has a channel region between the drain (drain terminal, drain region, or drain electrode) and the source (source terminal, source region, or source electrode), and current can flow through the drain, channel region, and source.

여기서, 소스와 드레인은, 트랜지스터의 구조 또는 동작 조건 등에 따라 바뀌기 때문에, 어느 쪽이 소스 또는 드레인인지를 한정하는 것이 어렵다. 그러므로, 소스로서 기능하는 부분, 및 드레인으로서 기능하는 부분을, 소스 또는 드레인이라고 부르지 않고, 소스와 드레인 중 한쪽을 제 1 전극이라고 표기하고, 소스와 드레인 중 다른 쪽을 제 2 전극이라고 표기하는 경우가 있다.Here, since the source and drain change depending on the structure or operating conditions of the transistor, it is difficult to determine which is the source or drain. Therefore, the part that functions as the source and the part that functions as the drain are not called source or drain, but one of the source and drain is denoted as the first electrode, and the other of the source and drain is denoted as the second electrode. There is.

또한 본 명세서에서 사용하는 "제 1", "제 2", "제 3"이라는 서수사는, 구성 요소의 혼동을 피하기 위하여 붙인 것이며, 수적으로 한정하는 것은 아님을 부기한다.Additionally, it should be noted that the ordinal numbers “first,” “second,” and “third” used in this specification are added to avoid confusion between constituent elements and are not numerically limiting.

또한, 본 명세서 등에서는, 표시 패널의 기판에, 예를 들어 FPC(Flexible Printed Circuits) 또는 TCP(Tape Carrier Package) 등이 장착된 것, 또는 기판에 COG(Chip On Glass) 방식에 의하여 IC(집적 회로)가 직접 실장된 것을, 표시 장치라고 부르는 경우가 있다.In addition, in this specification and the like, for example, FPC (Flexible Printed Circuits) or TCP (Tape Carrier Package), etc. are mounted on the substrate of the display panel, or IC (integrated) is installed on the substrate using the COG (Chip On Glass) method. A device in which a circuit is directly mounted is sometimes called a display device.

또한, "막"이라는 말과, "층"이라는 말은, 경우에 따라서는, 또는 상황에 따라서, 서로 바꾸는 것이 가능하다. 예를 들어, "도전층"이라는 용어를, "도전막"이라는 용어로 변경하는 것이 가능한 경우가 있다. 또는, 예를 들어, "절연막"이라는 용어를, "절연층"이라는 용어로 변경하는 것이 가능한 경우가 있다.Additionally, the words "membrane" and "layer" can be interchanged depending on the case or situation. For example, there are cases where it is possible to change the term “conductive layer” to the term “conductive film.” Alternatively, for example, it may be possible to change the term “insulating film” to the term “insulating layer.”

<어구의 정의에 관한 부기><Note on definitions of phrases>

이하에서는, 본 명세서 등에서의 각 어구의 정의에 대하여 설명한다.Below, the definition of each phrase in this specification and the like will be explained.

본 명세서에 있어서, "트렌치" 또는 "홈"이라는 용어를 사용한 경우, 가는 띠 형상의 오목한 부분을 말한다.In this specification, when the term “trench” or “groove” is used, it refers to a concave portion in the shape of a thin strip.

또한, 본 명세서에 있어서, 막으로서 예를 들어 산화 질화 실리콘을 나타내는 경우, SiOxNy라고 기재하는 경우가 있다. 이때, x 및 y는, 자연수이어도 좋고, 소수점을 가지는 수이어도 좋다.In addition, in this specification, when the film represents, for example, silicon oxynitride, it may be described as SiOxNy. At this time, x and y may be natural numbers or numbers with a decimal point.

<접속에 대하여><About connection>

본 명세서에 있어서, A와 B가 접속되어 있다라는 것은, A와 B가 직접 접속되어 있는 것 외에, 전기적으로 접속되어 있는 것을 포함하는 것으로 한다. 여기서, A와 B가 전기적으로 접속되어 있다라는 것은, A와 B 사이에서, 어떠한 전기적 작용을 가지는 대상물이 존재할 때, A와 B의 전기 신호의 수수(授受)를 가능하게 하는 것을 말한다.In this specification, the fact that A and B are connected includes not only that A and B are directly connected, but also that they are electrically connected. Here, the fact that A and B are electrically connected means that when an object with some kind of electrical action exists between A and B, the exchange of electric signals between A and B is possible.

또한, 이들 표현 방법은, 일례이며, 이들 표현 방법에 한정되지 않는다. 여기서, X, Y, Z1, Z2는, 대상물(예를 들어, 장치, 소자, 회로, 배선, 전극, 단자, 도전막, 층 등)인 것으로 한다.Additionally, these expression methods are examples and are not limited to these expression methods. Here, X, Y, Z1, and Z2 are assumed to be objects (e.g., devices, elements, circuits, wiring, electrodes, terminals, conductive films, layers, etc.).

또한, 어떤 하나의 실시형태에서 기술하는 내용(일부의 내용이라도 좋음)은, 그 실시형태에서 기술하는 다른 내용(일부의 내용이라도 좋음), 및/또는 하나 또는 복수의 다른 실시형태에서 기술하는 내용(일부의 내용이라도 좋음)에 대하여, 적용, 조합, 또는 치환 등을 행할 수 있다.In addition, the content described in one embodiment (which may be part of the content) is the other content described in that embodiment (which may be part of the content), and/or the content described in one or more other embodiments. You can apply, combine, or substitute (even part of the content).

또한, 실시형태에서 기술하는 내용이란, 각각의 실시형태에 있어서, 다양한 도면을 사용하여 기술하는 내용, 또는 명세서에 기재되는 문장을 사용하여 기술하는 내용을 가리킨다.In addition, the content described in the embodiment refers to the content described using various drawings or the content described using sentences described in the specification in each embodiment.

또한, 어떤 하나의 실시형태에 있어서 기술하는 도면(일부라도 좋음)은, 그 도면의 다른 부분, 그 실시형태에 있어서 기술하는 다른 도면(일부라도 좋음), 및/또는 하나 또는 복수의 다른 실시형태에 있어서 기술하는 도면(일부라도 좋음)에 대하여, 조합하는 것에 의하여, 더 많은 도면을 구성시킬 수 있다.In addition, a drawing (which may be a part) described in a certain embodiment may refer to other parts of the drawing, other drawings (which may be a part) described in that embodiment, and/or one or more other embodiments. By combining the drawings (even some) described in , more drawings can be formed.

(실시형태 1)(Embodiment 1)

본 실시형태에서는, 본 발명의 일 형태의 반도체 장치와, 그 제조 방법에 대하여 도면을 사용하여 설명한다.In this embodiment, a semiconductor device of one form of the present invention and its manufacturing method will be explained using drawings.

도 1의 (A), 도 1의 (B), 도 1의 (C)는, 본 발명의 일 형태의 트랜지스터(10)의 상면도 및 단면도이다. 도 1의 (A)는 상면도이고, 도 1의 (B)는 도 1의 (A)에 나타낸 일점쇄선 A1-A2간, 도 1의 (C)는 A3-A4간의 단면도이다. 또한, 도 1의 (A)에서는, 도면의 명료화를 위하여 일부의 요소를 확대, 축소, 또는 생략하여 도시하고 있다. 또한, 일점쇄선 A1-A2 방향을 채널 길이 방향, 일점쇄선 A3-A4 방향을 채널 폭 방향이라고 호칭하는 경우가 있다.FIG. 1(A), FIG. 1(B), and FIG. 1(C) are top and cross-sectional views of a

트랜지스터(10)는, 기판(100)과, 절연층(110)과, 산화물 반도체층(121)과, 산화물 반도체층(122)과, 산화물 반도체층(123)과, 소스 전극층(130)과, 드레인 전극층(140)과, 게이트 절연층(150)과, 게이트 전극층(160)과, 절연층(170)과, 절연층(175)을 가진다. 절연층(110)은, 기판(100) 위에 형성된다. 산화물 반도체층(121)은, 절연층(110) 위에 형성된다. 산화물 반도체층(122)은, 산화물 반도체층(121) 위에 형성된다. 소스 전극층(130) 및 드레인 전극층(140)은, 산화물 반도체층(122) 위에 형성되고, 산화물 반도체층(122)과 전기적으로 접속한다. 절연층(170)은, 절연층(110), 소스 전극층(130), 드레인 전극층(140) 위에 형성되고, 산화물 반도체층(121), 산화물 반도체층(122)의 측면과 접촉한다. 절연층(175)은, 절연층(170) 위에 형성되고, 측면부에 있어서 산화물 반도체층(123)과 접촉한다. 산화물 반도체층(123)은, 산화물 반도체층(122) 위에 형성된다. 또한, 산화물 반도체층(123)은 절연층(170)의 측면, 절연층(175)의 측면, 소스 전극층(130)의 측면, 및 드레인 전극층(140)의 측면과 접촉한다. 게이트 절연층(150)은, 산화물 반도체층(123) 위에 형성된다. 게이트 전극층(160)은, 게이트 절연층(150) 위에 형성된다.The

또한, 도 1의 (B)에 있어서, 게이트 전극층(160)은 단층의 예를 도시하였지만 후술하는 게이트 전극층(161) 및 게이트 전극층(162)의 적층이어도 좋다. 트랜지스터(10)에 포함되는 산화물 반도체층(123) 및 게이트 절연층(150)의 단부는, 게이트 전극층(160)보다 외측에 위치한다. 또한, 상술한 구조는, 산화물 반도체층(122) 및 산화물 반도체층(123)과, 소스 전극층(130) 및 드레인 전극층(140)이 접촉하기 때문에, 트랜지스터(10)의 동작 시에 산화물 반도체층(121), 산화물 반도체층(122), 및 산화물 반도체층(123) 내에 발생되는 열에 대하여, 방열 효과가 높은 특징을 가진다.Additionally, in Figure 1(B), the example of the

또한, 트랜지스터(10)는, 절연층(170)이 되는 제 2 절연막을 성막할 때에, 절연층(110)과의 계면에 절연층(110)의 재료와 제 2 절연막의 재료, 또한 제 2 절연막의 성막 시에 사용한 가스 등을 가진 혼합층이 형성되고, 당해 혼합층 또는 절연층(110)에 산소(과잉 산소, exO라고 함)가 첨가된다. 또한, 가열 처리를 행함으로써 당해 산소가 산화물 반도체층(121) 및 산화물 반도체층(122)까지 확산되어, 산화물 반도체층(121), 산화물 반도체층(122) 내에 존재하는 산소 결손에 대하여 당해 산소가 보전할 수 있다. 이에 의하여, 트랜지스터 특성(예를 들어, 문턱 전압, 신뢰성 등)을 향상시킬 수 있다.In addition, when the