KR102615142B1 - Boost power factor correction convertor based on model predictive current control and method for operating thereof - Google Patents

Boost power factor correction convertor based on model predictive current control and method for operating thereofDownload PDFInfo

- Publication number

- KR102615142B1 KR102615142B1KR1020230064930AKR20230064930AKR102615142B1KR 102615142 B1KR102615142 B1KR 102615142B1KR 1020230064930 AKR1020230064930 AKR 1020230064930AKR 20230064930 AKR20230064930 AKR 20230064930AKR 102615142 B1KR102615142 B1KR 102615142B1

- Authority

- KR

- South Korea

- Prior art keywords

- power factor

- current

- factor correction

- boost power

- cost function

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/42—Circuits or arrangements for compensating for or adjusting power factor in converters or inverters

- H02M1/4208—Arrangements for improving power factor of AC input

- H02M1/4225—Arrangements for improving power factor of AC input using a non-isolated boost converter

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/0003—Details of control, feedback or regulation circuits

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/0096—Means for increasing hold-up time, i.e. the duration of time that a converter's output will remain within regulated limits following a loss of input power

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/08—Circuits specially adapted for the generation of control voltages for semiconductor devices incorporated in static converters

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/14—Arrangements for reducing ripples from DC input or output

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02B—CLIMATE CHANGE MITIGATION TECHNOLOGIES RELATED TO BUILDINGS, e.g. HOUSING, HOUSE APPLIANCES OR RELATED END-USER APPLICATIONS

- Y02B70/00—Technologies for an efficient end-user side electric power management and consumption

- Y02B70/10—Technologies improving the efficiency by using switched-mode power supplies [SMPS], i.e. efficient power electronics conversion e.g. power factor correction or reduction of losses in power supplies or efficient standby modes

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Dc-Dc Converters (AREA)

- Rectifiers (AREA)

Abstract

Translated fromKoreanDescription

Translated fromKorean본 발명은 모델 예측 전류 제어(Model Pridictive Current Control: MPCC) 기반의 부스트(boost) 역률 보정(Power Factor Correction: PFC) 변환기(convertor) 및 그의 동작 방법에 관한 것이다.The present invention relates to a boost power factor correction (PFC) converter based on Model Predictive Current Control (MPCC) and a method of operating the same.

다양한 비선형 부하의 증가에 따라 전력 품질 확보(예: 고조파를 줄여주며 안정적인 출력을 제공)의 중요성이 대두됨에 따라, 역률 보정(Power Factor Correction: PFC) 변환기를 이용하는 전자 장치들이 증가하고 있다. 한편, 다양한 방식의 역률 보정 변환기들 중 부스트 역률 보정 변환기가 널리 사용되고 있다. 이는 구조가 간단하며 입력 전류의 전체 고조파 왜곡(Total Harmonic Distortion: THD)이 낮고 넓은 범위의 동작에서 역률과 효율이 높으며 계통 왜란에도 출력 전압을 유지할 수 있기 때문이다.As the importance of securing power quality (e.g., reducing harmonics and providing stable output) increases with the increase in various non-linear loads, the number of electronic devices using power factor correction (PFC) converters is increasing. Meanwhile, among various types of power factor correction converters, boost power factor correction converters are widely used. This is because the structure is simple, the total harmonic distortion (THD) of the input current is low, the power factor and efficiency are high in a wide range of operation, and the output voltage can be maintained even during grid disturbance.

일반적으로, 상기 부스트 역률 보정 변환기는 인덕터 전류의 평균 값을 이용하는 평균 전류 모드 제어를 통해 동작한다. 이는 노이즈와 왜란에 강하기 때문이다. 하지만 평균 전류 모드 제어는 입력 전원의 왜곡에 취약하다는 단점이 있다. 이를 극복하기 위해, 입력 전압의 주파수와 동일한 정현파 기준 전류를 내부적으로 생성하는 예측 전류 모드 제어(Predictive Current Mode Control: PCMC)가 제안되었다. 상기 예측 전류 모드 제어는 예측된 정현파 전류 값을 기반으로 동작하여 입력 전원의 왜곡에 강인하다.Typically, the boost power factor correction converter operates through average current mode control using the average value of the inductor current. This is because it is resistant to noise and disturbance. However, average current mode control has the disadvantage of being vulnerable to distortion of the input power. To overcome this, predictive current mode control (PCMC), which internally generates a sinusoidal reference current equal to the frequency of the input voltage, has been proposed. The predicted current mode control operates based on the predicted sinusoidal current value and is robust to distortion of input power.

하지만, 상기 평균 전류 모드 제어 및 상기 예측 전류 모드 제어는 모두 고정된 스위칭 주파수를 사용하여 효율 개선에 한계가 있다. 이를 보완하기 위해, 첨두 전압 또는 영 전압 부근에서 스위칭을 멈추어 효율을 개선하는 부분(Partial) 스위칭 방식이 고안되었다. 하지만, 상기 부분 스위칭 방식은 전체 고조파 왜곡(THD)이 증가하며, 첨두 전압 부근에서 스위칭을 멈추면 승압이 불가하고, 영 전압 부근에서 스위칭을 멈추면 전체 고조파 왜곡(THD) 증가 대비 효율 개선이 미비하다는 단점이 존재한다.However, both the average current mode control and the predicted current mode control use a fixed switching frequency, so there is a limit to improving efficiency. To compensate for this, a partial switching method was designed to improve efficiency by stopping switching near peak voltage or zero voltage. However, the partial switching method increases total harmonic distortion (THD), and if switching is stopped near the peak voltage, step-up is not possible. If switching is stopped near zero voltage, efficiency improvement is insufficient compared to the increase in total harmonic distortion (THD). There is a downside to this.

한편, 전력 변환기에 포함되는 수동 소자의 부피를 줄이고 효율을 개선하기 위해, 2상의 역률 보정 변환 회로를 병렬로 연결하고, 위상을 천이할 수 있는 위상 폭 변조기(Pulse Width Modulator: PWM)를 이용하여 병렬 연결된 2상의 역률 보정 변환 회로에 상이한 위상을 가지는 전원을 각각 공급하여 전류 리플을 저감하는 인터리빙(interleaving) 기법이 고안되었다. 상기 인터리빙 기법을 적용시키는 경우 부스트 역률 보정 변환기는 위상이 다른 전류 간의 상쇄효과가 발생하여 스위칭 주파수가 증가하는 동시에 전류 리플이 저감되어 전체 고조파 왜곡(THD)을 낮출 수 있다. 하지만, 모델 예측 전류 제어 기반의 부스트 역률 보정 변환기는 위상 폭 변조기를 포함하지 않아 종래의 인터리빙 기법을 적용(즉, 2상의 역률 보정 변환 회로에 위상이 다른 전원을 각각 공급)할 수 없다는 문제점이 존재한다.Meanwhile, in order to reduce the volume of passive elements included in the power converter and improve efficiency, two-phase power factor correction conversion circuits are connected in parallel and a phase width modulator (PWM) that can shift the phase is used. An interleaving technique was designed to reduce current ripple by supplying power with different phases to a two-phase power factor correction conversion circuit connected in parallel. When applying the interleaving technique, the boost power factor correction converter generates a canceling effect between currents of different phases, increasing the switching frequency and reducing current ripple, thereby lowering total harmonic distortion (THD). However, the model-predicted current control-based boost power factor correction converter does not include a phase width modulator, so there is a problem in that the conventional interleaving technique cannot be applied (i.e., supplying power with different phases to the two-phase power factor correction converter circuit). do.

본 발명의 목적은, 상술한 문제점을 해결하기 위한 것으로, 스위칭 주파수를 가변하여 입력 전압의 왜곡에 대한 강건성 확보 및 효율을 개선(예: 스위칭 손실을 감소)할 수 있는 모델 예측 전류 제어 기반의 부스트 역률 보정 변환기 및 그의 동작 방법을 제공하는데 있다.The purpose of the present invention is to solve the above-mentioned problems, and a model-predicted current control-based boost that can secure robustness against distortion of the input voltage and improve efficiency (e.g., reduce switching loss) by varying the switching frequency. The object is to provide a power factor correction converter and a method of operating the same.

본 발명의 다른 목적은 위상 폭 변조기 없이, 2상의 부스트 역률 보정 변환 회로 중 일부의 샘플링 주기를 가변하여 전류 리플을 상쇄할 수 있는 모델 예측 전류 제어 기반의 부스트 역률 보정 변환기 및 그의 동작 방법을 제공하는데 있다.Another object of the present invention is to provide a boost power factor correction converter based on model predicted current control that can offset current ripple by varying the sampling period of a portion of a two-phase boost power factor correction converter circuit without a phase width modulator, and a method of operating the same. there is.

본 발명의 일 실시 예에 따른 모델 예측 전류 제어 기반의 부스트 역률 보정 변환기(boost power factor correction convertor)의 동작 방법은 입력 전압 및 출력 전압에 기초하여, 기준 전류를 산출하는 단계; 스위칭 소자가 온 상태일 때 다음 주기에 상기 인덕터에 흐를 것으로 예측되는 제1 예측 전류를 산출하는 단계; 상기 스위칭 소자가 오프 상태일 때 상기 다음 주기에 상기 인덕터에 흐를 것으로 예측되는 제2 예측 전류를 산출하는 단계; 상기 제1 예측 전류와 상기 기준 전류의 오차 및 상기 제2 예측 전류와 상기 기준 전류의 오차에 기초하여 최적의 비용 함수를 선정하는 단계; 및 상기 선정된 최적의 비용 함수에 기초하여 상기 스위칭 소자의 스위칭을 제어하는 단계를 포함할 수 있다.A method of operating a boost power factor correction convertor based on model predicted current control according to an embodiment of the present invention includes calculating a reference current based on an input voltage and an output voltage; calculating a first predicted current expected to flow in the inductor in the next cycle when the switching element is in an on state; calculating a second predicted current expected to flow in the inductor in the next cycle when the switching element is in an off state; selecting an optimal cost function based on an error between the first predicted current and the reference current and an error between the second predicted current and the reference current; And it may include controlling switching of the switching element based on the selected optimal cost function.

상기 최적의 비용 함수를 선정하는 단계는 상기 제1 예측 전류와 상기 기준 전류의 오차의 절대값을 상기 스위칭 소자가 온 상태일 때의 제1 비용함수로 결정하는 단계; 상기 제2 예측 전류와 상기 기준 전류의 오차의 절대 값을 상기 스위칭 소자가 오프 상태일 때 제2 비용함수로 결정하는 단계; 및 상기 제1 비용함수 및 상기 제2 비용함수 중 작은 비용함수를 상기 최적의 비용함수로 선정하는 단계를 포함할 수 있다.Selecting the optimal cost function includes determining an absolute value of an error between the first prediction current and the reference current as a first cost function when the switching element is in an on state; determining an absolute value of an error between the second predicted current and the reference current as a second cost function when the switching element is in an off state; and selecting a smaller cost function among the first cost function and the second cost function as the optimal cost function.

상기 스위칭 소자의 스위칭을 제어하는 단계는 상기 제1 비용 함수가 상기 제2 비용 함수보다 큰 경우 상기 스위칭 소자를 오프하는 단계; 및 상기 제1 비용 함수가 상기 제2 비용 함수보다 작은 경우 상기 스위칭 소자를 온하는 단계를 포함할 수 있다.Controlling switching of the switching device may include turning off the switching device when the first cost function is greater than the second cost function; and turning on the switching element when the first cost function is smaller than the second cost function.

상기 제1 예측 전류는 상기 인덕터의 현재 전류와 상기 입력 전압과 샘플링 주기의 곱을 상기 인덕터의 인덕턴스로 나눈 값의 합이고, 상기 제2 예측 전류는 상기 인덕터의 현재 전류와 상기 입력 전압과 상기 출력 전압의 차와 상기 샘플링 주기의 곱을 상기 인덕터의 인덕턴스로 나눈 값의 합이다.The first predicted current is the sum of the current current of the inductor, the product of the input voltage and the sampling period divided by the inductance of the inductor, and the second predicted current is the current current of the inductor, the input voltage and the output voltage. It is the sum of the difference between the product of the sampling period divided by the inductance of the inductor.

상기 기준 전류를 산출하는 단계는 위상 고정 루프를 통해 상기 입력 전압을 정현파로 변환하는 단계; 전압 제어기를 통해 상기 출력 전압과 기준 전압의 차인 에러 값을 이득 값으로 변환하는 단계; 및 상기 정현파 및 상기 이득 값을 곱하여 상기 기준 전류를 산출하는 단계를 포함할 수 있다.Calculating the reference current includes converting the input voltage into a sinusoidal wave through a phase-locked loop; Converting an error value that is the difference between the output voltage and a reference voltage into a gain value through a voltage controller; and calculating the reference current by multiplying the sinusoidal wave and the gain value.

본 발명의 일 실시 예에 따른 모델 예측 전류 제어 기반의 부스트 역률 보정 변환기(boost power factor correction convertor)는 인덕터, 스위칭 소자, 다이오드, 및 캐패시터를 포함하는 부스트 역률 보정 변환 회로; 및 상기 부스트 역률 보정 변환 회로의 입력 전압 및 출력 전압에 기초하여, 기준 전류를 산출하고, 상기 스위칭 소자가 온 상태일 때 다음 주기에 상기 인덕터에 흐를 것으로 예측되는 제1 예측 전류를 산출하고, 상기 스위칭 소자가 오프 상태일 때 상기 다음 주기에 상기 인덕터에 흐를 것으로 예측되는 제2 예측 전류를 산출하고, 상기 제1 예측 전류와 상기 기준 전류의 오차 및 상기 제2 예측 전류와 상기 기준 전류의 오차에 기초하여 최적의 비용 함수를 선정하며, 상기 선정된 최적의 비용 함수에 기초하여 상기 스위칭 소자의 스위칭을 제어하는 제어부를 포함할 수 있다.A boost power factor correction convertor based on model predicted current control according to an embodiment of the present invention includes a boost power factor correction conversion circuit including an inductor, a switching element, a diode, and a capacitor; and calculating a reference current based on the input voltage and output voltage of the boost power factor correction conversion circuit, and calculating a first predicted current predicted to flow in the inductor in the next cycle when the switching element is in an on state, When the switching element is in the off state, a second predicted current predicted to flow in the inductor in the next cycle is calculated, and the error between the first predicted current and the reference current and the error between the second predicted current and the reference current are calculated. It may include a control unit that selects an optimal cost function based on the selected optimal cost function and controls switching of the switching element based on the selected optimal cost function.

상기 제어부는 상기 제1 예측 전류와 상기 기준 전류의 오차의 절대값을 상기 스위칭 소자가 온 상태일 때의 제1 비용함수로 결정하고, 상기 제2 예측 전류와 상기 기준 전류의 오차의 절대 값을 상기 스위칭 소자가 오프 상태일 때 제2 비용함수로 결정하고, 및 상기 제1 비용함수 및 상기 제2 비용함수 중 작은 비용함수를 상기 최적의 비용함수로 선정할 수 있다.The control unit determines the absolute value of the error between the first predicted current and the reference current as the first cost function when the switching element is in the on state, and determines the absolute value of the error between the second predicted current and the reference current. When the switching element is in an off state, a second cost function may be determined, and a smaller cost function among the first cost function and the second cost function may be selected as the optimal cost function.

상기 제어부는 상기 제1 비용 함수가 상기 제2 비용 함수보다 큰 경우 상기 스위칭 소자를 오프하고, 및 상기 제1 비용 함수가 상기 제2 비용 함수보다 작은 경우 상기 스위칭 소자를 온할 수 있다.The control unit may turn off the switching element when the first cost function is greater than the second cost function, and may turn on the switching element when the first cost function is smaller than the second cost function.

상기 제어부는 상기 인덕터의 현재 전류와 상기 입력 전압과 샘플링 주기의 곱을 상기 인덕터의 인덕턴스로 나누어 상기 제1 예측 전류를 산출하고, 및 상기 인덕터의 현재 전류와 상기 입력 전압과 상기 출력 전압의 차와 상기 샘플링 주기의 곱을 상기 인덕터의 인덕턴스로 나누어 상기 제2 예측 전류를 산출할 수 있다.The control unit calculates the first predicted current by dividing the product of the current current of the inductor, the input voltage, and the sampling period by the inductance of the inductor, and the difference between the current current of the inductor, the input voltage, and the output voltage and the The second predicted current can be calculated by dividing the product of the sampling period by the inductance of the inductor.

상기 제어부는 위상 고정 루프를 통해 상기 입력 전압을 정현파로 변환하고, 전압 제어기를 통해 상기 출력 전압과 기준 전압의 차인 에러 값을 이득 값으로 변환하고, 및 상기 정현파 및 상기 이득 값을 곱하여 상기 기준 전류를 산출할 수 있다.The control unit converts the input voltage into a sinusoidal wave through a phase-locked loop, converts an error value that is the difference between the output voltage and the reference voltage into a gain value through a voltage controller, and multiplies the sinusoidal wave and the gain value to obtain the reference current. can be calculated.

본 발명의 일 실시 예에 따른 2상 부스트 역률 보정 변환 회로를 포함하는 모델 예측 전류 제어 기반의 부스트 역률 보정 변환기(boost power factor correction convertor)의 동작 방법은 입력 전압 및 출력 전압에 기초하여, 기준 전류를 산출하는 단계; 상기 2상의 부스트 역률 보정 변환 회로 각각에 대하여, 다음 주기의 인덕터 전류를 예측하는 단계; 상기 예측된 인덕터 전류와 상기 기준 전류의 오차에 기초하여 최적의 비용 함수를 선정하는 단계; 상기 선정된 최적의 비용 함수에 기초하여, 상기 2상의 부스트 역률 보정 변환 회로 중 하나에 포함된 제1 스위칭 소자의 스위칭을 제어하는 단계; 및 상기 선정된 최적의 비용 함수에 샘플링 타임 가중치를 적용하고, 상기 샘플링 타임 가중치가 적용된 비용 함수에 기초하여, 다른 하나의 부스트 역률 보정 변환 회로에 포함된 제2 스위칭 소자의 스위칭을 제어하는 단계를 포함할 수 있다.A method of operating a boost power factor correction convertor based on model prediction current control including a two-phase boost power factor correction conversion circuit according to an embodiment of the present invention is based on the input voltage and output voltage, and the reference current Calculating; predicting the inductor current of the next cycle for each of the two-phase boost power factor correction conversion circuits; selecting an optimal cost function based on an error between the predicted inductor current and the reference current; Controlling switching of a first switching element included in one of the two-phase boost power factor correction conversion circuit based on the selected optimal cost function; and applying a sampling time weight to the selected optimal cost function and controlling switching of a second switching element included in another boost power factor correction conversion circuit based on the cost function to which the sampling time weight is applied. It can be included.

상기 샘플링 타임 가중치는 상기 2상의 부스트 역률 보정 변환 회로에 포함된 제1 및 제2 인덕터들의 전류 리플의 합이 최소가 되는 값이다.The sampling time weight is a value that minimizes the sum of current ripples of the first and second inductors included in the two-phase boost power factor correction conversion circuit.

상기 샘플링 타임 가중치는 0 보다 크고 0.5 보다 작은 값을 가진다.The sampling time weight has a value greater than 0 and less than 0.5.

본 발명의 일 실시 예에 따른 모델 예측 전류 제어 기반의 부스트 역률 보정 변환기(boost power factor correction convertor)는 2상의 부스트 역률 보정 변환 회로; 및 상기 부스트 역률 보정 변환기의 입력 전압 및 출력 전압에 기초하여 기준 전류를 산출하고, 상기 2상의 부스트 역률 보정 변환 회로 각각에 대하여, 다음 주기의 인덕터 전류를 예측하고, 상기 예측된 인덕터 전류와 상기 기준 전류의 오차에 기초하여 최적의 비용 함수를 선정하고, 상기 선정된 최적의 비용 함수에 기초하여 상기 2상의 부스트 역률 보정 변환 회로 중 하나에 포함된 제1 스위칭 소자의 스위칭을 제어하고, 상기 선정된 최적의 비용 함수에 샘플링 타임 가중치를 적용하고, 상기 샘플링 타임 가중치가 적용된 비용 함수에 기초하여 다른 하나의 부스트 역률 보정 변환 회로에 포함된 제2 스위칭 소자의 스위칭을 제어하는 제어부를 포함할 수 있다.A boost power factor correction convertor based on model predicted current control according to an embodiment of the present invention includes a two-phase boost power factor correction converter; and calculate a reference current based on the input voltage and output voltage of the boost power factor correction converter, predict the inductor current of the next cycle for each of the two-phase boost power factor correction converter, and calculate the predicted inductor current and the reference. Selecting an optimal cost function based on the current error, controlling switching of the first switching element included in one of the two-phase boost power factor correction conversion circuit based on the selected optimal cost function, and controlling the switching of the first switching element included in the selected optimal cost function. It may include a control unit that applies a sampling time weight to the optimal cost function and controls switching of a second switching element included in another boost power factor correction conversion circuit based on the cost function to which the sampling time weight is applied.

상기 제어부는 상기 기준 전류를 산출하는 기준 전류 산출부; 및 상기 최적의 비용함수를 선정하는 모델 예측 전류 제어기를 포함할 수 있다.The control unit includes a reference current calculation unit that calculates the reference current; and a model prediction current controller that selects the optimal cost function.

상기 샘플링 타임 가중치는 상기 2상의 부스트 역률 보정 변환 회로에 포함된 제1 및 제2 인덕터들의 전류 리플의 합이 최소가 되는 값이다.The sampling time weight is a value that minimizes the sum of current ripples of the first and second inductors included in the two-phase boost power factor correction conversion circuit.

상기 샘플링 타임 가중치는 0 보다 크고 0.5 보다 작은 값을 가진다.The sampling time weight has a value greater than 0 and less than 0.5.

본 발명은 스위칭 주파수가 고정되지 않고, 스위칭 주파수가 가변됨에 따라 입력 전압의 왜곡에 대한 강건성 확보 및 전력 변환 효율을 개선(예: 스위칭 손실을 감소)할 수 있다. 또한, 본 발명은 시스템 모델 기반의 비용함수를 이용하여 부스트 역률 보정 변환기를 제어함에 따라, 제어이득 설계 및 조정 등이 필요 없고, 별도의 변조기(예: 위상 폭 변조기(PWM))를 요구하지 않아 비교적 간단한 구조를 가진다. 또한, 본 발명은 높은 전류가 흐르는 첨두 전압 부근에서 스위칭 주파수가 감소하여 별도의 회로나, 제어 방식을 추가하지 않고도 전력 변환 효율을 개선할 수 있다.In the present invention, since the switching frequency is not fixed and the switching frequency is variable, it is possible to secure robustness against distortion of the input voltage and improve power conversion efficiency (e.g., reduce switching loss). In addition, the present invention controls the boost power factor correction converter using a system model-based cost function, so there is no need for control gain design and adjustment, and a separate modulator (e.g., phase width modulator (PWM)) is not required. It has a relatively simple structure. In addition, the present invention reduces the switching frequency near the peak voltage where high current flows, thereby improving power conversion efficiency without adding a separate circuit or control method.

한편, 본 발명은, 위상 폭 변조기(PWM)없이, 2상의 부스트 역률 보정 변환 회로 중 일부의 샘플링 주기를 가변하는 기법을 통해 전류 리플을 상쇄할 수 있다. 이로 인하여, 본 발명은 별도의 변조기 없이 간편하게 인터리빙 효과를 제공할 수 있다.Meanwhile, the present invention can cancel out current ripple through a technique of varying the sampling period of some of the two-phase boost power factor correction conversion circuit without a phase width modulator (PWM). Because of this, the present invention can easily provide an interleaving effect without a separate modulator.

도 1은 본 발명의 일 실시 예에 따른 모델 예측 전류 제어 기반의부스트 역률 보정 변환기의 구성을 도시한 도면이다.

도 2a는 본 발명의 일 실시 예에 따른 모델 예측 전류 제어 기반의부스트 역률 보정 변환기의 스위칭 소자가 온 상태일 때의 동작을 설명하기 위한 도면이다.

도 2b는 본 발명의 일 실시 예에 따른 모델 예측 전류 제어 기반의부스트 역률 보정 변환기의 스위칭 소자가 오프 상태일 때의 동작을 설명하기 위한 도면이다.

도 3은 본 발명의 일 실시 예에 따른 모델 예측 전류 제어 기반의부스트 역률 보정 변환기의 최적의 비용함수를 선정하는 방법을 설명하기 위한 도면이다.

도 4는 본 발명의 일 실시 예에 따른 모델 예측 전류 제어 기반의부스트 역률 보정 변환기의 최적의 비용함수를 기초로 스위칭을 제어하는 예를 도시한 도면이다.

도 5a는 본 발명 및 종래의 부스트 역률 보정 변환기의 스위칭 횟수를 비교하여 설명하기 위한 도면이다.

도 5b는 본 발명의 일 실시 예에 따른 모델 예측 전류 제어 기반의 부스트 역률 보정 변환기의 입력 전압과 입력 전류의 파형을 도시한 도면이다.

도 5c는 본 발명의 일 실시 예에 따른 모델 예측 전류 제어 기반의 부스트 역률 보정 변환기의 부하 변동 시 출력 전압과 입력 전류의 파형을 도시한 도면이다.

도 5d는 본 발명 및 종래의 부스트 역률 보정 변환기의 부하 변동에 따른 전력 변환 효율 및 역률을 도시한 도면이다.

도 6a는 본 발명의 다른 실시 예에 따른 모델 예측 전류 제어 기반의부스트 역률 보정 변환기의 구성을 도시한 도면이다.

도 6b는 본 발명의 다른 실시 예에 따른 모델 예측 전류 제어 기반의부스트 역률 보정 변환기의 제어부의 구성을 도시한 도면이다.

도 7a 및 도 7b는 본 발명의 다른 실시 예에 따른 제2 인덕터 전류 및 제2 인덕터 전류의 샘플링 주기를 도시한 도면이다.

도 8은 본 발명의 다른 실시 예에 따른 모델 예측 전류 제어 기반의부스트 역률 보정 변환기의 가중치에 따른 첨두 부근에서 평균 전류 리플율의 변화를 나타내는 도면이다.

도 9a는 본 발명에 따른 인터리빙 기법을 적용하지 않은 전체 입력 전류의 파형을 도시한 도면이다.

도 9b는 본 발명에 따른 인터리빙 기법을 적용한 후 전체 입력 전류의 파형을 도시한 도면이다.

도 9C는 본 발명에 따른 인터리빙 기법을 적용하기 전과 적용한 후 10차까지의 고조파 성분을 도시한 도면이다.

도 10은 본 발명의 다른 실시 예에 따른 모델 예측 전류 제어 기반의부스트 역률 보정 변환기의 인덕터 전류의 파형을 도시한 도면이다.1 is a model-predicted current control-based diagram according to an embodiment of the present invention.This diagram shows the configuration of a boost power factor correction converter.

Figure 2a shows model-predicted current control based on an embodiment of the present invention.This is a diagram to explain the operation when the switching element of the boost power factor correction converter is in the on state.

Figure 2b shows model-predicted current control based on an embodiment of the present invention.This is a diagram to explain the operation when the switching element of the boost power factor correction converter is in the off state.

Figure 3 shows model-predicted current control based on an embodiment of the present invention.This diagram is intended to explain how to select the optimal cost function of a boost power factor correction converter.

Figure 4 shows model-predicted current control-based according to an embodiment of the present invention.This diagram shows an example of switching control based on the optimal cost function of the boost power factor correction converter.

Figure 5a is a diagram for explaining the comparison of the switching number of the present invention and the conventional boost power factor correction converter.

Figure 5b is a diagram showing the waveforms of the input voltage and input current of the boost power factor correction converter based on model predicted current control according to an embodiment of the present invention.

Figure 5c is a diagram illustrating the waveforms of the output voltage and input current when the load changes of the boost power factor correction converter based on model predicted current control according to an embodiment of the present invention.

Figure 5d is a diagram showing power conversion efficiency and power factor according to load changes of the present invention and the conventional boost power factor correction converter.

Figure 6a shows model-predicted current control based on another embodiment of the present invention.This diagram shows the configuration of a boost power factor correction converter.

Figure 6b shows model-predicted current control based on another embodiment of the present invention.This diagram shows the configuration of the control unit of the boost power factor correction converter.

7A and 7B are diagrams showing a second inductor current and a sampling period of the second inductor current according to another embodiment of the present invention.

Figure 8 shows model predicted current control based on another embodiment of the present invention.This is a diagram showing the change in average current ripple rate near the peak according to the weight of the boost power factor correction converter.

Figure 9a is a diagram showing the waveform of the total input current without applying the interleaving technique according to the present invention.

Figure 9b is a diagram showing the waveform of the total input current after applying the interleaving technique according to the present invention.

Figure 9C is a diagram showing harmonic components up to the 10th order before and after applying the interleaving technique according to the present invention.

Figure 10 shows model-predicted current control-based according to another embodiment of the present invention.This diagram shows the waveform of the inductor current of the boost power factor correction converter.

이하, 첨부된 도면을 참조하여 본 발명의 바람직한 실시예를 상세히 설명한다. 본 발명의 이점 및 특징, 그리고 그것들을 달성하는 방법은 첨부되는 도면과 함께 상세하게 후술되어 있는 실시예들을 참조하면 명확해질 것이다. 그러나 본 발명은 이하에서 개시되는 실시예들에 한정되는 것이 아니라 서로 다른 다양한 형태로 구현될 것이며, 단지 본 실시예들은 본 발명의 개시가 완전하도록 하며, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 발명의 범주를 완전하게 알려주기 위해 제공되는 것이며, 본 발명은 청구항의 범주에 의해 정의될 뿐이다. 이하에서 동일한 참조 부호는 동일 구성 요소를 지칭한다.Hereinafter, preferred embodiments of the present invention will be described in detail with reference to the attached drawings. The advantages and features of the present invention and methods for achieving them will become clear by referring to the embodiments described in detail below along with the accompanying drawings. However, the present invention is not limited to the embodiments disclosed below and will be implemented in various different forms. The present embodiments only serve to ensure that the disclosure of the present invention is complete and that common knowledge in the technical field to which the present invention pertains is not limited. It is provided to fully inform those who have the scope of the invention, and the present invention is only defined by the scope of the claims. Hereinafter, like reference numerals refer to like components.

비록 제1, 제2 등이 다양한 소자, 구성요소 및/또는 섹션들을 서술하기 위해서 사용되나, 이들 소자, 구성요소 및/또는 섹션들은 이들 용어에 의해 제한되지 않음은 물론이다. 이들 용어들은 단지 하나의 소자, 구성요소 또는 섹션들을 다른 소자, 구성요소 또는 섹션들과 구별하기 위하여 사용하는 것이다. 따라서, 이하에서 언급되는 제1 소자, 제1 구성요소 또는 제1 섹션은 본 발명의 기술적 사상 내에서 제2 소자, 제2 구성요소 또는 제2 섹션일 수도 있음은 물론이다.Although first, second, etc. are used to describe various elements, elements and/or sections, it is understood that these elements, elements and/or sections are not limited by these terms. These terms are merely used to distinguish one element, element, or section from other elements, elements, or sections. Therefore, it goes without saying that the first element, first element, or first section mentioned below may also be a second element, second element, or second section within the technical spirit of the present invention.

본 명세서에서 사용된 용어는 실시예들을 설명하기 위한 것이며 본 발명을 제한하고자 하는 것은 아니다. 본 명세서에서, 단수형은 문구에서 특별히 언급하지 않는 한 복수형도 포함한다. 명세서에서 사용되는 "포함한다(comprises)" 및/또는 "이루어지다(made of)"는 언급된 구성요소, 단계, 동작 및/또는 소자는 하나 이상의 다른 구성요소, 단계, 동작 및/또는 소자의 존재 또는 추가를 배제하지 않는다.The terminology used herein is for describing embodiments and is not intended to limit the invention. As used herein, singular forms also include plural forms, unless specifically stated otherwise in the context. As used in the specification, “comprises” and/or “made of” refers to a referenced component, step, operation and/or element of one or more other components, steps, operations and/or elements. Does not exclude presence or addition.

다른 정의가 없다면, 본 명세서에서 사용되는 모든 용어(기술 및 과학적 용어를 포함)는 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 공통적으로 이해될 수 있는 의미로 사용될 수 있을 것이다. 또한, 일반적으로 사용되는 사전에 정의되어 있는 용어들은 명백하게 특별히 정의되어 있지 않는 한 이상적으로 또는 과도하게 해석되지 않는다.Unless otherwise defined, all terms (including technical and scientific terms) used in this specification may be used with meanings that can be commonly understood by those skilled in the art to which the present invention pertains. Additionally, terms defined in commonly used dictionaries are not interpreted ideally or excessively unless clearly specifically defined.

도 1은 본 발명의 일 실시 예에 따른 모델 예측 전류 제어 기반의부스트 역률 보정 변환기의 구성을 도시한 도면이고, 도 2a는 본 발명의 일 실시 예에 따른 모델 예측 전류 제어 기반의부스트 역률 보정 변환기의 스위칭 소자가 온 상태일 때의 동작을 설명하기 위한 도면이고, 도 2b는 본 발명의 일 실시 예에 따른 모델 예측 전류 제어 기반의부스트 역률 보정 변환기의 스위칭 소자가 오프 상태일 때의 동작을 설명하기 위한 도면이며, 도 3은 본 발명의 일 실시 예에 따른 모델 예측 전류 제어 기반의부스트 역률 보정 변환기의 최적의 비용함수를 선정하는 방법을 설명하기 위한 도면이고, 도 4는 본 발명의 일 실시 예에 따른 모델 예측 전류 제어 기반의부스트 역률 보정 변환기의 최적의 비용함수를 기초로 스위칭을 제어하는 예를 도시한 도면이다.1 is a model-predicted current control-based diagram according to an embodiment of the present invention.A diagram showing the configuration of a boost power factor correction converter, and Figure 2a is a diagram showing the model prediction current control based on an embodiment of the present invention.It is a diagram to explain the operation when the switching element of the boost power factor correction converter is in the on state, and FIG. 2b is a diagram showing the model prediction current control based on an embodiment of the present invention.This is a diagram to explain the operation when the switching element of the boost power factor correction converter is in the off state, and Figure 3 is a diagram showing the model prediction current control based on an embodiment of the present invention.It is a diagram to explain a method of selecting the optimal cost function of a boost power factor correction converter, and Figure 4 shows a model-predicted current control-based method according to an embodiment of the present invention.This diagram shows an example of switching control based on the optimal cost function of the boost power factor correction converter.

도 1 내지 도 4를 참조하면, 본 발명의 일 실시 예에 따른 모델 예측 전류 제어 기반의부스트 역률 보정 변환기(100)는 입력 전원(10), 정류부(15), 부하(20), 직류 링크 캐패시터(25), 부스트 역률 보정 변환 회로(110), 및 제어부(130)를 포함할 수 있다.1 to 4, model-predicted current control-based according to an embodiment of the present inventionThe boost power factor correction converter 100 may include an

부스트 역률 보정 변환 회로(110)는 교류의 입력 전원(10)을 직류 전원으로 변환하는 교류-직류(AC-DC) 컨버터일 수 있다. 부스트 역률 보정 변환 회로(110)는 인덕터(111), 스위칭 소자(112), 및 다이오드(113)를 포함할 수 있다. 이러한 부스트 역률 보정 변환 회로(110)는 알려진 구성으로 상세한 설명은 생략하기로 한다.The boost power factor

제어부(130)는 모델 예측 전류 제어 기반의부스트 역률 보정 변환기(100)의 동작을 제어할 수 있다. 제어부(130)는 기준 전류 산출부(120) 및 모델 예측 전류 제어기(125)를 포함할 수 있다.The

기준 전류 산출부(120)는 입력 전압 및 출력 전압에 기초하여 기준 전류(i_ref(k+1))를 산출할 수 있다. 기준 전류 산출부(120)의 위상고정루프(Phase Lock Loop: PLL)는 입력 전압(Vin(k))의 위상각을 검출하여 크기가 1인 정현파()(30)를 생성하여 출력한다. 여기서,는 입력전원 주파수(예: 50 Hz)이다. 한편, 기준 전류 산출부(120)의 전압 제어기(voltage controller)는 출력전압(Vo(k))과 기준전압(또는 전압 지령)(Vo_ref)의 차인 에러 값(e(k))을 입력 받아 이득 값(Vc(k))(40)을 출력한다. 여기서, 이득 값(Vc(k))은 기준 전류의 크기이다. 기준 전류 산출부(120)는 정현파()(30)와 이득 값(Vc(k))(40)을 곱하여 기준 전류(i_ref(k+1))를 산출한다.The reference

모델 예측 전류 제어기(125)는 스위칭 소자(112)의 온/오프를 제어할 수 있다. 예를 들어, 모델 예측 전류 제어기(125)는 스위칭 주파수에 기초하여 스위칭 소자(112)의 온/오프를 제어할 수 있다. 상기 스위칭 주파수는 가변될 수 있다. 예를 들어, 모델 예측 전류 제어기(125)는 예측 전류(iL(k+1)) 및 기준 전류(i_ref(k+1))를 비교하여 최적의 비용함수(gopt)를 선정하고, 선정된 최적의 비용 함수(gopt)에 기초하여 스위칭 소자(112)의 온/오프를 제어할 수 있다. 여기서, 상기 예측 전류(iL(k+1))는 스위칭 소자(112)가 온(ON) 상태일 때 인덕터(111)에 흐르는 제1 예측 전류(iL_on(k+1)) 및 스위칭 소자(112)가 오프(OFF) 상태일 때 인덕터(111)에 흐르는 제2 예측 전류(iL_off(k+1))를 포함할 수 있다.The model prediction

도 2a 및 도 2b를 참조하여 설명하면, 스위칭 소자(112)의 온 및 오프 시 부스트 역률 보정 변환 회로(110)의 인덕터(111)에 걸리는 전압은 각각 아래의 <식 1> 및 <식 2>와 같다. 아래의 아래의 <식 1> 및 <식 2>에서, "VL_ON(k)"는 k 시점에서 스위칭 소자(112)가 온(ON) 상태일 때 인덕터(111)의 전압을 의미하고, "VL_OFF(k)"는 k 시점에서 스위칭 소자(112)가 오프(OFF) 상태일 때 인덕터(111)의 전압을 의미하고, "L"은 인덕터(111)의 인덕턴스를 의미하고, "iL(k)"은 k 시점에서 인덕터(111)의 전류를 의미하고, "Vin(k)"는 K 시점의 입력 전압을 의미하고, "Vo(k)"는 K 시점의 출력 전압을 의미한다. 한편, 이하에서는 부스트 역률 보정 변환 회로(110)의 동작 모드를 연속 전도 모드로 가정하고, 직관적인 해석을 위해 인덕터(111)와 커패시터(25)의 등가 직렬 저항(ESR) 성분을 고려하지 않았다. 또한, 스위칭 주파수는 라인 주파수보다 빠르며, 출력 전압은 직류로 가정하였다.2A and 2B, the voltage applied to the

………………………… <식 1>… … … … … … … … … … <

……………… <식 2>… … … … … … <

상기 <식 1>을 참조하면, 스위칭 소자(112)가 온 상태일 때 인덕터(111)의 전압(VL_ON(k))은 입력 전압(Vin(k))과 동일하다. 한편, 상기 <식 2>를 참조하면, 스위칭 소자(112)가 오프 상태일 때 인덕터(111)의 전압(VL_OFF(k))은 입력 전압(Vin(k))에서 출력 전압(Vo(k))을 뺀 값을 가진다.Referring to <

상기 <식 1> 및 <식 2>에 아래의 <식 3>의 오일러 법칙을 적용하면, 다음 스위칭 주기의 제1 예측 전류(iL_on(k+1)) 및 제2 예측 전류(iL_off(k+1))는 각각 아래의 <식 4> 및 <식 5>와 같을 수 있다. 아래의 <식 4> 및 <식 5>에서, "iL(k+1)"은 k+1 시점에서 인덕터(111)의 전류를 의미하고, "TS"는 샘플링 타임(샘플링 주기)를 의미한다.Applying Euler's law of <Equation 3> below to <

………………………………… <식 3>… … … … … … … … … … … … … <Equation 3>

…………………………… <식 4>… … … … … … … … … … … <Equation 4>

…………………… <식 5>… … … … … … … … <Equation 5>

상기 <식 4>을 참조하면, 제1 예측 전류(iL_on(k+1))는, 도 3의 S310에 도시된 바와 같이, 현재 시점(k)의 인덕터 전류(iL(k))와 스위칭 소자(112)가 온 상태일 때의 인덕터 전류의 변화량(입력전압(Vin(k))과 샘플링 타임(Ts)의 곱을 인덕턴스(L)로 나눈 값)의 합으로 계산될 수 있다. 유사하게, 상기 <식 5>를 참조하면, 제2 예측 전류(iL_off(k+1))는, 도 3의 S320에 도시된 바와 같이, 현재 시점(k)의 인덕터 전류(iL(k))와 스위칭 소자(112)가 오프 상태일 때의 인덕터 전류의 변화량(입력전압(Vin(k))과 출력 전압(Vo(k))의 차와 샘플링 타임(Ts)의 곱을 인덕턴스(L)로 나눈 값)의 합으로 계산될 수 있다.Referring to <Equation 4>, the first predicted current (iL_on (k+1)) is the inductor current (iL (k)) at the current time point (k), as shown in S310 of FIG. 3. It can be calculated as the sum of the change in inductor current (the product of the input voltage (Vin (k)) and the sampling time (Ts) divided by the inductance (L)) when the switching

모델 예측 전류 제어기(125)는 예측 전류(iL(k+1)) 및 기준 전류(i_ref(k+1))에 기초하여 비용 함수를 구할 수 있다. 비용 함수는 스위칭 소자(112)가 온 상태 일때의 제1 비용 함수(gon) 및 스위칭 소자(112)가 오프 상태 일때의 제2 비용 함수(goff)를 포함할 수 있다. 상기 제1 비용 함수(gon) 및 제2 비용 함수(goff)는, 아래의 <식 6> 및 <식 7>을 통해, 산출될 수 있다.The model prediction

…………… <식 6>… … … … … <Equation 6>

…………… <식 7>… … … … … <Equation 7>

상기 <식 6> 및 <식 7>을 참조하면, 제1 비용 함수(gon)는 제1 예측 전류(iL_on(K+1))와 기준 전류(iL_ref(k+1))의 차의 절대값이고, 제2 비용 함수(goff)는 제2 예측 전류(iL_off(K+1))와 기준 전류(iL_ref(k+1))의 차의 절대값일 수 있다. 즉, 모델 예측 전류 제어기(125)는, 도 3의 S330 및 S350에 도시된 바와 같이, 제1 예측 전류(iL_on(K+1))와 기준 전류(iL_ref(k+1))의 차를 구하고, 차에 대한 절대값을 구하여 제1 비용 함수(gon)를 산출할 수 있다. 유사하게, 모델 예측 전류 제어기(125)는, 도 3의 S340 및 S350에 도시된 바와 같이, 제2 예측 전류(iL_off(K+1))와 기준 전류(iL_ref(k+1))의 차를 구하고, 차에 대한 절대값을 구하여 제2 비용 함수(goff)를 산출할 수 있다.Referring to <Equation 6> and <Equation 7>, the first cost function (gon ) is the difference between the first prediction current (iL_on (K+1)) and the reference current (iL_ref (k+1)) is the absolute value of , and the second cost function (goff ) may be the absolute value of the difference between the second predicted current (iL_off (K+1)) and the reference current (iL_ref (k+1)). That is, the model prediction

한편, 모델 예측 전류 제어기(125)는 제1 비용함수(gon) 및 제2 비용함수(goff)를 기초로, 최적의 비용함수(gopt)를 선정할 수 있다. 예를 들어, 모델 예측 전류 제어기(125)는, 도 3의 S360에 도시된 바와 같이, 제1 비용함수(gon) 및 제2 비용함수(goff)를 비교하여 비용함수가 최소가 되도록 최적의 비용함수(gopt)를 선정할 수 있다.Meanwhile, the model prediction

모델 예측 전류 제어기(125)는 상기 선정된 최적의 비용함수(gopt)를 기초로 스위칭 소자(112)의 스위칭을 제어할 수 있다. 예를 들어, 모델 예측 전류 제어기(125)는 아래의 <식 8>에 기초하여 스위칭 소자(112)의 스위칭을 제어할 수 있다.The model prediction

……………… <식 8>… … … … … … <Equation 8>

상기 <식 8>을 참조하면, 모델 예측 전류 제어기(125)는 제1 비용함수(gon)가 제2 비용함수(goff)보다 작거나 같으면, 스위칭 소자(112)를 온(즉, Q=1)하고, 제1 비용함수(gon)가 제2 비용함수(goff)보다 크면, 스위칭 소자(112)를 오프(즉, Q=0)하도록 제어할 수 있다. 예를 들어, 모델 예측 전류 제어기(125)는, 도 4에 도시된 바와 같이, "K+1" 시점에 제1 비용 함수(gon)가 제2 비용 함수(goff)보다 작아질 것으로 예측됨에 따라, "k - k+1"구간에서 스위칭 소자(112)를 온시키고, "K+2"내지 "K+4" 시점에 제1 비용 함수(gon)가 제2 비용 함수(goff)보다 커질 것으로 예측됨에 따라 "k+1 - k+2"구간, "k+2 - k+3"구간 및 "k+3 - k+4"구간에서 스위칭 소자(112)를 오프시킬 수 있다.Referring to <Equation 8>, if the first cost function (gon ) is less than or equal to the second cost function (goff ), the model prediction

도 5a는 본 발명 및 종래의 부스트 역률 보정 변환기의 스위칭 횟수를 비교하여 설명하기 위한 도면이다. 여기서, 종래의 부스트 역률 보정 변환기는 예측전류모드제어(Predictive Current Mode Control: PCMC)기반의 부스트 역률 보정 변환기이다.Figure 5a is a diagram for explaining the comparison of the switching number of the present invention and the conventional boost power factor correction converter. Here, the conventional boost power factor correction converter is a boost power factor correction converter based on Predictive Current Mode Control (PCMC).

도 5a를 참조하면, 종래의 부스트 역률 보정 변환기는, 식별 부호 510의 도면에 도시된 바와 같이, 모든 구간(A, B, C)에서 동일한 스위칭 횟수를 가진다. 이는 종래의 부스트 역률 보정 변환기는 고정된 샘플링 주파수를 가지기 때문이다.Referring to FIG. 5A, the conventional boost power factor correction converter has the same number of switching times in all sections (A, B, C), as shown in the figure at 510. This is because conventional boost power factor correction converters have a fixed sampling frequency.

이에 반하여, 본 발명은, 식별 부호 520의 도면에 도시된 바와 같이, 모든 구간(A, B, C)에서 종래의 부스트 역률 보정 변환기에 비하여 스위칭 횟수가 낮으며, 특히 첨두 구간(B)에서 스위칭 횟수가 다른 구간(A, C)에 비하여 약 50%로 감소함을 알 수 있다. 이는, 도 4에 도시된 바와 같이, 첨두 구간(B)에서 온 상태로 유지되는 구간(예: 1 개)보다 오프 상태로 유지되는 구간(예: 3개)이 많아지기 때문이다. 즉, 첨두 구간에서는 스위칭 주파수가 낮아지며, 스위칭 주파수가 낮아짐에 따라, 고정 스위칭 주파수를 이용하는 종래의 방식에 비하여 스위칭 손실을 줄일 수 있다. 이로 인하여, 본 발명은 전력 변환 효율 역시 개선할 수 있다.In contrast, the present invention, as shown in the drawing with identification symbol 520, has a lower number of switching compared to the conventional boost power factor correction converter in all sections (A, B, C), and especially switching in the peak section (B). It can be seen that the number of times decreases by about 50% compared to other sections (A, C). This is because, as shown in FIG. 4, the number of sections (e.g., three) maintained in the off state increases more than the section (e.g., one) maintained in the on state in the peak section (B). That is, the switching frequency is lowered in the peak section, and as the switching frequency is lowered, switching loss can be reduced compared to the conventional method using a fixed switching frequency. Because of this, the present invention can also improve power conversion efficiency.

도 5b는 본 발명의 일 실시 예에 따른 모델 예측 전류 제어 기반의 부스트 역률 보정 변환기의 입력 전압과 입력 전류의 파형을 도시한 도면이다.Figure 5b is a diagram showing the waveforms of the input voltage and input current of the boost power factor correction converter based on model predicted current control according to an embodiment of the present invention.

도 5b를 참조하면, 본 발명의 일 실시 예에 따른 모델 예측 전류 제어 기반의 부스트 역률 보정 변환기는 입력 전압의 왜곡에 강건하다. 상세하게는, 도 5b의 식별 부호 530의 도면과 540의 도면들을 비교하면, 입력 전압에 왜곡(입력 전압의 첨두 부분이 평평함)이 발생하더라도 입력 전류의 파형(502)이 왜곡이 없을 때의 입력 전류의 파형(501)과 거의 유사함을 알 수 있다. 이와 같이, 본 발명은 입력 전압의 왜곡에 강건함을 알 수 있다.Referring to FIG. 5B, the boost power factor correction converter based on model predicted current control according to an embodiment of the present invention is robust to distortion of the input voltage. In detail, comparing the drawings of identification number 530 and 540 in FIG. 5B, even if distortion occurs in the input voltage (the peak portion of the input voltage is flat), the input current waveform 502 has no distortion. It can be seen that it is almost similar to the current waveform 501. In this way, it can be seen that the present invention is robust to distortion of the input voltage.

도 5c는 본 발명의 일 실시 예에 따른 모델 예측 전류 제어 기반의 부스트 역률 보정 변환기의 부하 변동 시 출력 전압과 입력 전류의 파형을 도시한 도면이다.Figure 5c is a diagram illustrating the waveforms of the output voltage and input current when the load changes of the boost power factor correction converter based on model predicted current control according to an embodiment of the present invention.

도 5c를 참조하면, 본 발명의 일 실시 예에 따른 모델 예측 전류 제어 기반의 부스트 역률 보정 변환기는 부하가 급작스럽게 변경(예: 2.2KW -> 3.3kW)되더라도 출력 전압(Vo) 및 입력 전류(iin)가 일시적인 과도 상태(503)를 거쳐 정상 상태로 복원됨을 알 수 있다.Referring to FIG. 5C, the boost power factor correction converter based on model-predicted current control according to an embodiment of the present invention maintains the output voltage (Vo) and input current ( It can be seen that iin ) is restored to the normal state through a temporary transient state (503).

도 5d는 본 발명 및 종래의 부스트 역률 보정 변환기의 부하 변동에 따른 전력 변환 효율 및 역률을 도시한 도면이다.Figure 5d is a diagram showing power conversion efficiency and power factor according to load changes of the present invention and the conventional boost power factor correction converter.

도 5d를 참조하면, 본 발명의 일 실시 예에 따른 모델 예측 전류 제어 기반의 부스트 역률 보정 변환기는 종래의 역률 보정 변환기에 비하여 전력 변환 효율이 높고, 역률이 유사함을 알 수 있다. 예를 들어, 도 5d의 식별 부호 550의 도면을 참조하면, 600W의 부하에서 종래의 역률 보정 변환기(PCMC)는 전력 변환 효율이 약 97.71%이고, 본 발명(MPC)은 약 99.04%이다. 즉, 본 발명의 전력 변환 효율이 약 1.33% 만큼 더 좋음을 알 수 있다. 또한, 3.3kW의 부하에서 종래의 종래의 역률 보정 변환기(PCMC)는 전력 변환 효율이 약 96.98%이고, 본 발명(MPC)은 약 98.42%로, 본 발명의 전력 변환 효율이 약 1.44% 만큼 더 좋음을 알 수 있다.Referring to FIG. 5D, it can be seen that the boost power factor correction converter based on model predicted current control according to an embodiment of the present invention has higher power conversion efficiency and a similar power factor than a conventional power factor correction converter. For example, referring to the diagram at 550 in FIG. 5D, at a load of 600 W, the power conversion efficiency of the conventional power factor correction converter (PCMC) is about 97.71%, and that of the present invention (MPC) is about 99.04%. In other words, it can be seen that the power conversion efficiency of the present invention is better by about 1.33%. In addition, at a load of 3.3 kW, the power conversion efficiency of the conventional power factor correction converter (PCMC) is about 96.98%, that of the present invention (MPC) is about 98.42%, and the power conversion efficiency of the present invention is about 1.44% higher. You can tell it's good.

한편, 도 5d의 식별 부호 560의 도면을 참조하면, 600W의 부하에서 종래의 역률 보정 변환기(PCMC)는 역률이 약 0.9991이며, 본 발명(MPC)은 역률이 약 0.9920 이다. 비록, 600W의 부하에서 본 발명이 종래보다 상대적으로 낮은 역률을 보이나, 3.3kW의 부하에서 종래의 역률 보정 변환기(PCMC)는 역률이 약 0.9998 이며, 본 발명(MPC)은 역률이 약 0.9996로 거의 유사해짐을 알 수 있다.Meanwhile, referring to the drawing at identification number 560 in FIG. 5D, at a load of 600W, the power factor of the conventional power factor correction converter (PCMC) is about 0.9991, and the power factor of the present invention (MPC) is about 0.9920. Although, at a load of 600W, the power factor of the present invention is relatively lower than that of the prior art, at a load of 3.3kW, the power factor of the conventional power factor correction converter (PCMC) is about 0.9998, and the power factor of the present invention (MPC) is about 0.9996, which is almost You can see that they are similar.

도 6a는 본 발명의 다른 실시 예에 따른 모델 예측 전류 제어 기반의부스트 역률 보정 변환기의 구성을 도시한 도면이고, 도 6b는 본 발명의 다른 실시 예에 따른 모델 예측 전류 제어 기반의부스트 역률 보정 변환기의 제어부의 구성을 도시한 도면이고, 도 7a 및 도 7b는 본 발명의 다른 실시 예에 따른 제2 인덕터 전류 및 제2 인덕터 전류의 샘플링 주기를 도시한 도면이고, 도 8은 본 발명의 다른 실시 예에 따른 모델 예측 전류 제어 기반의부스트 역률 보정 변환기의 가중치에 따른 첨두 부근에서 평균 전류 리플율의 변화를 나타내는 도면이다.Figure 6a shows model-predicted current control based on another embodiment of the present invention.It is a diagram showing the configuration of a boost power factor correction converter, and Figure 6b is a diagram showing the model prediction current control based on another embodiment of the present invention.It is a diagram showing the configuration of the control unit of the boost power factor correction converter, and FIGS. 7A and 7B are diagrams showing the second inductor current and the sampling period of the second inductor current according to another embodiment of the present invention, and FIG. 8 is a diagram showing the configuration of the control unit of the boost power factor correction converter. Model-predictive current control-based according to another embodiment of the inventionThis is a diagram showing the change in average current ripple rate near the peak according to the weight of the boost power factor correction converter.

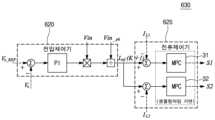

도 6a 내지 도 8을 참조하면, 본 발명의 다른 실시 예에 따른 모델 예측 전류 제어 기반의부스트 역률 보정 변환기(600)는 입력 전원(60), 정류부(65), 캐패시터(75), 2상의 부스트 역률 보정 변환 회로(610), 및 제어부(630)를 포함할 수 있다. 즉, 모델 예측 전류 제어 기반의부스트 역률 보정 변환기(600)는 인터리브드(interleaved) 부스트 역률 보정 변환기일 수 있다.6A to 8, model-predicted current control-based according to another embodiment of the present inventionThe boost power

2상의 부스트 역률 보정 변환 회로(610)는 제1 및 제2 부스트 역률 보정 변환 회로를 포함할 수 있다. 제1 부스트 역률 보정 변환 회로는 제1 인덕터(L1), 제1 스위칭 소자(S1) 및 제1 다이오드(D1)를 포함하고, 제2 부스트 역률 보정 변환 회로는 제2 인덕터(L2), 제2 스위칭 소자(S2) 및 제2 다이오드(D2)를 포함할 수 있다.The two-phase boost power factor

모델 예측 전류 제어 기반의부스트 역률 보정 변환기(600)의 제어부(630)는 도 1의 모델 예측 전류 제어 기반의부스트 역률 보정 변환기(100)와 유사하게 기준 전류 및 예측 전류를 기초로 최적의 비용함수를 선정하고, 선정된 최적의 비용함수를 기초로 스위칭 소자들(S1, S2)의 스위칭을 제어할 수 있다. 이를 위하여, 제어부(630)는, 도 6b에 도시된 바와 같이, 기준 전류(I_ref(k+1))를 산출하는 기준 전류 산출부(620) 및 최적의 비용함수를 선정하는 모델 예측 전류 제어기(625)를 포함할 수 있다. 상기 기준 전류 산출부(620)는 전압제어기를 이용하여 기준 전압 (Vo_ref)과 출력 전압 (Vo)간의 오차(예: 도 1의 에러 값(e(k))에 따른 기준 전류의 크기(예: 도 1의 이득 값(Vc(k))(40))를 계산하고, 입력 전압(Vin)(도 1의 정현파 신호(30))와 곱한 후 입력 전압의 크기(Vin_pk)로 나누어 입력 전압(Vin)과 동상이며 크기가 "1"인 기준 전류값(I_ref(k+1))을 계산할 수 있다.Based on model-predicted current controlThe

상기 모델 예측 전류 제어기(625)는 기준 전류값(I_ref(k+1))과 인덕터들(L1, L2)의 예측 전류(IL1, IL2) 값의 오차에 기초하여 비용 함수를 산출하고, 산출된 비용 함수가 최소화되도록 최적의 비용함수를 선정하고, 선정된 최적의 비용함수를 기초로 스위칭 소자(S1, S2)의 스위칭을 제어할 수 있다. 상기 모델 예측 전류 제어기(625)는 제1 스위칭 소자(S1)의 스위칭을 제어하기 위한 제1 최적의 비용함수를 선정하는 제1 모델 예측 전류 제어기(31) 및 제2 스위칭 소자(S2)의 스위칭을 제어하기 위한 제2 최적의 비용함수를 선정하는 제2 모델 예측 전류 제어기(32)를 포함할 수 있다.The model predicted

상기 제1 모델 예측 전류 제어기(31)는, 아래의 <식 9> 및 <식 10>을 통해, 제1 인덕터(L1)의 제1 예측 전류(iL1_on(k+1)) 및 제2 예측 전류(iL1_off(k+1))를 각각 산출할 수 있다. 또한, 상기 제1 모델 예측 전류 제어기(31)는, 아래의 <식 11> 및 <식 12>을 통해, 제1 인덕터(L1)의 제1 비용 함수(g1_on) 및 제2 비용 함수(g1_off)를 각각 산출할 수 있다.The first model predicted

………………… <식 9>… … … … … … … <Equation 9>

………… <식 10>… … … … <

………………… <식 11>… … … … … … … <Equation 11>

……………… <식 12>… … … … … … <Equation 12>

한편, 제2 모델 예측 전류 제어기(32)는, 아래의 <식 13> 및 <식 14>를 통해, 제2 인덕터(L2)의 제1 예측 전류(iL2_on(k+1)) 및 제2 예측 전류(iL2_off(k+1))를 각각 산출할 수 있다. 또한, 제2 모델 예측 전류 제어기(32)는, 아래의 <식 15> 및 <식 16>를 통해, 제2 인덕터(L2)의 제1 비용 함수(g2_on) 및 제2 비용 함수(g2_off)를 각각 산출할 수 있다.Meanwhile, the second model predicted

…………………… <식 13>… … … … … … … … <Equation 13>

………… <식 14>… … … … <Equation 14>

…………………… <식 15>… … … … … … … … <

……………… <식 16>… … … … … … <Equation 16>

상기 모델 예측 전류 제어기(625)는 제1 인덕터(L1) 및 제2 인덕터(L2)의 전류 간의 오차를 "0"(또는 최소)으로 제어하기 위해 비용함수를 조정할 수 있다. 상세하게는, 상기 모델 예측 전류 제어기(625)는 상기 제1 인덕터 전류(iL1)에 대한 비용함수 및 상기 제2 인덕터 전류(iL2)에 대한 비용함수에 기준 전류를 비교하는 시간인 샘플링타임 가중치(α)를 적용하여 샘플링 타임을 가변 할 수 있다. 이하에서는, 제2 인덕터 전류(iL2)에 대한 비용함수에 샘플링타임 가중치(α)를 적용하는 경우를 예로 하여 설명하기로 한다. 상기 제2 인덕터 전류(iL2)에 대한 비용함수에 샘플링 타임 가중치(α)를 적용하는 경우 제1 인덕터(L1)의 예측 전류(iL1(k+1)) 및 제2 인덕터(L2)의 예측 전류(iL2(k+1))는 각각 아래의 <식 17> 및 <식 18>과 같을 수 있다.The model prediction

…………… <식 17>… … … … … <Equation 17>

…………… <식 18>… … … … … <Equation 18>

이때, 제1 인덕터(L1)의 전류에 대한 최적 비용함수(g1_opt) 및 제2 인덕터(L2)의 전류에 대한 최적 비용함수(g2_opt)는 각각 아래의 <식 19> 및 <식 20>과 같을 수 있다.At this time, the optimal cost function (g1_opt) for the current of the first inductor (L1) and the optimal cost function (g2_opt) for the current of the second inductor (L2) are as <Equation 19> and <

……… <식 19>… … … <Equation 19>

……… <식 20>… … … <

상기 <식 17> 및 <식 18>을 참조하면, 제2 인덕터 전류(iL2)에 대한 비용함수에 가중치를 적용하는 것은 샘플링 주기(Ts)에 영향을 준다. 예를 들어, 제1 인덕터 전류(iL1)는, 도 7a에 도시된 바와 같이, 제1 샘플링 주기(TS1)를 가지고, 제2 인덕터 전류(iL2)는 제1 샘플링 주기(TS1)보다 큰 제2 샘플링 주기(TS2 = (1 + α)TS1)를 가질 수 있다. 한편, 제1 샘플링 주기(TS1) 및 제2 샘플링 주기(TS2)는, 도 7b에 도시된 일 예와 같이, 일정 시간(Ttotal) 경과 후 종료 시점이 같아질 수 있다.Referring to <Equation 17> and <Equation 18> above, applying a weight to the cost function for the second inductor current (iL2 ) affects the sampling period (Ts). For example, the first inductor current (iL1 ) has a first sampling period (TS1 ), and the second inductor current (iL2 ) has a first sampling period (TS1 ), as shown in Figure 7A. It may have a larger second sampling period (TS2 = (1 + α)TS1 ). Meanwhile, the first sampling period (TS1 ) and the second sampling period (TS2 ) may have the same end point after a certain period of time (Ttotal ), as shown in the example shown in FIG. 7B.

상기 가중치(α)는 제1 인덕터 전류(iL1)에 대한 비용함수(g1) 및 제2 인덕터 전류(iL2)에 대한 비용함수(g2)의 전류 리플의 합이 최소가 되는 값으로 결정될 수 있다. 즉, 상기 가중치(α)는 전체 주기(Ttotal)에서 제1 인덕터 전류(iL1) 및 제2 인덕터 전류(iL2)가 서로 상쇄되는 구간의 비율이 큰 값으로 결정될 수 있다.The weight (α) can be determined as a value that minimizes the sum of the current ripples of the cost function (g1) for the first inductor current (iL1 ) and the cost function (g2) for the second inductor current (iL2 ). there is. That is, the weight α may be determined as a value in which the ratio of the section in which the first inductor current (iL1 ) and the second inductor current (iL2 ) cancel each other out in the entire period (Ttotal ) is large.

상기 가중치(α)는 0 < α < 0.5의 값을 가질 수 있다. 이는 가중치(α)가 0.5일 때, 인덕터 포화 방지를 위한 전류 허용치가 100 %가 되기 때문이다. 즉, 가중치(α)가 0.5일 때 리플이 100 % 증가하기 때문이다. 예를 들어, 평균 전류 리플율은, 도 8에 도시된 바와 같이, 가중치(α)가 "0.001"보다 작으면 거의 감소하지 않고(즉, 가변량이 너무 작아 인터리빙 효과가 미비), 가중치(α)가 "0.001"보다 커지면 감소하기 시작하고, "0.005"에서 크게 감소하며, "0.02"보다 커지면, 제2 인덕터 전류(iL2)의 샘플링 주기의 가변으로 인해 발생되는 리플이 증가함에 따라, 증가하기 시작할 수 있다. 즉, 도 8과 같은 경우 상기 가중치(α)는 "0.02"로 선정될 수 있다. 한편, 도 8은 "입력 전압이 220Vrms, 출력 전압 380 Vdc, 로드 46.21 옴, 샘플링 주파수 100 kHz, 제1 인덕터 및 제2 인덕터 2.5mH 및 캐패시터 1000 uF의 조건에서 측정된 일 예일 뿐, 본 발명을 한정하지는 않는다.The weight (α) may have a value of 0 < α < 0.5. This is because when the weight (α) is 0.5, the current allowable value to prevent inductor saturation is 100%. In other words, when the weight (α) is 0.5, the ripple increases by 100%. For example, as shown in FIG. 8, the average current ripple rate hardly decreases when the weight α is less than “0.001” (i.e., the variable amount is too small to have an interleaving effect), and the weight α When becomes greater than "0.001", it begins to decrease, decreases significantly at "0.005", and when it becomes greater than "0.02", it increases as the ripple caused by the variation of the sampling period of the second inductor current (iL2 ) increases. You can start. That is, in the case shown in FIG. 8, the weight α may be selected as “0.02”. Meanwhile, Figure 8 is only an example measured under the conditions of "input voltage 220Vrms, output voltage 380 Vdc, load 46.21 ohm, sampling frequency 100 kHz, first inductor and second inductor 2.5mH, and capacitor 1000 uF, and the present invention It is not limited.

도 9a는 본 발명에 따른 인터리빙 기법을 적용하지 않은 전체 입력 전류의 파형을 도시한 도면이고, 도 9b는 본 발명에 따른 인터리빙 기법을 적용한 후 전체 입력 전류의 파형을 도시한 도면이며, 도 9C는 본 발명에 따른 인터리빙 기법을 적용하기 전과 적용한 후 10차까지의 고조파 성분을 도시한 도면이다.Figure 9A is a diagram showing the waveform of the total input current without applying the interleaving technique according to the present invention, Figure 9B is a diagram showing the waveform of the total input current after applying the interleaving technique according to the present invention, and Figure 9C is a diagram showing the waveform of the total input current after applying the interleaving technique according to the present invention. This diagram shows harmonic components up to the 10th order before and after applying the interleaving technique according to the present invention.

도 9a 및 도 9b를 참조하면, 본 발명에 따른 인터리빙 기법을 적용한 후 전체 입력 전류(iL_total)의 리플이 감소함(즉, 도 9b의 전체 입력 전류(iL_total)를 나타내는 곡선의 두께가 도 9a의 전체 입력 전류(iL_total)를 나타내는 곡선의 두께보다 얇음)을 알 수 있다.Referring to FIGS. 9A and 9B, after applying the interleaving technique according to the present invention, the ripple of the total input current (iL_total ) is reduced (i.e., the thickness of the curve representing the total input current (iL_total ) in FIG. 9B is shown in FIG. It can be seen that it is thinner than the thickness of the curve representing the total input current (iL_total ) of 9a.

도 9c를 참조하면, 본 발명에 따른 인터리빙 기법을 적용한 후 전체 고조파 왜곡(THD)이 감소함을 알 수 있다. 이는, 본 발명에 따른 인터리빙 기법을 적용한 후 두 상의 인덕터 전류간에 상쇄효과가 발생하여 주파수가 2배인 동시에 리플이 저감되기 때문이다.Referring to Figure 9c, it can be seen that the total harmonic distortion (THD) is reduced after applying the interleaving technique according to the present invention. This is because after applying the interleaving technique according to the present invention, an offset effect occurs between the inductor currents of the two phases, doubling the frequency and reducing ripple.

도 10은 본 발명의 다른 실시 예에 따른 모델 예측 전류 제어 기반의부스트 역률 보정 변환기의 인덕터 전류의 파형을 도시한 도면이다.Figure 10 shows model-predicted current control-based according to another embodiment of the present invention.This diagram shows the waveform of the inductor current of the boost power factor correction converter.

도 10을 참조하면, 제1 인덕터 전류(iL1) 및 제2 인덕터 전류(iL2)의 리플이 각각 1.05 A이고, 전체 인덕터 전류(iL_total)의 리플이 1.27A임을 알 수 있다. 이와 같이, 본 발명은 전체 인덕터 전류(iL_total)의 리플이 제1 인덕터 전류(iL1) 및 제2 인덕터 전류(iL2)의 리플의 합(2.1 A = 1.05 +1.05)보다 작음을 알 수 있다. 즉, 본 발명은 샘플링 타임의 가변을 통해 인덕터 전류의 리플이 상쇄되는 인터리브드 효과를 제공함을 알 수 있다.Referring to FIG. 10 , it can be seen that the ripples of the first inductor current (iL1 ) and the second inductor current (iL2 ) are each 1.05 A, and the ripple of the total inductor current (iL_total ) is 1.27A. In this way, in the present invention, it can be seen that the ripple of the total inductor current (iL_total ) is smaller than the sum of the ripples of the first inductor current (iL1 ) and the second inductor current (iL2 ) (2.1 A = 1.05 +1.05). there is. In other words, it can be seen that the present invention provides an interleaved effect in which the ripple of the inductor current is canceled through variation of the sampling time.

이상과 같이 본 발명의 도시된 실시 예를 참고하여 설명하고 있으나, 이는 예시적인 것들에 불과하며, 본 발명이 속하는 기술 분야의 통상의 지식을 가진 자라면 본 발명의 요지 및 범위에 벗어나지 않으면서도 다양한 변형, 변경 및 균등한 타 실시 예들이 가능하다는 것을 명백하게 알 수 있을 것이다. 따라서 본 발명의 진정한 기술적 보호 범위는 첨부된 청구범위의 기술적인 사상에 의해 정해져야 할 것이다.As described above, the present invention is described with reference to the illustrated embodiments, but these are merely illustrative examples, and those of ordinary skill in the art to which the present invention pertains can make various modifications without departing from the gist and scope of the present invention. It will be apparent that variations, modifications, and equivalent other embodiments are possible. Therefore, the true scope of technical protection of the present invention should be determined by the technical spirit of the appended claims.

Claims (17)

Translated fromKorean입력 전압 및 출력 전압에 기초하여, 기준 전류를 산출하는 단계;

상기 2상의 부스트 역률 보정 변환 회로 각각에 대하여, 상기 2상의 부스트 역률 보정 변환 회로 각각에 포함된 제1 인덕터 및 제2 인덕터 각각의 다음 주기의 인덕터 전류를 예측하는 단계;

상기 예측된 인덕터 전류와 상기 기준 전류의 오차에 기초하여 최적의 비용 함수를 선정하는 단계;

상기 선정된 최적의 비용 함수에 기초하여, 상기 2상의 부스트 역률 보정 변환 회로 중 하나에 포함된 제1 스위칭 소자의 스위칭을 제어하는 단계; 및

상기 선정된 최적의 비용 함수에 샘플링 타임 가중치를 적용하고, 상기 샘플링 타임 가중치가 적용된 비용 함수에 기초하여, 다른 하나의 부스트 역률 보정 변환 회로에 포함된 제2 스위칭 소자의 스위칭을 제어하는 단계를 포함하는 것을 특징으로 하는 방법.

In the operating method of a boost power factor correction convertor based on model predicted current control including a two-phase boost power factor correction conversion circuit,

calculating a reference current based on the input voltage and output voltage;

For each of the two-phase boost power factor correction conversion circuits, predicting inductor currents of the next cycle of each of the first inductor and the second inductor included in each of the two-phase boost power factor correction conversion circuits;

selecting an optimal cost function based on an error between the predicted inductor current and the reference current;

Controlling switching of a first switching element included in one of the two-phase boost power factor correction conversion circuit based on the selected optimal cost function; and

Applying a sampling time weight to the selected optimal cost function, and controlling switching of a second switching element included in another boost power factor correction conversion circuit based on the cost function to which the sampling time weight is applied. A method characterized by:

상기 샘플링 타임 가중치는

상기 2상의 부스트 역률 보정 변환 회로에 포함된 제1 및 제2 인덕터들의 전류 리플의 합이 최소가 되는 값으로 결정되는 것을 특징으로 하는 방법.

According to claim 11,

The sampling time weight is

A method characterized in that the sum of current ripples of the first and second inductors included in the two-phase boost power factor correction conversion circuit is determined to be the minimum value.

상기 샘플링 타임 가중치는

0 보다 크고 0.5 보다 작은 값을 가지는 것을 특징으로 하는 방법.

According to claim 11,

The sampling time weight is

A method characterized by having a value greater than 0 and less than 0.5.

제1 인덕터 및 제2 인덕터를 포함하는 2상의 부스트 역률 보정 변환 회로; 및

상기 부스트 역률 보정 변환기의 입력 전압 및 출력 전압에 기초하여 기준 전류를 산출하고, 상기 2상의 부스트 역률 보정 변환 회로 각각에 대하여, 상기 제1 인덕터 및 제2 인덕터 각각의 다음 주기의 인덕터 전류를 예측하고, 상기 예측된 인덕터 전류와 상기 기준 전류의 오차에 기초하여 최적의 비용 함수를 선정하고, 상기 선정된 최적의 비용 함수에 기초하여 상기 2상의 부스트 역률 보정 변환 회로 중 하나에 포함된 제1 스위칭 소자의 스위칭을 제어하고, 상기 선정된 최적의 비용 함수에 샘플링 타임 가중치를 적용하고, 상기 샘플링 타임 가중치가 적용된 비용 함수에 기초하여 다른 하나의 부스트 역률 보정 변환 회로에 포함된 제2 스위칭 소자의 스위칭을 제어하는 제어부를 포함하는 것을 특징으로 하는 부스트 역률 보정 변환기.

In a boost power factor correction convertor based on model predicted current control,

a two-phase boost power factor correction conversion circuit including a first inductor and a second inductor; and

Calculating a reference current based on the input voltage and output voltage of the boost power factor correction converter, predicting the inductor current of the next cycle of each of the first inductor and the second inductor for each of the two-phase boost power factor correction converter circuit, and , selecting an optimal cost function based on the error between the predicted inductor current and the reference current, and a first switching element included in one of the two-phase boost power factor correction conversion circuit based on the selected optimal cost function. Controls the switching, applies a sampling time weight to the selected optimal cost function, and switches the second switching element included in another boost power factor correction conversion circuit based on the cost function to which the sampling time weight is applied. A boost power factor correction converter comprising a control unit for controlling.

상기 제어부는

상기 기준 전류를 산출하는 기준 전류 산출부; 및

상기 최적의 비용함수를 선정하는 모델 예측 전류 제어기를 포함하는 것을 특징으로 하는 부스트 역률 보정 변환기.

According to claim 14,

The control unit

a reference current calculation unit that calculates the reference current; and

A boost power factor correction converter comprising a model prediction current controller that selects the optimal cost function.

상기 샘플링 타임 가중치는

상기 2상의 부스트 역률 보정 변환 회로에 포함된 제1 및 제2 인덕터들의 전류 리플의 합이 최소가 되는 값으로 결정되는 것을 특징으로 하는 부스트 역률 보정 변환기.

According to claim 14,

The sampling time weight is

A boost power factor correction converter, wherein the sum of current ripples of the first and second inductors included in the two-phase boost power factor correction conversion circuit is determined to be the minimum value.

상기 샘플링 타임 가중치는

0 보다 크고 0.5 보다 작은 값을 가지는 것을 특징으로 하는 부스트 역률 보정 변환기.According to claim 14,

The sampling time weight is

A boost power factor correction converter, characterized in that it has a value greater than 0 and less than 0.5.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020230064930AKR102615142B1 (en) | 2023-05-19 | 2023-05-19 | Boost power factor correction convertor based on model predictive current control and method for operating thereof |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020230064930AKR102615142B1 (en) | 2023-05-19 | 2023-05-19 | Boost power factor correction convertor based on model predictive current control and method for operating thereof |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR102615142B1true KR102615142B1 (en) | 2023-12-19 |

Family

ID=89385302

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020230064930AActiveKR102615142B1 (en) | 2023-05-19 | 2023-05-19 | Boost power factor correction convertor based on model predictive current control and method for operating thereof |

Country Status (1)

| Country | Link |

|---|---|

| KR (1) | KR102615142B1 (en) |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20140313795A1 (en)* | 2013-04-17 | 2014-10-23 | The Regents Of The University Of Michigan | Single phase bi-directional ac-dc converter with reduced passive components size and common mode electro-magnetic interference |

| CN115149806A (en)* | 2022-06-21 | 2022-10-04 | 西北工业大学 | Adaptive model prediction control method for interleaved parallel Boost converters |

| KR20230062629A (en)* | 2020-09-14 | 2023-05-09 | 비테스코 테크놀로지스 유에스에이 엘엘씨 | Method and device for switching frequency modulation in interleaved power factor correction for on-board charging applications |

- 2023

- 2023-05-19KRKR1020230064930Apatent/KR102615142B1/enactiveActive

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20140313795A1 (en)* | 2013-04-17 | 2014-10-23 | The Regents Of The University Of Michigan | Single phase bi-directional ac-dc converter with reduced passive components size and common mode electro-magnetic interference |

| KR20230062629A (en)* | 2020-09-14 | 2023-05-09 | 비테스코 테크놀로지스 유에스에이 엘엘씨 | Method and device for switching frequency modulation in interleaved power factor correction for on-board charging applications |

| CN115149806A (en)* | 2022-06-21 | 2022-10-04 | 西北工业大学 | Adaptive model prediction control method for interleaved parallel Boost converters |

Non-Patent Citations (1)

| Title |

|---|

| Qihui Fu et al., Fractional-Order Model Predictive Control of SiC PFC Converter, 2021 IEEE Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia) (2021.08.27)** |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10020724B2 (en) | Duty-ratio controller | |

| US10476378B2 (en) | Power factor correction circuit, control method and controller | |

| US9800138B2 (en) | Power factor correction circuit | |

| JP5141774B2 (en) | PFC converter | |

| US8681513B2 (en) | Optimization of a power converter employing an LLC converter | |

| US9450496B2 (en) | Multi-stage power converters and methods for varying a regulated voltage of one stage as a function of an output current of another stage | |

| US9812951B2 (en) | Advanced PFC voltage controller | |

| TWI551017B (en) | System and method for regulating operation of non-symmetric boost based front end stage of rectifier with power factor correction, and system and method for reducing volume and losses of boost inductor in pfc rectifier | |

| US7148669B2 (en) | Predictive digital current controllers for switching power converters | |

| JP5326804B2 (en) | Power factor improving power supply device, control circuit used for power supply device, and control method | |

| US7317625B2 (en) | Parallel current mode control using a direct duty cycle algorithm with low computational requirements to perform power factor correction | |

| JP5104947B2 (en) | Switching power supply | |

| WO2011030640A1 (en) | Pfc converter | |

| EP2166657A1 (en) | Pfc converter | |

| WO2010061653A1 (en) | Pfc converter | |

| EP2330727B1 (en) | Method of controlling a PFC stage operating in boundary conduction mode | |

| JP6409515B2 (en) | Insulated AC-DC converter | |

| JP6398537B2 (en) | AC-DC converter | |

| KR102615142B1 (en) | Boost power factor correction convertor based on model predictive current control and method for operating thereof | |

| EP3396831B1 (en) | Phase compensation for power factor correction circuit to reduce zero-crossing distortion | |

| US20210099076A1 (en) | AC-DC Converter with Boost Front End Having Flat Current and Active Blanking Control | |

| Grote et al. | Semi-digital interleaved PFC control with optimized light load efficiency | |

| KR101782497B1 (en) | Dcm region input voltage expansion control device and control method | |

| Choi et al. | A novel active discontinuous PWM control strategy for high efficiency partial switching predictive current-mode control PFC converter | |

| Ivaldi et al. | Flexible pfc control featuring adaptive gain, mode estimation, and dual feedforward compensation |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0109 | Patent application | Patent event code:PA01091R01D Comment text:Patent Application Patent event date:20230519 | |

| PA0201 | Request for examination | ||

| PA0302 | Request for accelerated examination | Patent event date:20230608 Patent event code:PA03022R01D Comment text:Request for Accelerated Examination Patent event date:20230519 Patent event code:PA03021R01I Comment text:Patent Application | |

| PE0902 | Notice of grounds for rejection | Comment text:Notification of reason for refusal Patent event date:20230808 Patent event code:PE09021S01D | |

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration | Patent event code:PE07011S01D Comment text:Decision to Grant Registration Patent event date:20231212 | |

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment | Comment text:Registration of Establishment Patent event date:20231213 Patent event code:PR07011E01D | |

| PR1002 | Payment of registration fee | Payment date:20231214 End annual number:3 Start annual number:1 | |

| PG1601 | Publication of registration |