KR102307633B1 - 반도체 소자 및 그 제조 방법 - Google Patents

반도체 소자 및 그 제조 방법Download PDFInfo

- Publication number

- KR102307633B1 KR102307633B1KR1020140177548AKR20140177548AKR102307633B1KR 102307633 B1KR102307633 B1KR 102307633B1KR 1020140177548 AKR1020140177548 AKR 1020140177548AKR 20140177548 AKR20140177548 AKR 20140177548AKR 102307633 B1KR102307633 B1KR 102307633B1

- Authority

- KR

- South Korea

- Prior art keywords

- contact

- conductive pattern

- insulating layer

- contact hole

- opening

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/69—IGFETs having charge trapping gate insulators, e.g. MNOS transistors

- H10D30/694—IGFETs having charge trapping gate insulators, e.g. MNOS transistors characterised by the shapes, relative sizes or dispositions of the gate electrodes

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/20—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by three-dimensional arrangements, e.g. with cells on different height levels

- H10B41/23—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by three-dimensional arrangements, e.g. with cells on different height levels with source and drain on different levels, e.g. with sloping channels

- H10B41/27—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by three-dimensional arrangements, e.g. with cells on different height levels with source and drain on different levels, e.g. with sloping channels the channels comprising vertical portions, e.g. U-shaped channels

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

- H01L21/76805—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics the opening being a via or contact hole penetrating the underlying conductor

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

- H01L21/76816—Aspects relating to the layout of the pattern or to the size of vias or trenches

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/31—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape

- H01L23/3157—Partial encapsulation or coating

- H01L23/3171—Partial encapsulation or coating the coating being directly applied to the semiconductor body, e.g. passivation layer

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/482—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of lead-in layers inseparably applied to the semiconductor body (electrodes)

- H01L23/485—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of lead-in layers inseparably applied to the semiconductor body (electrodes) consisting of layered constructions comprising conductive layers and insulating layers, e.g. planar contacts

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/5226—Via connections in a multilevel interconnection structure

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B43/00—EEPROM devices comprising charge-trapping gate insulators

- H10B43/20—EEPROM devices comprising charge-trapping gate insulators characterised by three-dimensional arrangements, e.g. with cells on different height levels

- H10B43/23—EEPROM devices comprising charge-trapping gate insulators characterised by three-dimensional arrangements, e.g. with cells on different height levels with source and drain on different levels, e.g. with sloping channels

- H10B43/27—EEPROM devices comprising charge-trapping gate insulators characterised by three-dimensional arrangements, e.g. with cells on different height levels with source and drain on different levels, e.g. with sloping channels the channels comprising vertical portions, e.g. U-shaped channels

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B43/00—EEPROM devices comprising charge-trapping gate insulators

- H10B43/30—EEPROM devices comprising charge-trapping gate insulators characterised by the memory core region

- H10B43/35—EEPROM devices comprising charge-trapping gate insulators characterised by the memory core region with cell select transistors, e.g. NAND

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B43/00—EEPROM devices comprising charge-trapping gate insulators

- H10B43/50—EEPROM devices comprising charge-trapping gate insulators characterised by the boundary region between the core and peripheral circuit regions

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/0413—Manufacture or treatment of FETs having insulated gates [IGFET] of FETs having charge-trapping gate insulators, e.g. MNOS transistors

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/69—IGFETs having charge trapping gate insulators, e.g. MNOS transistors

- H10D30/693—Vertical IGFETs having charge trapping gate insulators

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/01—Manufacture or treatment

- H10D64/031—Manufacture or treatment of data-storage electrodes

- H10D64/037—Manufacture or treatment of data-storage electrodes comprising charge-trapping insulators

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Semiconductor Memories (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Geometry (AREA)

Abstract

Description

도 1b는 본 발명의 일 실시예들에 따른 반도체 소자의 단면도로서, 도 1a의 I-I'선에 대응하는 단면을 나타낸다.

도 2a 내지 6a, 및 도 3c는 본 발명의 일 실시예들에 따른 반도체 소자의 제조 방법을 나타내는 평면도들이다.

도 2b 내지 6b, 및 도 3d는 본 발명의 일 실시예들에 따른 반도체 소자의 제조 방법을 나타내는 단면도들로서, 각각 도 2a 내지 6a 및 도 3c의 I-I'선에 대응한다.

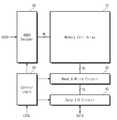

도 7은 본 발명의 개념에 의한 실시예들에 따른 메모리 장치를 나타내는 블록도이다.

도 8은 도 7의 메모리 셀 어레이의 예를 나타내는 블록도이다.

도 9는 본 발명의 개념에 의한 실시예들에 따른 것으로, 도 8의 메모리 블록의 셀 어레이를 나타내는 간략 회로도이다.

도 10a는 본 발명의 다른 실시예들에 따른 반도체 소자의 평면도이다.

도 10b는 도 10a의 I-I'선에 따른 단면도이다.

도 11a 내지 도 11l은 본 발명의 다른 실시예들에 따른 반도체 소자의 제조 방법에 관한 도면들로, 도 10a의 I-I'선에 대응되는 단면도들이다.

도 12는 본 발명의 또 다른 실시예들에 따른 것으로, 도 8의 메모리 블록의 셀 어레이를 나타내는 간략 회로도이다.

도 13은 본 발명의 또 다른 실시예들에 따른 반도체 소자의 단면도이다.

도 14는 본 발명의 개념에 의한 실시예들에 따라 형성된 메모리 장치를 포함하는 전자 시스템의 일 예를 나타내는 개략 블록도이다.

도 15는 본 발명의 개념에 의한 실시예들에 따라 형성된 메모리 장치를 구비하는 메모리 카드의 일 예를 나타내는 개략 블록도이다.

도 16은 본 발명의 개념에 의한 실시예들에 따라 형성된 메모리 장치를 장착한 정보 처리 시스템의 일 예를 나타내는 개략 블록도이다.

Claims (10)

- 기판 상에 적층된 제1 도전성 패턴 및 제2 도전성 패턴, 상기 제1 및 제2 도전성 패턴들의 각각은 제1 방향으로 연장되고, 상기 제2 도전성 패턴의 상기 제1 방향에 따른 길이는 상기 제1 도전성 패턴의 상기 제1 방향에 따른 길이보다 작은 것;

상기 제1 및 제2 도전성 패턴들을 덮는 매립 절연막; 및

상기 제1 도전성 패턴 및 상기 제2 도전성 패턴에 각각 연결되는 제1 콘택 플러그 및 제2 콘택 플러그를 포함하되,

상기 제1 콘택 플러그는 상기 제1 도전성 패턴 내의 제1 콘택 플레이트, 및 상기 제1 콘택 플레이트의 상면과 접하며 상기 매립 절연막을 관통하는 제1 콘택 바디를 포함하고, 상기 제1 콘택 플레이트의 상기 상면의 너비는 상기 제1 콘택 바디의 하면의 너비보다 크고,

상기 제2 콘택 플러그는 상기 제2 도전성 패턴 내의 제2 콘택 플레이트, 및 상기 제2 콘택 플레이트의 상면과 접하며 상기 매립 절연막을 관통하는 제2 콘택 바디를 포함하고, 상기 제2 콘택 플레이트의 상기 상면의 너비는 상기 제2 콘택 바디의 하면의 너비보다 큰 반도체 소자. - 제 1 항에 있어서,

상기 제1 콘택 플레이트는 원판(circular plate) 구조를 갖는 반도체 소자. - 제 1 항에 있어서,

상기 제1 콘택 플레이트의 표면 및 상기 제1 콘택 바디의 측면을 컨포멀하게 덮는 제1 배리어 막을 더 포함하는 반도체 소자. - 제 1 항에 있어서,

상기 제1 콘택 플레이트는 상기 제1 도전성 패턴을 관통하는 반도체 소자. - 기판 상에 적층된 제1 도전성 패턴 및 제2 도전성 패턴을 형성하되, 상기 제1 및 제2 도전성 패턴들의 각각은 제1 방향으로 연장되고, 상기 제2 도전성 패턴의 상기 제1 방향에 따른 길이는 상기 제1 도전성 패턴의 상기 제1 방향에 따른 길이보다 작은 것;

상기 제1 및 제2 도전성 패턴들을 덮는 매립 절연막을 형성하는 것;

상기 매립 절연막 내에 제1 콘택 홀 및 제2 콘택 홀을 형성하되, 상기 제1 콘택 홀의 바닥은 상기 제1 도전성 패턴에 인접하고, 상기 제2 콘택 홀의 바닥은 상기 제2 도전성 패턴에 인접하는 것;

상기 제1 도전성 패턴을 부분적으로 제거함으로써 상기 제1 도전성 패턴 내에 제1 개구부를 형성하고, 상기 제2 도전성 패턴을 부분적으로 제거함으로써 상기 제2 도전성 패턴 내에 제2 개구부를 형성하되, 상기 제1 개구부는 상기 제1 콘택 홀에 연결되고, 상기 제2 개구부는 상기 제2 콘택 홀에 연결되는 것; 및

상기 제1 콘택 홀 및 상기 제1 개구부를 채우는 제1 콘택 플러그, 및 상기 제2 콘택 홀 및 상기 제2 개구부를 채우는 제2 콘택 플러그를 형성하는 것을 포함하되,

상기 제1 개구부의 너비는 상기 제1 콘택 홀의 너비보다 크고,

상기 제2 개구부의 너비는 상기 제2 콘택 홀의 너비보다 큰 반도체 소자의 제조방법. - 제 5 항에 있어서,

상기 제1 및 제2 콘택 플러그들을 형성하기 전에, 상기 제1 및 제2 콘택 홀들 및 상기 제1 및 제2 개구부들의 내면들을 컨포멀하게 덮는 배리어 막을 형성하는 것을 더 포함하는 반도체 소자의 제조 방법. - 제 5 항에 있어서,

상기 제1 개구부는 상기 제1 도전성 패턴의 상면에서 하면으로 연장되도록 형성되는 반도체 소자의 제조 방법. - 제 5 항에 있어서,

상기 제1 및 제2 개구부들을 형성하는 것은 습식 식각을 수행하여 상기 제1 및 제2 도전성 패턴들을 부분적으로 제거하는 것을 포함하는 반도체 소자의 제조 방법. - 제 8 항에 있어서,

상기 습식 식각은 상기 매립 절연막 보다 상기 제1 및 제2 도전성 패턴들에 대하여 더 빠른 식각 속도를 가지는 반도체 소자의 제조 방법. - 제 8 항에 있어서,

상기 제1 및 제2 콘택 홀들을 형성하는 것은 상기 제1 콘택 홀과 상기 제1 도전성 패턴 사이, 및 상기 제2 콘택 홀과 상기 제2 도전성 패턴 사이에 상기 매립 절연막의 잔존물을 형성하는 것을 포함하되,

상기 습식 식각은 상기 잔존물을 제거하는 것을 포함하는 반도체 소자의 제조 방법.

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020140177548AKR102307633B1 (ko) | 2014-12-10 | 2014-12-10 | 반도체 소자 및 그 제조 방법 |

| US14/956,735US9711603B2 (en) | 2014-12-10 | 2015-12-02 | Semiconductor device and method for manufacturing the same |

| US15/591,736US10103236B2 (en) | 2014-12-10 | 2017-05-10 | Semiconductor device and method for manufacturing the same |

| US16/121,020US10608091B2 (en) | 2014-12-10 | 2018-09-04 | Semiconductor device and method for manufacturing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020140177548AKR102307633B1 (ko) | 2014-12-10 | 2014-12-10 | 반도체 소자 및 그 제조 방법 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20160070896A KR20160070896A (ko) | 2016-06-21 |

| KR102307633B1true KR102307633B1 (ko) | 2021-10-06 |

Family

ID=56111902

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020140177548AActiveKR102307633B1 (ko) | 2014-12-10 | 2014-12-10 | 반도체 소자 및 그 제조 방법 |

Country Status (2)

| Country | Link |

|---|---|

| US (3) | US9711603B2 (ko) |

| KR (1) | KR102307633B1 (ko) |

Families Citing this family (330)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9394608B2 (en) | 2009-04-06 | 2016-07-19 | Asm America, Inc. | Semiconductor processing reactor and components thereof |

| US8802201B2 (en) | 2009-08-14 | 2014-08-12 | Asm America, Inc. | Systems and methods for thin-film deposition of metal oxides using excited nitrogen-oxygen species |

| US20130023129A1 (en) | 2011-07-20 | 2013-01-24 | Asm America, Inc. | Pressure transmitter for a semiconductor processing environment |

| US9017481B1 (en) | 2011-10-28 | 2015-04-28 | Asm America, Inc. | Process feed management for semiconductor substrate processing |

| US10714315B2 (en) | 2012-10-12 | 2020-07-14 | Asm Ip Holdings B.V. | Semiconductor reaction chamber showerhead |

| US20160376700A1 (en) | 2013-02-01 | 2016-12-29 | Asm Ip Holding B.V. | System for treatment of deposition reactor |

| US11015245B2 (en) | 2014-03-19 | 2021-05-25 | Asm Ip Holding B.V. | Gas-phase reactor and system having exhaust plenum and components thereof |

| KR20150139255A (ko) | 2014-06-03 | 2015-12-11 | 에스케이하이닉스 주식회사 | 반도체 장치 및 그 제조방법 |

| US10858737B2 (en) | 2014-07-28 | 2020-12-08 | Asm Ip Holding B.V. | Showerhead assembly and components thereof |

| US9890456B2 (en) | 2014-08-21 | 2018-02-13 | Asm Ip Holding B.V. | Method and system for in situ formation of gas-phase compounds |

| US10941490B2 (en) | 2014-10-07 | 2021-03-09 | Asm Ip Holding B.V. | Multiple temperature range susceptor, assembly, reactor and system including the susceptor, and methods of using the same |

| KR102307633B1 (ko)* | 2014-12-10 | 2021-10-06 | 삼성전자주식회사 | 반도체 소자 및 그 제조 방법 |

| US10276355B2 (en) | 2015-03-12 | 2019-04-30 | Asm Ip Holding B.V. | Multi-zone reactor, system including the reactor, and method of using the same |

| US10458018B2 (en) | 2015-06-26 | 2019-10-29 | Asm Ip Holding B.V. | Structures including metal carbide material, devices including the structures, and methods of forming same |

| KR102392685B1 (ko)* | 2015-07-06 | 2022-04-29 | 삼성전자주식회사 | 배선 구조체를 갖는 반도체 소자 |

| KR102447489B1 (ko)* | 2015-09-02 | 2022-09-27 | 삼성전자주식회사 | 반도체 메모리 소자 |

| US9831121B2 (en)* | 2015-09-14 | 2017-11-28 | Toshiba Memory Corporation | Semiconductor memory device with contact plugs extending inside contact connection portions |

| US10211308B2 (en) | 2015-10-21 | 2019-02-19 | Asm Ip Holding B.V. | NbMC layers |

| US11139308B2 (en) | 2015-12-29 | 2021-10-05 | Asm Ip Holding B.V. | Atomic layer deposition of III-V compounds to form V-NAND devices |

| KR102650535B1 (ko) | 2016-01-18 | 2024-03-25 | 삼성전자주식회사 | 3차원 반도체 메모리 장치 |

| US9633945B1 (en)* | 2016-01-27 | 2017-04-25 | Kabushiki Kaisha Toshiba | Semiconductor device and method of manufacturing semiconductor device |

| US10529554B2 (en) | 2016-02-19 | 2020-01-07 | Asm Ip Holding B.V. | Method for forming silicon nitride film selectively on sidewalls or flat surfaces of trenches |

| US10343920B2 (en) | 2016-03-18 | 2019-07-09 | Asm Ip Holding B.V. | Aligned carbon nanotubes |

| US10865475B2 (en) | 2016-04-21 | 2020-12-15 | Asm Ip Holding B.V. | Deposition of metal borides and silicides |

| US10190213B2 (en) | 2016-04-21 | 2019-01-29 | Asm Ip Holding B.V. | Deposition of metal borides |

| US10367080B2 (en) | 2016-05-02 | 2019-07-30 | Asm Ip Holding B.V. | Method of forming a germanium oxynitride film |

| US11453943B2 (en) | 2016-05-25 | 2022-09-27 | Asm Ip Holding B.V. | Method for forming carbon-containing silicon/metal oxide or nitride film by ALD using silicon precursor and hydrocarbon precursor |

| US10612137B2 (en) | 2016-07-08 | 2020-04-07 | Asm Ip Holdings B.V. | Organic reactants for atomic layer deposition |

| US9859151B1 (en) | 2016-07-08 | 2018-01-02 | Asm Ip Holding B.V. | Selective film deposition method to form air gaps |

| US9812320B1 (en) | 2016-07-28 | 2017-11-07 | Asm Ip Holding B.V. | Method and apparatus for filling a gap |

| KR102532607B1 (ko) | 2016-07-28 | 2023-05-15 | 에이에스엠 아이피 홀딩 비.브이. | 기판 가공 장치 및 그 동작 방법 |

| US9887082B1 (en) | 2016-07-28 | 2018-02-06 | Asm Ip Holding B.V. | Method and apparatus for filling a gap |

| KR102495914B1 (ko) | 2016-08-11 | 2023-02-03 | 삼성전자 주식회사 | 반도체 소자 |

| US10643826B2 (en) | 2016-10-26 | 2020-05-05 | Asm Ip Holdings B.V. | Methods for thermally calibrating reaction chambers |

| US11532757B2 (en) | 2016-10-27 | 2022-12-20 | Asm Ip Holding B.V. | Deposition of charge trapping layers |

| US10714350B2 (en) | 2016-11-01 | 2020-07-14 | ASM IP Holdings, B.V. | Methods for forming a transition metal niobium nitride film on a substrate by atomic layer deposition and related semiconductor device structures |

| US10229833B2 (en) | 2016-11-01 | 2019-03-12 | Asm Ip Holding B.V. | Methods for forming a transition metal nitride film on a substrate by atomic layer deposition and related semiconductor device structures |

| KR102546317B1 (ko) | 2016-11-15 | 2023-06-21 | 에이에스엠 아이피 홀딩 비.브이. | 기체 공급 유닛 및 이를 포함하는 기판 처리 장치 |

| KR102728512B1 (ko)* | 2016-12-09 | 2024-11-12 | 삼성전자주식회사 | 반도체 소자 |

| KR102762543B1 (ko) | 2016-12-14 | 2025-02-05 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치 |

| US11581186B2 (en) | 2016-12-15 | 2023-02-14 | Asm Ip Holding B.V. | Sequential infiltration synthesis apparatus |

| US11447861B2 (en) | 2016-12-15 | 2022-09-20 | Asm Ip Holding B.V. | Sequential infiltration synthesis apparatus and a method of forming a patterned structure |

| KR102700194B1 (ko) | 2016-12-19 | 2024-08-28 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치 |

| US10269558B2 (en) | 2016-12-22 | 2019-04-23 | Asm Ip Holding B.V. | Method of forming a structure on a substrate |

| US10867788B2 (en) | 2016-12-28 | 2020-12-15 | Asm Ip Holding B.V. | Method of forming a structure on a substrate |

| US11390950B2 (en) | 2017-01-10 | 2022-07-19 | Asm Ip Holding B.V. | Reactor system and method to reduce residue buildup during a film deposition process |

| US10468261B2 (en) | 2017-02-15 | 2019-11-05 | Asm Ip Holding B.V. | Methods for forming a metallic film on a substrate by cyclical deposition and related semiconductor device structures |

| JP2018152412A (ja)* | 2017-03-10 | 2018-09-27 | 東芝メモリ株式会社 | 半導体装置及びその製造方法 |

| US10529563B2 (en) | 2017-03-29 | 2020-01-07 | Asm Ip Holdings B.V. | Method for forming doped metal oxide films on a substrate by cyclical deposition and related semiconductor device structures |

| KR102457289B1 (ko) | 2017-04-25 | 2022-10-21 | 에이에스엠 아이피 홀딩 비.브이. | 박막 증착 방법 및 반도체 장치의 제조 방법 |

| US10770286B2 (en) | 2017-05-08 | 2020-09-08 | Asm Ip Holdings B.V. | Methods for selectively forming a silicon nitride film on a substrate and related semiconductor device structures |

| US10892156B2 (en) | 2017-05-08 | 2021-01-12 | Asm Ip Holding B.V. | Methods for forming a silicon nitride film on a substrate and related semiconductor device structures |

| US9960272B1 (en)* | 2017-05-16 | 2018-05-01 | International Business Machines Corporation | Bottom contact resistance reduction on VFET |

| US10886123B2 (en) | 2017-06-02 | 2021-01-05 | Asm Ip Holding B.V. | Methods for forming low temperature semiconductor layers and related semiconductor device structures |

| US12040200B2 (en) | 2017-06-20 | 2024-07-16 | Asm Ip Holding B.V. | Semiconductor processing apparatus and methods for calibrating a semiconductor processing apparatus |

| US11306395B2 (en) | 2017-06-28 | 2022-04-19 | Asm Ip Holding B.V. | Methods for depositing a transition metal nitride film on a substrate by atomic layer deposition and related deposition apparatus |

| KR102421766B1 (ko)* | 2017-07-07 | 2022-07-18 | 삼성전자주식회사 | 3차원 반도체 장치 및 그 제조 방법 |

| KR20190009245A (ko) | 2017-07-18 | 2019-01-28 | 에이에스엠 아이피 홀딩 비.브이. | 반도체 소자 구조물 형성 방법 및 관련된 반도체 소자 구조물 |

| US11018002B2 (en) | 2017-07-19 | 2021-05-25 | Asm Ip Holding B.V. | Method for selectively depositing a Group IV semiconductor and related semiconductor device structures |

| US11374112B2 (en) | 2017-07-19 | 2022-06-28 | Asm Ip Holding B.V. | Method for depositing a group IV semiconductor and related semiconductor device structures |

| US10541333B2 (en) | 2017-07-19 | 2020-01-21 | Asm Ip Holding B.V. | Method for depositing a group IV semiconductor and related semiconductor device structures |

| US10590535B2 (en) | 2017-07-26 | 2020-03-17 | Asm Ip Holdings B.V. | Chemical treatment, deposition and/or infiltration apparatus and method for using the same |

| TWI815813B (zh) | 2017-08-04 | 2023-09-21 | 荷蘭商Asm智慧財產控股公司 | 用於分配反應腔內氣體的噴頭總成 |

| US10770336B2 (en) | 2017-08-08 | 2020-09-08 | Asm Ip Holding B.V. | Substrate lift mechanism and reactor including same |

| US10692741B2 (en) | 2017-08-08 | 2020-06-23 | Asm Ip Holdings B.V. | Radiation shield |

| US11769682B2 (en) | 2017-08-09 | 2023-09-26 | Asm Ip Holding B.V. | Storage apparatus for storing cassettes for substrates and processing apparatus equipped therewith |

| US11139191B2 (en) | 2017-08-09 | 2021-10-05 | Asm Ip Holding B.V. | Storage apparatus for storing cassettes for substrates and processing apparatus equipped therewith |

| CN107644876B (zh) | 2017-08-28 | 2019-01-01 | 长江存储科技有限责任公司 | 台阶结构及其形成方法 |

| US11830730B2 (en) | 2017-08-29 | 2023-11-28 | Asm Ip Holding B.V. | Layer forming method and apparatus |

| US11295980B2 (en) | 2017-08-30 | 2022-04-05 | Asm Ip Holding B.V. | Methods for depositing a molybdenum metal film over a dielectric surface of a substrate by a cyclical deposition process and related semiconductor device structures |

| US11056344B2 (en) | 2017-08-30 | 2021-07-06 | Asm Ip Holding B.V. | Layer forming method |

| KR102491945B1 (ko) | 2017-08-30 | 2023-01-26 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치 |

| KR102401446B1 (ko) | 2017-08-31 | 2022-05-24 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치 |

| KR102630301B1 (ko) | 2017-09-21 | 2024-01-29 | 에이에스엠 아이피 홀딩 비.브이. | 침투성 재료의 순차 침투 합성 방법 처리 및 이를 이용하여 형성된 구조물 및 장치 |

| US10844484B2 (en) | 2017-09-22 | 2020-11-24 | Asm Ip Holding B.V. | Apparatus for dispensing a vapor phase reactant to a reaction chamber and related methods |

| US10658205B2 (en) | 2017-09-28 | 2020-05-19 | Asm Ip Holdings B.V. | Chemical dispensing apparatus and methods for dispensing a chemical to a reaction chamber |

| US10403504B2 (en) | 2017-10-05 | 2019-09-03 | Asm Ip Holding B.V. | Method for selectively depositing a metallic film on a substrate |

| US10923344B2 (en) | 2017-10-30 | 2021-02-16 | Asm Ip Holding B.V. | Methods for forming a semiconductor structure and related semiconductor structures |

| US10910262B2 (en) | 2017-11-16 | 2021-02-02 | Asm Ip Holding B.V. | Method of selectively depositing a capping layer structure on a semiconductor device structure |

| US11022879B2 (en) | 2017-11-24 | 2021-06-01 | Asm Ip Holding B.V. | Method of forming an enhanced unexposed photoresist layer |

| WO2019103613A1 (en) | 2017-11-27 | 2019-05-31 | Asm Ip Holding B.V. | A storage device for storing wafer cassettes for use with a batch furnace |

| CN111344522B (zh) | 2017-11-27 | 2022-04-12 | 阿斯莫Ip控股公司 | 包括洁净迷你环境的装置 |

| US10872771B2 (en) | 2018-01-16 | 2020-12-22 | Asm Ip Holding B. V. | Method for depositing a material film on a substrate within a reaction chamber by a cyclical deposition process and related device structures |

| TWI799494B (zh) | 2018-01-19 | 2023-04-21 | 荷蘭商Asm 智慧財產控股公司 | 沈積方法 |

| KR102695659B1 (ko) | 2018-01-19 | 2024-08-14 | 에이에스엠 아이피 홀딩 비.브이. | 플라즈마 보조 증착에 의해 갭 충진 층을 증착하는 방법 |

| US11018047B2 (en) | 2018-01-25 | 2021-05-25 | Asm Ip Holding B.V. | Hybrid lift pin |

| USD880437S1 (en) | 2018-02-01 | 2020-04-07 | Asm Ip Holding B.V. | Gas supply plate for semiconductor manufacturing apparatus |

| US11081345B2 (en) | 2018-02-06 | 2021-08-03 | Asm Ip Holding B.V. | Method of post-deposition treatment for silicon oxide film |

| US10896820B2 (en) | 2018-02-14 | 2021-01-19 | Asm Ip Holding B.V. | Method for depositing a ruthenium-containing film on a substrate by a cyclical deposition process |

| WO2019158960A1 (en) | 2018-02-14 | 2019-08-22 | Asm Ip Holding B.V. | A method for depositing a ruthenium-containing film on a substrate by a cyclical deposition process |

| US10731249B2 (en) | 2018-02-15 | 2020-08-04 | Asm Ip Holding B.V. | Method of forming a transition metal containing film on a substrate by a cyclical deposition process, a method for supplying a transition metal halide compound to a reaction chamber, and related vapor deposition apparatus |

| KR102636427B1 (ko) | 2018-02-20 | 2024-02-13 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 방법 및 장치 |

| US10975470B2 (en) | 2018-02-23 | 2021-04-13 | Asm Ip Holding B.V. | Apparatus for detecting or monitoring for a chemical precursor in a high temperature environment |

| US11473195B2 (en) | 2018-03-01 | 2022-10-18 | Asm Ip Holding B.V. | Semiconductor processing apparatus and a method for processing a substrate |

| US11629406B2 (en) | 2018-03-09 | 2023-04-18 | Asm Ip Holding B.V. | Semiconductor processing apparatus comprising one or more pyrometers for measuring a temperature of a substrate during transfer of the substrate |

| US11114283B2 (en) | 2018-03-16 | 2021-09-07 | Asm Ip Holding B.V. | Reactor, system including the reactor, and methods of manufacturing and using same |

| KR102646467B1 (ko) | 2018-03-27 | 2024-03-11 | 에이에스엠 아이피 홀딩 비.브이. | 기판 상에 전극을 형성하는 방법 및 전극을 포함하는 반도체 소자 구조 |

| US11088002B2 (en) | 2018-03-29 | 2021-08-10 | Asm Ip Holding B.V. | Substrate rack and a substrate processing system and method |

| US11230766B2 (en) | 2018-03-29 | 2022-01-25 | Asm Ip Holding B.V. | Substrate processing apparatus and method |

| KR102501472B1 (ko) | 2018-03-30 | 2023-02-20 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 방법 |

| KR102600229B1 (ko) | 2018-04-09 | 2023-11-10 | 에이에스엠 아이피 홀딩 비.브이. | 기판 지지 장치, 이를 포함하는 기판 처리 장치 및 기판 처리 방법 |

| KR102624625B1 (ko)* | 2018-04-20 | 2024-01-12 | 삼성전자주식회사 | 수직형 메모리 장치 및 그 제조 방법 |

| US10825867B2 (en) | 2018-04-24 | 2020-11-03 | Micron Technology, Inc. | Cross-point memory array and related fabrication techniques |

| US10950663B2 (en) | 2018-04-24 | 2021-03-16 | Micron Technology, Inc. | Cross-point memory array and related fabrication techniques |

| KR102633073B1 (ko)* | 2018-04-24 | 2024-02-06 | 삼성전자주식회사 | 반도체 메모리 소자 |

| US10729012B2 (en) | 2018-04-24 | 2020-07-28 | Micron Technology, Inc. | Buried lines and related fabrication techniques |

| US12025484B2 (en) | 2018-05-08 | 2024-07-02 | Asm Ip Holding B.V. | Thin film forming method |

| TWI811348B (zh) | 2018-05-08 | 2023-08-11 | 荷蘭商Asm 智慧財產控股公司 | 藉由循環沉積製程於基板上沉積氧化物膜之方法及相關裝置結構 |

| US12272527B2 (en) | 2018-05-09 | 2025-04-08 | Asm Ip Holding B.V. | Apparatus for use with hydrogen radicals and method of using same |

| KR20190129718A (ko) | 2018-05-11 | 2019-11-20 | 에이에스엠 아이피 홀딩 비.브이. | 기판 상에 피도핑 금속 탄화물 막을 형성하는 방법 및 관련 반도체 소자 구조 |

| KR102596988B1 (ko) | 2018-05-28 | 2023-10-31 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 방법 및 그에 의해 제조된 장치 |

| TWI840362B (zh) | 2018-06-04 | 2024-05-01 | 荷蘭商Asm Ip私人控股有限公司 | 水氣降低的晶圓處置腔室 |

| US11718913B2 (en) | 2018-06-04 | 2023-08-08 | Asm Ip Holding B.V. | Gas distribution system and reactor system including same |

| US11286562B2 (en) | 2018-06-08 | 2022-03-29 | Asm Ip Holding B.V. | Gas-phase chemical reactor and method of using same |

| KR102568797B1 (ko) | 2018-06-21 | 2023-08-21 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 시스템 |

| US10797133B2 (en) | 2018-06-21 | 2020-10-06 | Asm Ip Holding B.V. | Method for depositing a phosphorus doped silicon arsenide film and related semiconductor device structures |

| KR102854019B1 (ko) | 2018-06-27 | 2025-09-02 | 에이에스엠 아이피 홀딩 비.브이. | 금속 함유 재료를 형성하기 위한 주기적 증착 방법 및 금속 함유 재료를 포함하는 필름 및 구조체 |

| TWI873894B (zh) | 2018-06-27 | 2025-02-21 | 荷蘭商Asm Ip私人控股有限公司 | 用於形成含金屬材料及包含含金屬材料的膜及結構之循環沉積方法 |

| US10612136B2 (en) | 2018-06-29 | 2020-04-07 | ASM IP Holding, B.V. | Temperature-controlled flange and reactor system including same |

| KR102686758B1 (ko) | 2018-06-29 | 2024-07-18 | 에이에스엠 아이피 홀딩 비.브이. | 박막 증착 방법 및 반도체 장치의 제조 방법 |

| US10388513B1 (en) | 2018-07-03 | 2019-08-20 | Asm Ip Holding B.V. | Method for depositing silicon-free carbon-containing film as gap-fill layer by pulse plasma-assisted deposition |

| US10755922B2 (en) | 2018-07-03 | 2020-08-25 | Asm Ip Holding B.V. | Method for depositing silicon-free carbon-containing film as gap-fill layer by pulse plasma-assisted deposition |

| US10767789B2 (en) | 2018-07-16 | 2020-09-08 | Asm Ip Holding B.V. | Diaphragm valves, valve components, and methods for forming valve components |

| US11053591B2 (en) | 2018-08-06 | 2021-07-06 | Asm Ip Holding B.V. | Multi-port gas injection system and reactor system including same |

| US10883175B2 (en) | 2018-08-09 | 2021-01-05 | Asm Ip Holding B.V. | Vertical furnace for processing substrates and a liner for use therein |

| US10829852B2 (en) | 2018-08-16 | 2020-11-10 | Asm Ip Holding B.V. | Gas distribution device for a wafer processing apparatus |

| US11430674B2 (en) | 2018-08-22 | 2022-08-30 | Asm Ip Holding B.V. | Sensor array, apparatus for dispensing a vapor phase reactant to a reaction chamber and related methods |

| US11758716B2 (en)* | 2018-09-05 | 2023-09-12 | Micron Technology, Inc. | Electronic devices including vertical memory cells and related methods |

| CN109244077B (zh)* | 2018-09-05 | 2020-07-03 | 长江存储科技有限责任公司 | 三维存储器的制作方法 |

| KR102707956B1 (ko) | 2018-09-11 | 2024-09-19 | 에이에스엠 아이피 홀딩 비.브이. | 박막 증착 방법 |

| US11024523B2 (en) | 2018-09-11 | 2021-06-01 | Asm Ip Holding B.V. | Substrate processing apparatus and method |

| US11049751B2 (en) | 2018-09-14 | 2021-06-29 | Asm Ip Holding B.V. | Cassette supply system to store and handle cassettes and processing apparatus equipped therewith |

| CN110970344B (zh) | 2018-10-01 | 2024-10-25 | Asmip控股有限公司 | 衬底保持设备、包含所述设备的系统及其使用方法 |

| US11232963B2 (en) | 2018-10-03 | 2022-01-25 | Asm Ip Holding B.V. | Substrate processing apparatus and method |

| KR102592699B1 (ko) | 2018-10-08 | 2023-10-23 | 에이에스엠 아이피 홀딩 비.브이. | 기판 지지 유닛 및 이를 포함하는 박막 증착 장치와 기판 처리 장치 |

| KR102546322B1 (ko) | 2018-10-19 | 2023-06-21 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치 및 기판 처리 방법 |

| KR102605121B1 (ko) | 2018-10-19 | 2023-11-23 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치 및 기판 처리 방법 |

| USD948463S1 (en) | 2018-10-24 | 2022-04-12 | Asm Ip Holding B.V. | Susceptor for semiconductor substrate supporting apparatus |

| US12378665B2 (en) | 2018-10-26 | 2025-08-05 | Asm Ip Holding B.V. | High temperature coatings for a preclean and etch apparatus and related methods |

| US11087997B2 (en) | 2018-10-31 | 2021-08-10 | Asm Ip Holding B.V. | Substrate processing apparatus for processing substrates |

| KR102748291B1 (ko) | 2018-11-02 | 2024-12-31 | 에이에스엠 아이피 홀딩 비.브이. | 기판 지지 유닛 및 이를 포함하는 기판 처리 장치 |

| US11572620B2 (en) | 2018-11-06 | 2023-02-07 | Asm Ip Holding B.V. | Methods for selectively depositing an amorphous silicon film on a substrate |

| US11031242B2 (en) | 2018-11-07 | 2021-06-08 | Asm Ip Holding B.V. | Methods for depositing a boron doped silicon germanium film |

| US10818758B2 (en) | 2018-11-16 | 2020-10-27 | Asm Ip Holding B.V. | Methods for forming a metal silicate film on a substrate in a reaction chamber and related semiconductor device structures |

| US10847366B2 (en) | 2018-11-16 | 2020-11-24 | Asm Ip Holding B.V. | Methods for depositing a transition metal chalcogenide film on a substrate by a cyclical deposition process |

| US12040199B2 (en) | 2018-11-28 | 2024-07-16 | Asm Ip Holding B.V. | Substrate processing apparatus for processing substrates |

| US11217444B2 (en) | 2018-11-30 | 2022-01-04 | Asm Ip Holding B.V. | Method for forming an ultraviolet radiation responsive metal oxide-containing film |

| KR102636428B1 (ko) | 2018-12-04 | 2024-02-13 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치를 세정하는 방법 |

| US11158513B2 (en) | 2018-12-13 | 2021-10-26 | Asm Ip Holding B.V. | Methods for forming a rhenium-containing film on a substrate by a cyclical deposition process and related semiconductor device structures |

| TWI874340B (zh) | 2018-12-14 | 2025-03-01 | 荷蘭商Asm Ip私人控股有限公司 | 形成裝置結構之方法、其所形成之結構及施行其之系統 |

| TWI866480B (zh) | 2019-01-17 | 2024-12-11 | 荷蘭商Asm Ip 私人控股有限公司 | 藉由循環沈積製程於基板上形成含過渡金屬膜之方法 |

| KR102727227B1 (ko) | 2019-01-22 | 2024-11-07 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치 |

| CN111524788B (zh) | 2019-02-01 | 2023-11-24 | Asm Ip私人控股有限公司 | 氧化硅的拓扑选择性膜形成的方法 |

| TWI845607B (zh) | 2019-02-20 | 2024-06-21 | 荷蘭商Asm Ip私人控股有限公司 | 用來填充形成於基材表面內之凹部的循環沉積方法及設備 |

| TWI873122B (zh) | 2019-02-20 | 2025-02-21 | 荷蘭商Asm Ip私人控股有限公司 | 填充一基板之一表面內所形成的一凹槽的方法、根據其所形成之半導體結構、及半導體處理設備 |

| TWI838458B (zh) | 2019-02-20 | 2024-04-11 | 荷蘭商Asm Ip私人控股有限公司 | 用於3d nand應用中之插塞填充沉積之設備及方法 |

| KR102626263B1 (ko) | 2019-02-20 | 2024-01-16 | 에이에스엠 아이피 홀딩 비.브이. | 처리 단계를 포함하는 주기적 증착 방법 및 이를 위한 장치 |

| TWI842826B (zh) | 2019-02-22 | 2024-05-21 | 荷蘭商Asm Ip私人控股有限公司 | 基材處理設備及處理基材之方法 |

| KR102858005B1 (ko) | 2019-03-08 | 2025-09-09 | 에이에스엠 아이피 홀딩 비.브이. | 실리콘 질화물 층을 선택적으로 증착하는 방법, 및 선택적으로 증착된 실리콘 질화물 층을 포함하는 구조체 |

| US11742198B2 (en) | 2019-03-08 | 2023-08-29 | Asm Ip Holding B.V. | Structure including SiOCN layer and method of forming same |

| KR102782593B1 (ko) | 2019-03-08 | 2025-03-14 | 에이에스엠 아이피 홀딩 비.브이. | SiOC 층을 포함한 구조체 및 이의 형성 방법 |

| JP2020167398A (ja) | 2019-03-28 | 2020-10-08 | エーエスエム・アイピー・ホールディング・ベー・フェー | ドアオープナーおよびドアオープナーが提供される基材処理装置 |

| KR102809999B1 (ko) | 2019-04-01 | 2025-05-19 | 에이에스엠 아이피 홀딩 비.브이. | 반도체 소자를 제조하는 방법 |

| KR20200123380A (ko) | 2019-04-19 | 2020-10-29 | 에이에스엠 아이피 홀딩 비.브이. | 층 형성 방법 및 장치 |

| KR20200125453A (ko) | 2019-04-24 | 2020-11-04 | 에이에스엠 아이피 홀딩 비.브이. | 기상 반응기 시스템 및 이를 사용하는 방법 |

| KR20200130121A (ko) | 2019-05-07 | 2020-11-18 | 에이에스엠 아이피 홀딩 비.브이. | 딥 튜브가 있는 화학물질 공급원 용기 |

| US11289326B2 (en) | 2019-05-07 | 2022-03-29 | Asm Ip Holding B.V. | Method for reforming amorphous carbon polymer film |

| KR20200130652A (ko) | 2019-05-10 | 2020-11-19 | 에이에스엠 아이피 홀딩 비.브이. | 표면 상에 재료를 증착하는 방법 및 본 방법에 따라 형성된 구조 |

| JP7598201B2 (ja) | 2019-05-16 | 2024-12-11 | エーエスエム・アイピー・ホールディング・ベー・フェー | ウェハボートハンドリング装置、縦型バッチ炉および方法 |

| JP7612342B2 (ja) | 2019-05-16 | 2025-01-14 | エーエスエム・アイピー・ホールディング・ベー・フェー | ウェハボートハンドリング装置、縦型バッチ炉および方法 |

| USD947913S1 (en) | 2019-05-17 | 2022-04-05 | Asm Ip Holding B.V. | Susceptor shaft |

| USD975665S1 (en) | 2019-05-17 | 2023-01-17 | Asm Ip Holding B.V. | Susceptor shaft |

| USD935572S1 (en) | 2019-05-24 | 2021-11-09 | Asm Ip Holding B.V. | Gas channel plate |

| USD922229S1 (en) | 2019-06-05 | 2021-06-15 | Asm Ip Holding B.V. | Device for controlling a temperature of a gas supply unit |

| KR20200141002A (ko) | 2019-06-06 | 2020-12-17 | 에이에스엠 아이피 홀딩 비.브이. | 배기 가스 분석을 포함한 기상 반응기 시스템을 사용하는 방법 |

| KR20200141931A (ko) | 2019-06-10 | 2020-12-21 | 에이에스엠 아이피 홀딩 비.브이. | 석영 에피택셜 챔버를 세정하는 방법 |

| KR20200143254A (ko) | 2019-06-11 | 2020-12-23 | 에이에스엠 아이피 홀딩 비.브이. | 개질 가스를 사용하여 전자 구조를 형성하는 방법, 상기 방법을 수행하기 위한 시스템, 및 상기 방법을 사용하여 형성되는 구조 |

| USD944946S1 (en) | 2019-06-14 | 2022-03-01 | Asm Ip Holding B.V. | Shower plate |

| USD931978S1 (en) | 2019-06-27 | 2021-09-28 | Asm Ip Holding B.V. | Showerhead vacuum transport |

| KR20210005515A (ko) | 2019-07-03 | 2021-01-14 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치용 온도 제어 조립체 및 이를 사용하는 방법 |

| JP7499079B2 (ja) | 2019-07-09 | 2024-06-13 | エーエスエム・アイピー・ホールディング・ベー・フェー | 同軸導波管を用いたプラズマ装置、基板処理方法 |

| CN112216646A (zh) | 2019-07-10 | 2021-01-12 | Asm Ip私人控股有限公司 | 基板支撑组件及包括其的基板处理装置 |

| KR20210010307A (ko) | 2019-07-16 | 2021-01-27 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치 |

| KR102860110B1 (ko) | 2019-07-17 | 2025-09-16 | 에이에스엠 아이피 홀딩 비.브이. | 실리콘 게르마늄 구조를 형성하는 방법 |

| KR20210010816A (ko) | 2019-07-17 | 2021-01-28 | 에이에스엠 아이피 홀딩 비.브이. | 라디칼 보조 점화 플라즈마 시스템 및 방법 |

| US11643724B2 (en) | 2019-07-18 | 2023-05-09 | Asm Ip Holding B.V. | Method of forming structures using a neutral beam |

| KR20210010817A (ko) | 2019-07-19 | 2021-01-28 | 에이에스엠 아이피 홀딩 비.브이. | 토폴로지-제어된 비정질 탄소 중합체 막을 형성하는 방법 |

| TWI839544B (zh) | 2019-07-19 | 2024-04-21 | 荷蘭商Asm Ip私人控股有限公司 | 形成形貌受控的非晶碳聚合物膜之方法 |

| TWI851767B (zh) | 2019-07-29 | 2024-08-11 | 荷蘭商Asm Ip私人控股有限公司 | 用於利用n型摻雜物及/或替代摻雜物選擇性沉積以達成高摻雜物併入之方法 |

| CN112309899A (zh) | 2019-07-30 | 2021-02-02 | Asm Ip私人控股有限公司 | 基板处理设备 |

| CN112309900A (zh) | 2019-07-30 | 2021-02-02 | Asm Ip私人控股有限公司 | 基板处理设备 |

| US12169361B2 (en) | 2019-07-30 | 2024-12-17 | Asm Ip Holding B.V. | Substrate processing apparatus and method |

| US11587815B2 (en) | 2019-07-31 | 2023-02-21 | Asm Ip Holding B.V. | Vertical batch furnace assembly |

| US11227782B2 (en) | 2019-07-31 | 2022-01-18 | Asm Ip Holding B.V. | Vertical batch furnace assembly |

| US11587814B2 (en) | 2019-07-31 | 2023-02-21 | Asm Ip Holding B.V. | Vertical batch furnace assembly |

| CN112323048B (zh) | 2019-08-05 | 2024-02-09 | Asm Ip私人控股有限公司 | 用于化学源容器的液位传感器 |

| CN112342526A (zh) | 2019-08-09 | 2021-02-09 | Asm Ip私人控股有限公司 | 包括冷却装置的加热器组件及其使用方法 |

| USD965524S1 (en) | 2019-08-19 | 2022-10-04 | Asm Ip Holding B.V. | Susceptor support |

| USD965044S1 (en) | 2019-08-19 | 2022-09-27 | Asm Ip Holding B.V. | Susceptor shaft |

| JP2021031769A (ja) | 2019-08-21 | 2021-03-01 | エーエスエム アイピー ホールディング ビー.ブイ. | 成膜原料混合ガス生成装置及び成膜装置 |

| USD930782S1 (en) | 2019-08-22 | 2021-09-14 | Asm Ip Holding B.V. | Gas distributor |

| USD949319S1 (en) | 2019-08-22 | 2022-04-19 | Asm Ip Holding B.V. | Exhaust duct |

| KR20210024423A (ko) | 2019-08-22 | 2021-03-05 | 에이에스엠 아이피 홀딩 비.브이. | 홀을 구비한 구조체를 형성하기 위한 방법 |

| USD940837S1 (en) | 2019-08-22 | 2022-01-11 | Asm Ip Holding B.V. | Electrode |

| USD979506S1 (en) | 2019-08-22 | 2023-02-28 | Asm Ip Holding B.V. | Insulator |

| KR20210024420A (ko) | 2019-08-23 | 2021-03-05 | 에이에스엠 아이피 홀딩 비.브이. | 비스(디에틸아미노)실란을 사용하여 peald에 의해 개선된 품질을 갖는 실리콘 산화물 막을 증착하기 위한 방법 |

| US11286558B2 (en) | 2019-08-23 | 2022-03-29 | Asm Ip Holding B.V. | Methods for depositing a molybdenum nitride film on a surface of a substrate by a cyclical deposition process and related semiconductor device structures including a molybdenum nitride film |

| KR102633039B1 (ko) | 2019-08-26 | 2024-02-05 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 및 이의 제조 방법 |

| KR102806450B1 (ko) | 2019-09-04 | 2025-05-12 | 에이에스엠 아이피 홀딩 비.브이. | 희생 캡핑 층을 이용한 선택적 증착 방법 |

| KR102733104B1 (ko) | 2019-09-05 | 2024-11-22 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치 |

| US11562901B2 (en) | 2019-09-25 | 2023-01-24 | Asm Ip Holding B.V. | Substrate processing method |

| KR102807252B1 (ko)* | 2019-09-26 | 2025-05-15 | 삼성전자주식회사 | 3차원 반도체 메모리 장치 |

| KR102711414B1 (ko) | 2019-10-01 | 2024-09-30 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 및 이의 제조 방법 |

| CN112593212B (zh) | 2019-10-02 | 2023-12-22 | Asm Ip私人控股有限公司 | 通过循环等离子体增强沉积工艺形成拓扑选择性氧化硅膜的方法 |

| KR20210042810A (ko) | 2019-10-08 | 2021-04-20 | 에이에스엠 아이피 홀딩 비.브이. | 활성 종을 이용하기 위한 가스 분배 어셈블리를 포함한 반응기 시스템 및 이를 사용하는 방법 |

| TW202128273A (zh) | 2019-10-08 | 2021-08-01 | 荷蘭商Asm Ip私人控股有限公司 | 氣體注入系統、及將材料沉積於反應室內之基板表面上的方法 |

| TWI846953B (zh) | 2019-10-08 | 2024-07-01 | 荷蘭商Asm Ip私人控股有限公司 | 基板處理裝置 |

| TWI846966B (zh) | 2019-10-10 | 2024-07-01 | 荷蘭商Asm Ip私人控股有限公司 | 形成光阻底層之方法及包括光阻底層之結構 |

| US12009241B2 (en) | 2019-10-14 | 2024-06-11 | Asm Ip Holding B.V. | Vertical batch furnace assembly with detector to detect cassette |

| TWI834919B (zh) | 2019-10-16 | 2024-03-11 | 荷蘭商Asm Ip私人控股有限公司 | 氧化矽之拓撲選擇性膜形成之方法 |

| US11637014B2 (en) | 2019-10-17 | 2023-04-25 | Asm Ip Holding B.V. | Methods for selective deposition of doped semiconductor material |

| KR102845724B1 (ko) | 2019-10-21 | 2025-08-13 | 에이에스엠 아이피 홀딩 비.브이. | 막을 선택적으로 에칭하기 위한 장치 및 방법 |

| KR20210050453A (ko) | 2019-10-25 | 2021-05-07 | 에이에스엠 아이피 홀딩 비.브이. | 기판 표면 상의 갭 피처를 충진하는 방법 및 이와 관련된 반도체 소자 구조 |

| US11646205B2 (en) | 2019-10-29 | 2023-05-09 | Asm Ip Holding B.V. | Methods of selectively forming n-type doped material on a surface, systems for selectively forming n-type doped material, and structures formed using same |

| KR20210054983A (ko) | 2019-11-05 | 2021-05-14 | 에이에스엠 아이피 홀딩 비.브이. | 도핑된 반도체 층을 갖는 구조체 및 이를 형성하기 위한 방법 및 시스템 |

| US11501968B2 (en) | 2019-11-15 | 2022-11-15 | Asm Ip Holding B.V. | Method for providing a semiconductor device with silicon filled gaps |

| KR102861314B1 (ko) | 2019-11-20 | 2025-09-17 | 에이에스엠 아이피 홀딩 비.브이. | 기판의 표면 상에 탄소 함유 물질을 증착하는 방법, 상기 방법을 사용하여 형성된 구조물, 및 상기 구조물을 형성하기 위한 시스템 |

| CN112951697B (zh) | 2019-11-26 | 2025-07-29 | Asmip私人控股有限公司 | 基板处理设备 |

| US11450529B2 (en) | 2019-11-26 | 2022-09-20 | Asm Ip Holding B.V. | Methods for selectively forming a target film on a substrate comprising a first dielectric surface and a second metallic surface |

| CN112885692B (zh) | 2019-11-29 | 2025-08-15 | Asmip私人控股有限公司 | 基板处理设备 |

| CN120432376A (zh) | 2019-11-29 | 2025-08-05 | Asm Ip私人控股有限公司 | 基板处理设备 |

| JP7527928B2 (ja) | 2019-12-02 | 2024-08-05 | エーエスエム・アイピー・ホールディング・ベー・フェー | 基板処理装置、基板処理方法 |

| KR20210070898A (ko) | 2019-12-04 | 2021-06-15 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치 |

| KR102730033B1 (ko) | 2019-12-17 | 2024-11-14 | 삼성전자주식회사 | 반도체 소자 |

| KR20210078405A (ko) | 2019-12-17 | 2021-06-28 | 에이에스엠 아이피 홀딩 비.브이. | 바나듐 나이트라이드 층을 형성하는 방법 및 바나듐 나이트라이드 층을 포함하는 구조 |

| KR20210080214A (ko) | 2019-12-19 | 2021-06-30 | 에이에스엠 아이피 홀딩 비.브이. | 기판 상의 갭 피처를 충진하는 방법 및 이와 관련된 반도체 소자 구조 |

| JP7636892B2 (ja) | 2020-01-06 | 2025-02-27 | エーエスエム・アイピー・ホールディング・ベー・フェー | チャネル付きリフトピン |

| JP7730637B2 (ja) | 2020-01-06 | 2025-08-28 | エーエスエム・アイピー・ホールディング・ベー・フェー | ガス供給アセンブリ、その構成要素、およびこれを含む反応器システム |

| US11993847B2 (en) | 2020-01-08 | 2024-05-28 | Asm Ip Holding B.V. | Injector |

| KR20210093163A (ko) | 2020-01-16 | 2021-07-27 | 에이에스엠 아이피 홀딩 비.브이. | 고 종횡비 피처를 형성하는 방법 |

| KR102675856B1 (ko) | 2020-01-20 | 2024-06-17 | 에이에스엠 아이피 홀딩 비.브이. | 박막 형성 방법 및 박막 표면 개질 방법 |

| TWI889744B (zh) | 2020-01-29 | 2025-07-11 | 荷蘭商Asm Ip私人控股有限公司 | 污染物捕集系統、及擋板堆疊 |

| TW202513845A (zh) | 2020-02-03 | 2025-04-01 | 荷蘭商Asm Ip私人控股有限公司 | 半導體裝置結構及其形成方法 |

| KR20210100010A (ko) | 2020-02-04 | 2021-08-13 | 에이에스엠 아이피 홀딩 비.브이. | 대형 물품의 투과율 측정을 위한 방법 및 장치 |

| US11776846B2 (en) | 2020-02-07 | 2023-10-03 | Asm Ip Holding B.V. | Methods for depositing gap filling fluids and related systems and devices |

| KR20210103956A (ko) | 2020-02-13 | 2021-08-24 | 에이에스엠 아이피 홀딩 비.브이. | 수광 장치를 포함하는 기판 처리 장치 및 수광 장치의 교정 방법 |

| TW202146691A (zh) | 2020-02-13 | 2021-12-16 | 荷蘭商Asm Ip私人控股有限公司 | 氣體分配總成、噴淋板總成、及調整至反應室之氣體的傳導率之方法 |

| TWI855223B (zh) | 2020-02-17 | 2024-09-11 | 荷蘭商Asm Ip私人控股有限公司 | 用於生長磷摻雜矽層之方法 |

| CN113410160A (zh) | 2020-02-28 | 2021-09-17 | Asm Ip私人控股有限公司 | 专用于零件清洁的系统 |

| KR20210113043A (ko) | 2020-03-04 | 2021-09-15 | 에이에스엠 아이피 홀딩 비.브이. | 반응기 시스템용 정렬 고정구 |

| US11876356B2 (en) | 2020-03-11 | 2024-01-16 | Asm Ip Holding B.V. | Lockout tagout assembly and system and method of using same |

| KR20210116240A (ko) | 2020-03-11 | 2021-09-27 | 에이에스엠 아이피 홀딩 비.브이. | 조절성 접합부를 갖는 기판 핸들링 장치 |

| KR102775390B1 (ko) | 2020-03-12 | 2025-02-28 | 에이에스엠 아이피 홀딩 비.브이. | 타겟 토폴로지 프로파일을 갖는 층 구조를 제조하기 위한 방법 |

| US12173404B2 (en) | 2020-03-17 | 2024-12-24 | Asm Ip Holding B.V. | Method of depositing epitaxial material, structure formed using the method, and system for performing the method |

| US11145628B1 (en) | 2020-03-20 | 2021-10-12 | Sandisk Technologies Llc | Semiconductor structure containing reentrant shaped bonding pads and methods of forming the same |

| US11527500B2 (en) | 2020-03-20 | 2022-12-13 | Sandisk Technologies Llc | Semiconductor structure containing multilayer bonding pads and methods of forming the same |

| WO2021188133A1 (en)* | 2020-03-20 | 2021-09-23 | Sandisk Technologies Llc | Semiconductor structure containing reentrant shaped bonding pads and methods of forming the same |

| US12347804B2 (en) | 2020-03-20 | 2025-07-01 | SanDisk Technologies, Inc. | Bonded assembly including interconnect-level bonding pads and methods of forming the same |

| US11201139B2 (en) | 2020-03-20 | 2021-12-14 | Sandisk Technologies Llc | Semiconductor structure containing reentrant shaped bonding pads and methods of forming the same |

| KR102755229B1 (ko) | 2020-04-02 | 2025-01-14 | 에이에스엠 아이피 홀딩 비.브이. | 박막 형성 방법 |

| TWI887376B (zh) | 2020-04-03 | 2025-06-21 | 荷蘭商Asm Ip私人控股有限公司 | 半導體裝置的製造方法 |

| TWI888525B (zh) | 2020-04-08 | 2025-07-01 | 荷蘭商Asm Ip私人控股有限公司 | 用於選擇性蝕刻氧化矽膜之設備及方法 |

| US11821078B2 (en) | 2020-04-15 | 2023-11-21 | Asm Ip Holding B.V. | Method for forming precoat film and method for forming silicon-containing film |

| KR20210128343A (ko) | 2020-04-15 | 2021-10-26 | 에이에스엠 아이피 홀딩 비.브이. | 크롬 나이트라이드 층을 형성하는 방법 및 크롬 나이트라이드 층을 포함하는 구조 |

| US11996289B2 (en) | 2020-04-16 | 2024-05-28 | Asm Ip Holding B.V. | Methods of forming structures including silicon germanium and silicon layers, devices formed using the methods, and systems for performing the methods |

| KR20210130646A (ko) | 2020-04-21 | 2021-11-01 | 에이에스엠 아이피 홀딩 비.브이. | 기판을 처리하기 위한 방법 |

| KR20210132612A (ko) | 2020-04-24 | 2021-11-04 | 에이에스엠 아이피 홀딩 비.브이. | 바나듐 화합물들을 안정화하기 위한 방법들 및 장치 |

| TW202208671A (zh) | 2020-04-24 | 2022-03-01 | 荷蘭商Asm Ip私人控股有限公司 | 形成包括硼化釩及磷化釩層的結構之方法 |

| KR20210132600A (ko) | 2020-04-24 | 2021-11-04 | 에이에스엠 아이피 홀딩 비.브이. | 바나듐, 질소 및 추가 원소를 포함한 층을 증착하기 위한 방법 및 시스템 |

| KR102866804B1 (ko) | 2020-04-24 | 2025-09-30 | 에이에스엠 아이피 홀딩 비.브이. | 냉각 가스 공급부를 포함한 수직형 배치 퍼니스 어셈블리 |

| CN113555279A (zh) | 2020-04-24 | 2021-10-26 | Asm Ip私人控股有限公司 | 形成含氮化钒的层的方法及包含其的结构 |

| KR102783898B1 (ko) | 2020-04-29 | 2025-03-18 | 에이에스엠 아이피 홀딩 비.브이. | 고체 소스 전구체 용기 |

| KR20210134869A (ko) | 2020-05-01 | 2021-11-11 | 에이에스엠 아이피 홀딩 비.브이. | Foup 핸들러를 이용한 foup의 빠른 교환 |

| JP7726664B2 (ja) | 2020-05-04 | 2025-08-20 | エーエスエム・アイピー・ホールディング・ベー・フェー | 基板を処理するための基板処理システム |

| KR102788543B1 (ko) | 2020-05-13 | 2025-03-27 | 에이에스엠 아이피 홀딩 비.브이. | 반응기 시스템용 레이저 정렬 고정구 |

| TW202146699A (zh) | 2020-05-15 | 2021-12-16 | 荷蘭商Asm Ip私人控股有限公司 | 形成矽鍺層之方法、半導體結構、半導體裝置、形成沉積層之方法、及沉積系統 |

| KR20210143653A (ko) | 2020-05-19 | 2021-11-29 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치 |

| KR102795476B1 (ko) | 2020-05-21 | 2025-04-11 | 에이에스엠 아이피 홀딩 비.브이. | 다수의 탄소 층을 포함한 구조체 및 이를 형성하고 사용하는 방법 |

| KR20210145079A (ko) | 2020-05-21 | 2021-12-01 | 에이에스엠 아이피 홀딩 비.브이. | 기판을 처리하기 위한 플랜지 및 장치 |

| TWI873343B (zh) | 2020-05-22 | 2025-02-21 | 荷蘭商Asm Ip私人控股有限公司 | 用於在基材上形成薄膜之反應系統 |

| KR20210146802A (ko) | 2020-05-26 | 2021-12-06 | 에이에스엠 아이피 홀딩 비.브이. | 붕소 및 갈륨을 함유한 실리콘 게르마늄 층을 증착하는 방법 |

| TWI876048B (zh) | 2020-05-29 | 2025-03-11 | 荷蘭商Asm Ip私人控股有限公司 | 基板處理方法 |

| TW202212620A (zh) | 2020-06-02 | 2022-04-01 | 荷蘭商Asm Ip私人控股有限公司 | 處理基板之設備、形成膜之方法、及控制用於處理基板之設備之方法 |

| TW202208659A (zh) | 2020-06-16 | 2022-03-01 | 荷蘭商Asm Ip私人控股有限公司 | 沉積含硼之矽鍺層的方法 |

| TW202218133A (zh) | 2020-06-24 | 2022-05-01 | 荷蘭商Asm Ip私人控股有限公司 | 形成含矽層之方法 |

| TWI873359B (zh) | 2020-06-30 | 2025-02-21 | 荷蘭商Asm Ip私人控股有限公司 | 基板處理方法 |

| US12431354B2 (en) | 2020-07-01 | 2025-09-30 | Asm Ip Holding B.V. | Silicon nitride and silicon oxide deposition methods using fluorine inhibitor |

| TW202202649A (zh) | 2020-07-08 | 2022-01-16 | 荷蘭商Asm Ip私人控股有限公司 | 基板處理方法 |

| KR20220010438A (ko) | 2020-07-17 | 2022-01-25 | 에이에스엠 아이피 홀딩 비.브이. | 포토리소그래피에 사용하기 위한 구조체 및 방법 |

| KR20220011092A (ko) | 2020-07-20 | 2022-01-27 | 에이에스엠 아이피 홀딩 비.브이. | 전이 금속층을 포함하는 구조체를 형성하기 위한 방법 및 시스템 |

| TWI878570B (zh) | 2020-07-20 | 2025-04-01 | 荷蘭商Asm Ip私人控股有限公司 | 用於沉積鉬層之方法及系統 |

| US12322591B2 (en) | 2020-07-27 | 2025-06-03 | Asm Ip Holding B.V. | Thin film deposition process |

| KR20220021863A (ko) | 2020-08-14 | 2022-02-22 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 방법 |

| US12040177B2 (en) | 2020-08-18 | 2024-07-16 | Asm Ip Holding B.V. | Methods for forming a laminate film by cyclical plasma-enhanced deposition processes |

| US11502000B2 (en)* | 2020-08-24 | 2022-11-15 | Taiwan Semiconductor Manufacturing Co., Ltd. | Bottom lateral expansion of contact plugs through implantation |

| TW202228863A (zh) | 2020-08-25 | 2022-08-01 | 荷蘭商Asm Ip私人控股有限公司 | 清潔基板的方法、選擇性沉積的方法、及反應器系統 |

| US11725280B2 (en) | 2020-08-26 | 2023-08-15 | Asm Ip Holding B.V. | Method for forming metal silicon oxide and metal silicon oxynitride layers |

| TW202229601A (zh) | 2020-08-27 | 2022-08-01 | 荷蘭商Asm Ip私人控股有限公司 | 形成圖案化結構的方法、操控機械特性的方法、裝置結構、及基板處理系統 |

| TW202217045A (zh) | 2020-09-10 | 2022-05-01 | 荷蘭商Asm Ip私人控股有限公司 | 沉積間隙填充流體之方法及相關系統和裝置 |

| USD990534S1 (en) | 2020-09-11 | 2023-06-27 | Asm Ip Holding B.V. | Weighted lift pin |

| KR20220036866A (ko) | 2020-09-16 | 2022-03-23 | 에이에스엠 아이피 홀딩 비.브이. | 실리콘 산화물 증착 방법 |

| USD1012873S1 (en) | 2020-09-24 | 2024-01-30 | Asm Ip Holding B.V. | Electrode for semiconductor processing apparatus |

| TWI889903B (zh) | 2020-09-25 | 2025-07-11 | 荷蘭商Asm Ip私人控股有限公司 | 基板處理方法 |

| US12009224B2 (en) | 2020-09-29 | 2024-06-11 | Asm Ip Holding B.V. | Apparatus and method for etching metal nitrides |

| KR20220045900A (ko) | 2020-10-06 | 2022-04-13 | 에이에스엠 아이피 홀딩 비.브이. | 실리콘 함유 재료를 증착하기 위한 증착 방법 및 장치 |

| CN114293174A (zh) | 2020-10-07 | 2022-04-08 | Asm Ip私人控股有限公司 | 气体供应单元和包括气体供应单元的衬底处理设备 |

| TW202229613A (zh) | 2020-10-14 | 2022-08-01 | 荷蘭商Asm Ip私人控股有限公司 | 於階梯式結構上沉積材料的方法 |

| TW202232565A (zh) | 2020-10-15 | 2022-08-16 | 荷蘭商Asm Ip私人控股有限公司 | 製造半導體裝置之方法及使用乙太網路控制自動化技術之基板處理裝置 |

| TW202217037A (zh) | 2020-10-22 | 2022-05-01 | 荷蘭商Asm Ip私人控股有限公司 | 沉積釩金屬的方法、結構、裝置及沉積總成 |

| TW202223136A (zh) | 2020-10-28 | 2022-06-16 | 荷蘭商Asm Ip私人控股有限公司 | 用於在基板上形成層之方法、及半導體處理系統 |

| TW202229620A (zh) | 2020-11-12 | 2022-08-01 | 特文特大學 | 沉積系統、用於控制反應條件之方法、沉積方法 |

| TW202229795A (zh) | 2020-11-23 | 2022-08-01 | 荷蘭商Asm Ip私人控股有限公司 | 具注入器之基板處理設備 |

| TW202235649A (zh) | 2020-11-24 | 2022-09-16 | 荷蘭商Asm Ip私人控股有限公司 | 填充間隙之方法與相關之系統及裝置 |

| TW202235675A (zh) | 2020-11-30 | 2022-09-16 | 荷蘭商Asm Ip私人控股有限公司 | 注入器、及基板處理設備 |

| US12255053B2 (en) | 2020-12-10 | 2025-03-18 | Asm Ip Holding B.V. | Methods and systems for depositing a layer |

| TW202233884A (zh) | 2020-12-14 | 2022-09-01 | 荷蘭商Asm Ip私人控股有限公司 | 形成臨限電壓控制用之結構的方法 |

| US11946137B2 (en) | 2020-12-16 | 2024-04-02 | Asm Ip Holding B.V. | Runout and wobble measurement fixtures |

| TW202232639A (zh) | 2020-12-18 | 2022-08-16 | 荷蘭商Asm Ip私人控股有限公司 | 具有可旋轉台的晶圓處理設備 |

| TW202226899A (zh) | 2020-12-22 | 2022-07-01 | 荷蘭商Asm Ip私人控股有限公司 | 具匹配器的電漿處理裝置 |

| TW202231903A (zh) | 2020-12-22 | 2022-08-16 | 荷蘭商Asm Ip私人控股有限公司 | 過渡金屬沉積方法、過渡金屬層、用於沉積過渡金屬於基板上的沉積總成 |

| TW202242184A (zh) | 2020-12-22 | 2022-11-01 | 荷蘭商Asm Ip私人控股有限公司 | 前驅物膠囊、前驅物容器、氣相沉積總成、及將固態前驅物裝載至前驅物容器中之方法 |

| US11569139B2 (en) | 2021-03-02 | 2023-01-31 | Western Digital Technologies, Inc. | Electrical overlay measurement methods and structures for wafer-to-wafer bonding |

| US11621202B2 (en) | 2021-03-02 | 2023-04-04 | Western Digital Technologies, Inc. | Electrical overlay measurement methods and structures for wafer-to-wafer bonding |

| USD980814S1 (en) | 2021-05-11 | 2023-03-14 | Asm Ip Holding B.V. | Gas distributor for substrate processing apparatus |

| USD980813S1 (en) | 2021-05-11 | 2023-03-14 | Asm Ip Holding B.V. | Gas flow control plate for substrate processing apparatus |

| USD981973S1 (en) | 2021-05-11 | 2023-03-28 | Asm Ip Holding B.V. | Reactor wall for substrate processing apparatus |

| USD1023959S1 (en) | 2021-05-11 | 2024-04-23 | Asm Ip Holding B.V. | Electrode for substrate processing apparatus |

| USD990441S1 (en) | 2021-09-07 | 2023-06-27 | Asm Ip Holding B.V. | Gas flow control plate |

| USD1060598S1 (en) | 2021-12-03 | 2025-02-04 | Asm Ip Holding B.V. | Split showerhead cover |

| KR20240087254A (ko)* | 2022-12-12 | 2024-06-19 | 에스케이하이닉스 주식회사 | 반도체 장치 및 반도체 장치의 제조 방법 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5619071A (en) | 1994-10-17 | 1997-04-08 | Intel Corporation | Anchored via connection |

| US20070040188A1 (en)* | 2005-08-19 | 2007-02-22 | Taiwan Semiconductor Manufacturing Company, Ltd. | Contact or via hole structure with enlarged bottom critical dimension |

Family Cites Families (29)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5070391A (en) | 1989-11-30 | 1991-12-03 | Sgs-Thomson Microelectronics, Inc. | Semiconductor contact via structure and method |

| US6028363A (en)* | 1997-06-04 | 2000-02-22 | Taiwan Semiconductor Manufacturing Company | Vertical via/contact |

| TW417293B (en) | 1999-08-27 | 2001-01-01 | Taiwan Semiconductor Mfg | Formation of DRAM capacitor |

| KR100382729B1 (ko) | 2000-12-09 | 2003-05-09 | 삼성전자주식회사 | 반도체 소자의 금속 컨택 구조체 및 그 형성방법 |

| KR20050052630A (ko) | 2003-11-28 | 2005-06-03 | 주식회사 하이닉스반도체 | 반도체 소자의 메탈 콘택 형성방법 |

| KR20070008118A (ko) | 2005-07-13 | 2007-01-17 | 매그나칩 반도체 유한회사 | 반도체소자의 금속 콘택 형성방법 |

| KR100655082B1 (ko)* | 2005-12-23 | 2006-12-08 | 삼성전자주식회사 | 상변화 메모리 소자 및 그 제조방법 |

| KR100766504B1 (ko)* | 2006-09-29 | 2007-10-15 | 삼성전자주식회사 | 반도체 소자 및 그 제조 방법 |

| KR20080060310A (ko) | 2006-12-27 | 2008-07-02 | 주식회사 하이닉스반도체 | 반도체소자의 플러그 형성 방법 |

| KR101226685B1 (ko) | 2007-11-08 | 2013-01-25 | 삼성전자주식회사 | 수직형 반도체 소자 및 그 제조 방법. |

| KR20090080435A (ko) | 2008-01-21 | 2009-07-24 | 주식회사 하이닉스반도체 | 반도체 소자의 금속 배선 형성방법 |

| JP5253875B2 (ja)* | 2008-04-28 | 2013-07-31 | 株式会社東芝 | 不揮発性半導体記憶装置、及びその製造方法 |

| KR20100006646A (ko) | 2008-07-10 | 2010-01-21 | 삼성전자주식회사 | 텅스텐 재성장을 통한 금속 배선 패턴 및 그 배선 패턴형성 방법 |

| KR101588852B1 (ko)* | 2008-10-31 | 2016-01-26 | 삼성전자주식회사 | 반도체 소자 및 그 형성방법 |

| US8541831B2 (en)* | 2008-12-03 | 2013-09-24 | Samsung Electronics Co., Ltd. | Nonvolatile memory device and method for fabricating the same |

| KR20110001527A (ko) | 2009-06-30 | 2011-01-06 | 주식회사 하이닉스반도체 | 수직채널형 비휘발성 메모리 소자의 제조 방법 |

| JP2011035237A (ja)* | 2009-08-04 | 2011-02-17 | Toshiba Corp | 半導体装置の製造方法及び半導体装置 |

| KR101698193B1 (ko)* | 2009-09-15 | 2017-01-19 | 삼성전자주식회사 | 3차원 반도체 메모리 장치 및 그 제조 방법 |

| KR101691092B1 (ko) | 2010-08-26 | 2016-12-30 | 삼성전자주식회사 | 불휘발성 메모리 장치, 그것의 동작 방법, 그리고 그것을 포함하는 메모리 시스템 |

| US8553466B2 (en) | 2010-03-04 | 2013-10-08 | Samsung Electronics Co., Ltd. | Non-volatile memory device, erasing method thereof, and memory system including the same |

| US9536970B2 (en) | 2010-03-26 | 2017-01-03 | Samsung Electronics Co., Ltd. | Three-dimensional semiconductor memory devices and methods of fabricating the same |

| KR20110108216A (ko)* | 2010-03-26 | 2011-10-05 | 삼성전자주식회사 | 3차원 반도체 장치 |

| KR101682666B1 (ko) | 2010-08-11 | 2016-12-07 | 삼성전자주식회사 | 비휘발성 메모리 장치, 그것의 채널 부스팅 방법, 그것의 프로그램 방법 및 그것을 포함하는 메모리 시스템 |

| KR101843580B1 (ko) | 2011-08-16 | 2018-03-30 | 에스케이하이닉스 주식회사 | 3차원 구조의 비휘발성 메모리 소자 및 그 제조 방법 |

| KR20130116607A (ko)* | 2012-04-16 | 2013-10-24 | 삼성전자주식회사 | 3차원 반도체 메모리 장치 및 그 제조 방법 |

| KR20150064520A (ko)* | 2013-12-03 | 2015-06-11 | 에스케이하이닉스 주식회사 | 반도체 장치 및 그 제조방법 |

| KR102134912B1 (ko)* | 2014-03-21 | 2020-07-20 | 에스케이하이닉스 주식회사 | 반도체 장치 및 그 제조방법 |

| KR20150139255A (ko)* | 2014-06-03 | 2015-12-11 | 에스케이하이닉스 주식회사 | 반도체 장치 및 그 제조방법 |

| KR102307633B1 (ko)* | 2014-12-10 | 2021-10-06 | 삼성전자주식회사 | 반도체 소자 및 그 제조 방법 |

- 2014

- 2014-12-10KRKR1020140177548Apatent/KR102307633B1/koactiveActive

- 2015

- 2015-12-02USUS14/956,735patent/US9711603B2/enactiveActive

- 2017

- 2017-05-10USUS15/591,736patent/US10103236B2/enactiveActive

- 2018

- 2018-09-04USUS16/121,020patent/US10608091B2/enactiveActive

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5619071A (en) | 1994-10-17 | 1997-04-08 | Intel Corporation | Anchored via connection |

| US20070040188A1 (en)* | 2005-08-19 | 2007-02-22 | Taiwan Semiconductor Manufacturing Company, Ltd. | Contact or via hole structure with enlarged bottom critical dimension |

| US7511349B2 (en) | 2005-08-19 | 2009-03-31 | Taiwan Semiconductor Manufacturing Company, Ltd. | Contact or via hole structure with enlarged bottom critical dimension |

Also Published As

| Publication number | Publication date |

|---|---|

| US20160172296A1 (en) | 2016-06-16 |

| US20170271463A1 (en) | 2017-09-21 |

| US10608091B2 (en) | 2020-03-31 |

| US20190019872A1 (en) | 2019-01-17 |

| US9711603B2 (en) | 2017-07-18 |

| KR20160070896A (ko) | 2016-06-21 |

| US10103236B2 (en) | 2018-10-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102307633B1 (ko) | 반도체 소자 및 그 제조 방법 | |

| KR102357992B1 (ko) | 반도체 장치 | |

| KR102321739B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| US10964720B2 (en) | Semiconductor memory device | |

| KR102400184B1 (ko) | 3차원 반도체 메모리 장치 및 이의 제조 방법 | |

| KR102264675B1 (ko) | 반도체 장치 및 그 형성방법 | |

| KR102248419B1 (ko) | 반도체 소자 및 그 제조 방법 | |

| US9847278B2 (en) | Semiconductor devices having air spacers and methods of manufacturing the same | |

| KR102175763B1 (ko) | 반도체 메모리 장치 및 이의 제조 방법 | |

| KR20160060850A (ko) | 메모리 장치 및 그 형성방법 | |

| KR102409748B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| KR102408657B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| US8754466B2 (en) | Three-dimensional semiconductor memory devices | |

| KR20120002832A (ko) | 반도체 메모리 소자 및 그의 형성방법 | |

| KR102270101B1 (ko) | 반도체 소자 및 그 제조 방법 | |

| JP2014057068A (ja) | 不揮発性メモリ装置及びその形成方法 | |

| US9601496B2 (en) | Semiconductor device having sacrificial layer pattern with concave sidewalls and method fabricating the same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0109 | Patent application | St.27 status event code:A-0-1-A10-A12-nap-PA0109 | |

| R17-X000 | Change to representative recorded | St.27 status event code:A-3-3-R10-R17-oth-X000 | |

| PG1501 | Laying open of application | St.27 status event code:A-1-1-Q10-Q12-nap-PG1501 | |

| A201 | Request for examination | ||

| PA0201 | Request for examination | St.27 status event code:A-1-2-D10-D11-exm-PA0201 | |

| D13-X000 | Search requested | St.27 status event code:A-1-2-D10-D13-srh-X000 | |

| D14-X000 | Search report completed | St.27 status event code:A-1-2-D10-D14-srh-X000 | |

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection | St.27 status event code:A-1-2-D10-D21-exm-PE0902 | |

| P11-X000 | Amendment of application requested | St.27 status event code:A-2-2-P10-P11-nap-X000 | |

| P13-X000 | Application amended | St.27 status event code:A-2-2-P10-P13-nap-X000 | |

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration | St.27 status event code:A-1-2-D10-D22-exm-PE0701 | |

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment | St.27 status event code:A-2-4-F10-F11-exm-PR0701 | |

| PR1002 | Payment of registration fee | St.27 status event code:A-2-2-U10-U11-oth-PR1002 Fee payment year number:1 | |

| PG1601 | Publication of registration | St.27 status event code:A-4-4-Q10-Q13-nap-PG1601 | |

| P22-X000 | Classification modified | St.27 status event code:A-4-4-P10-P22-nap-X000 | |

| P22-X000 | Classification modified | St.27 status event code:A-4-4-P10-P22-nap-X000 | |

| PR1001 | Payment of annual fee | St.27 status event code:A-4-4-U10-U11-oth-PR1001 Fee payment year number:4 | |

| PR1001 | Payment of annual fee | St.27 status event code:A-4-4-U10-U11-oth-PR1001 Fee payment year number:5 |