KR102061569B1 - 표시장치 및 표시장치의 구동방법 - Google Patents

표시장치 및 표시장치의 구동방법Download PDFInfo

- Publication number

- KR102061569B1 KR102061569B1KR1020130055845AKR20130055845AKR102061569B1KR 102061569 B1KR102061569 B1KR 102061569B1KR 1020130055845 AKR1020130055845 AKR 1020130055845AKR 20130055845 AKR20130055845 AKR 20130055845AKR 102061569 B1KR102061569 B1KR 102061569B1

- Authority

- KR

- South Korea

- Prior art keywords

- touch

- coils

- signals

- disposed

- period

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/01—Input arrangements or combined input and output arrangements for interaction between user and computer

- G06F3/03—Arrangements for converting the position or the displacement of a member into a coded form

- G06F3/041—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means

- G06F3/0416—Control or interface arrangements specially adapted for digitisers

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/01—Input arrangements or combined input and output arrangements for interaction between user and computer

- G06F3/03—Arrangements for converting the position or the displacement of a member into a coded form

- G06F3/041—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means

- G06F3/0412—Digitisers structurally integrated in a display

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/01—Input arrangements or combined input and output arrangements for interaction between user and computer

- G06F3/03—Arrangements for converting the position or the displacement of a member into a coded form

- G06F3/041—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means

- G06F3/0416—Control or interface arrangements specially adapted for digitisers

- G06F3/04166—Details of scanning methods, e.g. sampling time, grouping of sub areas or time sharing with display driving

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/01—Input arrangements or combined input and output arrangements for interaction between user and computer

- G06F3/03—Arrangements for converting the position or the displacement of a member into a coded form

- G06F3/041—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means

- G06F3/0416—Control or interface arrangements specially adapted for digitisers

- G06F3/0418—Control or interface arrangements specially adapted for digitisers for error correction or compensation, e.g. based on parallax, calibration or alignment

- G06F3/04184—Synchronisation with the driving of the display or the backlighting unit to avoid interferences generated internally

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/01—Input arrangements or combined input and output arrangements for interaction between user and computer

- G06F3/03—Arrangements for converting the position or the displacement of a member into a coded form

- G06F3/041—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means

- G06F3/044—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means by capacitive means

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/01—Input arrangements or combined input and output arrangements for interaction between user and computer

- G06F3/03—Arrangements for converting the position or the displacement of a member into a coded form

- G06F3/041—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means

- G06F3/044—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means by capacitive means

- G06F3/0443—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means by capacitive means using a single layer of sensing electrodes

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/01—Input arrangements or combined input and output arrangements for interaction between user and computer

- G06F3/03—Arrangements for converting the position or the displacement of a member into a coded form

- G06F3/041—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means

- G06F3/044—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means by capacitive means

- G06F3/0446—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means by capacitive means using a grid-like structure of electrodes in at least two directions, e.g. using row and column electrodes

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/01—Input arrangements or combined input and output arrangements for interaction between user and computer

- G06F3/03—Arrangements for converting the position or the displacement of a member into a coded form

- G06F3/041—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means

- G06F3/046—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means by electromagnetic means

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2203/00—Indexing scheme relating to G06F3/00 - G06F3/048

- G06F2203/041—Indexing scheme relating to G06F3/041 - G06F3/045

- G06F2203/04106—Multi-sensing digitiser, i.e. digitiser using at least two different sensing technologies simultaneously or alternatively, e.g. for detecting pen and finger, for saving power or for improving position detection

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0202—Addressing of scan or signal lines

- G09G2310/0218—Addressing of scan or signal lines with collection of electrodes in groups for n-dimensional addressing

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- General Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Human Computer Interaction (AREA)

- Computer Hardware Design (AREA)

- Crystallography & Structural Chemistry (AREA)

- Chemical & Material Sciences (AREA)

- Electromagnetism (AREA)

- Liquid Crystal (AREA)

- Position Input By Displaying (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

Abstract

Description

도 2는 도 1에 도시된 표시장치의 부분 사시도이다.

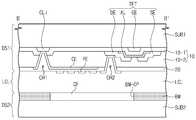

도 3은 도 2의 I-I'선에 따른 단면도들이다.

도 4a는 본 발명의 일 실시예에 따른 화소의 평면도이다.

도 4b는 도 4a의 Ⅱ-Ⅱ'선에 따른 단면도이다.

도 5는 본 발명의 일 실시예에 따른 터치패널의 평면도이다.

도 6a는 도 5의 제1 터치부를 도시한 평면도이다.

도 6b는 도 5의 제2 터치부를 도시한 평면도이다.

도 7은 본 발명의 일 실시예에 따른 표시장치에 인가되는 신호들의 타이밍도이다.

도 8a는 본 발명의 일 실시예에 따른 터치패널 구동부의 블럭도이다.

도 8b는 본 발명의 일 실시예에 따른 터치 감지부의 블럭도이다.

도 9a 및 도 9b는 본 발명의 일 실시예에 따른 스캔신호들의 타이밍도이다.

도 10은 제2 터치감지부에 영향을 주는 노이즈의 발생 경로를 도시한 등가회로도이다.

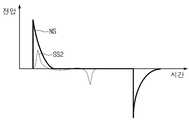

도 11a 및 도 11b는 노이즈와 감지신호의 관계를 도시한 그래프이다.

도 12는 본 발명의 일 실시예에 따른 표시장치의 노이즈 제거 경로를 도시한 등가회로도이다.

도 13은 본 발명의 일 실시예에 따른 표시장치에 인가되는 신호들의 타이밍도이다.

도 14 내지 도 16은 본 발명의 일 실시예들에 따른 표시장치의 단면도이다.

100: 신호제어부200: 게이트 구동부

300: 데이터 구동부400: 터치패널 구동부

500: 터치 감지부

Claims (19)

- 제1 영역과 제2 영역으로 구분되고, 복수 개의 화소들을 포함하며, 프레임 구간 동안 이미지를 생성하는 표시패널; 및

제1 터치코일들 및 상기 제1 터치코일들과 절연 교차하는 제2 터치코일들을 포함하는 제1 터치부, 및 상기 제1 터치부 상측에 배치되고 제1 터치전극들 및 상기 제1 터치전극들과 절연 교차하는 제2 터치전극들을 포함하는 제2 터치부를 포함하는 터치패널을 포함하고,

상기 프레임 구간 중 제1 구간 동안에, 상기 제1 터치코일들 중 상기 제2 영역에 배치된 제1 터치코일들에게 제1 스캔신호들 중 대응하는 제1 스캔신호들이 인가될 때, 상기 제1 터치전극들 중 상기 제1 영역에 배치된 제1 터치전극들에게 제2 스캔신호들 중 대응하는 제2 스캔신호들이 인가되며,

상기 제1 구간 동안에, 상기 복수 개의 화소들 중 상기 제1 영역에 배치된 화소들은 활성화되고, 상기 제2 영역에 배치된 화소들은 비활성화되고,

상기 제2 터치코일들은 상기 제2 영역에서 발생한 입력수단의 공진 주파수에 따른 제1 감지신호들을 출력하며,

상기 제2 터치전극들은 상기 제1 영역에서 발생한 정전용량 변화에 따른 제2 감지신호들을 출력하는 것을 특징으로 하는 표시장치. - 삭제

- 제1 항에 있어서,

상기 표시패널은,

상기 복수 개의 화소들이 배치된 제1 기판;

상기 제1 기판에 마주하는 제2 기판;

제1 방향으로 연장되며 상기 제1 방향에 직교하는 제2 방향으로 나열되고, 상기 복수 개의 화소들 중 대응하는 게이트 라인에 연결된 화소들을 턴-온 시키는 복수 개의 게이트 라인들; 및

상기 복수 개의 게이트 라인들에 절연 교차하고, 상기 턴-온 된 화소들에게 데이터 전압들을 제공하는 복수 개의 데이터 라인들;

을 포함하는 표시장치. - 제3 항에 있어서,

상기 프레임 구간 동안에 상기 복수 개의 게이트 라인들에게 게이트 신호들을 순차적으로 제공하는 게이트 구동부; 및

상기 복수 개의 데이터 라인들에게 상기 데이터 전압들을 제공하는 데이터 구동부를 포함하고,

상기 제1 구간 동안에 상기 게이트 구동부는 상기 복수 개의 게이트 라인들 중 상기 제1 영역에 배치된 게이트 라인들에게 상기 게이트 신호들 중 대응하는 게이트 신호들을 제공하는 것을 특징으로 하는 표시장치. - 제3 항에 있어서,

상기 제1 터치코일들 및 상기 제1 터치전극들은 상기 제1 방향으로 연장되고 상기 제2 방향으로 나열되며,

상기 제2 터치코일들 및 상기 제2 터치전극들은 상기 제2 방향으로 연장되고, 상기 제1 방향으로 나열된 것을 특징으로 하는 표시장치. - 제3 항에 있어서,

상기 복수 개의 화소들 각각은,

상기 복수 개의 게이트 라인들 중 대응하는 게이트 라인 및 복수 개의 데이터 라인들 중 대응하는 데이터 라인에 연결된 박막 트랜지스터;

공통전압을 수신하는 공통전극; 및

상기 박막 트랜지스터로부터 화소전압을 수신하고, 상기 공통전극과 전계를 형성하는 화소전극;

을 포함하는 것을 특징으로 하는 표시장치. - 제1 항에 있어서,

상기 프레임 구간 중 상기 제1 구간 이후의 제2 구간 동안에, 상기 제1 터치코일들 중 상기 제1 영역에 배치된 제1 터치코일들이 제1 스캔신호들 중 대응하는 제1 스캔신호들을 수신할 때, 상기 제1 터치전극들 중 상기 제2 영역에 배치된 제1 터치전극들은 제2 스캔신호들 중 대응하는 제2 스캔신호들을 수신하고,

상기 제2 터치코일들은 상기 제1 영역에서 발생한 상기 입력수단의 공진 주파수에 따른 제1 감지신호들을 출력하며,

상기 제2 터치전극들은 상기 제2 영역에서 발생한 정전용량 변화에 따른 제2 감지신호들을 출력하는 것을 특징으로 하는 표시장치. - 제7 항에 있어서,

상기 제2 구간 동안에, 상기 복수 개의 화소들 중 상기 제2 영역에 배치된 화소들은 활성화되는 것을 특징으로 하는 표시장치. - 제1 항에 있어서,

상기 제1 스캔신호들을 제공하는 제1 스캔신호 출력부;

상기 제2 스캔신호들을 제공하는 제2 스캔신호 출력부; 및

상기 제1 감지신호들 및 상기 제2 감지신호들 중 적어도 어느 하나로부터 입력지점의 좌표정보를 산출하는 터치 감지부를 더 포함하는 표시장치. - 제9 항에 있어서,

상기 제1 스캔신호 출력부는 상기 제1 구간 동안 상기 제2 영역에 배치된 제1 터치코일들에게 상기 대응하는 제1 스캔신호들을 복수 회 제공하고,

상기 제2 스캔신호 출력부는 상기 제1 구간 동안 상기 제1 영역에 배치된 제1 터치전극들에게 상기 대응하는 제2 스캔신호들을 복수 회 제공하는 것을 특징으로 하는 표시장치. - 제9 항에 있어서,

상기 제1 감지신호들을 제1 디지털신호들로 변환하는 제1 신호처리부;

상기 제2 감지신호들을 제2 디지털신호들로 변환하는 제2 신호처리부;

상기 복수 개의 제2 터치전극들로부터 수신된 상기 제1 감지신호들을 상기 제1 신호처리부에 순차적으로 제공하는 제1 선택부;

상기 복수 개의 제2 터치코일들로부터 수신된 상기 제2 감지신호들을 상기 제2 신호처리부에 순차적으로 제공하는 제2 선택부;

상기 제1 디지털신호들 또는 상기 제2 디지털신호들 중 적어도 어느 하나의 신호들로부터 상기 입력지점의 좌표정보를 산출하는 좌표산출부를 포함하는 표시장치. - 프레임 구간 동안 이미지를 생성하는 표시패널 및 입력 코일들, 출력 코일들, 입력 전극들 및 출력 전극들을 구비한 터치패널을 포함하는 표시장치의 구동방법에 있어서,

상기 프레임 구간의 제1 구간 동안, 상기 표시패널의 제1 영역에 배치된 화소들을 활성화시키는 단계;

상기 입력 코일들 중 상기 제1 영역에 인접한 제2 영역에 배치된 입력 코일들에게 제1 스캔신호들을 제공하는 단계;

상기 입력 전극들 중 상기 표시패널의 제1 영역에 배치된 입력 전극들에게 제2 스캔신호들을 제공하는 단계; 및

상기 출력 코일들로부터 출력된, 상기 제2 영역에서 발생한 입력수단의 공진 주파수에 따른 제1 감지신호들 및 상기 출력 전극들로부터 출력된, 상기 제1 영역에서 발생한 정전용량 변화에 따른 제2 감지신호 중 적어도 어느 하나로부터 입력지점의 좌표정보를 산출하는 단계; 및

상기 제1 구간 이후의 제2 구간 동안, 상기 제2 영역에 배치된 화소들을 활성화시키는 단계를 포함하고,

상기 제2 구간 동안 상기 제1 영역에 배치된 상기 화소들은 비활성화되는 표시장치의 구동방법. - 제12 항에 있어서,

상기 제2 구간 동안,

상기 입력 코일들 중 상기 제1 영역에 배치된 입력 코일들에게 상기 제1 스캔신호들을 제공하는 단계;

상기 입력 전극들 중 상기 제2 영역에 배치된 입력 전극들에게 상기 제2 스캔신호들을 제공하는 단계; 및

상기 출력 코일들로부터 출력된, 상기 제1 영역에서 발생한 상기 입력수단의 공진 주파수에 따른 제1 감지신호들 및 상기 출력 전극들로부터 출력된, 상기 제2 영역에서 발생한 정전용량 변화에 따른 제2 감지신호 중 적어도 어느 하나로부터 입력지점의 좌표정보를 산출하는 단계를 더 포함하는 표시장치의 구동방법. - 제12 항에 있어서,

상기 제2 영역에 배치된 상기 입력 코일들에게 상기 제1 스캔신호들을 제공하는 단계에서, 상기 제1 스캔신호들은 상기 제2 영역에 배치된 상기 입력 코일들에게 복수 회 제공되고,

상기 제1 영역에 배치된 상기 입력 전극들에게 상기 제2 스캔신호들을 제공하는 단계에서, 상기 제2 스캔신호들은 상기 제1 영역에 배치된 상기 입력 전극들에게 복수 회 제공되는 것을 특징으로 하는 표시장치의 구동방법. - 복수 개의 화소들을 포함하며, 표시구간과 비표시구간을 포함하는 프레임 구간 동안 이미지를 생성하는 표시패널; 및

제1 터치코일들 및 상기 제1 터치코일들과 절연 교차하는 제2 터치코일들을 포함하는 제1 터치부 및 상기 제1 터치부 상측에 배치되고 제1 터치전극들 및 상기 제1 터치전극들과 절연 교차하는 제2 터치전극들을 포함하는 제2 터치부를 포함하는 터치패널을 포함하고,

상기 표시구간 동안에 상기 제1 터치코일들에게 제1 스캔신호들이 인가되고, 상기 비표시구간 동안에 상기 제1 터치전극들에게 제2 스캔신호들이 인가되며,

상기 제2 터치코일들은 입력수단의 공진 주파수에 따른 제1 감지신호들을 출력하며, 상기 제2 터치전극들은 정전용량 변화에 따른 제2 감지신호들을 출력하는 것을 특징으로 하는 표시장치. - 제15 항에 있어서,

상기 표시패널은,

상기 복수 개의 화소들이 배치된 제1 기판;

상기 제1 기판에 마주하는 제2 기판;

제1 방향으로 연장되며 상기 제1 방향에 직교하는 제2 방향으로 나열되고, 상기 복수 개의 화소들 중 대응하는 게이트 라인에 연결된 화소들을 턴-온 시키는 복수 개의 게이트 라인들; 및

상기 복수 개의 게이트 라인들에 절연 교차하고, 상기 턴-온 된 화소들에게 데이터 전압들을 제공하는 복수 개의 데이터 라인들;

을 포함하는 표시장치. - 제16 항에 있어서,

상기 표시구간 동안에 상기 복수 개의 게이트 라인들에게 게이트 신호들을 순차적으로 제공하는 게이트 구동부; 및

상기 복수 개의 데이터 라인들에게 상기 데이터 전압들을 제공하는 데이터 구동부를 포함하는 것을 특징으로 하는 표시장치.

을 포함하는 표시장치. - 제15 항에 있어서,

상기 제1 스캔신호들을 제공하는 제1 스캔신호 출력부;

상기 제2 스캔신호들을 제공하는 제2 스캔신호 출력부; 및

상기 제1 감지신호들 및 상기 제2 감지신호들 중 적어도 어느 하나로부터 입력지점의 좌표정보를 산출하는 터치 감지부를 더 포함하는 표시장치. - 제18 항에 있어서,

상기 표시구간은 상기 비표시구간보다 길고,

상기 제1 스캔신호 출력부는 상기 표시구간 동안에 상기 제1 터치코일들에게 상기 제1 스캔신호들을 복수 회 제공하는 것을 특징으로 하는 표시장치.

Priority Applications (13)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020130055845AKR102061569B1 (ko) | 2013-05-16 | 2013-05-16 | 표시장치 및 표시장치의 구동방법 |

| US14/024,241US9389737B2 (en) | 2012-09-14 | 2013-09-11 | Display device and method of driving the same in two modes |

| EP14156884.0AEP2772838B1 (en) | 2013-02-27 | 2014-02-26 | Display device comprising a touch panel and method of driving the same |

| JP2014036809AJP2014164770A (ja) | 2013-02-27 | 2014-02-27 | 表示装置及び表示装置の駆動方法 |

| CN201910723225.2ACN110568954B (zh) | 2013-02-27 | 2014-02-27 | 显示装置 |

| CN201410069635.7ACN104007876B (zh) | 2013-02-27 | 2014-02-27 | 显示装置及其驱动方法 |

| CN201910723324.0ACN110568955B (zh) | 2013-02-27 | 2014-02-27 | 显示装置及其驱动方法 |

| CN201910722889.7ACN110568953B (zh) | 2013-02-27 | 2014-02-27 | 显示装置 |

| US15/179,315US10191580B2 (en) | 2012-09-14 | 2016-06-10 | Display device and method of driving the same in two modes |

| JP2018112915AJP6657312B2 (ja) | 2013-02-27 | 2018-06-13 | 表示装置 |

| US16/163,301US10921924B2 (en) | 2012-09-14 | 2018-10-17 | Display device and method of driving the same in two modes |

| US17/152,722US11314368B2 (en) | 2012-09-14 | 2021-01-19 | Display device and method of driving the same in two modes |

| US17/712,170US11775124B2 (en) | 2012-09-14 | 2022-04-03 | Display device and method of driving the same in two modes |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020130055845AKR102061569B1 (ko) | 2013-05-16 | 2013-05-16 | 표시장치 및 표시장치의 구동방법 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20140135493A KR20140135493A (ko) | 2014-11-26 |

| KR102061569B1true KR102061569B1 (ko) | 2020-01-03 |

Family

ID=50389188

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020130055845AActiveKR102061569B1 (ko) | 2012-09-14 | 2013-05-16 | 표시장치 및 표시장치의 구동방법 |

Country Status (4)

| Country | Link |

|---|---|

| EP (1) | EP2772838B1 (ko) |

| JP (2) | JP2014164770A (ko) |

| KR (1) | KR102061569B1 (ko) |

| CN (4) | CN110568955B (ko) |

Families Citing this family (44)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104484071B (zh) | 2014-12-25 | 2018-01-02 | 上海天马微电子有限公司 | 一种触控面板和触控装置及其驱动方法 |

| KR101618286B1 (ko)* | 2015-02-12 | 2016-05-04 | 주식회사 더한 | 정전용량 및 전자기유도 방식에 의한 위치검출이 가능한 디스플레이 모듈 및 이를 구비한 디스플레이 장치 |

| KR102342869B1 (ko)* | 2015-02-26 | 2021-12-23 | 삼성디스플레이 주식회사 | 가요성 표시 장치 및 이의 제조방법 |

| KR102325383B1 (ko)* | 2015-02-26 | 2021-11-10 | 삼성디스플레이 주식회사 | 터치 센싱 장치 및 그 구동방법 |

| JP6416687B2 (ja)* | 2015-04-17 | 2018-10-31 | 株式会社ジャパンディスプレイ | 表示装置およびタッチ検出装置 |

| CN104777940B (zh)* | 2015-04-30 | 2017-11-14 | 京东方科技集团股份有限公司 | 一种触控电极层以及触摸屏 |

| DE102016206922A1 (de)* | 2015-05-08 | 2016-11-10 | Semiconductor Energy Laboratory Co., Ltd. | Touchscreen |

| JP6502178B2 (ja) | 2015-05-29 | 2019-04-17 | 株式会社ジャパンディスプレイ | 表示装置 |

| US10168844B2 (en) | 2015-06-26 | 2019-01-01 | Samsung Display Co., Ltd. | Flexible display device |

| JP6605292B2 (ja)* | 2015-10-16 | 2019-11-13 | 株式会社ジャパンディスプレイ | 表示装置 |

| JP6698386B2 (ja)* | 2016-03-10 | 2020-05-27 | 株式会社ジャパンディスプレイ | 表示装置およびタッチ検出装置 |

| KR102562627B1 (ko)* | 2016-03-21 | 2023-08-03 | 삼성디스플레이 주식회사 | 디스플레이 장치 |

| JP6639296B2 (ja)* | 2016-03-23 | 2020-02-05 | 株式会社ジャパンディスプレイ | 表示装置 |

| KR102534273B1 (ko) | 2016-03-25 | 2023-05-19 | 삼성디스플레이 주식회사 | 플렉서블 표시장치 |

| CN105786290A (zh) | 2016-04-28 | 2016-07-20 | 京东方科技集团股份有限公司 | 触摸感测器件、触控面板、显示面板和显示装置 |

| KR102558004B1 (ko) | 2016-05-17 | 2023-07-20 | 삼성전자주식회사 | 지문 인식 겸용 터치 스크린 장치 및 그 구동 방법, 상기 터치 스크린 장치를 포함하는 전자 기기 |

| JP6717673B2 (ja)* | 2016-06-10 | 2020-07-01 | 株式会社ジャパンディスプレイ | 入力検出装置および電子装置 |

| JP6704802B2 (ja)* | 2016-06-10 | 2020-06-03 | 株式会社ジャパンディスプレイ | 入力検出装置および電子装置 |

| JP6660846B2 (ja) | 2016-08-01 | 2020-03-11 | 株式会社ジャパンディスプレイ | 入力検出装置および電子装置 |

| JP6647173B2 (ja) | 2016-08-05 | 2020-02-14 | 株式会社ジャパンディスプレイ | 入力検出装置 |

| JP6673780B2 (ja)* | 2016-08-10 | 2020-03-25 | 株式会社ジャパンディスプレイ | 入力検出装置 |

| JP6662738B2 (ja)* | 2016-08-19 | 2020-03-11 | 株式会社ジャパンディスプレイ | 入力検出装置および電子装置 |

| JP6595424B2 (ja)* | 2016-08-26 | 2019-10-23 | 株式会社ジャパンディスプレイ | 入力検出装置 |

| WO2018051955A1 (ja)* | 2016-09-15 | 2018-03-22 | シャープ株式会社 | タッチパネル内蔵ディスプレイ |

| WO2018066685A1 (ja)* | 2016-10-06 | 2018-04-12 | シャープ株式会社 | タッチパネル及びタッチパネルシステム |

| KR102810070B1 (ko) | 2016-12-27 | 2025-05-21 | 엘지디스플레이 주식회사 | 표시 장치 |

| CN108363506B (zh)* | 2017-01-26 | 2021-06-01 | 奇景光电股份有限公司 | 触控显示设备以及用于触控显示面板的方法 |

| WO2018163973A1 (ja)* | 2017-03-07 | 2018-09-13 | シャープ株式会社 | タッチパネルおよび電子機器 |

| CN110546598B (zh) | 2017-03-07 | 2023-03-31 | 夏普株式会社 | 触摸面板和电子设备 |

| JP6792506B2 (ja)* | 2017-04-18 | 2020-11-25 | 株式会社ジャパンディスプレイ | 表示装置 |

| JP6872980B2 (ja)* | 2017-06-01 | 2021-05-19 | 株式会社ジャパンディスプレイ | 表示装置 |

| JP7007121B2 (ja)* | 2017-07-10 | 2022-01-24 | 株式会社ジャパンディスプレイ | 表示装置 |

| CN119376568A (zh) | 2018-02-13 | 2025-01-28 | 株式会社和冠 | 位置检测装置以及控制装置 |

| KR102290000B1 (ko)* | 2019-05-24 | 2021-08-18 | 고려대학교 산학협력단 | 모듈러 형태를 갖는 터치 센서 및 이를 포함하는 표시 장치 |

| US11983364B2 (en) | 2020-01-22 | 2024-05-14 | Hideep Inc. | Stylus pen, antenna module, touch sensor, and electronic device |

| JP7567814B2 (ja)* | 2020-01-31 | 2024-10-16 | ソニーグループ株式会社 | センサモジュールおよび電子機器 |

| CN111430372B (zh)* | 2020-03-31 | 2022-08-02 | 厦门天马微电子有限公司 | 一种阵列基板、显示面板及显示装置 |

| TWI746197B (zh)* | 2020-10-06 | 2021-11-11 | 友達光電股份有限公司 | 電子裝置 |

| JP7562364B2 (ja)* | 2020-10-13 | 2024-10-07 | エルジー ディスプレイ カンパニー リミテッド | タッチ表示装置 |

| CN113220163A (zh) | 2021-05-17 | 2021-08-06 | Tcl华星光电技术有限公司 | 一种触摸屏的扫描方法、装置及系统 |

| CN113672119B (zh)* | 2021-08-05 | 2024-03-26 | Tcl华星光电技术有限公司 | 显示装置 |

| JP7615411B1 (ja)* | 2023-06-01 | 2025-01-16 | 株式会社ワコム | ディスプレイ |

| WO2025005066A1 (ja)* | 2023-06-27 | 2025-01-02 | 株式会社ワコム | 位置検出装置及びセンサ |

| CN120066312B (zh)* | 2025-04-29 | 2025-08-22 | 深圳贝特莱电子科技股份有限公司 | 在显示灯阵上实现全屏触摸的方法、系统与电子烟 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20120154326A1 (en) | 2010-12-16 | 2012-06-21 | Liu Hung-Ta | Dual-Mode Touch Sensing Apparatus and Method Thereof |

| US20120154327A1 (en) | 2010-12-16 | 2012-06-21 | Liu Hung-Ta | Touch sensor and touch display apparatus and driving method thereof |

| US20120169400A1 (en) | 2010-12-31 | 2012-07-05 | Hong-Da Liu | Dual mode touch sensing module and dual mode touch sensing display |

Family Cites Families (37)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS578884A (en)* | 1980-06-20 | 1982-01-18 | Sony Corp | Position detecting device |

| EP0525413A3 (en)* | 1991-07-09 | 1993-11-24 | Seiko Instr Inc | Coordinate input apparatus having correction sense line |

| US6864882B2 (en)* | 2000-05-24 | 2005-03-08 | Next Holdings Limited | Protected touch panel display system |

| JP2002062983A (ja)* | 2000-08-21 | 2002-02-28 | Hitachi Ltd | ポインティングデバイス |

| KR100499576B1 (ko)* | 2003-03-28 | 2005-07-05 | 엘지.필립스 엘시디 주식회사 | 전자기 유도형 터치 패널을 구비한 횡전계형 액정 표시 장치 |

| JP5631535B2 (ja)* | 2005-02-08 | 2014-11-26 | オブロング・インダストリーズ・インコーポレーテッド | ジェスチャベースの制御システムのためのシステムおよび方法 |

| CN101034331B (zh)* | 2006-02-13 | 2011-03-16 | 智点科技(深圳)有限公司 | 一种电容式触控屏 |

| JP4787087B2 (ja)* | 2006-03-23 | 2011-10-05 | 株式会社ワコム | 位置検出装置及び情報処理装置 |

| WO2008032476A1 (fr)* | 2006-09-11 | 2008-03-20 | Sharp Kabushiki Kaisha | Écran tactile |

| US9442607B2 (en)* | 2006-12-04 | 2016-09-13 | Smart Technologies Inc. | Interactive input system and method |

| KR101337262B1 (ko)* | 2007-02-12 | 2013-12-05 | 삼성디스플레이 주식회사 | 표시 장치 및 그의 구동 방법 |

| KR101359921B1 (ko)* | 2007-03-02 | 2014-02-07 | 삼성디스플레이 주식회사 | 표시 장치 |

| JP5050818B2 (ja)* | 2007-03-14 | 2012-10-17 | セイコーエプソン株式会社 | 給電装置、情報処理装置および記憶性表示装置 |

| KR20090027948A (ko)* | 2007-09-13 | 2009-03-18 | 삼성전자주식회사 | 표시 패널 및 이 표시 패널을 갖는 표시 장치 |

| WO2009060454A2 (en)* | 2007-11-07 | 2009-05-14 | N-Trig Ltd. | Multi-point detection on a single-point detection digitizer |

| JP2009259063A (ja)* | 2008-04-18 | 2009-11-05 | Gunze Ltd | タッチパネルおよびその製造方法 |

| KR100955339B1 (ko)* | 2008-04-22 | 2010-04-29 | 주식회사 애트랩 | 접촉 및 접근을 감지할 수 있는 디스플레이 패널과디스플레이 장치 및 이 패널을 이용하는 접촉 및 접근 감지방법 |

| CN101339314B (zh)* | 2008-08-13 | 2010-08-18 | 友达光电股份有限公司 | 触控式显示面板、光电装置及其制造方法 |

| US8279202B2 (en)* | 2008-08-25 | 2012-10-02 | Chrontel International Ltd. | Methods of making and using an apparatus for providing multi-touch sensing capability using an LCD screen without an extra touch screen layer |

| JP4678431B2 (ja)* | 2008-10-20 | 2011-04-27 | 三菱電機株式会社 | タッチパネル |

| US8482545B2 (en)* | 2008-10-02 | 2013-07-09 | Wacom Co., Ltd. | Combination touch and transducer input system and method |

| JP5088307B2 (ja)* | 2008-12-03 | 2012-12-05 | 富士通モバイルコミュニケーションズ株式会社 | 入力装置 |

| JP4650703B2 (ja)* | 2008-12-25 | 2011-03-16 | ソニー株式会社 | 表示パネルおよびモジュール並びに電子機器 |

| CN101825788B (zh)* | 2009-03-04 | 2012-11-21 | 北京京东方光电科技有限公司 | 触摸显示器、tft-lcd阵列基板及其制造方法 |

| CN101930133A (zh)* | 2009-06-19 | 2010-12-29 | 台均科技(深圳)有限公司 | 液晶面板和液晶显示器 |

| CN102834793A (zh)* | 2010-03-29 | 2012-12-19 | 夏普株式会社 | 带触摸面板功能的显示装置 |

| JP2012068287A (ja)* | 2010-09-21 | 2012-04-05 | Toppan Printing Co Ltd | カラーフィルタ基板及びその製造方法 |

| CN103534670B (zh)* | 2010-10-28 | 2017-02-08 | 谱瑞科技股份有限公司 | 用电容性感测数组同步的触控笔 |

| TWI470530B (zh)* | 2011-02-01 | 2015-01-21 | Hungta Liu | 觸控感應元件暨其觸控顯示器相關裝置及其觸控驅動方法 |

| TWI407349B (zh)* | 2010-12-17 | 2013-09-01 | Au Optronics Corp | 觸控面板的觸控訊號掃描次數決定方法 |

| JP5432193B2 (ja)* | 2011-01-18 | 2014-03-05 | 株式会社ジャパンディスプレイ | 表示装置 |

| CN102163112B (zh)* | 2011-04-07 | 2014-07-23 | 台均科技(深圳)有限公司 | 传感器、双模式触控模组及双模式触控电子装置 |

| JP5459795B2 (ja)* | 2011-06-06 | 2014-04-02 | 株式会社ワコム | 電子機器 |

| JP2013018185A (ja)* | 2011-07-11 | 2013-01-31 | Innovation & Infinity Global Corp | 導電性多層構造及びそれを有するタッチパネル |

| JP5694536B2 (ja)* | 2011-07-29 | 2015-04-01 | シャープ株式会社 | 表示装置 |

| CN102375612B (zh)* | 2011-10-18 | 2014-07-09 | 台均科技(深圳)有限公司 | 触控阵列、触控传感器、触控显示屏及触控设备 |

| CN102662526B (zh)* | 2012-05-04 | 2016-01-20 | 福建华映显示科技有限公司 | 触控面板及其触控感测方法 |

- 2013

- 2013-05-16KRKR1020130055845Apatent/KR102061569B1/koactiveActive

- 2014

- 2014-02-26EPEP14156884.0Apatent/EP2772838B1/enactiveActive

- 2014-02-27CNCN201910723324.0Apatent/CN110568955B/zhactiveActive

- 2014-02-27CNCN201910723225.2Apatent/CN110568954B/zhactiveActive

- 2014-02-27CNCN201410069635.7Apatent/CN104007876B/zhactiveActive

- 2014-02-27JPJP2014036809Apatent/JP2014164770A/jaactivePending

- 2014-02-27CNCN201910722889.7Apatent/CN110568953B/zhactiveActive

- 2018

- 2018-06-13JPJP2018112915Apatent/JP6657312B2/jaactiveActive

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20120154326A1 (en) | 2010-12-16 | 2012-06-21 | Liu Hung-Ta | Dual-Mode Touch Sensing Apparatus and Method Thereof |

| US20120154327A1 (en) | 2010-12-16 | 2012-06-21 | Liu Hung-Ta | Touch sensor and touch display apparatus and driving method thereof |

| US20120169400A1 (en) | 2010-12-31 | 2012-07-05 | Hong-Da Liu | Dual mode touch sensing module and dual mode touch sensing display |

Also Published As

| Publication number | Publication date |

|---|---|

| EP2772838B1 (en) | 2017-05-03 |

| CN104007876A (zh) | 2014-08-27 |

| CN110568955B (zh) | 2023-07-04 |

| CN110568954B (zh) | 2023-09-19 |

| EP2772838A1 (en) | 2014-09-03 |

| CN110568953B (zh) | 2023-06-27 |

| KR20140135493A (ko) | 2014-11-26 |

| CN110568954A (zh) | 2019-12-13 |

| CN110568955A (zh) | 2019-12-13 |

| JP2018173971A (ja) | 2018-11-08 |

| JP6657312B2 (ja) | 2020-03-04 |

| CN104007876B (zh) | 2019-08-30 |

| CN110568953A (zh) | 2019-12-13 |

| JP2014164770A (ja) | 2014-09-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102061569B1 (ko) | 표시장치 및 표시장치의 구동방법 | |

| KR102207985B1 (ko) | 표시장치 | |

| US10921924B2 (en) | Display device and method of driving the same in two modes | |

| US11644916B2 (en) | Touch panel display device | |

| EP2985681B1 (en) | Touch sensor integrated type display device | |

| JP6254250B2 (ja) | 容量内蔵型タッチパネルと表示装置 | |

| US20140313434A1 (en) | Display apparatuses | |

| WO2014045601A1 (ja) | 液晶表示装置 | |

| KR20120000467A (ko) | 터치 센서가 내장된 액정 표시 장치 및 그 구동 방법과 그 제조 방법 | |

| JP6815812B2 (ja) | 表示装置 | |

| JP5807190B2 (ja) | 表示装置 | |

| JP2019016283A (ja) | 表示装置 | |

| WO2014045605A1 (ja) | 表示装置 | |

| US11775124B2 (en) | Display device and method of driving the same in two modes | |

| WO2014045602A1 (ja) | 表示装置 | |

| JP2011170784A (ja) | タッチパネル付き表示装置 | |

| WO2014045600A1 (ja) | 液晶表示装置 | |

| WO2014045603A1 (ja) | 入力装置 | |

| WO2014045606A1 (ja) | 入力装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0109 | Patent application | Patent event code:PA01091R01D Comment text:Patent Application Patent event date:20130516 | |

| PG1501 | Laying open of application | ||

| A201 | Request for examination | ||

| PA0201 | Request for examination | Patent event code:PA02012R01D Patent event date:20180420 Comment text:Request for Examination of Application Patent event code:PA02011R01I Patent event date:20130516 Comment text:Patent Application | |

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection | Comment text:Notification of reason for refusal Patent event date:20190417 Patent event code:PE09021S01D | |

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration | Patent event code:PE07011S01D Comment text:Decision to Grant Registration Patent event date:20191014 | |

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment | Comment text:Registration of Establishment Patent event date:20191226 Patent event code:PR07011E01D | |

| PR1002 | Payment of registration fee | Payment date:20191227 End annual number:3 Start annual number:1 | |

| PG1601 | Publication of registration | ||

| PR1001 | Payment of annual fee | Payment date:20221124 Start annual number:4 End annual number:4 | |

| PR1001 | Payment of annual fee | Payment date:20241125 Start annual number:6 End annual number:6 |