KR101735526B1 - Management system of electrical field circuit design - Google Patents

Management system of electrical field circuit designDownload PDFInfo

- Publication number

- KR101735526B1 KR101735526B1KR1020160137809AKR20160137809AKR101735526B1KR 101735526 B1KR101735526 B1KR 101735526B1KR 1020160137809 AKR1020160137809 AKR 1020160137809AKR 20160137809 AKR20160137809 AKR 20160137809AKR 101735526 B1KR101735526 B1KR 101735526B1

- Authority

- KR

- South Korea

- Prior art keywords

- rule

- attribute

- generation

- parameter

- electric field

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

- G06F17/5068—

Landscapes

- Management, Administration, Business Operations System, And Electronic Commerce (AREA)

Abstract

Translated fromKoreanDescription

Translated fromKorean본 발명의 일실시예는 전장 설계 회로도 관리 시스템에 관한 것으로 더욱 상세하게는 와 EB(Engineering Base), EPLAN, Auto CAD electrical 등의 전장 설계 프로그램에 사용될 수 있는 전장 설계 회로도 관리 시스템에 관한 것이다.An embodiment of the present invention relates to an electric field design circuit diagram management system, and more particularly, to an electric field design circuit diagram management system that can be used for electric field design programs such as EB (Engineering Base), EPLAN, and Auto CAD electrical.

전장이란 자동차, 항공기 등에 장착되는 각종 전자, 제어 장비들을 전기적으로 연결하는 기능을 하며 이러한 전자, 제어 장비들의 수는 점차 증가하고 전장의 구성은 더욱 복잡해지고 있다.The battlefield is a function to electrically connect various electronic and control equipments mounted on automobiles and airplanes, and the number of such electronic and control equipments is gradually increasing and the configuration of the battlefield is getting more complicated.

이와 같은 전장은 항공기, 자동차, 전자제품 등의 용도에 따라 차이는 있지만 기본적으로 와이어와 번들, 커넥터, 터미날, 조인 등의 디바이스들로 구성된다.Such battlefields are basically composed of devices such as wires, bundles, connectors, terminals, and joins, though they differ depending on applications such as aircraft, automobiles, and electronic products.

전장의 설계는 설계 단계의 가장 마지막에 이루어지고 있으며, 잦은 설계변경이 이루어짐에 따라 설계의 변경이 용이해야 하고, 설계가 변경될 때마다 그에 대한 이력관리가 철저하게 이루어지지 않으면 않된다.The design of the battlefield is done at the end of the design stage. As the design changes are made frequently, the design should be easy to change and the history management should be done thoroughly whenever the design is changed.

하지만, 현재의 전장설계를 관리 방법은 설계자가 전장설계를 프로그램으로 작성하여 문서를 출력한 후에, 이를 검증 및 승인을 받아 다음 단계의 설계자에게 넘겨주면, 다음 단계의 설계자가 설계를 하는 과정에서 이전 설계의 문제점이 드러나는 경우가 있으며, 이와 같이 호환성, 연계성의 문제가 나타나는 경우에 다시 설계를 수정해야 한다.However, in the present method of managing the electric field design, the designer writes the electric field design program as a program, outputs the document, verifies and approves it, and hands it to the designer in the next step. In some cases, design problems may arise, and in the event of such compatibility or connectivity problems, the design should be revised again.

이러한 과정이 매우 많은 시간을 소요하는 비합리적인 방법으로 인식되고 있으며, 설계의 수정에서 요구되는 파츠(parts) 리스트나 라우팅 리스트 등은 전산화된 자료로 확보되어 있지 않으므로 설계자는 일일이 이에 관한 문서를 찾아내야 하는 문제점이 있다.This process is recognized as an irrational way that takes a lot of time, and the parts lists and routing lists required for design modifications are not available as computerized data, so designers need to find documents on them There is a problem.

결국, 최초 전장설계도면이 완성되었을때 이것이 최종적으로 검증과 승인을 받기 위해서는 많은 단계들을 거쳐야 하나, 어느 부분에서는 네트워크를 이용하여 결재되고 어느 부분에서는 문서상으로 결재되는 문제점에 의해 전장설계도면의 이력관리는 그 신빙성을 상실한 상태이며, 설계에 이용되는 구성요소들에 대한 세부적인 사항을 확인하기 위해 많은 시간들을 소비해야 하는 문제가 있다.As a result, when the initial electric field design drawing is completed, it is necessary to go through many steps in order to finally obtain the verification and approval. In some cases, Has lost its credibility and has had to spend a lot of time to check the details of the components used in the design.

본 발명이 이루고자 하는 기술적 과제는 특정 프로젝트와 특정 디바이스 별로 관리가 가능하고, 관리자 및 사용자의 필요에 따라 설계 룰의 등록, 변경, 수정, 삭제가 허용되는 전장 설계 회로도 관리 시스템을 제공하는데 있다.SUMMARY OF THE INVENTION The present invention has been made in view of the above problems, and it is an object of the present invention to provide an electric field design circuit diagram management system capable of managing specific projects and specific devices and permitting the registration, modification, modification and deletion of design rules according to needs of an administrator and a user.

또한, 설계 회로도의 완성도를 표준 규격뿐만이 아닌 사용자 편집 룰과 비교하여 완성도를 판단함으로써 다른 주체에 의하여 진행되는 프로젝트별 전장 설계도의 연계성을 용이하게 판단할 수 있는 전장 설계 회로도 관리 시스템을 제공하는데 있다.Also, it is an object of the present invention to provide an electric field design circuit diagram management system which can easily determine the connectivity of project-specific electric field diagrams conducted by other entities by comparing the completeness of a design diagram with a user edit rule rather than a standard standard.

본 발명의 실시예에 따르면, 특정 프로젝트의 특정 디바이스에 개별적으로 적용되는 룰을 작성하는 룰 생성부; 상기 룰 생성부에서 생성한 생성 룰과 전장 설계에 관한 기본 와이어 룰 및 디바이스 룰을 관리하는 룰 관리부; 입력된 전장 설계 회로도에 기본 와이어 룰 및 디바이스 룰을 적용하여 매칭 여부를 판단하고, 상기 전장 설계 회로도의 프로젝트를 확인하고 이에 포함된 특정 디바이스에 대하여 상기 생성 룰을 적용하여 매칭 여부를 판단하는 룰 체크부; 상기 기본 와이어 룰, 디바이스 룰 및 생성 룰 매칭 결과를 생성하는 결과 생성부를 포함하는 전장 설계 회로도 관리 시스템를 제공한다.According to an embodiment of the present invention, a rule generation unit generates a rule that is individually applied to a specific device of a specific project. A rule management unit for managing a generation rule generated by the rule generation unit, a basic wire rule and a device rule related to electric field design; A rule check is performed to determine whether a match is made by applying a basic wire rule and a device rule to an inputted electric field design circuit diagram, to confirm a project of the electric field design circuit diagram, and to apply matching to the specific device included therein, part; And a result generation unit that generates the basic wire rule, the device rule, and the result of matching the generation rule.

상기 룰 생성부는 디바이스 타입, 연결 조건, 속성명, 속성 타입, 속성값, 속성값 조건, 코드 마스터, 타겟 디바이스 조건 및 설정 범위 중 적어도 하나의 파라미터를 포함하는 룰을 생성하여 등록할 수 있다.The rule generation unit may generate and register a rule including at least one of a device type, a connection condition, an attribute name, an attribute type, an attribute value, an attribute value condition, a code master, a target device condition, and a setting range.

상기 룰 생성부는 상기 디바이스 타입, 연결 조건, 속성명, 속성 타입, 속성값, 속성값 조건, 코드 마스터, 타겟 디바이스 조건 및 설정 범위 중 적어도 하나의 등록된 파라미터를 이용하여 생성 룰간의 계층 구조를 구분할 수 있다.The rule generation unit classifies the hierarchical structure between generation rules by using at least one registered parameter among the device type, connection condition, attribute name, attribute type, attribute value, attribute value condition, code master, target device condition and setting range .

상기 룰 생성부는 상기 생성 룰의 갱신, 변경, 삭제 인터페이스를 제공할 수 있다.The rule generation unit may provide an interface for updating, changing, and deleting the generation rule.

상기 결과 생성부는 디바이스 또는 와이어 별로 상기 매칭 결과를 생성할 수 있다.The result generator may generate the matching result for each device or wire.

상기 룰 체크부는 사용자의 입력에 따라 상기 생성 룰 중 매칭 여부를 판단하기 위한 룰과 그렇지 않은 룰을 구분하여 상기 생성 룰에 대한 매칭 여부를 판단할 수 있다.The rule check unit can discriminate whether or not the generation rule is matched by dividing a rule for determining whether or not a match is generated among the generation rules according to a user's input.

본 발명인 전장 설계 회로는 특정 프로젝트와 특정 디바이스 별로 관리가 가능하고, 관리자 및 사용자의 필요에 따라 설계 룰의 등록, 변경, 수정, 삭제가 허용된다.The electric field design circuit of the present invention can be managed for specific projects and specific devices, and registration, modification, modification, and deletion of design rules are allowed according to the needs of administrators and users.

또한, 설계 회로도의 완성도를 표준 규격뿐만이 아닌 사용자 편집 룰과 비교하여 완성도를 판단함으로써 다른 주체에 의하여 진행되는 프로젝트별 전장 설계도의 연계성을 용이하게 판단할 수 있다.In addition, the completeness of the design circuit diagram is compared with the user edit rule, not only the standard specification, but the completeness of the design circuit diagram can be easily determined.

도1은 본 발명의 일실시예에 따른 전장 설계 회로도 관리 시스템의 블록 구성도이고,

도2내지 도8은 본 발명의 일실시예에 따른 전장 설계 회로도 관리 시스템의 동작을 설명하기 위한 도면이고,

도8 내지 도14는 본 발명의 일실시예에 따른 전장 설계 회로도 관리 시스템의 생성 룰 동작을 설명하기 위한 도면이다.FIG. 1 is a block diagram of an electric field design circuit diagram management system according to an embodiment of the present invention,

FIGS. 2 to 8 are views for explaining the operation of the electric field design circuit diagram management system according to the embodiment of the present invention,

8 to 14 are diagrams for explaining the generation rule operation of the electric field design circuit diagram management system according to the embodiment of the present invention.

본 발명은 다양한 변경을 가할 수 있고 여러 가지 실시예를 가질 수 있는 바, 특정 실시예들을 도면에 예시하고 설명하고자 한다. 그러나, 이는 본 발명을 특정한 실시 형태에 대해 한정하려는 것이 아니며, 본 발명의 사상 및 기술 범위에 포함되는 모든 변경, 균등물 내지 대체물을 포함하는 것으로 이해되어야 한다.The present invention is capable of various modifications and various embodiments, and specific embodiments are illustrated and described in the drawings. It should be understood, however, that the invention is not intended to be limited to the particular embodiments, but includes all modifications, equivalents, and alternatives falling within the spirit and scope of the invention.

제2, 제1 등과 같이 서수를 포함하는 용어는 다양한 구성요소들을 설명하는데 사용될 수 있지만, 상기 구성요소들은 상기 용어들에 의해 한정되지는 않는다. 상기 용어들은 하나의 구성요소를 다른 구성요소로부터 구별하는 목적으로만 사용된다. 예를 들어, 본 발명의 권리 범위를 벗어나지 않으면서 제2 구성요소는 제1 구성요소로 명명될 수 있고, 유사하게 제1 구성요소도 제2 구성요소로 명명될 수 있다. 및/또는 이라는 용어는 복수의 관련된 기재된 항목들의 조합 또는 복수의 관련된 기재된 항목들 중의 어느 항목을 포함한다.The terms including ordinal, such as second, first, etc., may be used to describe various elements, but the elements are not limited to these terms. The terms are used only for the purpose of distinguishing one component from another. For example, without departing from the scope of the present invention, the second component may be referred to as a first component, and similarly, the first component may also be referred to as a second component. And / or < / RTI > includes any combination of a plurality of related listed items or any of a plurality of related listed items.

어떤 구성요소가 다른 구성요소에 "연결되어" 있다거나 "접속되어" 있다고 언급된 때에는, 그 다른 구성요소에 직접적으로 연결되어 있거나 또는 접속되어 있을 수도 있지만, 중간에 다른 구성요소가 존재할 수도 있다고 이해되어야 할 것이다. 반면에, 어떤 구성요소가 다른 구성요소에 "직접 연결되어" 있다거나 "직접 접속되어" 있다고 언급된 때에는, 중간에 다른 구성요소가 존재하지 않는 것으로 이해되어야 할 것이다.It is to be understood that when an element is referred to as being "connected" or "connected" to another element, it may be directly connected or connected to the other element, . On the other hand, when an element is referred to as being "directly connected" or "directly connected" to another element, it should be understood that there are no other elements in between.

본 출원에서 사용한 용어는 단지 특정한 실시예를 설명하기 위해 사용된 것으로, 본 발명을 한정하려는 의도가 아니다. 단수의 표현은 문맥상 명백하게 다르게 뜻하지 않는 한, 복수의 표현을 포함한다. 본 출원에서, "포함하다" 또는 "가지다" 등의 용어는 명세서상에 기재된 특징, 숫자, 단계, 동작, 구성요소, 부품 또는 이들을 조합한 것이 존재함을 지정하려는 것이지, 하나 또는 그 이상의 다른 특징들이나 숫자, 단계, 동작, 구성요소, 부품 또는 이들을 조합한 것들의 존재 또는 부가 가능성을 미리 배제하지 않는 것으로 이해되어야 한다.The terminology used in this application is used only to describe a specific embodiment and is not intended to limit the invention. The singular expressions include plural expressions unless the context clearly dictates otherwise. In the present application, the terms "comprises" or "having" and the like are used to specify that there is a feature, a number, a step, an operation, an element, a component or a combination thereof described in the specification, But do not preclude the presence or addition of one or more other features, integers, steps, operations, elements, components, or combinations thereof.

다르게 정의되지 않는 한, 기술적이거나 과학적인 용어를 포함해서 여기서 사용되는 모든 용어들은 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자에 의해 일반적으로 이해되는 것과 동일한 의미를 가지고 있다. 일반적으로 사용되는 사전에 정의되어 있는 것과 같은 용어들은 관련 기술의 문맥 상 가지는 의미와 일치하는 의미를 가지는 것으로 해석되어야 하며, 본 출원에서 명백하게 정의하지 않는 한, 이상적이거나 과도하게 형식적인 의미로 해석되지 않는다.Unless defined otherwise, all terms used herein, including technical or scientific terms, have the same meaning as commonly understood by one of ordinary skill in the art to which this invention belongs. Terms such as those defined in commonly used dictionaries are to be interpreted as having a meaning consistent with the contextual meaning of the related art and are to be interpreted as either ideal or overly formal in the sense of the present application Do not.

도1은 본 발명의 일실시예에 따른 전장 설계 회로도 관리 시스템의 블록 구성도이다.FIG. 1 is a block diagram of an electric field design circuit diagram management system according to an embodiment of the present invention.

도1을 참조하면 본 발명의 일실시예에 따른 전장 설계 회로도 관리 시스템(1)은 룰 생성부(10), 룰 관리부(20), 룰 체크부(30) 및 결과 생성부(40)를 포함하여 구성될 수 있다.1, an electric field design circuit

먼저, 룰 생성부(10)는 특정 프로젝트의 특정 디바이스에 개별적으로 적용되는 룰을 작성할 수 있다. 룰 생성부(10)는 관리자 또는 사용자에게 룰 생성 툴을 제공하며 툴을 이용하여 작성된 룰을 생성할 수 있다. 룰 생성부(10)는 룰 생성을 위한 기본적인 파라미터를 제공할 수 있다. 룰 생성부(10)는 예를 들면 디바이스 타입, 연결 조건, 속성명, 속성 타입, 속성값, 속성값 조건, 코드 마스터, 타겟 디바이스 조건 및 설정 범위 중 적어도 하나의 파라미터를 포함하여 룰을 생성하여 등록할 수 있다.First, the

룰 생성부(10)는 상기 파라미터를 관리자 또는 사용자가 설정할 수 있도록 툴을 제공하며 툴에 입력된 값에 따라 룰을 생성하여 등록할 수 있다.The

여기서 디바이스 타입은 전장 설계 회로도에서 사용되는 부품의 타입을 의미한다. 예를 들면, 차단기, 모터, 클램프, 펌프, 컨트롤러 등을 포함하는 모든 전장 설비의 종류를 의미할 수 있다.The device type here refers to the type of part used in the electrical design schematic. For example, it may refer to all kinds of electrical equipment including breakers, motors, clamps, pumps, controllers, and the like.

연결 조건은 룰 간의 연계 조건을 의미할 수 있으며 AND, OR, NOR, NAND 등의 논리 조건을 이용하여 설정될 수 있다.The connection condition may refer to a linkage condition between rules and may be set using logical conditions such as AND, OR, NOR, and NAND.

속성명은 디바이스 타입별로 정의되어 있는 속성을 의미하며 예를 들면 제품번호, 디바이스 명칭, 무게, 사용전압 등의 고유 속성을 의미할 수 있다.The attribute name means an attribute defined for each device type, and may mean a unique attribute such as a product number, a device name, a weight, and a use voltage.

속성 타입은 속성에 입력될 수 있는 값의 종류로 string, integer, reference로 구성될 수 있다. 여기서 string는 대상 디바이스의 조건 속성이 문자열일 경우, integer는 대상 디바이스의 조건 속성이 숫자일 경우, reference는 다른 디바이스를 참조하는 속성으로 구분될 수 있다.An attribute type is a type of value that can be entered in an attribute, and can consist of string, integer, and reference. Where string is the conditional attribute of the target device is a string, integer can be separated into attributes referring to other devices if the condition attribute of the target device is numeric.

속성값은 MAIN디바이스와 이외의 디바이스를 구분하는 파라미터이다.The attribute value is a parameter that distinguishes the MAIN device from other devices.

속성값 조건은 입력된 속성값의 조건을 입력 받는 곳으로 수식"<", ">", "=", "!=", ">=", "<=" 중에서 선택되어 사용될 수 있다.The attribute value condition can be used to select the condition of input property value from among the formulas "<", ">", "=", "! =", "> =", "<=".

코드 마스터는 입력된 속성값의 대표값과 단위를 설정하기 위한 파라미터로 대표값의 경우 사용자가 여러가지로 표현할 수 있는 값들을 지정된 대표값으로 변경할 수 있고 단위 값은 사용자가 사용할 수 있는 여러개의 단위값을 공통의 단위값으로 변경 할 수 있다.The code master is a parameter for setting the representative value and unit of the input attribute value. In the case of the representative value, the values that the user can express variously can be changed to the designated representative value, and the unit value is the unit value It can be changed to a common unit value.

또한, 룰 생성부(10)는 디바이스 타입, 연결 조건, 속성명, 속성 타입, 속성값, 속성값 조건, 코드 마스터, 타겟 디바이스 조건 및 설정 범위 중 적어도 하나의 등록된 파라미터를 이용하여 생성 룰간의 계층 구조를 구분할 수 있다. 생성 룰은 프로젝트별, 디바이스별로 구분되어 적용되는 것으로 룰 생성부는 생성된 룰간의 연계 구조를 파악하고 상위 계층의 생성 룰과 하위 계층의 생성 룰간의 계층 구조를 구분할 수 있다. 예를 들면 룰 생성부는 디바이스 타입을 참고하여 특정 디바이스의 생성 룰과 그 하위단에 연결되는 디바이스의 생성 룰간에 계층 구조를 구분할 수 있다. 또는 속성값을 이용하여 MAIN디바이스와 이외의 디바이스간의 생성 룰을 각각 상위 계층의 생성 룰과 하위 계층의 생성 룰로 구분할 수 있다.The

또한, 룰 생성부(10)는 생성 룰의 갱신, 변경, 삭제 인터페이스를 제공할 수 있다.In addition, the

다음으로, 룰 관리부(20)는 룰 생성부(10)에서 생성한 생성 룰과 전장 설계에 관한 기본 와이어 룰 및 디바이스 룰을 관리할 수 있다.Next, the

기본 와이어 룰은 관리자 또는 사용자에 의하여 변경 또는 삭제가 불가능한 규칙으로써 예를 들면, 플로팅 와이어 체크 룰, 그라운드 연결 체크 룰, N/C Pin연결 체크 룰, 와이어의 색상과 Pin의 속성 체크 룰 등을 포함하여 구성될 수 있다. 기본 와이어 룰의 변경 및 삭제는 불가능하지만 관리자 또는 사용자는 룰 체크부의 매칭 동작시 적용 기본 와이어 룰과 비적용 기본 와이어 룰의 적용 여부를 결정할 수 있다.The basic wire rule is a rule that can not be changed or deleted by an administrator or a user, for example, a floating wire check rule, a ground connection check rule, an N / C pin connection check rule, . It is not possible to change or delete the basic wire rule, but the manager or the user can determine whether or not to apply the applied basic wire rule and the non-applied basic wire rule in the matching operation of the rule check unit.

디바이스 룰은 관리자 또는 사용자에 의하여 변경 또는 삭제가 불가능한 규칙으로써 예를 들면, 접지선의 두께는 전원선의 공급선 두께에 종속적이어야 한다는 규칙 등을 포함할 수 있다. 디바이스 룰의 변경 및 삭제는 불가능하지만 관리자 또는 사용자는 룰 체크부의 매칭 동작시 적용 기본 와이어 룰과 비적용 기본 와이어 룰의 적용 여부를 결정할 수 있다.A device rule may be a rule that can not be changed or deleted by an administrator or a user. For example, the rule that the thickness of the ground wire should be dependent on the thickness of the power supply wire. It is not possible to change or delete the device rule, but the manager or the user can decide whether or not to apply the applied basic wire rule and the non-applied basic wire rule in the matching operation of the rule check unit.

룰 체크부(30)는 입력된 전장 설계 회로도에 기본 와이어 룰 및 디바이스 룰을 적용하여 매칭 여부를 판단하고, 전장 설계 회로도의 프로젝트를 확인하고 이에 포함된 특정 디바이스에 대하여 생성 룰을 적용하여 매칭 여부를 판단할 수 있다.The rule check unit 30 determines whether a match is made by applying a basic wire rule and a device rule to the inputted electric field designing circuit diagram, confirms a project of the electric field designing circuit diagram, applies a generation rule to the specific device included therein, Can be determined.

룰 체크부(30)는 전장 설계 회로도가 입력되는 경우 기본 와이어 룰 및 디바이스 룰의 매칭 여부를 판단하고 오류를 판단한다. 룰 체크부(30)는 전장 설계 회로도에 포함된 와이어와 디바이스에 대하여 각각 기본 와이어 룰 및 디바이스 룰을 적용하여 매칭 여부를 판단한다.The rule check unit 30 judges whether a basic wire rule and a device rule are matched when an electric field design circuit diagram is input, and judges an error. The rule check unit 30 determines whether or not to match the wire and device included in the electric field design circuit diagram by applying the basic wire rule and the device rule, respectively.

또한, 룰 체크부(30)는 전장 설계 회로도가 입력되는 경우 해당 전장 설계 회로도에 연계된 프로젝트를 확인하고 해당 프로젝트에 대하여 생성된 생성 룰을 검?뵉磯?. 룰 체크부(30)는 검색된 생성 룰을 이용하여 대응되는 디바이스에 생성 룰을 각각 적용하고 매칭 여부를 판단한다.Also, the rule check unit 30 checks the project linked to the electric circuit design diagram when the electric field design circuit diagram is input, and checks the generation rule generated for the project. The rule check unit 30 applies the generation rule to the corresponding device using the searched generation rule, and judges whether or not the matching is performed.

또한, 룰 체크부(30)는 사용자의 입력에 따라 생성 룰 중 매칭 여부를 판단하기 위한 룰과 그렇지 않은 룰을 구분하여 생성 룰에 대한 매칭 여부를 판단할 수 있다. 룰 체크부는 검색된 생성 룰 중에서 사용자가 적용을 배제한 생성 룰은 제외하고 나머지 검색된 생성 룰을 비교하여 매칭 여부를 판단한다.In addition, the rule check unit 30 can determine whether or not the generated rule is matched by dividing the rule for determining whether or not the rule is generated according to the user's input, and the rule for not generating the rule. The rule check unit compares the generated generated rules except for the generated rules excluding the application by the user, and compares the generated generated rules to determine whether they are matched.

결과 생성부(40)는 기본 와이어 룰, 디바이스 룰 및 생성 룰 매칭 결과를 생성할 수 있다. 결과 생성부(40)는 디바이스 또는 와이어 별로 매칭 결과를 생성하여 출력할 수 있다.The result generating unit 40 can generate a basic wire rule, a device rule, and a generation rule matching result. The result generating unit 40 may generate and output a matching result for each device or wire.

도2내지 도8은 본 발명의 일실시예에 따른 전장 설계 회로도 관리 시스템의 동작을 설명하기 위한 도면이다.FIGS. 2 to 8 are views for explaining the operation of the electrical field design circuit diagram management system according to an embodiment of the present invention.

도2를 참조하면, 전장 설계 회로도가 입력되면 해당 전장 설계 회로도의 프로젝트와 이에 포함되는 와이어 및 디바이스 목록을 인지한다.Referring to FIG. 2, when a full-scale design circuit diagram is input, a project of a full-scale design schematic and a list of wires and devices included therein are recognized.

도3을 참조하면, 입력된 전장 설계 회로도에 적용될 기본 와이어 룰, 디바이스 룰과 생성 룰을 로드한다. 이때 관리자 또는 사용자는 적용하고자 하는 룰을 선택할 수 있다.Referring to FIG. 3, a basic wire rule, a device rule, and a generation rule to be applied to the inputted electric field design circuit diagram are loaded. At this time, the administrator or the user can select a rule to be applied.

도4를 참조하면, 생성 룰이 적용될 디바이스를 항목별로 체크하여 관리자 또는 사용자 임의로 룰 체크를 진행할 수 있다.Referring to FIG. 4, a device to which a generation rule is to be applied may be checked for each item, and an administrator or a user can proceed to rule checking as desired.

도5를 참조하면, 입력된 전장 설계도 회로도의 와이어 룰 중 각 와이어 별로 적용하기 위한 와이어 룰을 체크할 수 있다.Referring to FIG. 5, it is possible to check a wire rule to be applied to each wire among the wire rules of the circuit diagram of the inputted electric field.

도6을 참조하면, 각각의 와이어 룰 중 와이어별로 체크된 항목에 대하여서만 매칭 여부를 판단한다.Referring to FIG. 6, it is determined whether or not matching is performed only on items checked for each wire among the wire rules.

도7을 참조하면, 와이어 룰 매칭 여부 결과를 리스트로 작성하여 출력하고, 도8을 참조하면, 와이어 룰 매칭 여부 판단 결과를 와이여 명과 함께 그림으로 도시하여 나타내고 있다.Referring to FIG. 7, the results of the wire rule matching are listed and outputted. Referring to FIG. 8, the results of the wire rule matching determination are shown together with the name and the name.

도9 내지 도14는 본 발명의 일실시예에 따른 전장 설계 회로도 관리 시스템의 생성 룰 동작을 설명하기 위한 도면이다.9 to 14 are diagrams for explaining the generation rule operation of the electric field design circuit diagram management system according to the embodiment of the present invention.

도9를 참조하면 메인 차단기를 체크하기 위한 생성 룰에 관한 것으로 생성 룰에 대한 설명과 파라미터를 개략적으로 나타내고 있다.Referring to FIG. 9, a description is given of generation rules for checking the main breaker, and explanations and parameters of the generation rules are schematically shown.

도10을 참조하면, 생성 룰의 파라미터 중 연결 조건을 나타내고 있으며, 도11을 참조하면, 디바이스 타입의 목록이 나열되어 선택할 수 있도록 되어 있다. 도12를 참조하면, 속성명을 입력할 수 있는 목록이 나열되어 선택할 수 있도록 되어 있으며, 도13을 참조하면, 대표값과 단위값을 선택하여 코드 마스터를 선택할 수 있도록 되어 있다.Referring to FIG. 10, connection conditions among parameters of a generation rule are shown. Referring to FIG. 11, a list of device types is listed and selectable. Referring to FIG. 12, a list in which an attribute name can be inputted is selected and selected. Referring to FIG. 13, a code master can be selected by selecting a representative value and a unit value.

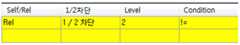

도14를 참조하면, 연결관계, 검색 방향, 디바이스 레벨, 조건 등의 연계 관계를 파라미터로 생성 룰에 포함하도록 설정할 수 있다. Self/Rel항목은 대상 디바이스가 자기 자신(self)인지 그렇지 않으면, 특정 디바이스로부터 특정 레벨단에 위치한 디바이스(relation)인지 선택할 수 있는 파라미터이고, 1/2차단은 Self/Rel항목에서 Rel을 선택하였을 경우 검색 방향을 설정하기 위한 파라미터이다. Level은 대상 디바이스를 중심으로 검색 가능한 디바이스의 범위를 나타내는 파라미터이고, condition은 디바이스의 검색 조건을 설정하기 위한 파라미터이다.Referring to FIG. 14, a linkage relationship such as a connection relation, a search direction, a device level, a condition, and the like can be set to be included in a generation rule as a parameter. Self / Rel is a parameter that allows the user to select whether the target device is self or a device located at a specific level from a specific device. Is a parameter for setting the search direction. Level is a parameter indicating the range of devices that can be searched centered on the target device, and condition is a parameter for setting the search condition of the device.

일예로 메인 차단기의 사용전류 속성이 10KA여야 하는 경우Self/Ref항목은 Self가 선택되어 1/2차단은 선택 할 수 없으며, Condition은 =으로, 속성은 사용전류, 속성 값은 10KA로 설정될 수 있다.For example, if the use current property of main breaker should be 10KA, Self / Ref item can be selected as Self and 1/2 can not be selected. Condition is =, property is current, property value is 10KA have.

다른 예로 메인 차단기 1차 바로 옆의 램프 (사용 전류 10KA)의 경우에는Self/Ref항목은 Ref가 선택되고, 1/2차단값은 1차단, 레벨은 1, Condition은 =, 디바이스는 Lamp, 속성은 사용전류, 속성 값은 10KA로 설정될 수 있다.As another example, in the case of the lamp (current 10KA) next to the main breaker primary, the Self / Ref item is selected, the 1/2 cutoff value is 1, the level is 1, the condition is = The used current, and the attribute value can be set to 10KA.

본 실시예에서 사용되는 '~부'라는 용어는 소프트웨어 또는 FPGA(field-programmable gate array) 또는 ASIC과 같은 하드웨어 구성요소를 의미하며, '~부'는 어떤 역할들을 수행한다. 그렇지만 '~부'는 소프트웨어 또는 하드웨어에 한정되는 의미는 아니다. '~부'는 어드레싱할 수 있는 저장 매체에 있도록 구성될 수도 있고 하나 또는 그 이상의 프로세서들을 재생시키도록 구성될 수도 있다. 따라서, 일 예로서 '~부'는 소프트웨어 구성요소들, 객체지향 소프트웨어 구성요소들, 클래스 구성요소들 및 태스크 구성요소들과 같은 구성요소들과, 프로세스들, 함수들, 속성들, 프로시저들, 서브루틴들, 프로그램 코드의 세그먼트들, 드라이버들, 펌웨어, 마이크로코드, 회로, 데이터, 데이터베이스, 데이터 구조들, 테이블들, 어레이들, 및 변수들을 포함한다. 구성요소들과 '~부'들 안에서 제공되는 기능은 더 작은 수의 구성요소들 및 '~부'들로 결합되거나 추가적인 구성요소들과 '~부'들로 더 분리될 수 있다. 뿐만 아니라, 구성요소들 및 '~부'들은 디바이스 또는 보안 멀티미디어카드 내의 하나 또는 그 이상의 CPU들을 재생시키도록 구현될 수도 있다.As used in this embodiment, the term " portion " refers to a hardware component such as software or an FPGA (field-programmable gate array) or ASIC, and 'part' performs certain roles. However, 'part' is not meant to be limited to software or hardware. &Quot; to " may be configured to reside on an addressable storage medium and may be configured to play one or more processors. Thus, by way of example, 'parts' may refer to components such as software components, object-oriented software components, class components and task components, and processes, functions, , Subroutines, segments of program code, drivers, firmware, microcode, circuitry, data, databases, data structures, tables, arrays, and variables. The functions provided in the components and components may be further combined with a smaller number of components and components or further components and components. In addition, the components and components may be implemented to play back one or more CPUs in a device or a secure multimedia card.

10: 룰 생성부

20: 룰 관리부

30: 룰 체크부

40: 결과 생성부10:

20:

30: rule check section

40:

Claims (6)

Translated fromKorean상기 룰 생성부에서 생성한 생성 룰과 전장 설계에 관한 기본 와이어 룰 및 디바이스 룰을 관리하는 룰 관리부;

입력된 전장 설계 회로도에 기본 와이어 룰 및 디바이스 룰을 적용하여 매칭 여부를 판단하고, 상기 전장 설계 회로도의 프로젝트를 확인하고 이에 포함된 특정 디바이스에 대하여 상기 생성 룰을 적용하여 매칭 여부를 판단하는 룰 체크부;

상기 기본 와이어 룰, 디바이스 룰 및 생성 룰 매칭 결과를 생성하는 결과 생성부를 포함하며,

상기 디바이스 타입은 전장 설계 회로도에서 사용되는 부품의 타입을 설정하기 위한 파라미터이고,

상기 연결 조건은 룰 간의 연계 조건을 설정하기 위한 파라미터이고,

상기 속성명은 디바이스 타입별로 정의되어 있는 속성을 설정하기 위한 파라미터이고,

상기 속성 타입은 속성에 입력될 수 있는 값의 종류를 설정하기 위한 파라미터이고,

상기 속성값은 MAIN디바이스와 이외의 디바이스를 구분하기 위한 값을 설정하기 위한 파라미터이고,

상기 속성값 조건은 입력된 속성값의 논리 조건을 설정하기 위한 파라미터이며,

상기 코드 마스터는 입력된 속성값의 대표값과 단위를 설정하기 위한 파라미터인 전장 설계 회로도 관리 시스템.A rule generation unit that generates rules that are individually applied to a specific device of a specific project including a device type, a connection condition, an attribute name, an attribute type, an attribute value, an attribute value condition, a code master, a target device condition, and a setting scope parameter;

A rule management unit for managing a generation rule generated by the rule generation unit, a basic wire rule and a device rule related to electric field design;

A rule check is performed to determine whether a match is made by applying a basic wire rule and a device rule to an inputted electric field design circuit diagram, to confirm a project of the electric field design circuit diagram, and to apply matching to the specific device included therein, part;

And a result generation unit for generating the basic wire rule, the device rule and the generation rule matching result,

The device type is a parameter for setting the type of the component used in the electric field design circuit diagram,

The connection condition is a parameter for setting a connection condition between rules,

The attribute name is a parameter for setting an attribute defined for each device type,

The attribute type is a parameter for setting a type of a value that can be input to an attribute,

The attribute value is a parameter for setting a value for distinguishing a MAIN device from other devices,

The attribute value condition is a parameter for setting a logical condition of an input attribute value,

Wherein the code master is a parameter for setting a representative value and a unit of an input attribute value.

상기 룰 생성부는 상기 디바이스 타입, 연결 조건, 속성명, 속성 타입, 속성값, 속성값 조건, 코드 마스터, 타겟 디바이스 조건 및 설정 범위 중 적어도 하나의 등록된 파라미터를 이용하여 생성 룰간의 계층 구조를 구분하는 전장 설계 회로도 관리 시스템.The method according to claim 1,

The rule generation unit classifies the hierarchical structure between generation rules by using at least one registered parameter among the device type, connection condition, attribute name, attribute type, attribute value, attribute value condition, code master, target device condition, Electric field design schematic management system.

상기 룰 생성부는 상기 생성 룰의 갱신, 변경, 삭제 인터페이스를 제공하는 전장 설계 회로도 관리 시스템.The method according to claim 1,

Wherein the rule generation unit provides an interface for updating, changing, and deleting the generation rule.

상기 결과 생성부는 디바이스 또는 와이어 별로 상기 매칭 결과를 생성하는 전장 설계 회로도 관리 시스템The method according to claim 1,

Wherein the result generating unit generates the matching result for each device or wire,

상기 룰 체크부는 사용자의 입력에 따라 상기 생성 룰 중 매칭 여부를 판단하기 위한 룰과 그렇지 않은 룰을 구분하여 상기 생성 룰에 대한 매칭 여부를 판단하는 전장 설계 회로도 관리 시스템.The method according to claim 1,

Wherein the rule check unit distinguishes between a rule for determining whether or not a match is generated among the generation rules and a rule that is not matched according to an input of a user, and determines whether the rule is matched with the generation rule.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020160137809AKR101735526B1 (en) | 2016-10-21 | 2016-10-21 | Management system of electrical field circuit design |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020160137809AKR101735526B1 (en) | 2016-10-21 | 2016-10-21 | Management system of electrical field circuit design |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR101735526B1true KR101735526B1 (en) | 2017-05-15 |

Family

ID=58739606

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020160137809AExpired - Fee RelatedKR101735526B1 (en) | 2016-10-21 | 2016-10-21 | Management system of electrical field circuit design |

Country Status (1)

| Country | Link |

|---|---|

| KR (1) | KR101735526B1 (en) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN112100779A (en)* | 2020-08-21 | 2020-12-18 | 广州明珞装备股份有限公司 | Method, system, device and medium for generating electrical drawing |

- 2016

- 2016-10-21KRKR1020160137809Apatent/KR101735526B1/ennot_activeExpired - Fee Related

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN112100779A (en)* | 2020-08-21 | 2020-12-18 | 广州明珞装备股份有限公司 | Method, system, device and medium for generating electrical drawing |

| CN112100779B (en)* | 2020-08-21 | 2024-05-14 | 广州明珞装备股份有限公司 | Method, system, device and medium for generating electrical drawing |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN114430827B (en) | Anomaly and drift detection using domain-indexed constraint repositories | |

| CA2786220C (en) | Validation of circuit definitions | |

| US7082590B2 (en) | Three-dimensional wire harness assembly models from three-dimensional zone models | |

| US20160299771A1 (en) | Collaborative generation of configuration technical data for a product to be manufactured | |

| US10831939B2 (en) | Printed circuit board design | |

| CN103294805A (en) | Creation method and device for data warehouse personalized dimension table | |

| KR101735526B1 (en) | Management system of electrical field circuit design | |

| US20180365341A1 (en) | Three-Dimensional Cad System Device, and Knowledge Management Method Used in Three-Dimensional Cad | |

| EP3525116A1 (en) | Management system of electrical field circuit design | |

| US20140297230A1 (en) | System and method for handling plant engineering data | |

| CN110866007A (en) | Information management method, system and computer equipment for big data application and table | |

| US20240111922A1 (en) | System and method for managing simulation artifacts | |

| US20210124566A1 (en) | Branch objects for dependent optimization problems | |

| CN114556238B (en) | Method and system for generating digital representations of asset information in a cloud computing environment | |

| US11061859B2 (en) | Object creation from hierarchical metadata stored on a storage device | |

| JP6919320B2 (en) | Parts search program, parts search method and parts search device | |

| CN114995719B (en) | List rendering method, device, device and storage medium | |

| CN111708582A (en) | On-line configuration method, device, and electronic device | |

| Masin et al. | Pluggable analysis viewpoints for design space exploration | |

| CN116484562A (en) | Component parameter processing method and device based on BIM platform | |

| CN1892661B (en) | Algorithm based on equivalence class to resolve short-circuit problem in IILVS | |

| US10430547B2 (en) | Universal circuit design systems and methods | |

| JP6364786B2 (en) | Design document management program, design document management method, and design document management apparatus | |

| US11586935B2 (en) | Systems and methods to semantically compare product configuration models | |

| CN114461878B (en) | Component classification and identification method and electronic equipment |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0109 | Patent application | St.27 status event code:A-0-1-A10-A12-nap-PA0109 | |

| PA0201 | Request for examination | St.27 status event code:A-1-2-D10-D11-exm-PA0201 | |

| PA0302 | Request for accelerated examination | St.27 status event code:A-1-2-D10-D17-exm-PA0302 St.27 status event code:A-1-2-D10-D16-exm-PA0302 | |

| D13-X000 | Search requested | St.27 status event code:A-1-2-D10-D13-srh-X000 | |

| D14-X000 | Search report completed | St.27 status event code:A-1-2-D10-D14-srh-X000 | |

| PE0902 | Notice of grounds for rejection | St.27 status event code:A-1-2-D10-D21-exm-PE0902 | |

| E13-X000 | Pre-grant limitation requested | St.27 status event code:A-2-3-E10-E13-lim-X000 | |

| P11-X000 | Amendment of application requested | St.27 status event code:A-2-2-P10-P11-nap-X000 | |

| P13-X000 | Application amended | St.27 status event code:A-2-2-P10-P13-nap-X000 | |

| PE0701 | Decision of registration | St.27 status event code:A-1-2-D10-D22-exm-PE0701 | |

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment | St.27 status event code:A-2-4-F10-F11-exm-PR0701 | |

| PR1002 | Payment of registration fee | St.27 status event code:A-2-2-U10-U11-oth-PR1002 Fee payment year number:1 | |

| PG1601 | Publication of registration | St.27 status event code:A-4-4-Q10-Q13-nap-PG1601 | |

| P22-X000 | Classification modified | St.27 status event code:A-4-4-P10-P22-nap-X000 | |

| P22-X000 | Classification modified | St.27 status event code:A-4-4-P10-P22-nap-X000 | |

| PC1903 | Unpaid annual fee | St.27 status event code:A-4-4-U10-U13-oth-PC1903 Not in force date:20200509 Payment event data comment text:Termination Category : DEFAULT_OF_REGISTRATION_FEE | |

| PC1903 | Unpaid annual fee | St.27 status event code:N-4-6-H10-H13-oth-PC1903 Ip right cessation event data comment text:Termination Category : DEFAULT_OF_REGISTRATION_FEE Not in force date:20200509 |