KR101097322B1 - 산화물 반도체 박막 트랜지스터, 그 제조방법 및 산화물 반도체 박막 트랜지스터를 구비한 유기전계 발광소자 - Google Patents

산화물 반도체 박막 트랜지스터, 그 제조방법 및 산화물 반도체 박막 트랜지스터를 구비한 유기전계 발광소자Download PDFInfo

- Publication number

- KR101097322B1 KR101097322B1KR1020090125031AKR20090125031AKR101097322B1KR 101097322 B1KR101097322 B1KR 101097322B1KR 1020090125031 AKR1020090125031 AKR 1020090125031AKR 20090125031 AKR20090125031 AKR 20090125031AKR 101097322 B1KR101097322 B1KR 101097322B1

- Authority

- KR

- South Korea

- Prior art keywords

- layer

- oxide semiconductor

- semiconductor layer

- thin film

- concentration

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000010409thin filmSubstances0.000titleclaimsabstractdescription85

- 238000004519manufacturing processMethods0.000titleclaimsdescription21

- 239000004065semiconductorSubstances0.000claimsabstractdescription201

- 239000000758substrateSubstances0.000claimsabstractdescription45

- 239000010408filmSubstances0.000claimsabstractdescription35

- 239000011701zincSubstances0.000claimsdescription76

- XLOMVQKBTHCTTD-UHFFFAOYSA-NZinc monoxideChemical compound[Zn]=OXLOMVQKBTHCTTD-UHFFFAOYSA-N0.000claimsdescription46

- 239000002184metalSubstances0.000claimsdescription28

- 229910052751metalInorganic materials0.000claimsdescription26

- 239000011787zinc oxideSubstances0.000claimsdescription23

- 229910052738indiumInorganic materials0.000claimsdescription22

- 229910052782aluminiumInorganic materials0.000claimsdescription18

- 229910052735hafniumInorganic materials0.000claimsdescription15

- 229910052725zincInorganic materials0.000claimsdescription15

- 238000000034methodMethods0.000claimsdescription13

- 229910052750molybdenumInorganic materials0.000claimsdescription13

- APFVFJFRJDLVQX-UHFFFAOYSA-Nindium atomChemical compound[In]APFVFJFRJDLVQX-UHFFFAOYSA-N0.000claimsdescription12

- 229910052804chromiumInorganic materials0.000claimsdescription10

- 229910052719titaniumInorganic materials0.000claimsdescription10

- GYHNNYVSQQEPJS-UHFFFAOYSA-NGalliumChemical compound[Ga]GYHNNYVSQQEPJS-UHFFFAOYSA-N0.000claimsdescription9

- 229910045601alloyInorganic materials0.000claimsdescription9

- 239000000956alloySubstances0.000claimsdescription9

- XAGFODPZIPBFFR-UHFFFAOYSA-NaluminiumChemical compound[Al]XAGFODPZIPBFFR-UHFFFAOYSA-N0.000claimsdescription9

- AJNVQOSZGJRYEI-UHFFFAOYSA-Ndigallium;oxygen(2-)Chemical compound[O-2].[O-2].[O-2].[Ga+3].[Ga+3]AJNVQOSZGJRYEI-UHFFFAOYSA-N0.000claimsdescription9

- 229910052733galliumInorganic materials0.000claimsdescription9

- 229910001195gallium oxideInorganic materials0.000claimsdescription9

- 229910052737goldInorganic materials0.000claimsdescription9

- AMGQUBHHOARCQH-UHFFFAOYSA-Nindium;oxotinChemical compound[In].[Sn]=OAMGQUBHHOARCQH-UHFFFAOYSA-N0.000claimsdescription9

- 229910052697platinumInorganic materials0.000claimsdescription9

- 229910052709silverInorganic materials0.000claimsdescription9

- 229910052715tantalumInorganic materials0.000claimsdescription9

- XOLBLPGZBRYERU-UHFFFAOYSA-Ntin dioxideChemical compoundO=[Sn]=OXOLBLPGZBRYERU-UHFFFAOYSA-N0.000claimsdescription9

- 229910001887tin oxideInorganic materials0.000claimsdescription9

- 229910052721tungstenInorganic materials0.000claimsdescription9

- YVTHLONGBIQYBO-UHFFFAOYSA-Nzinc indium(3+) oxygen(2-)Chemical compound[O--].[Zn++].[In+3]YVTHLONGBIQYBO-UHFFFAOYSA-N0.000claimsdescription9

- 239000011521glassSubstances0.000claimsdescription7

- 229910052710siliconInorganic materials0.000claimsdescription6

- 239000010703siliconSubstances0.000claimsdescription6

- 229910052814silicon oxideInorganic materials0.000claimsdescription6

- 229910004298SiO 2Inorganic materials0.000claimsdescription5

- 239000004033plasticSubstances0.000claimsdescription5

- 239000010410layerSubstances0.000description232

- 230000007423decreaseEffects0.000description10

- 229910003437indium oxideInorganic materials0.000description8

- PJXISJQVUVHSOJ-UHFFFAOYSA-Nindium(iii) oxideChemical compound[O-2].[O-2].[O-2].[In+3].[In+3]PJXISJQVUVHSOJ-UHFFFAOYSA-N0.000description8

- 229910021417amorphous siliconInorganic materials0.000description7

- 239000008186active pharmaceutical agentSubstances0.000description6

- 229910021420polycrystalline siliconInorganic materials0.000description6

- XUIMIQQOPSSXEZ-UHFFFAOYSA-NSiliconChemical compound[Si]XUIMIQQOPSSXEZ-UHFFFAOYSA-N0.000description5

- 229910052802copperInorganic materials0.000description4

- 230000015572biosynthetic processEffects0.000description3

- 229910052760oxygenInorganic materials0.000description3

- 229910018072Al 2 O 3Inorganic materials0.000description2

- 229910005265GaInZnOInorganic materials0.000description2

- 230000007547defectEffects0.000description2

- 230000005669field effectEffects0.000description2

- 238000002347injectionMethods0.000description2

- 239000007924injectionSubstances0.000description2

- 229910044991metal oxideInorganic materials0.000description2

- 150000004706metal oxidesChemical class0.000description2

- 239000000203mixtureSubstances0.000description2

- 238000000059patterningMethods0.000description2

- 238000011160researchMethods0.000description2

- 238000004544sputter depositionMethods0.000description2

- 229910004205SiNXInorganic materials0.000description1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-NSilicium dioxideChemical compoundO=[Si]=OVYPSYNLAJGMNEJ-UHFFFAOYSA-N0.000description1

- QVGXLLKOCUKJST-UHFFFAOYSA-Natomic oxygenChemical compound[O]QVGXLLKOCUKJST-UHFFFAOYSA-N0.000description1

- 239000003990capacitorSubstances0.000description1

- 238000012512characterization methodMethods0.000description1

- 239000013078crystalSubstances0.000description1

- 238000002425crystallisationMethods0.000description1

- 230000008025crystallizationEffects0.000description1

- 230000003247decreasing effectEffects0.000description1

- 238000000151depositionMethods0.000description1

- 230000008021depositionEffects0.000description1

- 230000006866deteriorationEffects0.000description1

- 230000002542deteriorative effectEffects0.000description1

- 239000003989dielectric materialSubstances0.000description1

- 238000005516engineering processMethods0.000description1

- 230000006870functionEffects0.000description1

- 230000005525hole transportEffects0.000description1

- 239000000463materialSubstances0.000description1

- 238000005259measurementMethods0.000description1

- 230000003287optical effectEffects0.000description1

- 239000001301oxygenSubstances0.000description1

- 230000002093peripheral effectEffects0.000description1

- 239000011241protective layerSubstances0.000description1

- 230000005428wave functionEffects0.000description1

Images

Classifications

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6755—Oxide semiconductors, e.g. zinc oxide, copper aluminium oxide or cadmium stannate

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/121—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements

- H10K59/1213—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements the pixel elements being TFTs

Landscapes

- Physics & Mathematics (AREA)

- Geometry (AREA)

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Thin Film Transistor (AREA)

- Electroluminescent Light Sources (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Liquid Crystal (AREA)

Abstract

Description

| Zn:In | Hf(at %) | VTH(V) | 이동도 (cm2/V·s) | S-팩터 (V/dec) | ΔV(V) |

| 38:55 | 5.0 | 0.08 | 16.96 | 0.28 | 10.1 |

| 38:55 | 7.8 | 1.91 | 11.94 | 0.35 | 9.4 |

| 35:54 | 11.0 | 1.95 | 6.70 | 0.32 | 5.1 |

| 39:48 | 12.3 | 4.56 | 2.59 | 0.81 | 3.7 |

| Zn:In | Hf(at %) | VTH(V) | 이동도 (cm2/V·s) | S-팩터 (V/dec) | ΔV(V) |

| 49:46 | 5.0 | 0.86 | 22.88 | 0.33 | 9.4 |

| 48:45 | 6.8 | 2.43 | 10.78 | 0.30 | 6.2 |

| 44:46 | 9.8 | 1.48 | 5.01 | 0.54 | 3.7 |

| 46:43 | 10.0 | 5.81 | 2.13 | 0.77 | 4.2 |

Claims (22)

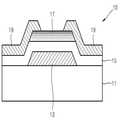

- 기판;상기 기판 상의 게이트 전극;상기 게이트 전극 및 노출된 상기 기판 위의 게이트 절연막;상기 게이트 절연막 위에서 상기 게이트 전극과 마주보는 위치에 있고, 상기 게이트 전극으로부터 멀어질수록 Hf 또는 Zn의 농도(원자백분율)가 점진적으로 높아지는 HfInZnO계 산화물 반도체로 이루어진 산화물 반도체층; 및상기 산화물 반도체층의 양측으로부터 상기 게이트 절연막 위로 연장되는 소스/드레인 영역;을 포함하는 박막 트랜지스터.

- 제1 항에 있어서, 상기 산화물 반도체층의 Hf의 농도가 9~15 at %(원자 백분율) (Hf, In, Zn의 at %의 합은 100)의 범위에 있는 박막 트랜지스터.

- 삭제

- 삭제

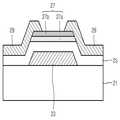

- 기판;상기 기판 상의 게이트 전극;상기 게이트 전극 및 노출된 상기 기판 위의 게이트 절연막;상기 게이트 절연막 위에서 상기 게이트 전극과 마주보는 위치에 있고, 상기 게이트 절연막 위의 제1 층 및 상기 제1 층 위의 제2 층을 포함하며, 상기 제2 층의 Hf의 농도가 상기 제1 층의 Hf의 농도보다 더 높거나 상기 제2 층의 Zn의 농도가 상기 제1 층의 Zn의 농도보다 더 높은, HfInZnO계 산화물 반도체로 이루어진 산화물 반도체층; 및상기 산화물 반도체층의 양측으로부터 상기 게이트 절연막 위로 연장되는 소스/드레인 영역;을 포함하는 박막 트랜지스터.

- 제5 항에 있어서, 상기 제1 층의 Hf이 3~15 at %의 범위를 갖고, 상기 제2 층의 Hf이 4~15 at %의 범위를 갖는 박막 트랜지스터.

- 삭제

- 제1 항 또는 제5항에 있어서, 상기 산화물 반도체층은 비정질인 박막 트랜지스터.

- 제1 항 또는 제5항에 있어서, 상기 산화물 반도체층은 결정질인 박막 트랜지스터.

- 제1 항 또는 제5항에 있어서, 상기 기판은 실리콘, 유리 또는 플라스틱으로 형성되어 있는 박막 트랜지스터.

- 제1 항 또는 제5항에 있어서, 상기 게이트 전극은 Ti, Pt, Ru, Cu, Au, Ag, Mo, Cr, Al, Ta,W 또는 이들의 합금과 같은 금속 또는 주석 산화물, 아연 산화물, 인듐 산화물, ITO(Indium Tin Oxide), IZO(Indium Zinc Oxide), GZO(gallium Zinc Oxide), IGO(Indium Gallium Oxide), AZO(Aluminum Znic Oxid)와 같은 전도성 산화물으로 형성되어 있는 박막 트랜지스터.

- 제1 항 또는 제5항에 있어서, 상기 게이트 절연막은 위로 SiO2, SiNx, SiON, HfO2, Al2O3-, Y2O3, Ta2O5 또는 이들의 조합으로 이루어진 형성되어 있는 박막 트랜지스터.

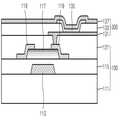

- 제1 항 또는 제5항에 있어서, 상기 기판과 상기 게이트 전극 사이에 버퍼층을 더 포함하는 박막 트랜지스터.

- 제1 항 또는 제5항에 있어서, 상기 산화물 반도체층 위에 식각 정지층을 더 포함하는 박막 트랜지스터.

- 기판 상에 게이트 전극을 형성하는 단계;상기 게이트 전극 및 노출된 상기 기판 상에 게이트 절연막을 형성하는 단계;상기 게이트 절연막 상에, 상기 게이트 전극으로부터 멀어질수록 Hf 또는 Zn의 농도가 점진적으로 높아지도록 HfInZnO계의 산화물 반도체층을 형성하는 단계; 및상기 산화물 반도체층의 양측으로부터 상기 게이트 절연막 위로 연장되는 소스/드레인 영역을 형성하는 단계;를 포함하는 박막 트랜지스터의 제조 방법.

- 제15 항에 있어서, 상기 산화물 반도체층을 형성하는 단계는 Hf이 9~15 at %(원자 백분율; Hf, In, Zn의 at %의 합은 100)의 범위에 있도록 상기 산화물 반도체층을 형성하는 박막 트랜지스터의 제조 방법.

- 제15 항에 있어서, 상기 산화물 반도체층을 형성하는 단계는 HfO2, In2O3, ZnO의 세 개의 타겟에 각각 파워를 인가하여 코스퍼터링을 실시하는 박막 트랜지스터의 제조 방법.

- 삭제

- 삭제

- 기판 상에 게이트 전극을 형성하는 단계;상기 게이트 전극 및 노출된 상기 기판 상에 게이트 절연막을 형성하는 단계;상기 게이트 절연막 상에, 제1층 및 상기 제1층 위의 제2층을 포함하고 상기 제2 층의 Hf의 농도가 상기 제1 층의 Hf의 농도보다 더 높거나 상기 제2 층의 Zn의 농도가 상기 제1 층의 Zn의 농도보다 더 높도록 HfInZnO계의 산화물 반도체층을 형성하는 단계; 및상기 산화물 반도체층의 양측으로부터 상기 게이트 절연막 위로 연장되는 소스/드레인 영역을 형성하는 단계;를 포함하는 박막 트랜지스터의 제조 방법.

- 삭제

- 제1 전극, 유기박막층, 제2 전극을 포함하는 유기전계 발광소자; 및기판; 상기 기판 상의 게이트 전극; 상기 게이트 전극 및 노출된 상기 기판 상의 게이트 절연막; 상기 게이트 절연막 위에서 상기 게이트 전극과 마주보는 위치에 있으면서, Hf이 9~15 at %(원자 백분율; Hf, In, Zn의 at %의 합은 100)의 범위에 있고, 하부에서 상부로 갈수록 Hf의 농도가 높아지는 HfInZnO계 산화물 반도체로 이루어진 산화물 반도체층; 및 상기 산화물 반도체층의 양측으로부터 상기 게이트 절연막 위로 연장되는 소스/드레인 영역;을 포함하는 상기 유기전계 발광소자를 제어하기 위한 박막 트랜지스터; 를 포함하는 유기전계 발광장치.

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020090125031AKR101097322B1 (ko) | 2009-12-15 | 2009-12-15 | 산화물 반도체 박막 트랜지스터, 그 제조방법 및 산화물 반도체 박막 트랜지스터를 구비한 유기전계 발광소자 |

| US12/873,206US8431927B2 (en) | 2009-12-15 | 2010-08-31 | Thin film transistor, method of manufacturing the same, and organic electroluminescent device including thin film transistor |

| TW099134824ATWI481037B (zh) | 2009-12-15 | 2010-10-13 | 薄膜電晶體、製造其之方法及包含其之有機電致發光裝置 |

| CN201010518645.6ACN102097486B (zh) | 2009-12-15 | 2010-10-20 | 薄膜晶体管及其制造方法以及有机电致发光设备 |

| JP2010278276AJP5400019B2 (ja) | 2009-12-15 | 2010-12-14 | 薄膜トランジスタ、その製造方法及び薄膜トランジスタを具備した有機電界発光装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020090125031AKR101097322B1 (ko) | 2009-12-15 | 2009-12-15 | 산화물 반도체 박막 트랜지스터, 그 제조방법 및 산화물 반도체 박막 트랜지스터를 구비한 유기전계 발광소자 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20110068181A KR20110068181A (ko) | 2011-06-22 |

| KR101097322B1true KR101097322B1 (ko) | 2011-12-23 |

Family

ID=44130457

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020090125031AActiveKR101097322B1 (ko) | 2009-12-15 | 2009-12-15 | 산화물 반도체 박막 트랜지스터, 그 제조방법 및 산화물 반도체 박막 트랜지스터를 구비한 유기전계 발광소자 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8431927B2 (ko) |

| JP (1) | JP5400019B2 (ko) |

| KR (1) | KR101097322B1 (ko) |

| CN (1) | CN102097486B (ko) |

| TW (1) | TWI481037B (ko) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101301219B1 (ko) | 2011-12-26 | 2013-08-28 | 연세대학교 산학협력단 | 박막 트랜지스터 및 박막 트랜지스터 제조 방법 |

| KR20190137266A (ko)* | 2018-06-01 | 2019-12-11 | 울산과학기술원 | Ta2O5/In2O3 적층구조의 제조방법 및 이에 따라 제조된 적층구조 |

Families Citing this family (32)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20230165355A (ko)* | 2009-09-16 | 2023-12-05 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시 장치 |

| KR20220127372A (ko)* | 2009-09-24 | 2022-09-19 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 산화물 반도체막 및 반도체 장치 |

| TWI406415B (zh)* | 2010-05-12 | 2013-08-21 | Prime View Int Co Ltd | 薄膜電晶體陣列基板及其製造方法 |

| TWI555205B (zh) | 2010-11-05 | 2016-10-21 | 半導體能源研究所股份有限公司 | 半導體裝置及半導體裝置的製造方法 |

| US8680627B2 (en)* | 2011-01-14 | 2014-03-25 | International Rectifier Corporation | Stacked half-bridge package with a common conductive clip |

| US8426952B2 (en) | 2011-01-14 | 2013-04-23 | International Rectifier Corporation | Stacked half-bridge package with a common conductive leadframe |

| US8674497B2 (en) | 2011-01-14 | 2014-03-18 | International Business Machines Corporation | Stacked half-bridge package with a current carrying layer |

| KR20130043063A (ko) | 2011-10-19 | 2013-04-29 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 반도체 장치의 제작 방법 |

| US9082861B2 (en)* | 2011-11-11 | 2015-07-14 | Semiconductor Energy Laboratory Co., Ltd. | Transistor with oxide semiconductor channel having protective layer |

| KR101942980B1 (ko) | 2012-01-17 | 2019-01-29 | 삼성디스플레이 주식회사 | 반도체 디바이스 및 그 형성 방법 |

| CN103378162A (zh)* | 2012-04-11 | 2013-10-30 | 东莞万士达液晶显示器有限公司 | 薄膜晶体管及其制作方法 |

| CN102637742A (zh)* | 2012-04-26 | 2012-08-15 | 北京大学 | 一种氧化物半导体薄膜晶体管及其制备方法 |

| CN104380473B (zh)* | 2012-05-31 | 2017-10-13 | 株式会社半导体能源研究所 | 半导体装置 |

| CN102723359B (zh) | 2012-06-13 | 2015-04-29 | 京东方科技集团股份有限公司 | 薄膜晶体管及其制作方法、阵列基板、显示装置 |

| KR102113160B1 (ko) | 2012-06-15 | 2020-05-20 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| WO2014061535A1 (en) | 2012-10-17 | 2014-04-24 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP6246549B2 (ja)* | 2012-10-17 | 2017-12-13 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| KR102720789B1 (ko)* | 2012-11-30 | 2024-10-22 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| KR102537022B1 (ko)* | 2013-05-20 | 2023-05-30 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| DE102014019794B4 (de)* | 2013-05-20 | 2024-10-24 | Semiconductor Energy Laboratory Co., Ltd. | Halbleitervorrichtung |

| JP6261125B2 (ja)* | 2014-01-31 | 2018-01-17 | 国立研究開発法人物質・材料研究機構 | 酸化物薄膜トランジスタおよびその製造方法 |

| CN103840011A (zh)* | 2014-02-26 | 2014-06-04 | 华中科技大学 | 氧化锌基非晶氧化物半导体薄膜晶体管及其制造方法 |

| KR102358289B1 (ko) | 2016-03-11 | 2022-02-03 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 복합체 및 트랜지스터 |

| CN105870173B (zh)* | 2016-04-26 | 2018-04-06 | 贵州民族大学 | 一种柔性全透明非晶氧化物薄膜晶体管及其制备方法 |

| CN106252394B (zh)* | 2016-08-30 | 2019-10-11 | 上海大学 | 氧化物薄膜的场效应晶体管器件及其制备方法 |

| KR101914835B1 (ko)* | 2016-11-18 | 2018-11-02 | 아주대학교산학협력단 | 금속산화물 이종 접합 구조, 이의 제조방법 및 이를 포함하는 박막트랜지스터 |

| KR102708746B1 (ko) | 2018-12-19 | 2024-09-20 | 엘지디스플레이 주식회사 | 박막 트랜지스터 및 이를 포함하는 표시장치 |

| CN111725238B (zh)* | 2019-03-19 | 2023-08-15 | 群创光电股份有限公司 | 具有晶体管元件的工作模块 |

| CN113838801B (zh)* | 2020-06-24 | 2024-10-22 | 京东方科技集团股份有限公司 | 半导体基板的制造方法和半导体基板 |

| CN113078112B (zh)* | 2021-03-29 | 2023-03-31 | 电子科技大学 | 一种氧化物基耗尽型负载反相器的制备方法 |

| CN113437018B (zh)* | 2021-06-02 | 2023-02-24 | 深圳市华星光电半导体显示技术有限公司 | 阵列基板的制造方法、阵列基板以及显示面板 |

| CN115832002B (zh)* | 2021-09-17 | 2025-09-09 | 京东方科技集团股份有限公司 | 薄膜晶体管及其制造方法、显示面板、显示设备 |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100916921B1 (ko) | 2008-06-26 | 2009-09-09 | 삼성모바일디스플레이주식회사 | 유기전계발광 표시 장치 및 그의 제조 방법 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06267867A (ja) | 1993-03-15 | 1994-09-22 | Nippon Telegr & Teleph Corp <Ntt> | 化合物半導体の結晶成長法およびこれを用いたオーミックコンタクトの形成法 |

| US6846751B2 (en) | 2002-12-13 | 2005-01-25 | Integrated Device Technology, Inc. | Nitrogen implementation to minimize device variation |

| US20050280100A1 (en) | 2004-06-17 | 2005-12-22 | Michael Artaki | Laterally diffused MOS device |

| KR101312259B1 (ko) | 2007-02-09 | 2013-09-25 | 삼성전자주식회사 | 박막 트랜지스터 및 그 제조방법 |

| KR101509663B1 (ko) | 2007-02-16 | 2015-04-06 | 삼성전자주식회사 | 산화물 반도체층 형성 방법 및 이를 이용한 반도체 소자제조방법 |

| JP4727684B2 (ja) | 2007-03-27 | 2011-07-20 | 富士フイルム株式会社 | 薄膜電界効果型トランジスタおよびそれを用いた表示装置 |

| US7935964B2 (en)* | 2007-06-19 | 2011-05-03 | Samsung Electronics Co., Ltd. | Oxide semiconductors and thin film transistors comprising the same |

| KR101468590B1 (ko) | 2007-12-06 | 2014-12-04 | 삼성전자주식회사 | 산화물 반도체 및 이를 포함하는 박막 트랜지스터 |

| KR20090002841A (ko) | 2007-07-04 | 2009-01-09 | 삼성전자주식회사 | 산화물 반도체, 이를 포함하는 박막 트랜지스터 및 그 제조방법 |

| KR100889688B1 (ko) | 2007-07-16 | 2009-03-19 | 삼성모바일디스플레이주식회사 | 반도체 활성층 제조 방법, 그를 이용한 박막 트랜지스터의제조 방법 및 반도체 활성층을 구비하는 박막 트랜지스터 |

| US8461583B2 (en)* | 2007-12-25 | 2013-06-11 | Idemitsu Kosan Co., Ltd. | Oxide semiconductor field effect transistor and method for manufacturing the same |

| KR101468591B1 (ko)* | 2008-05-29 | 2014-12-04 | 삼성전자주식회사 | 산화물 반도체 및 이를 포함하는 박막 트랜지스터 |

| KR101468594B1 (ko)* | 2008-07-31 | 2014-12-04 | 삼성전자주식회사 | 산화물 반도체 및 이를 포함하는 박막 트랜지스터 |

| US8378342B2 (en)* | 2009-03-23 | 2013-02-19 | Samsung Electronics Co., Ltd. | Oxide semiconductor and thin film transistor including the same |

| KR101638977B1 (ko)* | 2009-11-13 | 2016-07-12 | 삼성전자주식회사 | 트랜지스터와 그 제조방법 및 트랜지스터를 포함하는 전자소자 |

- 2009

- 2009-12-15KRKR1020090125031Apatent/KR101097322B1/koactiveActive

- 2010

- 2010-08-31USUS12/873,206patent/US8431927B2/enactiveActive

- 2010-10-13TWTW099134824Apatent/TWI481037B/zhactive

- 2010-10-20CNCN201010518645.6Apatent/CN102097486B/zhactiveActive

- 2010-12-14JPJP2010278276Apatent/JP5400019B2/jaactiveActive

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100916921B1 (ko) | 2008-06-26 | 2009-09-09 | 삼성모바일디스플레이주식회사 | 유기전계발광 표시 장치 및 그의 제조 방법 |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101301219B1 (ko) | 2011-12-26 | 2013-08-28 | 연세대학교 산학협력단 | 박막 트랜지스터 및 박막 트랜지스터 제조 방법 |

| KR20190137266A (ko)* | 2018-06-01 | 2019-12-11 | 울산과학기술원 | Ta2O5/In2O3 적층구조의 제조방법 및 이에 따라 제조된 적층구조 |

| KR102180014B1 (ko) | 2018-06-01 | 2020-11-17 | 울산과학기술원 | Ta2O5/In2O3 적층구조의 제조방법 및 이에 따라 제조된 적층구조 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN102097486A (zh) | 2011-06-15 |

| KR20110068181A (ko) | 2011-06-22 |

| TWI481037B (zh) | 2015-04-11 |

| CN102097486B (zh) | 2013-06-19 |

| US8431927B2 (en) | 2013-04-30 |

| TW201123460A (en) | 2011-07-01 |

| JP5400019B2 (ja) | 2014-01-29 |

| JP2011129923A (ja) | 2011-06-30 |

| US20110140096A1 (en) | 2011-06-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101097322B1 (ko) | 산화물 반도체 박막 트랜지스터, 그 제조방법 및 산화물 반도체 박막 트랜지스터를 구비한 유기전계 발광소자 | |

| KR101035357B1 (ko) | 산화물 반도체 박막 트랜지스터, 그 제조방법 및 산화물 반도체 박막 트랜지스터를 구비한 유기전계 발광소자 | |

| Fortunato et al. | Recent advances in ZnO transparent thin film transistors | |

| JP5467728B2 (ja) | 薄膜電界効果型トランジスタおよびその製造方法 | |

| US8314421B2 (en) | Thin film transistors and circuits with metal oxynitride active channel layers | |

| JP2009231664A (ja) | 電界効果トランジスタ及びその製造方法 | |

| JP2014229666A (ja) | 薄膜トランジスタ | |

| JP5274165B2 (ja) | 薄膜電界効果型トランジスタ及びその製造方法 | |

| JP2012028481A (ja) | 電界効果型トランジスタ及びその製造方法 | |

| JP6756875B1 (ja) | ディスプレイ用酸化物半導体薄膜、ディスプレイ用薄膜トランジスタ及びスパッタリングターゲット | |

| US8866141B2 (en) | Thin film transistor and method for fabricating the same | |

| TW201936951A (zh) | 氧化物半導體薄膜、薄膜電晶體及濺鍍靶材 | |

| TWI767186B (zh) | 氧化物半導體薄膜、薄膜電晶體及濺鍍靶 | |

| JP2011258804A (ja) | 電界効果型トランジスタ及びその製造方法 | |

| KR20110080118A (ko) | 다층의 식각 정지층을 구비한 박막 트랜지스터 및 그 제조방법 | |

| KR20200066372A (ko) | 산화물 반도체 박막 | |

| JP7625671B1 (ja) | 酸化物半導体薄膜、薄膜トランジスタおよびスパッタリングターゲット | |

| JP5489429B2 (ja) | 薄膜電界効果型トランジスタ | |

| KR20140071491A (ko) | 박막 트랜지스터, 박막 트랜지스터의 제조방법 및 반도체 장치 | |

| Wang | Composition Engineering for Solution-Processed Gallium-Rich Indium-Gallium-Zinc-Oxide Thin Film Transistors |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| PA0109 | Patent application | Patent event code:PA01091R01D Comment text:Patent Application Patent event date:20091215 | |

| PA0201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection | Comment text:Notification of reason for refusal Patent event date:20110421 Patent event code:PE09021S01D | |

| PG1501 | Laying open of application | ||

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration | Patent event code:PE07011S01D Comment text:Decision to Grant Registration Patent event date:20111121 | |

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment | Comment text:Registration of Establishment Patent event date:20111215 Patent event code:PR07011E01D | |

| PR1002 | Payment of registration fee | Payment date:20111216 End annual number:3 Start annual number:1 | |

| PG1601 | Publication of registration | ||

| FPAY | Annual fee payment | Payment date:20141128 Year of fee payment:4 | |

| PR1001 | Payment of annual fee | Payment date:20141128 Start annual number:4 End annual number:4 | |

| FPAY | Annual fee payment | Payment date:20171129 Year of fee payment:7 | |

| PR1001 | Payment of annual fee | Payment date:20171129 Start annual number:7 End annual number:7 | |

| FPAY | Annual fee payment | Payment date:20181126 Year of fee payment:8 | |

| PR1001 | Payment of annual fee | Payment date:20181126 Start annual number:8 End annual number:8 | |

| FPAY | Annual fee payment | Payment date:20191202 Year of fee payment:9 | |

| PR1001 | Payment of annual fee | Payment date:20191202 Start annual number:9 End annual number:9 | |

| PR1001 | Payment of annual fee | Payment date:20201201 Start annual number:10 End annual number:10 | |

| PR1001 | Payment of annual fee | Payment date:20211125 Start annual number:11 End annual number:11 | |

| PR1001 | Payment of annual fee | Payment date:20241125 Start annual number:14 End annual number:14 |