KR100269314B1 - 플라즈마처리를이용한반도체장치의커패시터제조방법 - Google Patents

플라즈마처리를이용한반도체장치의커패시터제조방법Download PDFInfo

- Publication number

- KR100269314B1 KR100269314B1KR1019970059413AKR19970059413AKR100269314B1KR 100269314 B1KR100269314 B1KR 100269314B1KR 1019970059413 AKR1019970059413 AKR 1019970059413AKR 19970059413 AKR19970059413 AKR 19970059413AKR 100269314 B1KR100269314 B1KR 100269314B1

- Authority

- KR

- South Korea

- Prior art keywords

- plasma

- capacitor

- film

- group

- dielectric

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D1/00—Resistors, capacitors or inductors

- H10D1/60—Capacitors

- H10D1/68—Capacitors having no potential barriers

- H10D1/682—Capacitors having no potential barriers having dielectrics comprising perovskite structures

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/201—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of only components covered by H10D1/00 or H10D8/00, e.g. RLC circuits

- H10D84/204—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of only components covered by H10D1/00 or H10D8/00, e.g. RLC circuits of combinations of diodes or capacitors or resistors

- H10D84/212—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of only components covered by H10D1/00 or H10D8/00, e.g. RLC circuits of combinations of diodes or capacitors or resistors of only capacitors

Landscapes

- Semiconductor Memories (AREA)

- Semiconductor Integrated Circuits (AREA)

Abstract

Description

Claims (26)

- 반도체기판 상에 커패시터를 형성하는 단계; 및상기 커패시터를 수소 원자가 함유된 소오스 가스의 플라즈마에 노출시키는 단계를 포함하는 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

- 제 1 항에 있어서, 상기 소오스 가스로서 암모니아(NH3), 수소분자(H2) 및 포스핀(PH3)으로 이루어진 군중 선택된 적어도 어느 하나를 사용하는 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

- 제 2 항에 있어서, 상기 소오스 가스로서 암모니아(NH3), 수소분자(H2) 및 포스핀(PH3)으로 이루어진 군중 선택된 적어도 어느 하나와 알곤 가스(Ar), 질소가스(N2), 일산화 이질소(N2O) 및 산소가스(O2)로 이루어진 군중 선택된 어느 하나가 결합된 혼합가스를 사용하는 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

- 제 3 항에 있어서, 상기 혼합가스는 NH3+ Ar, NH3+ N2O 또는 NH3+ O2인 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

- 제 1 항에 있어서, 상기 커패시터의 유전막 또는 상부전극을 상기 플라즈마에 노출시키는 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

- 제 5 항에 있어서, 상기 플라즈마는 ECR 플라즈마 또는 RF-플라즈마인 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

- 제 6 항에 있어서, 상기 ECR 플라즈마는 진동수가 2.45기가 헬쯔(Giga Hz) 정도인 ECR 마이크로파를 사용하여 형성하는 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

- 제 5 항에 있어서, 상기 유전막은 스퍼터링(sputtering)방식, 화학기상증착(Chemical Vapor Deposition)방식 및 솔-젤(sol-gel)방식으로 이루어진 군중 선택된 어느 하나로 형성하는 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

- 제 5 항에 있어서, 상기 유전막은 STO, BST, PZT, SBT, PLZT 및 BTO로 이루어진 군중 선택된 어느 하나로 형성하는 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

- 제 5 항에 있어서, 상기 상부 전극은 백금족, 백금족 산화물 및 이들의 혼합물로 이루어진 군중 선택된 어느 하나로 형성하는 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

- 제 10 항에 있어서, 상기 백금족 금속은 백금(Pt), 루테늄(Ru), 이리듐(Ir), 로듐(Rh), 오스뮴(Os) 및 팔라듐(Pd)으로 이루어진 군중 선택된 어느 하나로 형성하는 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

- 제 5 항에 있어서, 상기 플라즈마에 상기 상부전극을 노출한 다음 그 결과물을 열처리하는 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

- 제 6 항에 있어서, 상기 커패시터는 0.1∼10분 동안 상기 ECR 플라즈마 또는 RF 플라즈마중 선택된 어느 하나에 노출시키는 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

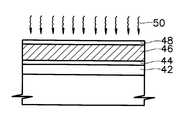

- (a) 반도체기판 상에 백금족 금속으로 하부전극을 형성하는 단계;(b) 상기 하부전극 상에 BST막을 형성하는 단계;(c) 상기 BST막을 수소 원자를 포함하는 소오스 가스를 이용한 플라즈마에 노출시키는 단계;(d) 상기 BST막 상에 백금족 금속으로 상부전극을 형성하는 단계; 및(e) 상기 결과물을 열처리하는 단계를 포함하는 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

- 제 14 항에 있어서, 상기 플라즈마는 ECR 플라즈마 또는 RF 플라즈마인 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

- 제 14 항에 있어서, 상기 열처리는 퍼니스(furnace)를 사용하는 방법 또는 급속 열 처리(rapid thermal annealing)방법으로 실행되는 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

- 제 15 항에 있어서, 상기 ECR 플라즈마는 진동수가 2.45기가 헬쯔(Giga Hz)정도인 ECR 마이크로파를 사용하여 형성하는 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

- 제 14 항에 있어서, 상기 소오스 가스로서 암모니아(NH3), 수소분자(H2) 및 포스핀(PH3)으로 이루어진 군중 선택된 적어도 어느 하나를 사용하는 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

- 제 14 항에 있어서, 상기 소오스 가스로서 암모니아(NH3), 수소분자(H2) 및 포스핀(PH3)으로 이루어진 군중 선택된 적어도 어느 하나와 알곤 가스(Ar), 질소가스(N2), 일산화 이질소(N2O) 및 산소 가스(O2)로 이루어진 군중 선택된 어느 하나가 결합된 혼합가스를 사용하는 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

- 제 19 항에 있어서, 상기 혼합가스는 NH3+ Ar, NH3+ N2O 또는 NH3+ O2인 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

- (a) 반도체기판 상에 백금족 금속으로 하부전극을 형성하는 단계;(b) 상기 하부전극 상에 BST막을 형성하는 단계;(c) 상기 BST막 상에 백금족 금속으로 상부전극을 형성하는 단계; 및(d) 상기 상부 전극을 수소 원자를 포함하는 소오스 가스를 이용한 플라즈마에 노출시키는 단계를 포함하는 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

- 제 21 항에 있어서, 상기 플라즈마는 ECR 플라즈마 또는 RF플라즈마인 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

- 제 22 항에 있어서, 상기 ECR 플라즈마는 진동수가 2.45기가 헬쯔(Giga Hz)정도인 ECR 마이크로파를 사용하여 형성되는 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

- 제 21 항에 있어서, 상기 소오스 가스는 암모니아(NH3), 수소분자(H2) 및 포스핀(PH3)으로 이루어진 군중 선택된 적어도 어느 하나를 사용하는 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

- 제 24 항에 있어서, 상기 소오스 가스로서 상기 암모니아(NH3), 수소분자(H2) 및 포스핀(PH3)으로 이루어진 군중 선택된 적어도 어느 하나와 알곤 가스(Ar), 질소가스(N2), 일산화 이질소(N2O) 및 산소가스(O2)로 이루어진 군중 선택된 어느 하나가 결합된 혼합가스를 사용하는 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

- 제 25 항에 있어서, 상기 혼합가스는 NH3+ Ar, NH3+ N2O 또는 NH3+ O2인 것을 특징으로 하는 반도체 장치의 커패시터 제조방법.

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1019970059413AKR100269314B1 (ko) | 1997-02-17 | 1997-11-12 | 플라즈마처리를이용한반도체장치의커패시터제조방법 |

| JP02438598AJP4804603B2 (ja) | 1997-02-17 | 1998-02-05 | 半導体装置のキャパシタ製造方法 |

| US09/022,311US6096592A (en) | 1997-02-17 | 1998-02-11 | Methods of forming integrated circuit capacitors having plasma treated regions therein |

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1019970004774 | 1997-02-17 | ||

| KR97-4774 | 1997-02-17 | ||

| KR19970004774 | 1997-02-17 | ||

| KR1019970059413AKR100269314B1 (ko) | 1997-02-17 | 1997-11-12 | 플라즈마처리를이용한반도체장치의커패시터제조방법 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR19980070086A KR19980070086A (ko) | 1998-10-26 |

| KR100269314B1true KR100269314B1 (ko) | 2000-10-16 |

Family

ID=26632523

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019970059413AExpired - Fee RelatedKR100269314B1 (ko) | 1997-02-17 | 1997-11-12 | 플라즈마처리를이용한반도체장치의커패시터제조방법 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US6096592A (ko) |

| JP (1) | JP4804603B2 (ko) |

| KR (1) | KR100269314B1 (ko) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20190049335A (ko)* | 2017-10-30 | 2019-05-09 | 타이완 세미콘덕터 매뉴팩쳐링 컴퍼니 리미티드 | 반도체 디바이스 및 그 제조 방법 |

Families Citing this family (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3209175B2 (ja) | 1998-02-23 | 2001-09-17 | 日本電気株式会社 | 薄膜キャパシタの製造方法 |

| US6201276B1 (en)* | 1998-07-14 | 2001-03-13 | Micron Technology, Inc. | Method of fabricating semiconductor devices utilizing in situ passivation of dielectric thin films |

| CA2351607A1 (en)* | 1998-11-27 | 2000-06-08 | Rohm Co., Ltd. | Method of forming inorganic compound solid and method of manufacturing semiconductor device employing the same |

| JP2000252359A (ja)* | 1999-03-03 | 2000-09-14 | Sony Corp | 絶縁膜のエッチング方法および配線層の形成方法 |

| KR100555483B1 (ko)* | 1999-09-03 | 2006-03-03 | 삼성전자주식회사 | 수소 열처리를 포함하는 반도체장치의 커패시터 제조방법 |

| KR100363081B1 (ko)* | 1999-09-16 | 2002-11-30 | 삼성전자 주식회사 | 박막 형성장치 |

| DE10008617A1 (de)* | 2000-02-24 | 2001-09-06 | Infineon Technologies Ag | Verfahren zur Herstellung einer ferroelektrischen Schicht |

| DE10065976A1 (de)* | 2000-02-25 | 2002-02-21 | Infineon Technologies Ag | Verfahren zur Herstellung eines Halbleiterbauelements |

| KR100587047B1 (ko)* | 2000-06-01 | 2006-06-07 | 주식회사 하이닉스반도체 | 반도체 메모리 소자의 캐패시터 제조방법 |

| KR100358149B1 (ko)* | 2000-06-30 | 2002-10-25 | 주식회사 하이닉스반도체 | 플라즈마 처리를 이용하여 강유전체 캐패시터의 열화를회복시키는 강유전체 메모리 소자 제조 방법 |

| US6943078B1 (en)* | 2000-08-31 | 2005-09-13 | Micron Technology, Inc. | Method and structure for reducing leakage current in capacitors |

| KR100376266B1 (ko)* | 2000-10-20 | 2003-03-17 | 주식회사 하이닉스반도체 | 반도체 소자의 캐패시터 제조 방법 |

| KR100399075B1 (ko)* | 2000-12-08 | 2003-09-26 | 주식회사 하이닉스반도체 | 반도체 소자의 강유전체 캐패시터 형성방법 |

| KR100387264B1 (ko)* | 2000-12-29 | 2003-06-12 | 주식회사 하이닉스반도체 | 반도체 소자의 캐패시터 제조 방법 |

| US6596652B2 (en)* | 2001-03-06 | 2003-07-22 | United Microelectronics Corp. | Method of fabricating low dielectric constant film |

| KR100399074B1 (ko)* | 2001-04-27 | 2003-09-26 | 주식회사 하이닉스반도체 | 비엘티 강유전체막을 구비하는 강유전체 메모리 소자 제조방법 |

| KR100418581B1 (ko)* | 2001-06-12 | 2004-02-11 | 주식회사 하이닉스반도체 | 메모리 소자의 제조방법 |

| KR100427030B1 (ko) | 2001-08-27 | 2004-04-14 | 주식회사 하이닉스반도체 | 다성분계 박막의 형성 방법 및 그를 이용한 커패시터의제조 방법 |

| KR20030025672A (ko) | 2001-09-22 | 2003-03-29 | 주식회사 하이닉스반도체 | 반도체 소자의 커패시터 제조방법 |

| KR20090091831A (ko) | 2001-10-02 | 2009-08-28 | 도꾸리쯔교세이호진상교기쥬쯔소고겡뀨죠 | 금속산화물 박막 및 그 제조방법 |

| US6656748B2 (en)* | 2002-01-31 | 2003-12-02 | Texas Instruments Incorporated | FeRAM capacitor post stack etch clean/repair |

| DE10239869A1 (de)* | 2002-08-29 | 2004-03-18 | Infineon Technologies Ag | Verbesserung der dielektrischen Eigenschaften von Schichten aus High-k-Materialien durch Plasmabehandlung |

| KR100548184B1 (ko)* | 2002-10-30 | 2006-02-02 | 고등기술연구원연구조합 | 대기압 플라즈마를 이용한 칫솔 살균 장치 |

| JP4523299B2 (ja)* | 2003-10-31 | 2010-08-11 | 学校法人早稲田大学 | 薄膜コンデンサの製造方法 |

| US20080272421A1 (en)* | 2007-05-02 | 2008-11-06 | Micron Technology, Inc. | Methods, constructions, and devices including tantalum oxide layers |

| US8012532B2 (en) | 2007-12-18 | 2011-09-06 | Micron Technology, Inc. | Methods of making crystalline tantalum pentoxide |

| US8208241B2 (en)* | 2008-06-04 | 2012-06-26 | Micron Technology, Inc. | Crystallographically orientated tantalum pentoxide and methods of making same |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0621333A (ja)* | 1992-07-03 | 1994-01-28 | Seiko Epson Corp | 半導体装置の製造方法 |

| JPH0714986A (ja)* | 1993-06-22 | 1995-01-17 | Toshiba Corp | 半導体装置の製造方法及びその製造装置 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0714986B2 (ja)* | 1987-03-06 | 1995-02-22 | 日本メクトロン株式会社 | アクリルエラストマ−の製造法 |

| JPH0621333B2 (ja)* | 1988-02-16 | 1994-03-23 | 住友金属工業株式会社 | ゼロスパングル処理用薬液噴霧ノズル |

| JP3169599B2 (ja)* | 1990-08-03 | 2001-05-28 | 株式会社日立製作所 | 半導体装置、その駆動方法、その読み出し方法 |

| US5305178A (en)* | 1991-08-12 | 1994-04-19 | The United States Of America As Represented By The Secretary Of The Army | Capacitor with increased electrical breakdown strength and method of forming the same |

| JP2987663B2 (ja)* | 1992-03-10 | 1999-12-06 | 株式会社日立製作所 | 基板処理装置 |

| DE69408405T2 (de)* | 1993-11-11 | 1998-08-20 | Nissin Electric Co Ltd | Plasma-CVD-Verfahren und Vorrichtung |

| US5468687A (en)* | 1994-07-27 | 1995-11-21 | International Business Machines Corporation | Method of making TA2 O5 thin film by low temperature ozone plasma annealing (oxidation) |

| US5541807A (en)* | 1995-03-17 | 1996-07-30 | Evans, Jr.; Joseph T. | Ferroelectric based capacitor for use in memory systems and method for fabricating the same |

| US5573979A (en)* | 1995-02-13 | 1996-11-12 | Texas Instruments Incorporated | Sloped storage node for a 3-D dram cell structure |

- 1997

- 1997-11-12KRKR1019970059413Apatent/KR100269314B1/konot_activeExpired - Fee Related

- 1998

- 1998-02-05JPJP02438598Apatent/JP4804603B2/janot_activeExpired - Fee Related

- 1998-02-11USUS09/022,311patent/US6096592A/ennot_activeExpired - Lifetime

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0621333A (ja)* | 1992-07-03 | 1994-01-28 | Seiko Epson Corp | 半導体装置の製造方法 |

| JPH0714986A (ja)* | 1993-06-22 | 1995-01-17 | Toshiba Corp | 半導体装置の製造方法及びその製造装置 |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20190049335A (ko)* | 2017-10-30 | 2019-05-09 | 타이완 세미콘덕터 매뉴팩쳐링 컴퍼니 리미티드 | 반도체 디바이스 및 그 제조 방법 |

| US10741678B2 (en) | 2017-10-30 | 2020-08-11 | Taiwan Semiconductor Manufacturing Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US10930769B2 (en) | 2017-10-30 | 2021-02-23 | Taiwan Semiconductor Manufacturing Co., Ltd. | Semiconductor device and manufacturing method thereof |

| KR102307829B1 (ko)* | 2017-10-30 | 2021-10-06 | 타이완 세미콘덕터 매뉴팩쳐링 컴퍼니 리미티드 | 반도체 디바이스 및 그 제조 방법 |

| US11631755B2 (en) | 2017-10-30 | 2023-04-18 | Taiwan Semiconductor Manufacturing Co., Ltd. | Semiconductor device and manufacturing method thereof |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4804603B2 (ja) | 2011-11-02 |

| US6096592A (en) | 2000-08-01 |

| JPH10233489A (ja) | 1998-09-02 |

| KR19980070086A (ko) | 1998-10-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100269314B1 (ko) | 플라즈마처리를이용한반도체장치의커패시터제조방법 | |

| US5972722A (en) | Adhesion promoting sacrificial etch stop layer in advanced capacitor structures | |

| KR100493040B1 (ko) | 반도체 소자의 커패시터 및 그 제조방법 | |

| US5254217A (en) | Method for fabricating a semiconductor device having a conductive metal oxide | |

| US6338994B1 (en) | Semiconductor device and method of fabricating thereof | |

| KR100417855B1 (ko) | 반도체소자의 캐패시터 및 그 제조방법 | |

| KR100494322B1 (ko) | 반도체 소자의 캐패시터 제조 방법 | |

| US20020076936A1 (en) | Method of fabricating semiconductor integrated circuit device and the semiconductor integrated circuit device | |

| KR100505397B1 (ko) | 반도체메모리소자의캐패시터제조방법 | |

| KR100269331B1 (ko) | 고유전체막을 구비하는 커패시터 형성방법 | |

| US6329237B1 (en) | Method of manufacturing a capacitor in a semiconductor device using a high dielectric tantalum oxide or barium strontium titanate material that is treated in an ozone plasma | |

| KR100395507B1 (ko) | 반도체 소자 및 그 제조방법 | |

| KR100519514B1 (ko) | TaON박막을 갖는 커패시터 제조방법 | |

| KR100474589B1 (ko) | 캐패시터제조방법 | |

| KR100717824B1 (ko) | 캐패시터 및 그의 제조방법 | |

| KR20010017212A (ko) | 반도체 소자의 캐패시터 제조 방법 | |

| KR100269298B1 (ko) | 반도체장치의백금막식각방법 | |

| KR0159013B1 (ko) | 반도체소자의 캐패시터 형성방법 | |

| KR100483359B1 (ko) | 반도체소자 제조방법 | |

| KR100390837B1 (ko) | 캐패시터 제조 방법 | |

| JPH1131682A (ja) | ドライエッチング方法および強誘電体メモリ素子の製造方法 | |

| KR100761406B1 (ko) | 탄탈륨산화막을 유전막으로 갖는 캐패시터의 제조 방법 | |

| KR100255660B1 (ko) | 이리듐막의 식각 방법 | |

| KR0180786B1 (ko) | 반도체소자의 캐패시터 형성방법 | |

| KR100673187B1 (ko) | 커패시터 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| PA0109 | Patent application | St.27 status event code:A-0-1-A10-A12-nap-PA0109 | |

| PA0201 | Request for examination | St.27 status event code:A-1-2-D10-D11-exm-PA0201 | |

| R17-X000 | Change to representative recorded | St.27 status event code:A-3-3-R10-R17-oth-X000 | |

| PG1501 | Laying open of application | St.27 status event code:A-1-1-Q10-Q12-nap-PG1501 | |

| R18-X000 | Changes to party contact information recorded | St.27 status event code:A-3-3-R10-R18-oth-X000 | |

| PN2301 | Change of applicant | St.27 status event code:A-3-3-R10-R13-asn-PN2301 St.27 status event code:A-3-3-R10-R11-asn-PN2301 | |

| PN2301 | Change of applicant | St.27 status event code:A-3-3-R10-R13-asn-PN2301 St.27 status event code:A-3-3-R10-R11-asn-PN2301 | |

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection | St.27 status event code:A-1-2-D10-D21-exm-PE0902 | |

| P11-X000 | Amendment of application requested | St.27 status event code:A-2-2-P10-P11-nap-X000 | |

| P13-X000 | Application amended | St.27 status event code:A-2-2-P10-P13-nap-X000 | |

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration | St.27 status event code:A-1-2-D10-D22-exm-PE0701 | |

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment | St.27 status event code:A-2-4-F10-F11-exm-PR0701 | |

| PR1002 | Payment of registration fee | St.27 status event code:A-2-2-U10-U11-oth-PR1002 Fee payment year number:1 | |

| R18-X000 | Changes to party contact information recorded | St.27 status event code:A-5-5-R10-R18-oth-X000 | |

| PG1601 | Publication of registration | St.27 status event code:A-4-4-Q10-Q13-nap-PG1601 | |

| PN2301 | Change of applicant | St.27 status event code:A-5-5-R10-R13-asn-PN2301 St.27 status event code:A-5-5-R10-R11-asn-PN2301 | |

| R18-X000 | Changes to party contact information recorded | St.27 status event code:A-5-5-R10-R18-oth-X000 | |

| R18-X000 | Changes to party contact information recorded | St.27 status event code:A-5-5-R10-R18-oth-X000 | |

| PR1001 | Payment of annual fee | St.27 status event code:A-4-4-U10-U11-oth-PR1001 Fee payment year number:4 | |

| R18-X000 | Changes to party contact information recorded | St.27 status event code:A-5-5-R10-R18-oth-X000 | |

| PR1001 | Payment of annual fee | St.27 status event code:A-4-4-U10-U11-oth-PR1001 Fee payment year number:5 | |

| PR1001 | Payment of annual fee | St.27 status event code:A-4-4-U10-U11-oth-PR1001 Fee payment year number:6 | |

| PN2301 | Change of applicant | St.27 status event code:A-5-5-R10-R13-asn-PN2301 St.27 status event code:A-5-5-R10-R11-asn-PN2301 | |

| PN2301 | Change of applicant | St.27 status event code:A-5-5-R10-R13-asn-PN2301 St.27 status event code:A-5-5-R10-R11-asn-PN2301 | |

| PR1001 | Payment of annual fee | St.27 status event code:A-4-4-U10-U11-oth-PR1001 Fee payment year number:7 | |

| PR1001 | Payment of annual fee | St.27 status event code:A-4-4-U10-U11-oth-PR1001 Fee payment year number:8 | |

| PR1001 | Payment of annual fee | St.27 status event code:A-4-4-U10-U11-oth-PR1001 Fee payment year number:9 | |

| PR1001 | Payment of annual fee | St.27 status event code:A-4-4-U10-U11-oth-PR1001 Fee payment year number:10 | |

| PR1001 | Payment of annual fee | St.27 status event code:A-4-4-U10-U11-oth-PR1001 Fee payment year number:11 | |

| PR1001 | Payment of annual fee | St.27 status event code:A-4-4-U10-U11-oth-PR1001 Fee payment year number:12 | |

| R18-X000 | Changes to party contact information recorded | St.27 status event code:A-5-5-R10-R18-oth-X000 | |

| FPAY | Annual fee payment | Payment date:20120706 Year of fee payment:13 | |

| PR1001 | Payment of annual fee | St.27 status event code:A-4-4-U10-U11-oth-PR1001 Fee payment year number:13 | |

| FPAY | Annual fee payment | Payment date:20130701 Year of fee payment:14 | |

| PR1001 | Payment of annual fee | St.27 status event code:A-4-4-U10-U11-oth-PR1001 Fee payment year number:14 | |

| LAPS | Lapse due to unpaid annual fee | ||

| PC1903 | Unpaid annual fee | St.27 status event code:A-4-4-U10-U13-oth-PC1903 Not in force date:20140721 Payment event data comment text:Termination Category : DEFAULT_OF_REGISTRATION_FEE | |

| PC1903 | Unpaid annual fee | St.27 status event code:N-4-6-H10-H13-oth-PC1903 Ip right cessation event data comment text:Termination Category : DEFAULT_OF_REGISTRATION_FEE Not in force date:20140721 | |

| P22-X000 | Classification modified | St.27 status event code:A-4-4-P10-P22-nap-X000 |