JP7112383B2 - Display panel manufacturing method - Google Patents

Display panel manufacturing methodDownload PDFInfo

- Publication number

- JP7112383B2 JP7112383B2JP2019500048AJP2019500048AJP7112383B2JP 7112383 B2JP7112383 B2JP 7112383B2JP 2019500048 AJP2019500048 AJP 2019500048AJP 2019500048 AJP2019500048 AJP 2019500048AJP 7112383 B2JP7112383 B2JP 7112383B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- light

- conductive film

- pixel

- display

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000004519manufacturing processMethods0.000titledescription28

- 239000010408filmSubstances0.000description965

- 230000006870functionEffects0.000description150

- 239000000463materialSubstances0.000description149

- 239000010410layerSubstances0.000description130

- 239000004065semiconductorSubstances0.000description97

- 239000000758substrateSubstances0.000description97

- 238000000034methodMethods0.000description85

- 238000001514detection methodMethods0.000description60

- 230000010365information processingEffects0.000description57

- 238000010586diagramMethods0.000description42

- XLOMVQKBTHCTTD-UHFFFAOYSA-NZinc monoxideChemical compound[Zn]=OXLOMVQKBTHCTTD-UHFFFAOYSA-N0.000description38

- 229910052738indiumInorganic materials0.000description37

- XUIMIQQOPSSXEZ-UHFFFAOYSA-NSiliconChemical compound[Si]XUIMIQQOPSSXEZ-UHFFFAOYSA-N0.000description36

- 229910052710siliconInorganic materials0.000description36

- 239000010703siliconSubstances0.000description36

- 239000011701zincSubstances0.000description33

- APFVFJFRJDLVQX-UHFFFAOYSA-Nindium atomChemical compound[In]APFVFJFRJDLVQX-UHFFFAOYSA-N0.000description31

- 239000004973liquid crystal related substanceSubstances0.000description30

- 229910052760oxygenInorganic materials0.000description30

- 238000012545processingMethods0.000description30

- 229910052751metalInorganic materials0.000description29

- QVGXLLKOCUKJST-UHFFFAOYSA-Natomic oxygenChemical compound[O]QVGXLLKOCUKJST-UHFFFAOYSA-N0.000description28

- 239000001301oxygenSubstances0.000description28

- 230000003287optical effectEffects0.000description26

- IJGRMHOSHXDMSA-UHFFFAOYSA-NAtomic nitrogenChemical compoundN#NIJGRMHOSHXDMSA-UHFFFAOYSA-N0.000description25

- 239000002184metalSubstances0.000description23

- 239000004020conductorSubstances0.000description21

- 229920005989resinPolymers0.000description21

- 239000011347resinSubstances0.000description21

- 239000010936titaniumSubstances0.000description20

- 238000004891communicationMethods0.000description19

- 239000007789gasSubstances0.000description19

- 229910044991metal oxideInorganic materials0.000description19

- 239000011787zinc oxideSubstances0.000description19

- RTAQQCXQSZGOHL-UHFFFAOYSA-NTitaniumChemical compound[Ti]RTAQQCXQSZGOHL-UHFFFAOYSA-N0.000description18

- 229910052719titaniumInorganic materials0.000description18

- 238000005530etchingMethods0.000description17

- 230000008569processEffects0.000description17

- 229910052725zincInorganic materials0.000description16

- 238000009792diffusion processMethods0.000description15

- HCHKCACWOHOZIP-UHFFFAOYSA-NZincChemical compound[Zn]HCHKCACWOHOZIP-UHFFFAOYSA-N0.000description14

- 230000005540biological transmissionEffects0.000description14

- 229920001721polyimidePolymers0.000description14

- 238000002834transmittanceMethods0.000description14

- 229910052581Si3N4Inorganic materials0.000description13

- 229910052782aluminiumInorganic materials0.000description13

- XAGFODPZIPBFFR-UHFFFAOYSA-NaluminiumChemical compound[Al]XAGFODPZIPBFFR-UHFFFAOYSA-N0.000description13

- 239000003990capacitorSubstances0.000description13

- 239000001257hydrogenSubstances0.000description13

- 229910052739hydrogenInorganic materials0.000description13

- 239000012535impuritySubstances0.000description13

- 239000002648laminated materialSubstances0.000description13

- 239000011368organic materialSubstances0.000description13

- HQVNEWCFYHHQES-UHFFFAOYSA-Nsilicon nitrideChemical compoundN12[Si]34N5[Si]62N3[Si]51N64HQVNEWCFYHHQES-UHFFFAOYSA-N0.000description13

- 229910052721tungstenInorganic materials0.000description13

- 239000010937tungstenSubstances0.000description13

- XKRFYHLGVUSROY-UHFFFAOYSA-NArgonChemical compound[Ar]XKRFYHLGVUSROY-UHFFFAOYSA-N0.000description12

- 239000004642PolyimideSubstances0.000description12

- 239000002131composite materialSubstances0.000description12

- 229910010272inorganic materialInorganic materials0.000description12

- 239000011147inorganic materialSubstances0.000description12

- 239000002346layers by functionSubstances0.000description12

- 229910052757nitrogenInorganic materials0.000description12

- UFHFLCQGNIYNRP-UHFFFAOYSA-NHydrogenChemical compound[H][H]UFHFLCQGNIYNRP-UHFFFAOYSA-N0.000description11

- ATJFFYVFTNAWJD-UHFFFAOYSA-NTinChemical compound[Sn]ATJFFYVFTNAWJD-UHFFFAOYSA-N0.000description11

- 239000013078crystalSubstances0.000description11

- 229910052733galliumInorganic materials0.000description11

- VYPSYNLAJGMNEJ-UHFFFAOYSA-Nsilicon dioxideInorganic materialsO=[Si]=OVYPSYNLAJGMNEJ-UHFFFAOYSA-N0.000description11

- 229910052709silverInorganic materials0.000description11

- 239000004332silverSubstances0.000description11

- 229910052718tinInorganic materials0.000description11

- WFKWXMTUELFFGS-UHFFFAOYSA-NtungstenChemical compound[W]WFKWXMTUELFFGS-UHFFFAOYSA-N0.000description11

- OKTJSMMVPCPJKN-UHFFFAOYSA-NCarbonChemical compound[C]OKTJSMMVPCPJKN-UHFFFAOYSA-N0.000description10

- XEEYBQQBJWHFJM-UHFFFAOYSA-NIronChemical compound[Fe]XEEYBQQBJWHFJM-UHFFFAOYSA-N0.000description10

- PXHVJJICTQNCMI-UHFFFAOYSA-NNickelChemical compound[Ni]PXHVJJICTQNCMI-UHFFFAOYSA-N0.000description10

- 239000011521glassSubstances0.000description10

- 239000003566sealing materialSubstances0.000description10

- 238000003860storageMethods0.000description10

- 239000004925Acrylic resinSubstances0.000description9

- 229920000178Acrylic resinPolymers0.000description9

- GYHNNYVSQQEPJS-UHFFFAOYSA-NGalliumChemical compound[Ga]GYHNNYVSQQEPJS-UHFFFAOYSA-N0.000description9

- MUBZPKHOEPUJKR-UHFFFAOYSA-NOxalic acidChemical compoundOC(=O)C(O)=OMUBZPKHOEPUJKR-UHFFFAOYSA-N0.000description9

- 230000015572biosynthetic processEffects0.000description9

- 150000004706metal oxidesChemical class0.000description9

- 238000004544sputter depositionMethods0.000description9

- RYGMFSIKBFXOCR-UHFFFAOYSA-NCopperChemical compound[Cu]RYGMFSIKBFXOCR-UHFFFAOYSA-N0.000description8

- NBIIXXVUZAFLBC-UHFFFAOYSA-NPhosphoric acidChemical compoundOP(O)(O)=ONBIIXXVUZAFLBC-UHFFFAOYSA-N0.000description8

- 229910052802copperInorganic materials0.000description8

- 239000010949copperSubstances0.000description8

- 230000005684electric fieldEffects0.000description8

- 229910021389grapheneInorganic materials0.000description8

- 229910052814silicon oxideInorganic materials0.000description8

- 238000004380ashingMethods0.000description7

- 238000004364calculation methodMethods0.000description7

- 239000000203mixtureSubstances0.000description7

- 238000001228spectrumMethods0.000description7

- 229910052715tantalumInorganic materials0.000description7

- GUVRBAGPIYLISA-UHFFFAOYSA-Ntantalum atomChemical compound[Ta]GUVRBAGPIYLISA-UHFFFAOYSA-N0.000description7

- MYMOFIZGZYHOMD-UHFFFAOYSA-NDioxygenChemical compoundO=OMYMOFIZGZYHOMD-UHFFFAOYSA-N0.000description6

- KDLHZDBZIXYQEI-UHFFFAOYSA-NPalladiumChemical compound[Pd]KDLHZDBZIXYQEI-UHFFFAOYSA-N0.000description6

- 229910052786argonInorganic materials0.000description6

- 239000000969carrierSubstances0.000description6

- 239000003086colorantSubstances0.000description6

- 150000001875compoundsChemical class0.000description6

- 229910001882dioxygenInorganic materials0.000description6

- 230000000694effectsEffects0.000description6

- 229910003437indium oxideInorganic materials0.000description6

- PJXISJQVUVHSOJ-UHFFFAOYSA-Nindium(iii) oxideChemical compound[O-2].[O-2].[O-2].[In+3].[In+3]PJXISJQVUVHSOJ-UHFFFAOYSA-N0.000description6

- AMGQUBHHOARCQH-UHFFFAOYSA-Nindium;oxotinChemical compound[In].[Sn]=OAMGQUBHHOARCQH-UHFFFAOYSA-N0.000description6

- 239000002070nanowireSubstances0.000description6

- TWNQGVIAIRXVLR-UHFFFAOYSA-Noxo(oxoalumanyloxy)alumaneChemical compoundO=[Al]O[Al]=OTWNQGVIAIRXVLR-UHFFFAOYSA-N0.000description6

- -1polyethylene terephthalatePolymers0.000description6

- YVTHLONGBIQYBO-UHFFFAOYSA-Nzinc indium(3+) oxygen(2-)Chemical compound[O--].[Zn++].[In+3]YVTHLONGBIQYBO-UHFFFAOYSA-N0.000description6

- ZOKXTWBITQBERF-UHFFFAOYSA-NMolybdenumChemical compound[Mo]ZOKXTWBITQBERF-UHFFFAOYSA-N0.000description5

- 239000004952PolyamideSubstances0.000description5

- 239000000853adhesiveSubstances0.000description5

- 230000001070adhesive effectEffects0.000description5

- 238000006243chemical reactionMethods0.000description5

- PMHQVHHXPFUNSP-UHFFFAOYSA-Mcopper(1+);methylsulfanylmethane;bromideChemical compoundBr[Cu].CSCPMHQVHHXPFUNSP-UHFFFAOYSA-M0.000description5

- 239000005262ferroelectric liquid crystals (FLCs)Substances0.000description5

- 229910052742ironInorganic materials0.000description5

- 229910052750molybdenumInorganic materials0.000description5

- 239000011733molybdenumSubstances0.000description5

- 239000002105nanoparticleSubstances0.000description5

- 229910052759nickelInorganic materials0.000description5

- 239000000243solutionSubstances0.000description5

- XLYOFNOQVPJJNP-UHFFFAOYSA-NwaterSubstancesOXLYOFNOQVPJJNP-UHFFFAOYSA-N0.000description5

- 229910001868waterInorganic materials0.000description5

- 238000001039wet etchingMethods0.000description5

- VYZAMTAEIAYCRO-UHFFFAOYSA-NChromiumChemical compound[Cr]VYZAMTAEIAYCRO-UHFFFAOYSA-N0.000description4

- PWHULOQIROXLJO-UHFFFAOYSA-NManganeseChemical compound[Mn]PWHULOQIROXLJO-UHFFFAOYSA-N0.000description4

- 229910006404SnO 2Inorganic materials0.000description4

- NRTOMJZYCJJWKI-UHFFFAOYSA-NTitanium nitrideChemical compound[Ti]#NNRTOMJZYCJJWKI-UHFFFAOYSA-N0.000description4

- 229910000147aluminium phosphateInorganic materials0.000description4

- 238000000231atomic layer depositionMethods0.000description4

- 230000000903blocking effectEffects0.000description4

- 230000008859changeEffects0.000description4

- 239000000460chlorineSubstances0.000description4

- 229910052804chromiumInorganic materials0.000description4

- 239000011651chromiumSubstances0.000description4

- 239000000470constituentSubstances0.000description4

- 239000013256coordination polymerSubstances0.000description4

- 238000005520cutting processMethods0.000description4

- 230000006837decompressionEffects0.000description4

- 238000001312dry etchingMethods0.000description4

- 238000005401electroluminescenceMethods0.000description4

- 238000010894electron beam technologyMethods0.000description4

- MRELNEQAGSRDBK-UHFFFAOYSA-Nlanthanum(3+);oxygen(2-)Chemical compound[O-2].[O-2].[O-2].[La+3].[La+3]MRELNEQAGSRDBK-UHFFFAOYSA-N0.000description4

- 239000011572manganeseSubstances0.000description4

- PLDDOISOJJCEMH-UHFFFAOYSA-Nneodymium(3+);oxygen(2-)Chemical compound[O-2].[O-2].[O-2].[Nd+3].[Nd+3]PLDDOISOJJCEMH-UHFFFAOYSA-N0.000description4

- 150000004767nitridesChemical class0.000description4

- 150000002894organic compoundsChemical class0.000description4

- BASFCYQUMIYNBI-UHFFFAOYSA-NplatinumChemical compound[Pt]BASFCYQUMIYNBI-UHFFFAOYSA-N0.000description4

- 229920002647polyamidePolymers0.000description4

- 239000004417polycarbonateSubstances0.000description4

- 229920000515polycarbonatePolymers0.000description4

- 229920000728polyesterPolymers0.000description4

- 229920000098polyolefinPolymers0.000description4

- 239000002096quantum dotSubstances0.000description4

- 239000005341toughened glassSubstances0.000description4

- QTBSBXVTEAMEQO-UHFFFAOYSA-NAcetic acidChemical compoundCC(O)=OQTBSBXVTEAMEQO-UHFFFAOYSA-N0.000description3

- ZOXJGFHDIHLPTG-UHFFFAOYSA-NBoronChemical compound[B]ZOXJGFHDIHLPTG-UHFFFAOYSA-N0.000description3

- 102100027310Bromodomain adjacent to zinc finger domain protein 1AHuman genes0.000description3

- 229910052684CeriumInorganic materials0.000description3

- ZAMOUSCENKQFHK-UHFFFAOYSA-NChlorine atomChemical compound[Cl]ZAMOUSCENKQFHK-UHFFFAOYSA-N0.000description3

- 101000937778Homo sapiens Bromodomain adjacent to zinc finger domain protein 1AProteins0.000description3

- FYYHWMGAXLPEAU-UHFFFAOYSA-NMagnesiumChemical compound[Mg]FYYHWMGAXLPEAU-UHFFFAOYSA-N0.000description3

- 229910052779NeodymiumInorganic materials0.000description3

- 229910004298SiO 2Inorganic materials0.000description3

- QCWXUUIWCKQGHC-UHFFFAOYSA-NZirconiumChemical compound[Zr]QCWXUUIWCKQGHC-UHFFFAOYSA-N0.000description3

- 229910021417amorphous siliconInorganic materials0.000description3

- 239000012298atmosphereSubstances0.000description3

- 229910052790berylliumInorganic materials0.000description3

- ATBAMAFKBVZNFJ-UHFFFAOYSA-Nberyllium atomChemical compound[Be]ATBAMAFKBVZNFJ-UHFFFAOYSA-N0.000description3

- 229910052796boronInorganic materials0.000description3

- 239000000919ceramicSubstances0.000description3

- ZMIGMASIKSOYAM-UHFFFAOYSA-NceriumChemical compound[Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce]ZMIGMASIKSOYAM-UHFFFAOYSA-N0.000description3

- 229910052801chlorineInorganic materials0.000description3

- AJNVQOSZGJRYEI-UHFFFAOYSA-Ndigallium;oxygen(2-)Chemical compound[O-2].[O-2].[O-2].[Ga+3].[Ga+3]AJNVQOSZGJRYEI-UHFFFAOYSA-N0.000description3

- 238000000295emission spectrumMethods0.000description3

- 238000002149energy-dispersive X-ray emission spectroscopyMethods0.000description3

- 239000003822epoxy resinSubstances0.000description3

- 230000005669field effectEffects0.000description3

- 229910001195gallium oxideInorganic materials0.000description3

- 229910052732germaniumInorganic materials0.000description3

- GNPVGFCGXDBREM-UHFFFAOYSA-Ngermanium atomChemical compound[Ge]GNPVGFCGXDBREM-UHFFFAOYSA-N0.000description3

- 229910052735hafniumInorganic materials0.000description3

- VBJZVLUMGGDVMO-UHFFFAOYSA-Nhafnium atomChemical compound[Hf]VBJZVLUMGGDVMO-UHFFFAOYSA-N0.000description3

- 238000010438heat treatmentMethods0.000description3

- 238000009413insulationMethods0.000description3

- 238000003475laminationMethods0.000description3

- 229910052746lanthanumInorganic materials0.000description3

- FZLIPJUXYLNCLC-UHFFFAOYSA-Nlanthanum atomChemical compound[La]FZLIPJUXYLNCLC-UHFFFAOYSA-N0.000description3

- 229910052749magnesiumInorganic materials0.000description3

- 239000011777magnesiumSubstances0.000description3

- 238000005259measurementMethods0.000description3

- QEFYFXOXNSNQGX-UHFFFAOYSA-Nneodymium atomChemical compound[Nd]QEFYFXOXNSNQGX-UHFFFAOYSA-N0.000description3

- 235000006408oxalic acidNutrition0.000description3

- 229910052763palladiumInorganic materials0.000description3

- 239000002245particleSubstances0.000description3

- 229920000647polyepoxidePolymers0.000description3

- 229920001296polysiloxanePolymers0.000description3

- 239000010453quartzSubstances0.000description3

- 239000000126substanceSubstances0.000description3

- 229910052720vanadiumInorganic materials0.000description3

- GPPXJZIENCGNKB-UHFFFAOYSA-NvanadiumChemical compound[V]#[V]GPPXJZIENCGNKB-UHFFFAOYSA-N0.000description3

- 229910052727yttriumInorganic materials0.000description3

- VWQVUPCCIRVNHF-UHFFFAOYSA-Nyttrium atomChemical compound[Y]VWQVUPCCIRVNHF-UHFFFAOYSA-N0.000description3

- 229910052726zirconiumInorganic materials0.000description3

- 229910000881Cu alloyInorganic materials0.000description2

- 229920000089Cyclic olefin copolymerPolymers0.000description2

- YCKRFDGAMUMZLT-UHFFFAOYSA-NFluorine atomChemical compound[F]YCKRFDGAMUMZLT-UHFFFAOYSA-N0.000description2

- 229910000914Mn alloyInorganic materials0.000description2

- CBENFWSGALASAD-UHFFFAOYSA-NOzoneChemical compound[O-][O+]=OCBENFWSGALASAD-UHFFFAOYSA-N0.000description2

- BQCADISMDOOEFD-UHFFFAOYSA-NSilverChemical compound[Ag]BQCADISMDOOEFD-UHFFFAOYSA-N0.000description2

- 241001422033ThestylusSpecies0.000description2

- WGLPBDUCMAPZCE-UHFFFAOYSA-NTrioxochromiumChemical compoundO=[Cr](=O)=OWGLPBDUCMAPZCE-UHFFFAOYSA-N0.000description2

- 238000002441X-ray diffractionMethods0.000description2

- 239000002253acidSubstances0.000description2

- 229910045601alloyInorganic materials0.000description2

- 239000000956alloySubstances0.000description2

- 239000005354aluminosilicate glassSubstances0.000description2

- 239000002585baseSubstances0.000description2

- DQXBYHZEEUGOBF-UHFFFAOYSA-Nbut-3-enoic acid;etheneChemical compoundC=C.OC(=O)CC=CDQXBYHZEEUGOBF-UHFFFAOYSA-N0.000description2

- 239000003638chemical reducing agentSubstances0.000description2

- 229910000423chromium oxideInorganic materials0.000description2

- 239000010941cobaltSubstances0.000description2

- 229910017052cobaltInorganic materials0.000description2

- GUTLYIVDDKVIGB-UHFFFAOYSA-Ncobalt atomChemical compound[Co]GUTLYIVDDKVIGB-UHFFFAOYSA-N0.000description2

- 229920001940conductive polymerPolymers0.000description2

- 238000011161developmentMethods0.000description2

- 239000000428dustSubstances0.000description2

- 230000005674electromagnetic inductionEffects0.000description2

- 239000005038ethylene vinyl acetateSubstances0.000description2

- 230000001747exhibiting effectEffects0.000description2

- 238000000605extractionMethods0.000description2

- 239000011737fluorineSubstances0.000description2

- 229910052731fluorineInorganic materials0.000description2

- PCHJSUWPFVWCPO-UHFFFAOYSA-NgoldChemical compound[Au]PCHJSUWPFVWCPO-UHFFFAOYSA-N0.000description2

- 229910052737goldInorganic materials0.000description2

- 239000010931goldSubstances0.000description2

- 229910002804graphiteInorganic materials0.000description2

- 239000010439graphiteSubstances0.000description2

- 229910000449hafnium oxideInorganic materials0.000description2

- WIHZLLGSGQNAGK-UHFFFAOYSA-Nhafnium(4+);oxygen(2-)Chemical compound[O-2].[O-2].[Hf+4]WIHZLLGSGQNAGK-UHFFFAOYSA-N0.000description2

- 150000002431hydrogenChemical class0.000description2

- 238000003384imaging methodMethods0.000description2

- 229910052809inorganic oxideInorganic materials0.000description2

- 238000005468ion implantationMethods0.000description2

- 150000002500ionsChemical class0.000description2

- 230000001678irradiating effectEffects0.000description2

- 230000033001locomotionEffects0.000description2

- 229910052748manganeseInorganic materials0.000description2

- 239000011159matrix materialSubstances0.000description2

- 150000002739metalsChemical class0.000description2

- 239000011259mixed solutionSubstances0.000description2

- 239000002159nanocrystalSubstances0.000description2

- 238000001579optical reflectometryMethods0.000description2

- SIWVEOZUMHYXCS-UHFFFAOYSA-Noxo(oxoyttriooxy)yttriumChemical compoundO=[Y]O[Y]=OSIWVEOZUMHYXCS-UHFFFAOYSA-N0.000description2

- BPUBBGLMJRNUCC-UHFFFAOYSA-Noxygen(2-);tantalum(5+)Chemical compound[O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5]BPUBBGLMJRNUCC-UHFFFAOYSA-N0.000description2

- RVTZCBVAJQQJTK-UHFFFAOYSA-Noxygen(2-);zirconium(4+)Chemical compound[O-2].[O-2].[Zr+4]RVTZCBVAJQQJTK-UHFFFAOYSA-N0.000description2

- 230000000737periodic effectEffects0.000description2

- 229910052697platinumInorganic materials0.000description2

- 229920001200poly(ethylene-vinyl acetate)Polymers0.000description2

- 229920002037poly(vinyl butyral) polymerPolymers0.000description2

- 229920000139polyethylene terephthalatePolymers0.000description2

- 239000005020polyethylene terephthalateSubstances0.000description2

- 239000009719polyimide resinSubstances0.000description2

- 229920000915polyvinyl chloridePolymers0.000description2

- 239000004800polyvinyl chlorideSubstances0.000description2

- 230000009467reductionEffects0.000description2

- 239000005871repellentSubstances0.000description2

- 239000000523sampleSubstances0.000description2

- 229910052594sapphireInorganic materials0.000description2

- 239000010980sapphireSubstances0.000description2

- MZLGASXMSKOWSE-UHFFFAOYSA-Ntantalum nitrideChemical compound[Ta]#NMZLGASXMSKOWSE-UHFFFAOYSA-N0.000description2

- 229910001936tantalum oxideInorganic materials0.000description2

- VZGDMQKNWNREIO-UHFFFAOYSA-NtetrachloromethaneChemical compoundClC(Cl)(Cl)ClVZGDMQKNWNREIO-UHFFFAOYSA-N0.000description2

- 229910001928zirconium oxideInorganic materials0.000description2

- VXEGSRKPIUDPQT-UHFFFAOYSA-N4-[4-(4-methoxyphenyl)piperazin-1-yl]anilineChemical compoundC1=CC(OC)=CC=C1N1CCN(C=2C=CC(N)=CC=2)CC1VXEGSRKPIUDPQT-UHFFFAOYSA-N0.000description1

- 229910019974CrSiInorganic materials0.000description1

- 239000005264High molar mass liquid crystalSubstances0.000description1

- CPELXLSAUQHCOX-UHFFFAOYSA-NHydrogen bromideChemical compoundBrCPELXLSAUQHCOX-UHFFFAOYSA-N0.000description1

- 229910016006MoSiInorganic materials0.000description1

- GRYLNZFGIOXLOG-UHFFFAOYSA-NNitric acidChemical compoundO[N+]([O-])=OGRYLNZFGIOXLOG-UHFFFAOYSA-N0.000description1

- 239000004677NylonSubstances0.000description1

- 229920012266Poly(ether sulfone) PESPolymers0.000description1

- 239000004983Polymer Dispersed Liquid CrystalSubstances0.000description1

- KWYUFKZDYYNOTN-UHFFFAOYSA-MPotassium hydroxideChemical compound[OH-].[K+]KWYUFKZDYYNOTN-UHFFFAOYSA-M0.000description1

- 229910018503SF6Inorganic materials0.000description1

- 229910003902SiCl 4Inorganic materials0.000description1

- BLRPTPMANUNPDV-UHFFFAOYSA-NSilaneChemical compound[SiH4]BLRPTPMANUNPDV-UHFFFAOYSA-N0.000description1

- 229910000577Silicon-germaniumInorganic materials0.000description1

- 239000004990Smectic liquid crystalSubstances0.000description1

- 239000004974Thermotropic liquid crystalSubstances0.000description1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N[Si].[Ge]Chemical compound[Si].[Ge]LEVVHYCKPQWKOP-UHFFFAOYSA-N0.000description1

- 230000002159abnormal effectEffects0.000description1

- 238000010521absorption reactionMethods0.000description1

- 230000001133accelerationEffects0.000description1

- 239000000654additiveSubstances0.000description1

- 230000000996additive effectEffects0.000description1

- 229910052783alkali metalInorganic materials0.000description1

- 150000001340alkali metalsChemical class0.000description1

- 229910052784alkaline earth metalInorganic materials0.000description1

- 150000001342alkaline earth metalsChemical class0.000description1

- 238000004458analytical methodMethods0.000description1

- 239000004760aramidSubstances0.000description1

- 229920003235aromatic polyamidePolymers0.000description1

- 229910000420cerium oxideInorganic materials0.000description1

- 238000005229chemical vapour depositionMethods0.000description1

- 230000003098cholesteric effectEffects0.000description1

- 238000004040coloringMethods0.000description1

- 230000000295complement effectEffects0.000description1

- 229920001577copolymerPolymers0.000description1

- 238000012937correctionMethods0.000description1

- 230000007547defectEffects0.000description1

- 238000000151depositionMethods0.000description1

- 230000008021depositionEffects0.000description1

- 230000006866deteriorationEffects0.000description1

- 238000007865dilutingMethods0.000description1

- 229910001873dinitrogenInorganic materials0.000description1

- 239000006185dispersionSubstances0.000description1

- 238000005516engineering processMethods0.000description1

- 230000007274generation of a signal involved in cell-cell signalingEffects0.000description1

- YBMRDBCBODYGJE-UHFFFAOYSA-Ngermanium oxideInorganic materialsO=[Ge]=OYBMRDBCBODYGJE-UHFFFAOYSA-N0.000description1

- 230000003760hair shineEffects0.000description1

- 230000020169heat generationEffects0.000description1

- 239000001307heliumSubstances0.000description1

- 229910052734heliumInorganic materials0.000description1

- SWQJXJOGLNCZEY-UHFFFAOYSA-Nhelium atomChemical compound[He]SWQJXJOGLNCZEY-UHFFFAOYSA-N0.000description1

- 239000012943hotmeltSubstances0.000description1

- 150000003949imidesChemical class0.000description1

- 238000007654immersionMethods0.000description1

- 230000001771impaired effectEffects0.000description1

- 239000011261inert gasSubstances0.000description1

- 238000002347injectionMethods0.000description1

- 239000007924injectionSubstances0.000description1

- 239000011229interlayerSubstances0.000description1

- 238000010030laminatingMethods0.000description1

- 239000005355lead glassSubstances0.000description1

- 238000001459lithographyMethods0.000description1

- 239000000395magnesium oxideSubstances0.000description1

- CPLXHLVBOLITMK-UHFFFAOYSA-Nmagnesium oxideInorganic materials[Mg]=OCPLXHLVBOLITMK-UHFFFAOYSA-N0.000description1

- AXZKOIWUVFPNLO-UHFFFAOYSA-Nmagnesium;oxygen(2-)Chemical compound[O-2].[Mg+2]AXZKOIWUVFPNLO-UHFFFAOYSA-N0.000description1

- 238000013507mappingMethods0.000description1

- 238000000691measurement methodMethods0.000description1

- 239000012528membraneSubstances0.000description1

- 239000011156metal matrix compositeSubstances0.000description1

- UNRFQJSWBQGLDR-UHFFFAOYSA-Nmethane trihydrofluorideChemical compoundC.F.F.FUNRFQJSWBQGLDR-UHFFFAOYSA-N0.000description1

- 238000013508migrationMethods0.000description1

- 230000005012migrationEffects0.000description1

- 238000012986modificationMethods0.000description1

- 230000004048modificationEffects0.000description1

- QKCGXXHCELUCKW-UHFFFAOYSA-Nn-[4-[4-(dinaphthalen-2-ylamino)phenyl]phenyl]-n-naphthalen-2-ylnaphthalen-2-amineChemical compoundC1=CC=CC2=CC(N(C=3C=CC(=CC=3)C=3C=CC(=CC=3)N(C=3C=C4C=CC=CC4=CC=3)C=3C=C4C=CC=CC4=CC=3)C3=CC4=CC=CC=C4C=C3)=CC=C21QKCGXXHCELUCKW-UHFFFAOYSA-N0.000description1

- 229910017604nitric acidInorganic materials0.000description1

- 229920001778nylonPolymers0.000description1

- 239000005416organic matterSubstances0.000description1

- 230000001151other effectEffects0.000description1

- 230000003647oxidationEffects0.000description1

- 238000007254oxidation reactionMethods0.000description1

- BMMGVYCKOGBVEV-UHFFFAOYSA-Noxo(oxoceriooxy)ceriumChemical compound[Ce]=O.O=[Ce]=OBMMGVYCKOGBVEV-UHFFFAOYSA-N0.000description1

- PVADDRMAFCOOPC-UHFFFAOYSA-NoxogermaniumChemical compound[Ge]=OPVADDRMAFCOOPC-UHFFFAOYSA-N0.000description1

- 239000005011phenolic resinSubstances0.000description1

- 229920002120photoresistant polymerPolymers0.000description1

- 230000000704physical effectEffects0.000description1

- 239000011295pitchSubstances0.000description1

- 238000009832plasma treatmentMethods0.000description1

- 229920003023plasticPolymers0.000description1

- 239000004033plasticSubstances0.000description1

- 229920006122polyamide resinPolymers0.000description1

- 229920005668polycarbonate resinPolymers0.000description1

- 239000004431polycarbonate resinSubstances0.000description1

- 229910021420polycrystalline siliconInorganic materials0.000description1

- 229920001225polyester resinPolymers0.000description1

- 239000011112polyethylene naphthalateSubstances0.000description1

- 229920005672polyolefin resinPolymers0.000description1

- 229920005591polysiliconPolymers0.000description1

- 229920002635polyurethanePolymers0.000description1

- 239000004814polyurethaneSubstances0.000description1

- 229940072033potashDrugs0.000description1

- BWHMMNNQKKPAPP-UHFFFAOYSA-Lpotassium carbonateSubstances[K+].[K+].[O-]C([O-])=OBWHMMNNQKKPAPP-UHFFFAOYSA-L0.000description1

- 235000015320potassium carbonateNutrition0.000description1

- 238000003672processing methodMethods0.000description1

- 239000000565sealantSubstances0.000description1

- 229910000077silaneInorganic materials0.000description1

- HBMJWWWQQXIZIP-UHFFFAOYSA-Nsilicon carbideChemical compound[Si+]#[C-]HBMJWWWQQXIZIP-UHFFFAOYSA-N0.000description1

- 229910010271silicon carbideInorganic materials0.000description1

- 239000005049silicon tetrachlorideSubstances0.000description1

- 229920002050silicone resinPolymers0.000description1

- 239000002356single layerSubstances0.000description1

- 239000005361soda-lime glassSubstances0.000description1

- 239000007787solidSubstances0.000description1

- 238000004528spin coatingMethods0.000description1

- 239000010935stainless steelSubstances0.000description1

- 229910001220stainless steelInorganic materials0.000description1

- SFZCNBIFKDRMGX-UHFFFAOYSA-Nsulfur hexafluorideChemical compoundFS(F)(F)(F)(F)FSFZCNBIFKDRMGX-UHFFFAOYSA-N0.000description1

- 229960000909sulfur hexafluorideDrugs0.000description1

- TXEYQDLBPFQVAA-UHFFFAOYSA-NtetrafluoromethaneChemical compoundFC(F)(F)FTXEYQDLBPFQVAA-UHFFFAOYSA-N0.000description1

- 229920001187thermosetting polymerPolymers0.000description1

- 239000010409thin filmSubstances0.000description1

- FAQYAMRNWDIXMY-UHFFFAOYSA-NtrichloroboraneChemical compoundClB(Cl)ClFAQYAMRNWDIXMY-UHFFFAOYSA-N0.000description1

- 239000002699waste materialSubstances0.000description1

- 239000002023woodSubstances0.000description1

Images

Classifications

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09F—DISPLAYING; ADVERTISING; SIGNS; LABELS OR NAME-PLATES; SEALS

- G09F9/00—Indicating arrangements for variable information in which the information is built-up on a support by selection or combination of individual elements

- G09F9/30—Indicating arrangements for variable information in which the information is built-up on a support by selection or combination of individual elements in which the desired character or characters are formed by combining individual elements

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05B—ELECTRIC HEATING; ELECTRIC LIGHT SOURCES NOT OTHERWISE PROVIDED FOR; CIRCUIT ARRANGEMENTS FOR ELECTRIC LIGHT SOURCES, IN GENERAL

- H05B33/00—Electroluminescent light sources

- H05B33/10—Apparatus or processes specially adapted to the manufacture of electroluminescent light sources

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05B—ELECTRIC HEATING; ELECTRIC LIGHT SOURCES NOT OTHERWISE PROVIDED FOR; CIRCUIT ARRANGEMENTS FOR ELECTRIC LIGHT SOURCES, IN GENERAL

- H05B33/00—Electroluminescent light sources

- H05B33/12—Light sources with substantially two-dimensional radiating surfaces

- H05B33/14—Light sources with substantially two-dimensional radiating surfaces characterised by the chemical or physical composition or the arrangement of the electroluminescent material, or by the simultaneous addition of the electroluminescent material in or onto the light source

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05B—ELECTRIC HEATING; ELECTRIC LIGHT SOURCES NOT OTHERWISE PROVIDED FOR; CIRCUIT ARRANGEMENTS FOR ELECTRIC LIGHT SOURCES, IN GENERAL

- H05B33/00—Electroluminescent light sources

- H05B33/12—Light sources with substantially two-dimensional radiating surfaces

- H05B33/22—Light sources with substantially two-dimensional radiating surfaces characterised by the chemical or physical composition or the arrangement of auxiliary dielectric or reflective layers

- H05B33/24—Light sources with substantially two-dimensional radiating surfaces characterised by the chemical or physical composition or the arrangement of auxiliary dielectric or reflective layers of metallic reflective layers

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05B—ELECTRIC HEATING; ELECTRIC LIGHT SOURCES NOT OTHERWISE PROVIDED FOR; CIRCUIT ARRANGEMENTS FOR ELECTRIC LIGHT SOURCES, IN GENERAL

- H05B33/00—Electroluminescent light sources

- H05B33/12—Light sources with substantially two-dimensional radiating surfaces

- H05B33/26—Light sources with substantially two-dimensional radiating surfaces characterised by the composition or arrangement of the conductive material used as an electrode

- H05B33/28—Light sources with substantially two-dimensional radiating surfaces characterised by the composition or arrangement of the conductive material used as an electrode of translucent electrodes

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/80—Constructional details

- H10K59/875—Arrangements for extracting light from the devices

- H10K59/876—Arrangements for extracting light from the devices comprising a resonant cavity structure, e.g. Bragg reflector pair

Landscapes

- Engineering & Computer Science (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Manufacturing & Machinery (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Electroluminescent Light Sources (AREA)

Description

Translated fromJapanese本発明の一態様は、表示パネル、情報処理装置または表示パネルの作製方法に関する。One embodiment of the present invention relates to a display panel, an information processing device, or a method for manufacturing a display panel.

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の一態様の技術分野は、物、方法、または、作製方法に関するものである。または、本発明の一態様は、プロセス、マシン、マニュファクチャ、または、組成物(コンポジション・オブ・マター)に関するものである。そのため、より具体的に本明細書で開示する本発明の一態様の技術分野としては、半導体装置、表示装置、発光装置、蓄電装置、記憶装置、それらの駆動方法、または、それらの作製方法、を一例として挙げることができる。Note that one embodiment of the present invention is not limited to the above technical field. A technical field of one embodiment of the invention disclosed in this specification and the like relates to a product, a method, or a manufacturing method. Alternatively, one aspect of the invention relates to a process, machine, manufacture, or composition of matter. Therefore, the technical fields of one embodiment of the present invention disclosed in this specification more specifically include semiconductor devices, display devices, light-emitting devices, power storage devices, memory devices, driving methods thereof, and manufacturing methods thereof; can be mentioned as an example.

ディスプレイ技術の発展に伴って、要求される性能は日々高度化している。あるディスプレイが再現可能な色域を示す規格には、従来から広く指標とされているsRGB規格やNTSC規格などがあるが、最近ではより広い色域をカバーするBT.2020規格が提唱されている。With the development of display technology, the required performance is becoming more sophisticated day by day. Standards that indicate the color gamut that a certain display can reproduce include the sRGB standard and the NTSC standard, which have been widely used in the past, but recently BT. 2020 standards have been proposed.

ほぼ全ての物体色を表現できるBT.2020規格ではあるが、有機化合物の発するブロードな発光スペクトルをそのまま用いるのでは現状実現が難しいため、キャビティ構造等を用いることによって色純度を高めることで、当該規格を実現する試みがなされている。BT. Although it is the 2020 standard, it is currently difficult to achieve it by using the broad emission spectrum emitted by organic compounds as it is, so attempts are being made to realize the standard by increasing the color purity by using a cavity structure.

表示パネルにおいて、より広い色域をカバーする、キャビティ長の異なる領域を設ける構造などが提案されている(例えば、特許文献1参照)。In a display panel, a structure in which regions with different cavity lengths are provided to cover a wider color gamut has been proposed (see, for example, Patent Document 1).

マイクロキャビティ方式を利用する発光素子は、フルカラー化を実現する上で有利である。特に、広い色再現性を達成するためには、最適な発光スペクトルピーク波長と、シャープなスペクトルを得ることが必要である。A light-emitting element using the microcavity method is advantageous in realizing full-color display. In particular, in order to achieve wide color reproducibility, it is necessary to obtain an optimum emission spectrum peak wavelength and a sharp spectrum.

しかしながら、マイクロキャビティ方式を利用するフルカラー化の発光素子の場合において、発光色の異なる画素毎に一対の電極間の距離を調節する必要があるが、画素によっては、複数の波長が存在し、色純度の低下が問題となっている。さらに、一対の電極間の距離を調節する上でのマスク枚数や工程の増加も問題になっている。However, in the case of a full-color light-emitting element using a microcavity method, it is necessary to adjust the distance between a pair of electrodes for each pixel emitting light of different colors. A decrease in purity has become a problem. Furthermore, the increase in the number of masks and processes involved in adjusting the distance between the pair of electrodes is also a problem.

そこで、本発明の一態様では、異なる波長の光を呈する発光素子を複数有するマイクロキャビティ方式を利用した発光装置において、各発光素子から所望の波長の光のみが射出される素子構造とすることにより、色純度が良く、光取り出し効率の良い発光素子を備えた発光装置および照明装置を提供することを目的とする。さらに、工程数およびコストの削減を図ることを目的とする。Therefore, in one aspect of the present invention, in a light-emitting device using a microcavity method having a plurality of light-emitting elements emitting light of different wavelengths, an element structure in which only light of a desired wavelength is emitted from each light-emitting element is provided. An object of the present invention is to provide a light-emitting device and a lighting device having light-emitting elements with high color purity and high light extraction efficiency. A further object is to reduce the number of steps and the cost.

本発明の一態様は、利便性または信頼性に優れた新規な表示パネルを提供することを課題の一とする。または、利便性または信頼性に優れた新規な表示装置を提供することを課題の一とする。または、利便性または信頼性に優れた新規な入出力装置を提供することを課題の一とする。または、利便性または信頼性に優れた新規な情報処理装置を提供することを課題の一とする。または、新規な表示パネル、新規な表示装置、新規な入出力装置、新規な情報処理装置または新規な半導体装置を提供することを課題の一とする。An object of one embodiment of the present invention is to provide a novel display panel that is highly convenient and reliable. Another object is to provide a novel display device that is highly convenient and reliable. Another object is to provide a new input/output device that is highly convenient and reliable. Another object is to provide a new information processing device that is highly convenient or reliable. Another object is to provide a novel display panel, a novel display device, a novel input/output device, a novel information processing device, or a novel semiconductor device.

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。The description of these problems does not preclude the existence of other problems. Note that one embodiment of the present invention does not necessarily solve all of these problems. Problems other than these are self-evident from the descriptions of the specification, drawings, claims, etc., and it is possible to extract problems other than these from the descriptions of the specification, drawings, claims, etc. is.

本発明の一態様の表示パネルは、第1の画素と、第2の画素と、を有する。第1の画素及び第2の画素はそれぞれ、発光層と、第1の導電膜と、第2の導電膜と、第3の導電膜とを有する。第1の導電膜は、半光透過性および半光反射性を備え、第2の導電膜は、光反射性を備える。または、第1の導電膜は光反射性を備え、第2の導電膜は半光透過性および半光反射性を備える。A display panel of one embodiment of the present invention includes a first pixel and a second pixel. Each of the first pixel and the second pixel has a light-emitting layer, a first conductive film, a second conductive film, and a third conductive film. The first conductive film is semi-light transmissive and semi-light reflective, and the second conductive film is light reflective. Alternatively, the first conductive film is light reflective and the second conductive film is semi-light transmissive and semi-light reflective.

第3の導電膜は、光透過性を備え、第1の導電膜は、第2の導電膜との間に、第3の導電膜を挟むように形成され、発光層は、第2の導電膜と、第3の導電膜との間に挟まれるように形成され、第1の画素は、第1の導電膜と第2の導電膜との間に、第1の距離を備え、第2の画素は、第1の導電膜と第2の導電膜との間に、第2の距離を備え、第2の距離は、第1の距離と等しく、第1の画素は、発光極大波長を波長630nm以上670nm以下の波長領域に有するスペクトルを備える光を射出し、第2の画素は、発光極大波長を波長430nm以上460nm以下の波長領域に有するスペクトルを備える光を射出する。The third conductive film has a light-transmitting property, the first conductive film is formed so as to sandwich the third conductive film between the first conductive film and the second conductive film, and the light-emitting layer has the second conductive film. The first pixel is formed sandwiched between the film and the third conductive film, the first pixel includes a first distance between the first conductive film and the second conductive film, and the second pixel has a first distance between the first conductive film and the second conductive film. comprises a second distance between the first conductive film and the second conductive film, the second distance being equal to the first distance, and the first pixel having an emission maximum wavelength of Light having a spectrum in a wavelength region of 630 nm or more and 670 nm or less is emitted, and the second pixel emits light having a spectrum having an emission maximum wavelength in a wavelength region of 430 nm or more and 460 nm or less.

上記構成において、さらに第3の画素を有し、第3の画素は発光層と、第1の導電膜と、第2の導電膜と、第3の導電膜とを有し、第3の画素は、第1の導電膜と第2の導電膜との間に、第3の距離を備え、第3の距離は、第1の距離と異なり、第3の画素は、緑色の光を射出すると好ましい。The above structure further includes a third pixel, the third pixel includes a light-emitting layer, a first conductive film, a second conductive film, and a third conductive film, and the third pixel has a third distance between the first conductive film and the second conductive film, the third distance is different from the first distance, and the third pixel emits green light. preferable.

上記各構成において、さらに第4の導電膜を有し、第4の導電膜は、光透過性を備えると好ましい。また、第1の画素において、第4の導電膜は、発光層と、第3の導電膜との間に挟まれるように配置され、第2の画素において、第4の導電膜は、発光層と、第3の導電膜との間に挟まれるように配置されると好ましい。また、第1の画素において、第3の導電膜は、第1の膜厚を備え、第2の画素において、第3の導電膜は、第2の膜厚を備え、第1の画素において、第4の導電膜は、第3の膜厚を備え、第2の画素において、第4の導電膜は、第4の膜厚を備え、第1の膜厚は第2の膜厚と等しく、第3の膜厚は第4の膜厚と等しいと好ましい。Each of the above structures preferably further includes a fourth conductive film, and the fourth conductive film has a light-transmitting property. In the first pixel, the fourth conductive film is sandwiched between the light-emitting layer and the third conductive film, and in the second pixel, the fourth conductive film is provided between the light-emitting layer and the third conductive film. and the third conductive film. Further, in the first pixel, the third conductive film has a first film thickness, in the second pixel, the third conductive film has a second film thickness, and in the first pixel, the fourth conductive film has a third thickness; in the second pixel, the fourth conductive film has a fourth thickness, the first thickness being equal to the second thickness; The third film thickness is preferably equal to the fourth film thickness.

上記各構成において、第3の導電膜は、第4の導電膜より、一のエッチング雰囲気におけるエッチングレートが小さいと好ましい。または、第3の導電膜は、第4の導電膜より、一の溶液を用いた場合のエッチングレートが小さいと好ましい。In each of the above structures, the third conductive film preferably has a lower etching rate in one etching atmosphere than the fourth conductive film. Alternatively, it is preferable that the etching rate of the third conductive film using one solution is lower than that of the fourth conductive film.

本発明の一態様の情報処理装置は、キーボード、ハードウェアボタン、ポインティングデバイス、タッチセンサ、照度センサ、撮像装置、音声入力装置、視線入力装置、姿勢検出装置、のうち一以上と、上記記載の表示パネルと、を含む。An information processing device of one embodiment of the present invention includes at least one of a keyboard, hardware buttons, a pointing device, a touch sensor, an illuminance sensor, an imaging device, a voice input device, a line-of-sight input device, and an orientation detection device, and the above-described a display panel;

本発明の一態様の表示パネルの作製方法は、第1の導電膜を形成する工程と、第1の導電膜の上方に第2の導電膜を形成する工程と、第2の導電膜の上方に第3の導電膜を形成する工程と、第3の導電膜の上方に、第1の領域と、第1の領域における厚さよりも小さな厚さを有する第2の領域と、を有するマスクを形成する工程と、第1の導電膜と、第2の導電膜と、第3の導電膜と、のマスクと重ならない部分を除去する第1の工程と、第1の工程の後、マスクを後退させることにより第2の領域のマスクを除去する第2の工程と、第2の工程の後、第3の導電膜の第2の領域と重なる部分を除去する第3の工程と、第3の工程の後、マスクを除去する工程と、第2の導電膜、または第3の導電膜の上方に、発光層を形成する工程と、発光層の上に、第4の導電膜を形成する工程と、を含むことを特徴とする。A method for manufacturing a display panel of one embodiment of the present invention includes steps of forming a first conductive film, forming a second conductive film over the first conductive film, and forming a second conductive film over the second conductive film. forming a third conductive film on the third conductive film; and forming a mask having a first region and a second region having a thickness smaller than the thickness of the first region above the third conductive film. a first step of removing portions of the first conductive film, the second conductive film, and the third conductive film that do not overlap with the mask; after the first step, the mask is removed; a second step of removing the mask in the second region by retreating; a third step of removing a portion of the third conductive film overlapping the second region after the second step; After the step of, removing the mask, forming a light-emitting layer over the second conductive film or the third conductive film, and forming a fourth conductive film over the light-emitting layer and a step.

本明細書に添付した図面では、構成要素を機能ごとに分類し、互いに独立したブロックとしてブロック図を示しているが、実際の構成要素は機能ごとに完全に切り分けることが難しく、一つの構成要素が複数の機能に係わることもあり得る。In the drawings attached to this specification, constituent elements are classified according to function and block diagrams are shown as mutually independent blocks. may be involved in multiple functions.

本明細書においてトランジスタが有するソースとドレインは、トランジスタの極性及び各端子に与えられる電位の高低によって、その呼び方が入れ替わる。一般的に、nチャネル型トランジスタでは、低い電位が与えられる端子がソースと呼ばれ、高い電位が与えられる端子がドレインと呼ばれる。また、pチャネル型トランジスタでは、低い電位が与えられる端子がドレインと呼ばれ、高い電位が与えられる端子がソースと呼ばれる。本明細書では、便宜上、ソースとドレインとが固定されているものと仮定して、トランジスタの接続関係を説明する場合があるが、実際には上記電位の関係に従ってソースとドレインの呼び方が入れ替わる。In this specification, the terms "source" and "drain" of a transistor interchange with each other depending on the polarity of the transistor and the level of the potential applied to each terminal. Generally, in an n-channel transistor, a terminal to which a low potential is applied is called a source, and a terminal to which a high potential is applied is called a drain. In a p-channel transistor, a terminal to which a low potential is applied is called a drain, and a terminal to which a high potential is applied is called a source. In this specification, for the sake of convenience, the connection relationship of transistors may be described on the assumption that the source and the drain are fixed. .

本明細書においてトランジスタのソースとは、活性層として機能する半導体膜の一部であるソース領域、或いは上記半導体膜に接続されたソース電極を意味する。同様に、トランジスタのドレインとは、上記半導体膜の一部であるドレイン領域、或いは上記半導体膜に接続されたドレイン電極を意味する。また、ゲートはゲート電極を意味する。In this specification, the source of a transistor means a source region which is part of a semiconductor film that functions as an active layer, or a source electrode connected to the semiconductor film. Similarly, the drain of a transistor means a drain region that is part of the semiconductor film or a drain electrode connected to the semiconductor film. Also, a gate means a gate electrode.

本明細書においてトランジスタが直列に接続されている状態とは、例えば、第1のトランジスタのソースまたはドレインの一方のみが、第2のトランジスタのソースまたはドレインの一方のみに接続されている状態を意味する。また、トランジスタが並列に接続されている状態とは、第1のトランジスタのソースまたはドレインの一方が第2のトランジスタのソースまたはドレインの一方に接続され、第1のトランジスタのソースまたはドレインの他方が第2のトランジスタのソースまたはドレインの他方に接続されている状態を意味する。In this specification, a state in which transistors are connected in series means, for example, a state in which only one of the source and drain of the first transistor is connected to only one of the source and drain of the second transistor. do. In addition, a state in which transistors are connected in parallel means that one of the source and drain of the first transistor is connected to one of the source and drain of the second transistor, and the other of the source and drain of the first transistor is connected to It means the state of being connected to the other of the source and the drain of the second transistor.

本明細書において接続とは、電気的な接続を意味しており、電流、電圧または電位が、供給可能、或いは伝送可能な状態に相当する。従って、接続している状態とは、直接接続している状態を必ずしも指すわけではなく、電流、電圧または電位が、供給可能、或いは伝送可能であるように、配線、抵抗、ダイオード、トランジスタなどの回路素子を介して間接的に接続している状態も、その範疇に含む。In this specification, connection means electrical connection, and corresponds to a state in which current, voltage or potential can be supplied or transmitted. Therefore, the state of being connected does not necessarily refer to the state of being directly connected, but rather the state of wiring, resistors, diodes, transistors, etc., so that current, voltage or potential can be supplied or transmitted. A state of being indirectly connected via a circuit element is also included in this category.

本明細書において回路図上は独立している構成要素どうしが接続されている場合であっても、実際には、例えば配線の一部が電極として機能する場合など、一の導電膜が、複数の構成要素の機能を併せ持っている場合もある。本明細書において接続とは、このような、一の導電膜が、複数の構成要素の機能を併せ持っている場合も、その範疇に含める。In this specification, even when components that are independent on the circuit diagram are connected to each other, in practice, for example, when a part of the wiring functions as an electrode, one conductive film is connected to a plurality of may also have the functions of the constituent elements of In this specification, "connection" includes such a case where one conductive film has the functions of a plurality of constituent elements.

また、本明細書中において、トランジスタの第1の電極または第2の電極の一方がソース電極を、他方がドレイン電極を指す。Also, in this specification, one of the first electrode and the second electrode of the transistor refers to the source electrode, and the other refers to the drain electrode.

本発明の一態様によれば、利便性または信頼性に優れた新規な表示パネルを提供することができる。または、利便性または信頼性に優れた新規な表示装置を提供することができる。または、利便性または信頼性に優れた新規な入出力装置を提供することができる。または、利便性または信頼性に優れた新規な情報処理装置を提供することができる。または、新規な表示パネル、新規な表示装置、新規な入出力装置、新規な情報処理装置または新規な半導体装置を提供することができる。According to one embodiment of the present invention, a novel display panel with excellent convenience and reliability can be provided. Alternatively, a novel display device with excellent convenience or reliability can be provided. Alternatively, it is possible to provide a novel input/output device with excellent convenience or reliability. Alternatively, it is possible to provide a novel information processing apparatus that is superior in convenience or reliability. Alternatively, a new display panel, a new display device, a new input/output device, a new information processing device, or a new semiconductor device can be provided.

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、必ずしも、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。Note that the description of these effects does not preclude the existence of other effects. Note that one embodiment of the present invention does not necessarily have all of these effects. Effects other than these are self-evident from the descriptions of the specification, drawings, claims, etc., and it is possible to extract effects other than these from the descriptions of the specification, drawings, claims, etc. is.

本発明の一態様の表示パネルは、複数の画素を備える。当該複数の画素は、色相が互いに異なる色を表示する自発光型の表示素子を備える。当該複数の画素は、微小光共振器(マイクロキャビティともいう)を備える。A display panel of one embodiment of the present invention includes a plurality of pixels. The plurality of pixels includes self-luminous display elements that display colors with different hues. The plurality of pixels includes a micro optical resonator (also referred to as microcavity).

これにより、色純度が良い発光素子を備えた発光装置および照明装置を提供することができる。さらに、色相が互いに異なる2の画素の、微少共振器構造の作製工程の一部を同一とすることにより、工程数およびコストの削減を図ることができる。Accordingly, it is possible to provide a light-emitting device and a lighting device having a light-emitting element with high color purity. Furthermore, by using the same part of the microcavity structure manufacturing process for two pixels having different hues, the number of processes and the cost can be reduced.

実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。Embodiments will be described in detail with reference to the drawings. However, the present invention is not limited to the following description, and those skilled in the art will easily understand that various changes can be made in form and detail without departing from the spirit and scope of the present invention. Therefore, the present invention should not be construed as being limited to the descriptions of the embodiments shown below. In the configuration of the invention to be described below, the same reference numerals are used in common for the same parts or parts having similar functions in different drawings, and repeated description thereof will be omitted.

(実施の形態1)

本実施の形態では、本発明の一態様の表示パネルの構成について説明する。(Embodiment 1)

In this embodiment, a structure of a display panel of one embodiment of the present invention will be described.

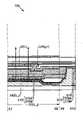

図1(A)および図1(B)はそれぞれ、本発明の一態様の表示パネルの画素と副画素を説明する上面図および断面図である。図1(A)は本発明の一態様の表示パネルの画素の上面図であり、図1(B)は図1(A)の切断線Y3-Y4における断面図である。FIGS. 1A and 1B are a top view and a cross-sectional view, respectively, illustrating a pixel and a subpixel of a display panel of one embodiment of the present invention. FIG. 1A is a top view of a pixel of a display panel of one embodiment of the present invention, and FIG. 1B is a cross-sectional view taken along line Y3-Y4 in FIG. 1A.

図2(A)および図2(B)はそれぞれ、本発明の一態様の表示パネルの画素と副画素を説明する上面図および断面図である。図2(A)は本発明の一態様の表示パネルの画素の上面図であり、図2(B)は図2(A)の切断線Y3-Y4における断面図である。2A and 2B are a top view and a cross-sectional view, respectively, illustrating a pixel and a subpixel of a display panel of one embodiment of the present invention. FIG. 2A is a top view of a pixel of a display panel of one embodiment of the present invention, and FIG. 2B is a cross-sectional view taken along line Y3-Y4 in FIG. 2A.

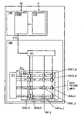

図3は本発明の一態様の表示パネルの構成を説明する図である。図3(A)は表示パネルの上面図であり、図3(B)は図3(A)に示す表示パネルの画素の一部を説明する上面図である。図3(C)は図3(A)に示す表示パネルの断面の構成を説明する模式図である。FIG. 3 illustrates a structure of a display panel of one embodiment of the present invention. FIG. 3A is a top view of a display panel, and FIG. 3B is a top view illustrating part of a pixel of the display panel shown in FIG. 3A. FIG. 3C is a schematic diagram illustrating a cross-sectional structure of the display panel shown in FIG. 3A.

図6は図3(A)に示す表示パネルの画素の構成を説明する上面図である。FIG. 6 is a top view illustrating the structure of a pixel of the display panel shown in FIG. 3A.

図4および図5は表示パネルの構成を説明する断面図である。図4(A)は図3(A)の切断線X1-X2、切断線X3-X4、図6の切断線X5-X6における断面図であり、図4(B)および図4(C)はいずれも図4(A)の一部を説明する図である。4 and 5 are sectional views for explaining the configuration of the display panel. FIG. 4A is a cross-sectional view taken along section lines X1-X2, X3-X4, and X5-X6 in FIG. 3A, and FIGS. All of them are diagrams for explaining a part of FIG. 4(A).

図5は図6の切断線X7-X8、図3(A)の切断線X9-X10における断面図である。5 is a cross-sectional view taken along line X7-X8 in FIG. 6 and line X9-X10 in FIG. 3A.

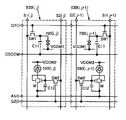

図7は本発明の一態様の表示パネルが備える画素回路の構成を説明する回路図である。FIG. 7 is a circuit diagram illustrating the structure of a pixel circuit included in the display panel of one embodiment of the present invention.

なお、本明細書において、1以上の整数を値にとる変数を符号に用いる場合がある。例えば、1以上の整数の値をとる変数pを含む(p)を、最大p個の構成要素のいずれかを特定する符号の一部に用いる場合がある。また、例えば、1以上の整数の値をとる変数mおよび変数nを含む(m,n)を、最大m×n個の構成要素のいずれかを特定する符号の一部に用いる場合がある。In this specification, a variable whose value is an integer of 1 or more may be used as a code. For example, (p), which includes a variable p that takes an integer value of 1 or more, may be used as part of the code specifying one of the maximum p components. Also, for example, (m, n) including variable m and variable n, which take integer values of 1 or more, may be used as part of the code specifying one of the maximum m×n components.

<表示パネルの構成例1>

本実施の形態で説明する表示パネル700は、複数の画素を備える。当該複数の画素は、色相が互いに異なる色を表示する機能を備える。<Configuration example 1 of display panel>

The

当該複数の画素を用いて、各々その画素では表示できない色相の色を、加法混色により表示することができる。By using the plurality of pixels, colors of hues that cannot be displayed by the pixels can be displayed by additive color mixture.

なお、色相が異なる色を表示することができる複数の画素を混色に用いる場合において、それぞれの画素を副画素と言い換えることができる。また、複数の副画素を一組にして、画素と言い換えることができる。Note that when a plurality of pixels capable of displaying colors with different hues are used for color mixture, each pixel can be called a sub-pixel. Also, a set of sub-pixels can be called a pixel.

例えば、画素702(i,j)、画素702(i,j+1)および画素702(i,j+2)を、いずれも副画素とみなし、これらを一組にして画素703(i,k)と言い換えることができる(図1(A)参照)。For example, pixel 702(i,j), pixel 702(i,j+1), and pixel 702(i,j+2) are all considered sub-pixels and grouped together as pixel 703(i,k). (See FIG. 1(A)).

具体的には、赤色を表示する画素702(i,j)、緑色を表示する画素702(i,j+1)および青色を表示する画素702(i,j+2)を副画素とみなし、一組にして、画素703(i,k)に用いることができる。Specifically, a pixel 702 (i, j) displaying red, a pixel 702 (i, j+1) displaying green, and a pixel 702 (i, j+2) displaying blue are regarded as sub-pixels, and , can be used for pixel 703(i,k).

また、例えば、白色を表示する副画素等を上記の一組に加えて、画素に用いることができる。Further, for example, a sub-pixel or the like that displays white can be added to the above set and used as a pixel.

<表示素子の構成例1>

画素702(i,j)は、表示素子550(i,j)を有する(図1(B)参照)。表示素子550(i,j)は、光を射出する機能を備える。例えば、有機EL素子を表示素子550(i,j)に用いることができる。表示素子550(i,j)は発光層553、電極551(i,j)、電極552を備える。例えば、電極551(i,j)は光透過性を有する材料、電極552は光反射性を有する材料を用いる。画素702(i,j+1)および画素702(i,j+2)についても同様である。発光層553は、発光性の材料を含む層である。<Configuration example 1 of display element>

A pixel 702(i,j) has a display element 550(i,j) (see FIG. 1B). The display element 550(i, j) has a function of emitting light. For example, an organic EL element can be used for the display element 550(i,j). A display element 550 (i, j) includes a light-emitting

また後述の部分で説明するが、画素702(i,j)は赤色の着色膜CF1(R)を備え、画素702(i,j+1)は緑色の着色膜CF1(G)を備え、画素702(i,j+2)は青色の着色膜CF1(B)を備える。As will be described later, the pixel 702(i, j) has a red colored film CF1(R), the pixel 702(i, j+1) has a green colored film CF1(G), and the pixel 702( i, j+2) is provided with a blue colored film CF1(B).

表示素子550(i,j)において、半光透過性・半光反射性を備える導電膜551_0(i,j)と、光透過性を備える導電膜551_1(i,j)とを、電極551(i,j)に用いることができる。表示素子550(i,j+1)、表示素子550(i,j+2)においても同様である。In the display element 550 (i, j), a semi-transmissive/semi-reflective conductive film 551_0 (i, j) and a light-transmitting conductive film 551_1 (i, j) are connected to electrodes 551 (i, j). i, j). The same applies to display element 550 (i, j+1) and display element 550 (i, j+2).

光透過性を備える導電膜551_1(i,j)は、半光透過性・半光反射性を備える導電膜551_0(i,j)および発光層553の間に挟まれる領域を備える。The light-transmitting conductive film 551_1(i, j) includes a region sandwiched between the semi-light-transmitting/semi-reflecting conductive film 551_0(i, j) and the light-emitting

この場合において、発光層553と、光透過性を備える導電膜551_1(i,j)との積層膜を、光透過性を有する膜とみなすことができる。表示素子550(i,j+1)、表示素子550(i,j+2)においても同様である。In this case, a stacked film of the light-emitting

画素702(i,j)、画素702(i,j+1)、画素702(i,j+2)は微少共振器構造を備える。微小光共振器構造とは、光透過性を有し、厚さ方向において所定の光学距離を有する膜を、半光透過性・半光反射性を備える膜と、光反射膜との間に挟む積層構造を指す。光透過性を有する導電膜551_1(i,j)は、光透過率の異なる2種以上の積層構造としても良い。Pixel 702(i,j), pixel 702(i,j+1), and pixel 702(i,j+2) have a microresonator structure. An optical microresonator structure is one in which a film having optical transparency and a predetermined optical distance in the thickness direction is sandwiched between a semi-optical transmissive/semi-reflective film and a light-reflecting film. Refers to a laminated structure. The light-transmitting conductive film 551_1(i, j) may have a layered structure of two or more layers with different light transmittances.

図1(B)には、赤色の光R01及びR02、緑色の光G01及びG02、青色の光B01及びB02が示されている。いずれの光も発光層553から射出される。また、d0、d1が示されている。d0、d1はいずれも、導電膜551_0(i,j)と電極552との間の、導電膜551_0の膜厚方向に沿った距離である。FIG. 1B shows red lights R01 and R02, green lights G01 and G02, and blue lights B01 and B02. Both lights are emitted from the

光R02、光G02、光B02、は半光透過性・半光反射性を備える導電膜551_0(i,j)と、光透過性を備える導電膜551_1(i,j)との界面で反射する。また光R02、光G02、光B02、は発光層553と、光反射性を有する電極552との界面で反射する。Light R02, light G02, and light B02 are reflected at the interface between the conductive film 551_0 (i, j) having semi-light transmissive/semi-light reflective properties and the conductive film 551_1 (i, j) having light transmissive property. . Further, the light R02, the light G02, and the light B02 are reflected at the interface between the light emitting

画素702(i,j)において光R01と光R02とは干渉して強めあう。画素702(i,j+1)において光G01と光G02とは干渉して強めあう。画素702(i,j+2)において光B01と光B02とは干渉して強めあう。At pixel 702(i,j), light R01 and light R02 interfere and strengthen each other. At pixel 702 (i, j+1), light G01 and light G02 interfere and strengthen each other. At pixel 702 (i, j+2), light B01 and light B02 interfere and strengthen each other.

本発明の一態様の表示パネル700において、画素702(i,j)と、画素702(i,j+2)と、は距離d0を有する。また、画素702(i,j)における距離d0と、画素702(i,j+1)における距離d1とは異なる。換言すると、画素702(i,j)における電極552と導電膜551_0(i,j)との距離と、画素702(i,j+2)における電極552と導電膜551_0(i,j+2)との距離とは、概略等しい。また、画素702(i,j)における電極552と導電膜551_0(i,j)との距離と、画素702(i,j+1)における電極552と導電膜551_0(i,j+1)との距離とは、異なる。なお、本明細書等において、2つの距離が概略等しいとは、2つの距離のうちの一方の、他方に対する比が0.8以上1.2以下であることを示す。In the

光透過性を備える導電膜551_1(i,j)の屈折率に波長依存性があり、赤色の光と青色の光とで互いに屈折率が異なるのであれば、画素702(i,j)における距離d0と、画素702(i,j+2)における距離d0とにおいて、光学距離は異なる。表示パネル700において、上記屈折率を考慮して、距離d0を決定することで、有効な微小光共振器構造が形成される。If the refractive index of the conductive film 551_1 (i, j) having optical transparency has wavelength dependence, and red light and blue light have different refractive indices, then the distance in the pixel 702 (i, j) is The optical distance is different between d0 and the distance d0 at pixel 702(i,j+2). In the

なお、半光透過性・半光反射性を備える膜は、可視光の一部を透過する機能および他の一部を反射する機能を備える。具体的には、光が透過する程度に薄い金属膜を半光透過性・半光反射性を備える膜に用いることができる。A semi-transmissive/semi-reflective film has a function of transmitting a part of visible light and a function of reflecting the other part. Specifically, a metal film thin enough to transmit light can be used as a semi-light-transmitting/semi-reflecting film.

これにより、微小光共振器構造を画素702(i,j)、画素702(i,j+1)、画素702(i,j+2)に設けることができる。画素702(i,j)は、赤色の色純度を高め、表示を鮮やかにすることができる。また画素702(i,j+1)は、緑色の色純度を高め、表示を鮮やかにすることができる。また画素702(i,j+2)は、青色の色純度を高め、表示を鮮やかにすることができる。Thereby, a micro optical resonator structure can be provided in pixel 702(i,j), pixel 702(i,j+1), and pixel 702(i,j+2). Pixel 702(i,j) can increase the color purity of red and make the display more vivid. Also, the pixel 702 (i, j+1) can increase the color purity of green and make the display vivid. In addition, the pixel 702 (i, j+2) can increase the color purity of blue to make the display more vivid.

または、所定の波長の光を他の光より効率よく取り出すことができる。または、スペクトルの半値幅が狭い光を取り出すことができる。または、鮮やかな色の光を取り出すことができる。Alternatively, light with a predetermined wavelength can be extracted more efficiently than other light. Alternatively, light with a narrow half width of the spectrum can be extracted. Or you can take out bright colors of light.

また表示パネル700_1のように、導電膜551_1(i,j)に接して導電膜551_2(i,j)を設ける積層構造としてもよい(図2(B)参照)。ここで、導電膜551_1(i,j)と、導電膜551_2(i,j)とは異なる材料であると好ましい。なお、導電膜551_1(i,j)と、導電膜551_2(i,j)は同じ材料としてもよい。導電膜551_1(i,j+2)においても同様である。Alternatively, a stacked structure in which a conductive film 551_2(i, j) is provided in contact with the conductive film 551_1(i, j) may be employed like the display panel 700_1 (see FIG. 2B). Here, it is preferable that the conductive films 551_1(i, j) and the conductive films 551_2(i, j) are made of different materials. Note that the conductive film 551_1(i, j) and the conductive film 551_2(i, j) may be made of the same material. The same applies to the conductive film 551_1(i, j+2).

表示素子550(i,j)において、半光透過性・半光反射性を備える導電膜551_0(i,j)と、光透過性を備える導電膜551_1(i,j)と、光透過性を備える導電膜551_2(i,j)とを、電極551(i,j)に用いることができる。表示素子550(i,j+2)においても同様である。In the display element 550(i, j), a conductive film 551_0(i, j) having semi-transmissive/semi-light reflective properties, a conductive film 551_1(i, j) having light-transmitting properties, and a conductive film 551_1(i, j) having light-transmitting properties The conductive film 551_2(i,j) provided can be used for the electrode 551(i,j). The same applies to display element 550 (i, j+2).

光透過性を備える導電膜551_1(i,j)は、半光透過性・半光反射性を備える導電膜551_0(i,j)および発光層553の間に挟まれる領域を備える。また、光透過性を備える導電膜551_2(i,j)は、光透過性を備える導電膜551_1(i,j)および発光層553の間に挟まれる領域を備える。この場合において、発光層553、光透過性を備える導電膜551_1(i,j)および光透過性を備える導電膜551_2(i,j)の積層膜を光透過性を有する膜とみなすことができる。表示素子550(i,j+2)においても同様である。The light-transmitting conductive film 551_1(i, j) has a region sandwiched between the semi-light-transmitting/semi-reflecting conductive film 551_0(i, j) and the light-emitting

表示素子550(i,j+1)において、半光透過性・半光反射性を備える導電膜551_0(i,j+1)と、光透過性を備える導電膜551_1(i,j+1)とを、電極551(i,j+1)に用いることができる。In the display element 550 (i, j+1), a semi-transmissive/semi-reflective conductive film 551_0 (i, j+1) and a light-transmitting conductive film 551_1 (i, j+1) are connected to the electrode 551 ( i, j+1).

光透過性を備える導電膜551_1(i,j+1)は、半光透過性・半光反射性を備える導電膜551_0(i,j+1)および発光層553の間に挟まれる領域を備える。この場合において、発光層553および光透過性を備える導電膜551_1(i,j+1)の積層膜を光透過性を有する膜とみなすことができる。The light-transmitting conductive film 551_1 (i, j+1) has a region sandwiched between the semi-light-transmitting/semi-light-reflecting conductive film 551_0 (i, j+1) and the light-emitting

実施の形態2で説明するが、電極551(i,j)が、表示パネル700_1のような、積層構造を有する場合、電極551(i,j)の作製工程の簡略化に有効である。As described in

<画素の構成例1>

例えば、白色の光を発する発光層を発光層553に用いることができる(図2(B)参照)。<Pixel configuration example 1>

For example, a light-emitting layer that emits white light can be used for the light-emitting layer 553 (see FIG. 2B).

画素702(i,j)は赤色の着色膜CF1(R)を備え、赤色の光を射出する機能を備える(図2(B)参照)。画素702(i,j+1)は緑色の着色膜CF1(G)を備え、緑色の光を射出する機能を備える。画素702(i,j+2)は青色の着色膜CF1(B)を備え、青色の光を射出する機能を備える。副画素は、互いに絶縁膜528で区切られている。発光層553は、画素702(i,j)において配設される領域、画素702(i,j+1)において配設される領域、画素702(i,j+2)において配設される領域、を有する。A pixel 702(i, j) includes a red colored film CF1(R) and has a function of emitting red light (see FIG. 2B). The pixel 702(i, j+1) has a green colored film CF1(G) and has a function of emitting green light. A pixel 702 (i, j+2) includes a blue colored film CF1 (B) and has a function of emitting blue light. Sub-pixels are separated from each other by an insulating

画素702(i,j)において、発光層553は、例えば188nmの膜厚とすることができる。導電膜551_1(i,j)は、例えば膜厚50nmの、インジウムと錫と珪素とを有する酸化物導電膜を用いることができる。導電膜551_2(i,j)は、例えば膜厚62nmの、インジウムと亜鉛とを有する酸化物導電膜を用いることができる。画素702(i,j+2)においても同様である。In pixel 702(i,j), light-emitting

画素702(i,j+1)において、発光層553は、例えば188nmの膜厚とすることができる。導電膜551_1(i,j+1)は、例えば膜厚50nmの、インジウムと錫と珪素とを有する酸化物導電膜を用いることができる。In pixel 702(i,j+1), the light-emitting

上記膜厚による各副画素の構成により、画素702(i,j)は赤色の色純度を高め、画素702(i,j+1)は緑色の色純度を高め、画素702(i,j+1)は青色の色純度を高め、いずれの表示も鮮やかにすることができる。By configuring each sub-pixel with the above film thickness, the pixel 702(i,j) enhances the color purity of red, the pixel 702(i,j+1) enhances the color purity of green, and the pixel 702(i,j+1) enhances the color purity of blue. The color purity of the display can be increased, and any display can be made vivid.

<表示パネルの構成例2>

本実施の形態で説明する表示パネル700は、画素702(i,j)を有する(図3(A)または図17参照)。<Configuration example 2 of the display panel>

A

<画素の構成例2>

画素702(i,j)は、表示素子550(i,j)を備える(図3(C)参照)。また、画素702(i,j)は、画素回路530(i,j)を備える。<Example 2 of Pixel Configuration>

A pixel 702(i,j) includes a display element 550(i,j) (see FIG. 3C). Pixel 702(i,j) also includes pixel circuit 530(i,j).

画素回路530(i,j)は導電膜を備える。当該導電膜は可視光を透過する領域を備えてもよい。例えば、可視光を透過する導電膜を導電膜512A、導電膜512Bおよび導電膜504に用いることができる(図4(A)参照)。The pixel circuit 530(i,j) comprises a conductive film. The conductive film may have a region that transmits visible light. For example, a conductive film that transmits visible light can be used for the

なお、導電膜512A、導電膜512Bおよび導電膜504は、いずれもトランジスタMの電極の機能を備える。または、導電膜512A、導電膜512Bおよび導電膜504は、いずれも画素回路530(i,j)の配線の機能を備える(図4(A)または図4(B)参照)。Note that the

<表示素子の構成例2>

表示素子550(i,j)は画素回路530(i,j)と電気的に接続される(図3(C)参照)。例えば、表示素子550(i,j)は、接続部522Aにおいて、画素回路530(i,j)と電気的に接続される。具体的には、表示素子550(i,j)の電極551(i,j)は、トランジスタMの導電膜512Aと電気的に接続される。<Configuration Example 2 of Display Element>

The display element 550(i, j) is electrically connected to the pixel circuit 530(i, j) (see FIG. 3C). For example, display element 550(i,j) is electrically connected to pixel circuit 530(i,j) at

表示素子550(i,j)は、基板770に向かって可視光を射出する機能を備える(図3(C)、図4(A)参照)。このとき光L1の射出する経路に、着色膜CF1(R)を設けることができる。表示素子550(i,j+1)、表示素子550(i,j+2)も同様とする。The display element 550(i, j) has a function of emitting visible light toward the substrate 770 (see FIGS. 3C and 4A). At this time, a colored film CF1(R) can be provided on the path through which the light L1 is emitted. The same applies to display element 550 (i, j+1) and display element 550 (i, j+2).

<画素回路の構成例1>

画素回路530(i,j)は、トランジスタMを備え、トランジスタMは、半導体膜508、導電膜512A、導電膜512Bおよびゲート電極として機能する導電膜504を備える。<Configuration Example 1 of Pixel Circuit>

The pixel circuit 530(i,j) includes a transistor M, which includes a

半導体膜508は、導電膜512Aと電気的に接続される領域508A、導電膜512Bと電気的に接続される領域508Bを備える(図4(B)参照)。The

半導体膜508は、領域508Aおよび領域508Bの間にゲート電極として機能する導電膜504と重なる領域508Cを備える。The

画素回路530(i,j)は表示素子550(i,j)を駆動する機能を備える(図7参照)。The pixel circuit 530(i,j) has a function of driving the display element 550(i,j) (see FIG. 7).

スイッチ、トランジスタ、ダイオード、抵抗素子、インダクタまたは容量素子等を画素回路530(i,j)に用いることができる。A switch, a transistor, a diode, a resistive element, an inductor, a capacitive element, or the like can be used for the pixel circuit 530(i,j).

例えば、単数または複数のトランジスタをスイッチに用いることができる。または、並列に接続された複数のトランジスタ、直列に接続された複数のトランジスタ、直列と並列が組み合わされて接続された複数のトランジスタを、一のスイッチに用いることができる。For example, one or more transistors can be used for the switches. Alternatively, a plurality of transistors connected in parallel, a plurality of transistors connected in series, or a plurality of transistors connected in series and in parallel can be used for one switch.

例えば、画素回路530(i,j)は、信号線S2(j)、走査線G2(i)および導電膜ANOと電気的に接続される(図7参照)。なお、導電膜512Bは、接続部522Bにおいて導電膜ANOと電気的に接続される(図4(A)および図7参照)。For example, the pixel circuit 530(i,j) is electrically connected to the signal line S2(j), the scanning line G2(i) and the conductive film ANO (see FIG. 7). Note that the

画素回路530(i,j)は、スイッチSW2、トランジスタMおよび容量素子C21を含む(図7参照)。The pixel circuit 530(i,j) includes a switch SW2, a transistor M and a capacitive element C21 (see FIG. 7).

例えば、走査線G2(i)と電気的に接続されるゲート電極と、信号線S2(j)と電気的に接続される第1の電極と、を有するトランジスタを、スイッチSW2に用いることができる。For example, a transistor having a gate electrode electrically connected to the scan line G2(i) and a first electrode electrically connected to the signal line S2(j) can be used for the switch SW2. .

トランジスタMは、スイッチSW2に用いるトランジスタの第2の電極と電気的に接続されるゲート電極と、導電膜ANOと電気的に接続される第1の電極と、を有する。The transistor M has a gate electrode electrically connected to the second electrode of the transistor used for the switch SW2, and a first electrode electrically connected to the conductive film ANO.

なお、半導体膜をゲート電極との間に挟むように設けられた導電膜を備えるトランジスタを、トランジスタMに用いることができる。例えば、トランジスタMのゲート電極と同じ電位を供給することができる配線と電気的に接続される導電膜を当該導電膜に用いることができる。Note that a transistor including a conductive film in which a semiconductor film is interposed with a gate electrode can be used as the transistor M. For example, a conductive film that is electrically connected to a wiring capable of supplying the same potential as that of the gate electrode of the transistor M can be used as the conductive film.

容量素子C21は、スイッチSW2に用いるトランジスタの第2の電極と電気的に接続される第1の電極と、トランジスタMの第1の電極と電気的に接続される第2の電極と、を有する。The capacitive element C21 has a first electrode electrically connected to the second electrode of the transistor used for the switch SW2 and a second electrode electrically connected to the first electrode of the transistor M. .

また、表示素子550(i,j)の電極551(i,j)をトランジスタMの第2の電極と電気的に接続し、表示素子550(i,j)の電極552を導電膜VCOM2と電気的に接続する。これにより、表示素子550(i,j)を駆動することができる。Further, the electrode 551(i,j) of the display element 550(i,j) is electrically connected to the second electrode of the transistor M, and the

<画素の構成例3>

画素702(i,j)は絶縁膜573を備える(図5参照)。例えば、単数の膜または複数の膜を積層した積層膜を絶縁膜573に用いることができる。具体的には、絶縁膜573Aおよび絶縁膜573Bを積層した積層膜を絶縁膜573に用いることができる。<Example 3 of Pixel Configuration>

The pixel 702(i,j) has an insulating film 573 (see FIG. 5). For example, a single film or a stacked film in which a plurality of films are stacked can be used as the insulating

画素702(i,j)は、絶縁膜518を備える。なお、絶縁膜573は、例えば、表示領域231の外側で絶縁膜518と接する領域を備える。The pixel 702 (i,j) comprises an insulating

表示素子550(i,j)は絶縁膜573および絶縁膜518に挟まれる領域を備える。The display element 550 (i, j) has a region sandwiched between the insulating

表示素子550(i,j)は電極551(i,j)、発光層553、および電極552を備える。発光層553は、電極551(i,j)および電極552の間に挟まれる領域を備える。発光層553は、有機化合物を含む。The display element 550(i,j) comprises an electrode 551(i,j), a

これにより、表示素子への不純物の拡散を抑制することができる。その結果、利便性または信頼性に優れた新規な表示装置を提供することができる。This can suppress the diffusion of impurities into the display element. As a result, it is possible to provide a novel display device with excellent convenience or reliability.

<表示パネルの構成例3>

また、本実施の形態で説明する表示パネル700は、表示領域231を有する(図17参照)。<Configuration example 3 of the display panel>

Further, the

<表示領域の構成例>

表示領域231は、一群の複数の画素702(i,1)乃至画素702(i,n)と、他の一群の複数の画素702(1,j)乃至画素702(m,j)と、走査線G2(i)と、信号線S2(j)と、を有する(図17参照)。また、導電膜VCOM2と、導電膜ANOと、を有する。なお、iは1以上m以下の整数であり、jは1以上n以下の整数であり、mおよびnは1以上の整数である。<Configuration example of display area>

The

一群の複数の画素702(i,1)乃至画素702(i,n)は画素702(i,j)を含み、一群の複数の画素702(i,1)乃至画素702(i,n)は行方向(図中に矢印R1で示す方向)に配設される。The group of pixels 702(i,1) through 702(i,n) includes pixel 702(i,j), and the group of pixels 702(i,1) through 702(i,n) includes They are arranged in the row direction (the direction indicated by arrow R1 in the figure).

他の一群の複数の画素702(1,j)乃至画素702(m,j)は画素702(i,j)を含み、他の一群の複数の画素702(1,j)乃至画素702(m,j)は行方向と交差する列方向(図中に矢印C1で示す方向)に配設される。Another group of pixels 702(1,j) through 702(m,j) includes pixel 702(i,j), and another group of pixels 702(1,j) through 702(m) includes pixel 702(i,j). , j) are arranged in the column direction (the direction indicated by arrow C1 in the figure) intersecting the row direction.

走査線G2(i)は、行方向に配設される一群の複数の画素702(i,1)乃至画素702(i,n)と電気的に接続される。The scanning line G2(i) is electrically connected to a group of pixels 702(i,1) to 702(i,n) arranged in the row direction.

信号線S2(j)は、列方向に配設される他の一群の複数の画素702(1,j)乃至画素702(m,j)と電気的に接続される。The signal line S2(j) is electrically connected to another group of pixels 702(1,j) to 702(m,j) arranged in the column direction.

<表示パネルの構成例4>

また、本実施の形態で説明する表示パネル700は、駆動回路GDまたは駆動回路SDを備えることができる(図3(A)および図17参照)。<Display panel configuration example 4>

Further, the

<駆動回路GD>

駆動回路GDは、制御情報に基づいて選択信号を供給する機能を有する。<Drive circuit GD>

The drive circuit GD has a function of supplying a selection signal based on control information.

一例を挙げれば、制御情報に基づいて、30Hz以上、好ましくは60Hz以上の頻度で一の走査線に選択信号を供給する機能を備える。これにより、動画像をなめらかに表示することができる。For example, it has a function of supplying a selection signal to one scanning line at a frequency of 30 Hz or more, preferably 60 Hz or more, based on control information. As a result, moving images can be displayed smoothly.

例えば、制御情報に基づいて、30Hz未満、好ましくは1Hz未満より好ましくは一分に一回未満の頻度で一の走査線に選択信号を供給する機能を備える。これにより、フリッカーが抑制された状態で静止画像を表示することができる。For example, based on the control information, it provides a selection signal to one scan line at a frequency of less than 30 Hz, preferably less than 1 Hz, and more preferably less than once per minute. As a result, a still image can be displayed with flicker suppressed.

また、表示パネルは、複数の駆動回路を有することができる。例えば、表示パネル700Bは、駆動回路GDAおよび駆動回路GDBを有する(図18参照)。Also, the display panel can have a plurality of drive circuits. For example, the

また、例えば、複数の駆動回路を備える場合、駆動回路GDAが選択信号を供給する頻度と、駆動回路GDBが選択信号を供給する頻度とを、異ならせることができる。具体的には、静止画像を表示する一の領域に選択信号を供給する頻度より高い頻度で、動画像を表示する他の領域に選択信号を供給することができる。これにより、一の領域にフリッカーが抑制された状態で静止画像を表示し、他の領域に滑らかに動画像を表示することができる。Further, for example, when a plurality of driving circuits are provided, the frequency of supplying the selection signal by the driving circuit GDA and the frequency of supplying the selection signal by the driving circuit GDB can be made different. Specifically, the selection signal can be supplied to the other area displaying the moving image at a frequency higher than the frequency of supplying the selection signal to one area displaying the still image. As a result, a still image can be displayed in one area with flicker suppressed, and a moving image can be smoothly displayed in another area.

<駆動回路SD>

駆動回路SDは、駆動回路SD1と、駆動回路SD2と、を有する。駆動回路SD1は、情報V11に基づいて画像信号を供給する機能を有し、駆動回路SD2は、情報V12に基づいて画像信号を供給する機能を有する(図22または図23参照)。<Drive circuit SD>

The drive circuit SD has a drive circuit SD1 and a drive circuit SD2. The drive circuit SD1 has a function of supplying an image signal based on the information V11, and the drive circuit SD2 has a function of supplying an image signal based on the information V12 (see FIG. 22 or 23).

駆動回路SD1または駆動回路SD2は、画像信号を生成する機能と、当該画像信号を一の表示素子と電気的に接続される画素回路に供給する機能を備える。具体的には、極性が反転する信号を生成する機能を備える。これにより、例えば、液晶表示素子を駆動することができる。The drive circuit SD1 or the drive circuit SD2 has a function of generating an image signal and a function of supplying the image signal to a pixel circuit electrically connected to one display element. Specifically, it has a function of generating a signal whose polarity is inverted. Thereby, for example, a liquid crystal display element can be driven.

例えば、シフトレジスタ等のさまざまな順序回路等を駆動回路SDに用いることができる。For example, various sequential circuits such as shift registers can be used for the drive circuit SD.

例えば、駆動回路SD1および駆動回路SD2が集積された集積回路を、駆動回路SDに用いることができる。具体的には、シリコン基板上に形成された集積回路を駆動回路SDに用いることができる。For example, an integrated circuit in which the drive circuit SD1 and the drive circuit SD2 are integrated can be used as the drive circuit SD. Specifically, an integrated circuit formed on a silicon substrate can be used for the drive circuit SD.

例えば、COG(Chip on glass)法またはCOF(Chip on Film)法を用いて、集積回路を端子に実装することができる。具体的には、異方性導電膜を用いて、集積回路を端子に実装することができる。For example, the COG (Chip on glass) method or the COF (Chip on Film) method can be used to mount the integrated circuit on the terminals. Specifically, an anisotropic conductive film can be used to mount an integrated circuit on the terminals.

<表示パネルの構成例5>

また、本実施の形態で説明する表示パネル700は、端子519B、基板570、基板770、接合層505、機能膜770P等を備える(図4(A)または図5参照)。<Display panel configuration example 5>

In addition, the

<端子519B>

端子519Bは、例えば、導電膜511Bを備える。端子519Bは、例えば、信号線S2(j)と電気的に接続することができる。<

The terminal 519B includes, for example, a

<基板570、基板770>

基板770は、基板570と重なる領域を備える。基板770は、基板570との間に表示素子550(i,j)を挟む領域を備える。<

基板770の、表示素子550(i,j)と重なる領域において、例えば、複屈折が抑制された材料を用いることができる。A material with reduced birefringence, for example, can be used in a region of the

<接合層505>

接合層505は、基板770および基板570を貼り合せる機能を備える。<Joining

The

<機能膜770P等>

機能膜770Pは、表示素子550(i,j)と重なる領域を備える。<

The

<構成要素の例>

表示パネル700は、基板570、基板770または接合層505を有する。<Examples of components>

The