JP7048707B2 - Transistors and display devices - Google Patents

Transistors and display devicesDownload PDFInfo

- Publication number

- JP7048707B2 JP7048707B2JP2020194149AJP2020194149AJP7048707B2JP 7048707 B2JP7048707 B2JP 7048707B2JP 2020194149 AJP2020194149 AJP 2020194149AJP 2020194149 AJP2020194149 AJP 2020194149AJP 7048707 B2JP7048707 B2JP 7048707B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- transistor

- insulating film

- metal oxide

- film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 229910044991metal oxideInorganic materials0.000claimsdescription282

- 150000004706metal oxidesChemical class0.000claimsdescription282

- 239000000758substrateSubstances0.000claimsdescription121

- 229910052738indiumInorganic materials0.000claimsdescription36

- 229910052721tungstenInorganic materials0.000claimsdescription22

- 229910052725zincInorganic materials0.000claimsdescription22

- WFKWXMTUELFFGS-UHFFFAOYSA-NtungstenChemical compound[W]WFKWXMTUELFFGS-UHFFFAOYSA-N0.000claimsdescription21

- 239000010937tungstenSubstances0.000claimsdescription21

- 229910052710siliconInorganic materials0.000claimsdescription19

- PXHVJJICTQNCMI-UHFFFAOYSA-NNickelChemical compound[Ni]PXHVJJICTQNCMI-UHFFFAOYSA-N0.000claimsdescription18

- XUIMIQQOPSSXEZ-UHFFFAOYSA-NSiliconChemical compound[Si]XUIMIQQOPSSXEZ-UHFFFAOYSA-N0.000claimsdescription18

- 239000010703siliconSubstances0.000claimsdescription18

- 239000010949copperSubstances0.000claimsdescription16

- 229910052802copperInorganic materials0.000claimsdescription15

- 239000010936titaniumSubstances0.000claimsdescription15

- XEEYBQQBJWHFJM-UHFFFAOYSA-NIronChemical compound[Fe]XEEYBQQBJWHFJM-UHFFFAOYSA-N0.000claimsdescription13

- RYGMFSIKBFXOCR-UHFFFAOYSA-NCopperChemical compound[Cu]RYGMFSIKBFXOCR-UHFFFAOYSA-N0.000claimsdescription12

- 229910052733galliumInorganic materials0.000claimsdescription12

- 229910052719titaniumInorganic materials0.000claimsdescription12

- RTAQQCXQSZGOHL-UHFFFAOYSA-NTitaniumChemical compound[Ti]RTAQQCXQSZGOHL-UHFFFAOYSA-N0.000claimsdescription11

- 229910052782aluminiumInorganic materials0.000claimsdescription10

- 229910052759nickelInorganic materials0.000claimsdescription10

- GYHNNYVSQQEPJS-UHFFFAOYSA-NGalliumChemical compound[Ga]GYHNNYVSQQEPJS-UHFFFAOYSA-N0.000claimsdescription8

- 229910052735hafniumInorganic materials0.000claimsdescription8

- 229910052715tantalumInorganic materials0.000claimsdescription8

- XAGFODPZIPBFFR-UHFFFAOYSA-NaluminiumChemical compound[Al]XAGFODPZIPBFFR-UHFFFAOYSA-N0.000claimsdescription7

- 229910052742ironInorganic materials0.000claimsdescription7

- 229910052750molybdenumInorganic materials0.000claimsdescription7

- ZOKXTWBITQBERF-UHFFFAOYSA-NMolybdenumChemical compound[Mo]ZOKXTWBITQBERF-UHFFFAOYSA-N0.000claimsdescription6

- 239000011733molybdenumSubstances0.000claimsdescription6

- GUVRBAGPIYLISA-UHFFFAOYSA-Ntantalum atomChemical compound[Ta]GUVRBAGPIYLISA-UHFFFAOYSA-N0.000claimsdescription6

- 229910052796boronInorganic materials0.000claimsdescription5

- VBJZVLUMGGDVMO-UHFFFAOYSA-Nhafnium atomChemical compound[Hf]VBJZVLUMGGDVMO-UHFFFAOYSA-N0.000claimsdescription5

- 229910052727yttriumInorganic materials0.000claimsdescription5

- 229910052726zirconiumInorganic materials0.000claimsdescription5

- ZOXJGFHDIHLPTG-UHFFFAOYSA-NBoronChemical compound[B]ZOXJGFHDIHLPTG-UHFFFAOYSA-N0.000claimsdescription4

- 229910052684CeriumInorganic materials0.000claimsdescription4

- 229910052779NeodymiumInorganic materials0.000claimsdescription4

- QCWXUUIWCKQGHC-UHFFFAOYSA-NZirconiumChemical compound[Zr]QCWXUUIWCKQGHC-UHFFFAOYSA-N0.000claimsdescription4

- 229910052790berylliumInorganic materials0.000claimsdescription4

- QEFYFXOXNSNQGX-UHFFFAOYSA-Nneodymium atomChemical compound[Nd]QEFYFXOXNSNQGX-UHFFFAOYSA-N0.000claimsdescription4

- 229910052720vanadiumInorganic materials0.000claimsdescription4

- ATBAMAFKBVZNFJ-UHFFFAOYSA-Nberyllium atomChemical compound[Be]ATBAMAFKBVZNFJ-UHFFFAOYSA-N0.000claimsdescription3

- 229910052732germaniumInorganic materials0.000claimsdescription3

- GNPVGFCGXDBREM-UHFFFAOYSA-Ngermanium atomChemical compound[Ge]GNPVGFCGXDBREM-UHFFFAOYSA-N0.000claimsdescription3

- 229910052746lanthanumInorganic materials0.000claimsdescription3

- FZLIPJUXYLNCLC-UHFFFAOYSA-Nlanthanum atomChemical compound[La]FZLIPJUXYLNCLC-UHFFFAOYSA-N0.000claimsdescription3

- 229910052749magnesiumInorganic materials0.000claimsdescription3

- 239000011777magnesiumSubstances0.000claimsdescription3

- VWQVUPCCIRVNHF-UHFFFAOYSA-Nyttrium atomChemical compound[Y]VWQVUPCCIRVNHF-UHFFFAOYSA-N0.000claimsdescription3

- FYYHWMGAXLPEAU-UHFFFAOYSA-NMagnesiumChemical compound[Mg]FYYHWMGAXLPEAU-UHFFFAOYSA-N0.000claims2

- GWXLDORMOJMVQZ-UHFFFAOYSA-NceriumChemical compound[Ce]GWXLDORMOJMVQZ-UHFFFAOYSA-N0.000claims2

- LEONUFNNVUYDNQ-UHFFFAOYSA-Nvanadium atomChemical compound[V]LEONUFNNVUYDNQ-UHFFFAOYSA-N0.000claims2

- 239000010408filmSubstances0.000description739

- 239000011701zincSubstances0.000description174

- 239000010410layerSubstances0.000description146

- 238000000034methodMethods0.000description101

- 239000004065semiconductorSubstances0.000description77

- 229910052760oxygenInorganic materials0.000description69

- 230000006870functionEffects0.000description68

- 239000001301oxygenSubstances0.000description68

- QVGXLLKOCUKJST-UHFFFAOYSA-Natomic oxygenChemical compound[O]QVGXLLKOCUKJST-UHFFFAOYSA-N0.000description67

- 239000007789gasSubstances0.000description62

- 239000000463materialSubstances0.000description58

- 125000004429atomChemical group0.000description53

- 239000000523sampleSubstances0.000description48

- 230000037230mobilityEffects0.000description44

- 238000002149energy-dispersive X-ray emission spectroscopyMethods0.000description35

- 239000013078crystalSubstances0.000description31

- IJGRMHOSHXDMSA-UHFFFAOYSA-NAtomic nitrogenChemical compoundN#NIJGRMHOSHXDMSA-UHFFFAOYSA-N0.000description30

- 238000013507mappingMethods0.000description30

- APFVFJFRJDLVQX-UHFFFAOYSA-Nindium atomChemical compound[In]APFVFJFRJDLVQX-UHFFFAOYSA-N0.000description29

- 238000004544sputter depositionMethods0.000description29

- 238000003917TEM imageMethods0.000description27

- 239000004973liquid crystal related substanceSubstances0.000description27

- 229910052581Si3N4Inorganic materials0.000description26

- 239000001257hydrogenSubstances0.000description25

- 229910052739hydrogenInorganic materials0.000description25

- HQVNEWCFYHHQES-UHFFFAOYSA-Nsilicon nitrideChemical compoundN12[Si]34N5[Si]62N3[Si]51N64HQVNEWCFYHHQES-UHFFFAOYSA-N0.000description24

- 239000000203mixtureSubstances0.000description21

- 230000005669field effectEffects0.000description20

- 238000004519manufacturing processMethods0.000description20

- VYPSYNLAJGMNEJ-UHFFFAOYSA-Nsilicon dioxideInorganic materialsO=[Si]=OVYPSYNLAJGMNEJ-UHFFFAOYSA-N0.000description20

- UFHFLCQGNIYNRP-UHFFFAOYSA-NHydrogenChemical compound[H][H]UFHFLCQGNIYNRP-UHFFFAOYSA-N0.000description19

- 206010021143HypoxiaDiseases0.000description19

- 229920005989resinPolymers0.000description19

- 239000011347resinSubstances0.000description19

- 229910052814silicon oxideInorganic materials0.000description19

- 230000015572biosynthetic processEffects0.000description18

- 239000012535impuritySubstances0.000description18

- 238000012545processingMethods0.000description18

- 238000004458analytical methodMethods0.000description17

- 229910052751metalInorganic materials0.000description17

- XKRFYHLGVUSROY-UHFFFAOYSA-NArgonChemical compound[Ar]XKRFYHLGVUSROY-UHFFFAOYSA-N0.000description16

- 230000008569processEffects0.000description16

- -1element MChemical compound0.000description15

- 230000001965increasing effectEffects0.000description15

- HCHKCACWOHOZIP-UHFFFAOYSA-NZincChemical compound[Zn]HCHKCACWOHOZIP-UHFFFAOYSA-N0.000description14

- 239000002585baseSubstances0.000description14

- 238000010586diagramMethods0.000description14

- 238000010438heat treatmentMethods0.000description14

- 239000002184metalSubstances0.000description14

- 229910052757nitrogenInorganic materials0.000description14

- XLYOFNOQVPJJNP-UHFFFAOYSA-NwaterSubstancesOXLYOFNOQVPJJNP-UHFFFAOYSA-N0.000description14

- 230000007547defectEffects0.000description12

- 229910007541Zn OInorganic materials0.000description11

- 239000012790adhesive layerSubstances0.000description11

- 239000004020conductorSubstances0.000description11

- 238000010894electron beam technologyMethods0.000description11

- 239000012298atmosphereSubstances0.000description10

- 238000005229chemical vapour depositionMethods0.000description10

- 238000001312dry etchingMethods0.000description10

- VUFNLQXQSDUXKB-DOFZRALJSA-N2-[4-[4-[bis(2-chloroethyl)amino]phenyl]butanoyloxy]ethyl (5z,8z,11z,14z)-icosa-5,8,11,14-tetraenoateChemical groupCCCCC\C=C/C\C=C/C\C=C/C\C=C/CCCC(=O)OCCOC(=O)CCCC1=CC=C(N(CCCl)CCCl)C=C1VUFNLQXQSDUXKB-DOFZRALJSA-N0.000description9

- MYMOFIZGZYHOMD-UHFFFAOYSA-NDioxygenChemical compoundO=OMYMOFIZGZYHOMD-UHFFFAOYSA-N0.000description9

- 229910001882dioxygenInorganic materials0.000description9

- 239000011521glassSubstances0.000description9

- 229910000449hafnium oxideInorganic materials0.000description9

- WIHZLLGSGQNAGK-UHFFFAOYSA-Nhafnium(4+);oxygen(2-)Chemical compound[O-2].[O-2].[Hf+4]WIHZLLGSGQNAGK-UHFFFAOYSA-N0.000description9

- 238000005259measurementMethods0.000description9

- 229910052786argonInorganic materials0.000description8

- 230000008859changeEffects0.000description8

- 230000002093peripheral effectEffects0.000description8

- 229910052718tinInorganic materials0.000description8

- 238000001039wet etchingMethods0.000description8

- ATJFFYVFTNAWJD-UHFFFAOYSA-NTinChemical compound[Sn]ATJFFYVFTNAWJD-UHFFFAOYSA-N0.000description7

- 239000000853adhesiveSubstances0.000description7

- 230000001070adhesive effectEffects0.000description7

- 150000001875compoundsChemical class0.000description7

- 230000000694effectsEffects0.000description7

- 239000012212insulatorSubstances0.000description7

- 229910052784alkaline earth metalInorganic materials0.000description6

- 150000001342alkaline earth metalsChemical class0.000description6

- 239000000969carrierSubstances0.000description6

- 239000002131composite materialSubstances0.000description6

- 230000005685electric field effectEffects0.000description6

- 239000007769metal materialSubstances0.000description6

- 150000004767nitridesChemical class0.000description6

- 125000004430oxygen atomChemical groupO*0.000description6

- 239000002245particleSubstances0.000description6

- BLRPTPMANUNPDV-UHFFFAOYSA-NSilaneChemical compound[SiH4]BLRPTPMANUNPDV-UHFFFAOYSA-N0.000description5

- 229910052783alkali metalInorganic materials0.000description5

- 150000001340alkali metalsChemical class0.000description5

- 229910052799carbonInorganic materials0.000description5

- 238000000576coating methodMethods0.000description5

- 238000009826distributionMethods0.000description5

- 238000002524electron diffraction dataMethods0.000description5

- 238000005530etchingMethods0.000description5

- 150000002431hydrogenChemical class0.000description5

- 238000010191image analysisMethods0.000description5

- 238000009413insulationMethods0.000description5

- 239000013081microcrystalSubstances0.000description5

- 239000002159nanocrystalSubstances0.000description5

- TWNQGVIAIRXVLR-UHFFFAOYSA-Noxo(oxoalumanyloxy)alumaneChemical compoundO=[Al]O[Al]=OTWNQGVIAIRXVLR-UHFFFAOYSA-N0.000description5

- 229910000077silaneInorganic materials0.000description5

- 239000000126substanceSubstances0.000description5

- MZLGASXMSKOWSE-UHFFFAOYSA-Ntantalum nitrideChemical compound[Ta]#NMZLGASXMSKOWSE-UHFFFAOYSA-N0.000description5

- 238000002230thermal chemical vapour depositionMethods0.000description5

- OKTJSMMVPCPJKN-UHFFFAOYSA-NCarbonChemical compound[C]OKTJSMMVPCPJKN-UHFFFAOYSA-N0.000description4

- GQPLMRYTRLFLPF-UHFFFAOYSA-NNitrous OxideChemical compound[O-][N+]#NGQPLMRYTRLFLPF-UHFFFAOYSA-N0.000description4

- XLOMVQKBTHCTTD-UHFFFAOYSA-NZinc monoxideChemical compound[Zn]=OXLOMVQKBTHCTTD-UHFFFAOYSA-N0.000description4

- 229910045601alloyInorganic materials0.000description4

- 239000000956alloySubstances0.000description4

- QVQLCTNNEUAWMS-UHFFFAOYSA-Nbarium oxideChemical compound[Ba]=OQVQLCTNNEUAWMS-UHFFFAOYSA-N0.000description4

- 238000002003electron diffractionMethods0.000description4

- 238000001914filtrationMethods0.000description4

- 239000010931goldSubstances0.000description4

- 230000001590oxidative effectEffects0.000description4

- 238000009832plasma treatmentMethods0.000description4

- 238000004549pulsed laser depositionMethods0.000description4

- 229920006395saturated elastomerPolymers0.000description4

- 238000005477sputtering targetMethods0.000description4

- 239000010409thin filmSubstances0.000description4

- 230000007704transitionEffects0.000description4

- 238000011282treatmentMethods0.000description4

- CBENFWSGALASAD-UHFFFAOYSA-NOzoneChemical compound[O-][O+]=OCBENFWSGALASAD-UHFFFAOYSA-N0.000description3

- 238000002441X-ray diffractionMethods0.000description3

- 230000009471actionEffects0.000description3

- 238000011276addition treatmentMethods0.000description3

- 230000004888barrier functionEffects0.000description3

- 239000011651chromiumSubstances0.000description3

- 230000007423decreaseEffects0.000description3

- AJNVQOSZGJRYEI-UHFFFAOYSA-Ndigallium;oxygen(2-)Chemical compound[O-2].[O-2].[O-2].[Ga+3].[Ga+3]AJNVQOSZGJRYEI-UHFFFAOYSA-N0.000description3

- 230000005684electric fieldEffects0.000description3

- 229910001195gallium oxideInorganic materials0.000description3

- PCHJSUWPFVWCPO-UHFFFAOYSA-NgoldChemical compound[Au]PCHJSUWPFVWCPO-UHFFFAOYSA-N0.000description3

- 229910052737goldInorganic materials0.000description3

- 229910010272inorganic materialInorganic materials0.000description3

- 239000011147inorganic materialSubstances0.000description3

- 230000001678irradiating effectEffects0.000description3

- 239000007788liquidSubstances0.000description3

- 238000001459lithographyMethods0.000description3

- 239000011572manganeseSubstances0.000description3

- 239000002105nanoparticleSubstances0.000description3

- 239000007800oxidant agentSubstances0.000description3

- 229920001721polyimidePolymers0.000description3

- 238000005036potential barrierMethods0.000description3

- 230000001681protective effectEffects0.000description3

- 239000002994raw materialSubstances0.000description3

- 239000003870refractory metalSubstances0.000description3

- 229910052709silverInorganic materials0.000description3

- 238000001179sorption measurementMethods0.000description3

- 238000001228spectrumMethods0.000description3

- 238000003860storageMethods0.000description3

- WZJUBBHODHNQPW-UHFFFAOYSA-N2,4,6,8-tetramethyl-1,3,5,7,2$l^{3},4$l^{3},6$l^{3},8$l^{3}-tetraoxatetrasilocaneChemical compoundC[Si]1O[Si](C)O[Si](C)O[Si](C)O1WZJUBBHODHNQPW-UHFFFAOYSA-N0.000description2

- 239000004925Acrylic resinSubstances0.000description2

- 229920000178Acrylic resinPolymers0.000description2

- VYZAMTAEIAYCRO-UHFFFAOYSA-NChromiumChemical compound[Cr]VYZAMTAEIAYCRO-UHFFFAOYSA-N0.000description2

- 229910019092Mg-OInorganic materials0.000description2

- 229910019395Mg—OInorganic materials0.000description2

- 229910020923Sn-OInorganic materials0.000description2

- BOTDANWDWHJENH-UHFFFAOYSA-NTetraethyl orthosilicateChemical compoundCCO[Si](OCC)(OCC)OCCBOTDANWDWHJENH-UHFFFAOYSA-N0.000description2

- NRTOMJZYCJJWKI-UHFFFAOYSA-NTitanium nitrideChemical compound[Ti]#NNRTOMJZYCJJWKI-UHFFFAOYSA-N0.000description2

- 229910021536ZeoliteInorganic materials0.000description2

- 230000005540biological transmissionEffects0.000description2

- 229910052804chromiumInorganic materials0.000description2

- 239000011248coating agentSubstances0.000description2

- 229910017052cobaltInorganic materials0.000description2

- 239000010941cobaltSubstances0.000description2

- GUTLYIVDDKVIGB-UHFFFAOYSA-Ncobalt atomChemical compound[Co]GUTLYIVDDKVIGB-UHFFFAOYSA-N0.000description2

- 239000000470constituentSubstances0.000description2

- 239000002274desiccantSubstances0.000description2

- 238000003795desorptionMethods0.000description2

- 229910001873dinitrogenInorganic materials0.000description2

- HNPSIPDUKPIQMN-UHFFFAOYSA-Ndioxosilane;oxo(oxoalumanyloxy)alumaneChemical compoundO=[Si]=O.O=[Al]O[Al]=OHNPSIPDUKPIQMN-UHFFFAOYSA-N0.000description2

- 238000007772electroless platingMethods0.000description2

- 238000000921elemental analysisMethods0.000description2

- 238000000724energy-dispersive X-ray spectrumMethods0.000description2

- 239000003822epoxy resinSubstances0.000description2

- 238000000605extractionMethods0.000description2

- 239000001307heliumSubstances0.000description2

- 229910052734heliumInorganic materials0.000description2

- SWQJXJOGLNCZEY-UHFFFAOYSA-Nhelium atomChemical compound[He]SWQJXJOGLNCZEY-UHFFFAOYSA-N0.000description2

- 238000000731high angular annular dark-field scanning transmission electron microscopyMethods0.000description2

- 229910003437indium oxideInorganic materials0.000description2

- 239000011261inert gasSubstances0.000description2

- 150000002500ionsChemical class0.000description2

- MRELNEQAGSRDBK-UHFFFAOYSA-Nlanthanum(3+);oxygen(2-)Chemical compound[O-2].[O-2].[O-2].[La+3].[La+3]MRELNEQAGSRDBK-UHFFFAOYSA-N0.000description2

- 229910052748manganeseInorganic materials0.000description2

- 229960001730nitrous oxideDrugs0.000description2

- HMMGMWAXVFQUOA-UHFFFAOYSA-NoctamethylcyclotetrasiloxaneChemical compoundC[Si]1(C)O[Si](C)(C)O[Si](C)(C)O[Si](C)(C)O1HMMGMWAXVFQUOA-UHFFFAOYSA-N0.000description2

- 230000003287optical effectEffects0.000description2

- 239000011368organic materialSubstances0.000description2

- 230000000704physical effectEffects0.000description2

- 229920002037poly(vinyl butyral) polymerPolymers0.000description2

- 229920000647polyepoxidePolymers0.000description2

- 239000009719polyimide resinSubstances0.000description2

- 229920000915polyvinyl chloridePolymers0.000description2

- 239000004800polyvinyl chlorideSubstances0.000description2

- 239000002243precursorSubstances0.000description2

- 238000002360preparation methodMethods0.000description2

- 238000001004secondary ion mass spectrometryMethods0.000description2

- 239000002356single layerSubstances0.000description2

- 239000002904solventSubstances0.000description2

- 125000006850spacer groupChemical group0.000description2

- CZDYPVPMEAXLPK-UHFFFAOYSA-NtetramethylsilaneChemical compoundC[Si](C)(C)CCZDYPVPMEAXLPK-UHFFFAOYSA-N0.000description2

- 238000007736thin film deposition techniqueMethods0.000description2

- 238000012546transferMethods0.000description2

- 229910052724xenonInorganic materials0.000description2

- FHNFHKCVQCLJFQ-UHFFFAOYSA-Nxenon atomChemical compound[Xe]FHNFHKCVQCLJFQ-UHFFFAOYSA-N0.000description2

- 239000010457zeoliteSubstances0.000description2

- 239000011787zinc oxideSubstances0.000description2

- MGWGWNFMUOTEHG-UHFFFAOYSA-N4-(3,5-dimethylphenyl)-1,3-thiazol-2-amineChemical compoundCC1=CC(C)=CC(C=2N=C(N)SC=2)=C1MGWGWNFMUOTEHG-UHFFFAOYSA-N0.000description1

- QGZKDVFQNNGYKY-UHFFFAOYSA-NAmmoniaChemical compoundNQGZKDVFQNNGYKY-UHFFFAOYSA-N0.000description1

- ZAMOUSCENKQFHK-UHFFFAOYSA-NChlorine atomChemical compound[Cl]ZAMOUSCENKQFHK-UHFFFAOYSA-N0.000description1

- 229910017518Cu ZnInorganic materials0.000description1

- 229910017752Cu-ZnInorganic materials0.000description1

- 229910017943Cu—ZnInorganic materials0.000description1

- 238000004435EPR spectroscopyMethods0.000description1

- PWHULOQIROXLJO-UHFFFAOYSA-NManganeseChemical compound[Mn]PWHULOQIROXLJO-UHFFFAOYSA-N0.000description1

- OAICVXFJPJFONN-UHFFFAOYSA-NPhosphorusChemical compound[P]OAICVXFJPJFONN-UHFFFAOYSA-N0.000description1

- 239000004642PolyimideSubstances0.000description1

- 229910000577Silicon-germaniumInorganic materials0.000description1

- 229910006776Si—ZnInorganic materials0.000description1

- 229910008813Sn—SiInorganic materials0.000description1

- GWEVSGVZZGPLCZ-UHFFFAOYSA-NTitan oxideChemical compoundO=[Ti]=OGWEVSGVZZGPLCZ-UHFFFAOYSA-N0.000description1

- 229910010967Ti—SnInorganic materials0.000description1

- 239000007983Tris bufferSubstances0.000description1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N[Si].[Ge]Chemical compound[Si].[Ge]LEVVHYCKPQWKOP-UHFFFAOYSA-N0.000description1

- 238000010521absorption reactionMethods0.000description1

- 230000001133accelerationEffects0.000description1

- 238000005054agglomerationMethods0.000description1

- 230000002776aggregationEffects0.000description1

- 230000004075alterationEffects0.000description1

- 238000000779annular dark-field scanning transmission electron microscopyMethods0.000description1

- 238000000149argon plasma sinteringMethods0.000description1

- 230000008901benefitEffects0.000description1

- 230000005587bubblingEffects0.000description1

- DQXBYHZEEUGOBF-UHFFFAOYSA-Nbut-3-enoic acid;etheneChemical compoundC=C.OC(=O)CC=CDQXBYHZEEUGOBF-UHFFFAOYSA-N0.000description1

- BRPQOXSCLDDYGP-UHFFFAOYSA-Ncalcium oxideChemical compound[O-2].[Ca+2]BRPQOXSCLDDYGP-UHFFFAOYSA-N0.000description1

- 239000000292calcium oxideSubstances0.000description1

- ODINCKMPIJJUCX-UHFFFAOYSA-Ncalcium oxideInorganic materials[Ca]=OODINCKMPIJJUCX-UHFFFAOYSA-N0.000description1

- 238000004364calculation methodMethods0.000description1

- 239000003990capacitorSubstances0.000description1

- 239000006229carbon blackSubstances0.000description1

- 229910052800carbon group elementInorganic materials0.000description1

- 239000000919ceramicSubstances0.000description1

- ZMIGMASIKSOYAM-UHFFFAOYSA-NceriumChemical group[Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce]ZMIGMASIKSOYAM-UHFFFAOYSA-N0.000description1

- 229910000420cerium oxideInorganic materials0.000description1

- 238000006243chemical reactionMethods0.000description1

- 239000000460chlorineSubstances0.000description1

- 229910052801chlorineInorganic materials0.000description1

- 238000004040coloringMethods0.000description1

- 230000000295complement effectEffects0.000description1

- 238000001816coolingMethods0.000description1

- PMHQVHHXPFUNSP-UHFFFAOYSA-Mcopper(1+);methylsulfanylmethane;bromideChemical compoundBr[Cu].CSCPMHQVHHXPFUNSP-UHFFFAOYSA-M0.000description1

- 238000012937correctionMethods0.000description1

- 238000000151depositionMethods0.000description1

- 238000001514detection methodMethods0.000description1

- 238000009792diffusion processMethods0.000description1

- ZYLGGWPMIDHSEZ-UHFFFAOYSA-Ndimethylazanide;hafnium(4+)Chemical compound[Hf+4].C[N-]C.C[N-]C.C[N-]C.C[N-]CZYLGGWPMIDHSEZ-UHFFFAOYSA-N0.000description1

- PZPGRFITIJYNEJ-UHFFFAOYSA-NdisilaneChemical compound[SiH3][SiH3]PZPGRFITIJYNEJ-UHFFFAOYSA-N0.000description1

- SDIXRDNYIMOKSG-UHFFFAOYSA-Ldisodium methyl arsenateChemical compound[Na+].[Na+].C[As]([O-])([O-])=OSDIXRDNYIMOKSG-UHFFFAOYSA-L0.000description1

- 238000010494dissociation reactionMethods0.000description1

- 230000005593dissociationsEffects0.000description1

- NPEOKFBCHNGLJD-UHFFFAOYSA-Nethyl(methyl)azanide;hafnium(4+)Chemical compound[Hf+4].CC[N-]C.CC[N-]C.CC[N-]C.CC[N-]CNPEOKFBCHNGLJD-UHFFFAOYSA-N0.000description1

- 239000005038ethylene vinyl acetateSubstances0.000description1

- 239000000945fillerSubstances0.000description1

- 125000005843halogen groupChemical group0.000description1

- 230000012447hatchingEffects0.000description1

- 239000003779heat-resistant materialSubstances0.000description1

- FFUAGWLWBBFQJT-UHFFFAOYSA-NhexamethyldisilazaneChemical compoundC[Si](C)(C)N[Si](C)(C)CFFUAGWLWBBFQJT-UHFFFAOYSA-N0.000description1

- 125000004435hydrogen atomChemical group[H]*0.000description1

- 150000003949imidesChemical class0.000description1

- PJXISJQVUVHSOJ-UHFFFAOYSA-Nindium(iii) oxideChemical compound[O-2].[O-2].[O-2].[In+3].[In+3]PJXISJQVUVHSOJ-UHFFFAOYSA-N0.000description1

- 230000001939inductive effectEffects0.000description1

- 230000003993interactionEffects0.000description1

- 239000011229interlayerSubstances0.000description1

- 238000005468ion implantationMethods0.000description1

- 229910052743kryptonInorganic materials0.000description1

- DNNSSWSSYDEUBZ-UHFFFAOYSA-Nkrypton atomChemical compound[Kr]DNNSSWSSYDEUBZ-UHFFFAOYSA-N0.000description1

- 239000000395magnesium oxideSubstances0.000description1

- CPLXHLVBOLITMK-UHFFFAOYSA-Nmagnesium oxideInorganic materials[Mg]=OCPLXHLVBOLITMK-UHFFFAOYSA-N0.000description1

- AXZKOIWUVFPNLO-UHFFFAOYSA-Nmagnesium;oxygen(2-)Chemical compound[O-2].[Mg+2]AXZKOIWUVFPNLO-UHFFFAOYSA-N0.000description1

- 239000011159matrix materialSubstances0.000description1

- 239000012528membraneSubstances0.000description1

- 239000005300metallic glassSubstances0.000description1

- 150000002739metalsChemical class0.000description1

- 238000002156mixingMethods0.000description1

- CUZHTAHNDRTVEF-UHFFFAOYSA-Nn-[bis(dimethylamino)alumanyl]-n-methylmethanamineChemical compound[Al+3].C[N-]C.C[N-]C.C[N-]CCUZHTAHNDRTVEF-UHFFFAOYSA-N0.000description1

- 229910052754neonInorganic materials0.000description1

- GKAOGPIIYCISHV-UHFFFAOYSA-Nneon atomChemical compound[Ne]GKAOGPIIYCISHV-UHFFFAOYSA-N0.000description1

- JCXJVPUVTGWSNB-UHFFFAOYSA-Nnitrogen dioxideInorganic materialsO=[N]=OJCXJVPUVTGWSNB-UHFFFAOYSA-N0.000description1

- 239000001272nitrous oxideSubstances0.000description1

- 235000013842nitrous oxideNutrition0.000description1

- 125000002524organometallic groupChemical group0.000description1

- 230000001151other effectEffects0.000description1

- 230000003647oxidationEffects0.000description1

- 238000007254oxidation reactionMethods0.000description1

- BMMGVYCKOGBVEV-UHFFFAOYSA-Noxo(oxoceriooxy)ceriumChemical compound[Ce]=O.O=[Ce]=OBMMGVYCKOGBVEV-UHFFFAOYSA-N0.000description1

- SIWVEOZUMHYXCS-UHFFFAOYSA-Noxo(oxoyttriooxy)yttriumChemical compoundO=[Y]O[Y]=OSIWVEOZUMHYXCS-UHFFFAOYSA-N0.000description1

- BPUBBGLMJRNUCC-UHFFFAOYSA-Noxygen(2-);tantalum(5+)Chemical compound[O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5]BPUBBGLMJRNUCC-UHFFFAOYSA-N0.000description1

- RVTZCBVAJQQJTK-UHFFFAOYSA-Noxygen(2-);zirconium(4+)Chemical compound[O-2].[O-2].[Zr+4]RVTZCBVAJQQJTK-UHFFFAOYSA-N0.000description1

- 229910052763palladiumInorganic materials0.000description1

- 230000003071parasitic effectEffects0.000description1

- 230000035699permeabilityEffects0.000description1

- 239000005011phenolic resinSubstances0.000description1

- 229910052698phosphorusInorganic materials0.000description1

- 239000011574phosphorusSubstances0.000description1

- 239000000049pigmentSubstances0.000description1

- 238000005268plasma chemical vapour depositionMethods0.000description1

- 238000005498polishingMethods0.000description1

- 229920001200poly(ethylene-vinyl acetate)Polymers0.000description1

- 229910021420polycrystalline siliconInorganic materials0.000description1

- 238000010248power generationMethods0.000description1

- 239000010453quartzSubstances0.000description1

- 150000003254radicalsChemical class0.000description1

- 230000033764rhythmic processEffects0.000description1

- 229910052594sapphireInorganic materials0.000description1

- 239000010980sapphireSubstances0.000description1

- 150000004756silanesChemical class0.000description1

- 239000000741silica gelSubstances0.000description1

- 229910002027silica gelInorganic materials0.000description1

- HBMJWWWQQXIZIP-UHFFFAOYSA-Nsilicon carbideChemical compound[Si+]#[C-]HBMJWWWQQXIZIP-UHFFFAOYSA-N0.000description1

- 229910010271silicon carbideInorganic materials0.000description1

- 239000000377silicon dioxideSubstances0.000description1

- 239000002210silicon-based materialSubstances0.000description1

- 229920002050silicone resinPolymers0.000description1

- 239000004332silverSubstances0.000description1

- 239000006104solid solutionSubstances0.000description1

- 238000006467substitution reactionMethods0.000description1

- 229910001936tantalum oxideInorganic materials0.000description1

- JBQYATWDVHIOAR-UHFFFAOYSA-NtellanylidenegermaniumChemical compound[Te]=[Ge]JBQYATWDVHIOAR-UHFFFAOYSA-N0.000description1

- 229920001187thermosetting polymerPolymers0.000description1

- 230000008719thickeningEffects0.000description1

- 229910001887tin oxideInorganic materials0.000description1

- OGIDPMRJRNCKJF-UHFFFAOYSA-Ntitanium oxideInorganic materials[Ti]=OOGIDPMRJRNCKJF-UHFFFAOYSA-N0.000description1

- LXEXBJXDGVGRAR-UHFFFAOYSA-Ntrichloro(trichlorosilyl)silaneChemical compoundCl[Si](Cl)(Cl)[Si](Cl)(Cl)ClLXEXBJXDGVGRAR-UHFFFAOYSA-N0.000description1

- QQQSFSZALRVCSZ-UHFFFAOYSA-NtriethoxysilaneChemical compoundCCO[SiH](OCC)OCCQQQSFSZALRVCSZ-UHFFFAOYSA-N0.000description1

- MCULRUJILOGHCJ-UHFFFAOYSA-NtriisobutylaluminiumChemical compoundCC(C)C[Al](CC(C)C)CC(C)CMCULRUJILOGHCJ-UHFFFAOYSA-N0.000description1

- JLTRXTDYQLMHGR-UHFFFAOYSA-NtrimethylaluminiumChemical compoundC[Al](C)CJLTRXTDYQLMHGR-UHFFFAOYSA-N0.000description1

- VEDJZFSRVVQBIL-UHFFFAOYSA-NtrisilaneChemical compound[SiH3][SiH2][SiH3]VEDJZFSRVVQBIL-UHFFFAOYSA-N0.000description1

- GPPXJZIENCGNKB-UHFFFAOYSA-NvanadiumChemical group[V]#[V]GPPXJZIENCGNKB-UHFFFAOYSA-N0.000description1

- 238000007740vapor depositionMethods0.000description1

- 238000009834vaporizationMethods0.000description1

- 230000008016vaporizationEffects0.000description1

- 239000011800void materialSubstances0.000description1

- YVTHLONGBIQYBO-UHFFFAOYSA-Nzinc indium(3+) oxygen(2-)Chemical compound[O--].[Zn++].[In+3]YVTHLONGBIQYBO-UHFFFAOYSA-N0.000description1

- 229910001928zirconium oxideInorganic materials0.000description1

Images

Landscapes

- Physical Deposition Of Substances That Are Components Of Semiconductor Devices (AREA)

- Thin Film Transistor (AREA)

- Electroluminescent Light Sources (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Description

Translated fromJapanese本発明は、物、方法、または、製造方法に関する。または、本発明は、プロセス、マシン

、マニュファクチャ、または、組成物(コンポジション・オブ・マター)に関する。特に

、本発明の一態様は、金属酸化物、または当該金属酸化物の製造方法に関する。または、

本発明の一態様は、半導体装置、表示装置、液晶表示装置、発光装置、蓄電装置、記憶装

置、それらの駆動方法、または、それらの製造方法に関する。The present invention relates to a product, a method, or a manufacturing method. Alternatively, the invention relates to a process, machine, manufacture, or composition (composition of matter). In particular, one aspect of the present invention relates to a metal oxide or a method for producing the metal oxide. or,

One aspect of the present invention relates to a semiconductor device, a display device, a liquid crystal display device, a light emitting device, a power storage device, a storage device, a method for driving the same, or a method for manufacturing the same.

なお、本明細書等において、半導体装置とは、半導体特性を利用することで機能しうる装

置全般を指す。トランジスタなどの半導体素子をはじめ、半導体回路、演算装置、記憶装

置は、半導体装置の一態様である。撮像装置、表示装置、液晶表示装置、発光装置、電気

光学装置、発電装置(薄膜太陽電池、有機薄膜太陽電池等を含む)、及び電子機器は、半

導体装置を有している場合がある。In the present specification and the like, the semiconductor device refers to all devices that can function by utilizing the semiconductor characteristics. A semiconductor circuit, an arithmetic unit, and a storage device, including a semiconductor element such as a transistor, are one aspect of a semiconductor device. An image pickup device, a display device, a liquid crystal display device, a light emitting device, an electro-optical device, a power generation device (including a thin film solar cell, an organic thin film solar cell, etc.), and an electronic device may have a semiconductor device.

In-Zn-Ga-O系酸化物、In-Zn-Ga-Mg-O系酸化物、In-Zn-O

系酸化物、In-Sn-O系酸化物、In-O系酸化物、In-Ga-O系酸化物、及び

Sn-In-Zn-O系酸化物のうちのいずれかである非晶質酸化物を有する電界効果型

トランジスタが開示されている(例えば、特許文献1参照)。In-Zn-Ga-O-based oxide, In-Zn-Ga-Mg-O-based oxide, In-Zn-O

Amorphous oxide that is one of a system oxide, an In—Sn—O system oxide, an In—O system oxide, an In—Ga—O system oxide, and a Sn—In—Zn—O system oxide. An electric field effect transistor having an oxide is disclosed (see, for example, Patent Document 1).

また、非特許文献1では、トランジスタの活性層として、In-Zn-O系酸化物と、I

n-Ga-Zn-O系酸化物との2層積層の金属酸化物を有する構造が検討されている。Further, in

A structure having a two-layer laminated metal oxide with an n-Ga-Zn-O-based oxide has been studied.

特許文献1では、In-Zn-Ga-O系酸化物、In-Zn-Ga-Mg-O系酸化物

、In-Zn-O系酸化物、In-Sn-O系酸化物、In-O系酸化物、In-Ga-

O系酸化物、及びSn-In-Zn-O系酸化物のうちのいずれかである非晶質酸化物を

用いて、トランジスタの活性層を形成している。言い換えると、トランジスタの活性層は

、上記酸化物のいずれか1つ非晶質酸化物を有している。トランジスタの活性層が、上記

非晶質酸化物のいずれか1つから構成された場合、トランジスタの電気特性の1つである

オン電流が低くなるといった問題がある。または、トランジスタの活性層が、上記非晶質

酸化物のいずれか1つから構成された場合、トランジスタの信頼性が悪くなるといった問

題がある。In

The active layer of the transistor is formed by using an amorphous oxide which is either an O-based oxide or a Sn-In—Zn—O-based oxide. In other words, the active layer of the transistor has an amorphous oxide of any one of the above oxides. When the active layer of the transistor is composed of any one of the above amorphous oxides, there is a problem that the on-current, which is one of the electrical characteristics of the transistor, becomes low. Alternatively, when the active layer of the transistor is composed of any one of the above amorphous oxides, there is a problem that the reliability of the transistor is deteriorated.

また、非特許文献1では、チャネル保護型のボトムゲート型のトランジスタにおいて、ト

ランジスタの活性層として、In-Zn酸化物と、In-Ga-Zn酸化物との2層積層

とし、チャネルが形成されるIn-Zn酸化物の膜厚を10nmとすることで、高い電界

効果移動度(μ=62cm2V-1s-1)を実現している。一方で、トランジスタ特性

の一つであるS値(Subthreshold Swing、SSともいう)が0.41

V/decadeと大きい。また、トランジスタ特性の一つである、しきい値電圧(Vt

hともいう)が-2.9Vであり、所謂ノーマリーオンのトランジスタ特性である。Further, in Non-Patent

It is as large as V / decade. In addition, the threshold voltage (Vt), which is one of the transistor characteristics, is used.

H) is -2.9V, which is a so-called normally-on transistor characteristic.

上述の問題に鑑み、本発明の一態様は、新規な金属酸化物を提供することを課題の一とす

る。または、本発明の一態様は、半導体装置に良好な電気特性を付与することを課題の一

とする。または、信頼性の高い半導体装置を提供することを課題の一とする。または、新

規な構成の半導体装置を提供することを課題の一とする。または、新規な構成の表示装置

を提供することを課題の一とする。In view of the above problems, one aspect of the present invention is to provide a novel metal oxide. Alternatively, one aspect of the present invention is to impart good electrical characteristics to a semiconductor device. Alternatively, one of the issues is to provide a highly reliable semiconductor device. Alternatively, one of the issues is to provide a semiconductor device having a new configuration. Alternatively, one of the issues is to provide a display device having a new configuration.

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一

態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題

は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図

面、請求項などの記載から、これら以外の課題を抽出することが可能である。The description of these issues does not preclude the existence of other issues. It should be noted that one aspect of the present invention does not need to solve all of these problems. Issues other than these are self-evident from the description of the description, drawings, claims, etc., and it is possible to extract problems other than these from the description of the specification, drawings, claims, etc. Is.

本発明の一態様は、複数のエネルギーバンド幅を有する金属酸化物であって、金属酸化物

は、エネルギーバンドの伝導帯下端が低い領域と、エネルギーバンドの伝導帯下端が高い

領域と、を有し、伝導帯下端が低い領域は、伝導帯下端が高い領域よりもキャリアが多い

金属酸化物である。One aspect of the present invention is a metal oxide having a plurality of energy bandwidths, and the metal oxide has a region where the lower end of the conduction band of the energy band is low and a region where the lower end of the conduction band of the energy band is high. However, the region where the lower end of the conduction band is low is a metal oxide having more carriers than the region where the lower end of the conduction band is high.

本発明の他の一態様は、複数のエネルギーバンド幅を有する金属酸化物であって、金属酸

化物は、エネルギーバンドの伝導帯下端が低い領域と、エネルギーバンドの伝導帯下端が

高い領域と、を有し、伝導帯下端が低い領域は、伝導帯下端が高い領域よりもキャリアが

多く、伝導帯下端の高い領域は、伝導帯下端の低い領域よりも真性である金属酸化物であ

る。Another aspect of the present invention is a metal oxide having a plurality of energy bandwidths, wherein the metal oxide has a region where the lower end of the conduction band of the energy band is low and a region where the lower end of the conduction band of the energy band is high. The region where the lower end of the conduction band is low has more carriers than the region where the lower end of the conduction band is high, and the region where the lower end of the conduction band is high is a metal oxide which is more intrinsic than the region where the lower end of the conduction band is low.

本発明の他の一態様は、複数のエネルギーバンド幅を有する金属酸化物であって、金属酸

化物は、エネルギーバンドの伝導帯下端が低い領域と、エネルギーバンドの伝導帯下端が

高い領域と、を有し、伝導帯下端が低い領域は、伝導帯下端が高い領域よりもキャリアが

多く、伝導帯下端が低い領域と、伝導帯下端が高い領域とは、それぞれ異なる伝導帯を有

する金属酸化物である。Another aspect of the present invention is a metal oxide having a plurality of energy bandwidths, wherein the metal oxide has a region where the lower end of the conduction band of the energy band is low and a region where the lower end of the conduction band of the energy band is high. The region where the lower end of the conduction band is low has more carriers than the region where the lower end of the conduction band is high, and the region where the lower end of the conduction band is low and the region where the lower end of the conduction band is high have different conduction bands. Is.

上記態様において、伝導帯下端が高い領域は、In、Zn、Al、Ga、Si、B、Y、

Ti、Fe、Ni、Ge、Zr、Mo、La、Ce、Nd、Hf、Ta、W、Mg、V、

Be、またはCuの中から選ばれたいずれか一つまたは複数を有すると好ましい。In the above embodiment, the regions where the lower end of the conduction band is high are In, Zn, Al, Ga, Si, B, Y,

Ti, Fe, Ni, Ge, Zr, Mo, La, Ce, Nd, Hf, Ta, W, Mg, V,

It is preferable to have any one or more selected from Be or Cu.

本発明の一態様により、新規な金属酸化物を提供することができる。または、本発明の一

態様により、半導体装置に良好な電気特性を付与することができる。または、信頼性の高

い半導体装置を提供することができる。または、新規な構成の半導体装置を提供すること

ができる。または、新規な構成の表示装置を提供することができる。According to one aspect of the present invention, a novel metal oxide can be provided. Alternatively, according to one aspect of the present invention, good electrical characteristics can be imparted to the semiconductor device. Alternatively, a highly reliable semiconductor device can be provided. Alternatively, it is possible to provide a semiconductor device having a new configuration. Alternatively, a display device having a new configuration can be provided.

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一

態様は、必ずしも、これらの効果の全てを有する必要はない。なお、これら以外の効果は

、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面

、請求項などの記載から、これら以外の効果を抽出することが可能である。The description of these effects does not preclude the existence of other effects. It should be noted that one aspect of the present invention does not necessarily have to have all of these effects. It should be noted that the effects other than these are self-evident from the description of the description, drawings, claims, etc., and it is possible to extract the effects other than these from the description of the description, drawings, claims, etc. Is.

以下、実施の形態について図面を参照しながら説明する。但し、実施の形態は多くの異な

る態様で実施することが可能であり、趣旨及びその範囲から逸脱することなくその形態及

び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は、

以下の実施の形態の記載内容に限定して解釈されるものではない。Hereinafter, embodiments will be described with reference to the drawings. However, it is easily understood by those skilled in the art that the embodiments can be implemented in many different embodiments, and the embodiments and details can be variously changed without departing from the spirit and scope thereof. .. Therefore, the present invention

The interpretation is not limited to the description of the following embodiments.

また、図面において、大きさ、層の厚さ、又は領域は、明瞭化のために誇張されている場

合がある。よって、必ずしもそのスケールに限定されない。なお図面は、理想的な例を模

式的に示したものであり、図面に示す形状又は値などに限定されない。Also, in the drawings, the size, layer thickness, or area may be exaggerated for clarity. Therefore, it is not necessarily limited to that scale. The drawings schematically show ideal examples, and are not limited to the shapes or values shown in the drawings.

また、本明細書にて用いる「第1」、「第2」、「第3」という序数詞は、構成要素の混

同を避けるために付したものであり、数的に限定するものではないことを付記する。In addition, the ordinal numbers "first", "second", and "third" used in the present specification are added to avoid confusion of the components, and are not limited numerically. Addition.

また、本明細書において、「上に」、「下に」などの配置を示す語句は、構成同士の位置

関係を、図面を参照して説明するために、便宜上用いている。また、構成同士の位置関係

は、各構成を描写する方向に応じて適宜変化するものである。従って、明細書で説明した

語句に限定されず、状況に応じて適切に言い換えることができる。Further, in the present specification, words and phrases indicating arrangements such as "above" and "below" are used for convenience in order to explain the positional relationship between the configurations with reference to the drawings. Further, the positional relationship between the configurations changes appropriately depending on the direction in which each configuration is depicted. Therefore, it is not limited to the words and phrases explained in the specification, and can be appropriately paraphrased according to the situation.

また、本明細書等において、トランジスタとは、ゲートと、ドレインと、ソースとを含む

少なくとも三つの端子を有する素子である。そして、ドレイン(ドレイン端子、ドレイン

領域またはドレイン電極)とソース(ソース端子、ソース領域またはソース電極)の間に

チャネル形成領域を有しており、チャネル形成領域を介して、ソースとドレインとの間に

電流を流すことができるものである。なお、本明細書等において、チャネル形成領域とは

、電流が主として流れる領域をいう。Further, in the present specification and the like, a transistor is an element having at least three terminals including a gate, a drain, and a source. Then, a channel forming region is provided between the drain (drain terminal, drain region or drain electrode) and the source (source terminal, source region or source electrode), and between the source and drain via the channel forming region. It is possible to pass an electric current through. In the present specification and the like, the channel forming region means a region in which a current mainly flows.

また、ソースやドレインの機能は、異なる極性のトランジスタを採用する場合や、回路動

作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細

書等においては、ソースやドレインの用語は、入れ替えて用いることができるものとする

。Further, the functions of the source and the drain may be switched when transistors having different polarities are adopted or when the direction of the current changes in the circuit operation. Therefore, in the present specification and the like, the terms source and drain can be used interchangeably.

また、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの

」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの

」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。

例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタ

などのスイッチング素子、抵抗素子、インダクタ、キャパシタ、その他の各種機能を有す

る素子などが含まれる。Further, in the present specification and the like, "electrically connected" includes the case of being connected via "something having some kind of electrical action". Here, the "thing having some kind of electrical action" is not particularly limited as long as it enables the exchange of electric signals between the connection targets.

For example, "things having some kind of electrical action" include electrodes, wirings, switching elements such as transistors, resistance elements, inductors, capacitors, and other elements having various functions.

また、本明細書等において、酸化窒化シリコン膜とは、その組成として、窒素よりも酸素

の含有量が多い膜を指し、窒化酸化シリコン膜とは、その組成として、酸素よりも窒素の

含有量が多い膜を指す。Further, in the present specification and the like, the silicon oxynitride film refers to a film having a higher oxygen content than nitrogen in its composition, and the silicon nitride film has a nitrogen content higher than oxygen in its composition. Refers to a membrane with a lot of oxygen.

また、本明細書等において、図面を用いて発明の構成を説明するにあたり、同じものを指

す符号は異なる図面間でも共通して用いる場合がある。Further, in the present specification and the like, when explaining the structure of the invention by using the drawings, the reference numerals indicating the same may be commonly used between different drawings.

また、本明細書等において、「平行」とは、二つの直線が-10°以上10°以下の角度

で配置されている状態をいう。したがって、-5°以上5°以下の場合も含まれる。また

、「略平行」とは、二つの直線が-30°以上30°以下の角度で配置されている状態を

いう。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されてい

る状態をいう。したがって、85°以上95°以下の場合も含まれる。また、「略垂直」

とは、二つの直線が60°以上120°以下の角度で配置されている状態をいう。Further, in the present specification and the like, "parallel" means a state in which two straight lines are arranged at an angle of −10 ° or more and 10 ° or less. Therefore, the case of −5 ° or more and 5 ° or less is also included. Further, "substantially parallel" means a state in which two straight lines are arranged at an angle of -30 ° or more and 30 ° or less. Further, "vertical" means a state in which two straight lines are arranged at an angle of 80 ° or more and 100 ° or less. Therefore, the case of 85 ° or more and 95 ° or less is also included. Also, "almost vertical"

Refers to a state in which two straight lines are arranged at an angle of 60 ° or more and 120 ° or less.

また、本明細書等において、「膜」という用語と、「層」という用語とは、場合によって

は、互いに入れ替えることが可能である。例えば、「導電層」という用語を、「導電膜」

という用語に変更することが可能な場合がある。または、例えば、「絶縁膜」という用語

を、「絶縁層」という用語に変更することが可能な場合がある。Further, in the present specification and the like, the term "film" and the term "layer" can be interchanged with each other in some cases. For example, the term "conductive layer" is referred to as "conductive layer".

It may be possible to change to the term. Alternatively, for example, it may be possible to change the term "insulating film" to the term "insulating layer".

なお、「半導体」と表記した場合でも、例えば、導電性が十分低い場合は「絶縁体」とし

ての特性を有する場合がある。また、「半導体」と「絶縁体」は境界が曖昧であり、厳密

に区別できない場合がある。したがって、本明細書に記載の「半導体」は、「絶縁体」と

言い換えることができる場合がある。同様に、本明細書に記載の「絶縁体」は、「半導体

」と言い換えることができる場合がある。Even when the term "semiconductor" is used, for example, if the conductivity is sufficiently low, it may have characteristics as an "insulator". In addition, the boundary between "semiconductor" and "insulator" is ambiguous, and it may not be possible to make a strict distinction. Therefore, the "semiconductor" described in the present specification may be paraphrased as an "insulator". Similarly, the "insulator" described herein may be paraphrased as a "semiconductor."

なお、本明細書等において、ノーマリーオンとは、電源による電位の印加がない(0V)

ときにオン状態であることをいう。例えば、ノーマリーオンの特性とは、トランジスタの

ゲートに与える電圧が0Vの際に、しきい値電圧がマイナスとなる電気特性をさす場合が

ある。In the present specification and the like, normally-on means that no potential is applied by the power source (0V).

Sometimes it means that it is on. For example, the normally-on characteristic may refer to an electrical characteristic in which the threshold voltage becomes negative when the voltage applied to the gate of the transistor is 0V.

なお、本明細書等について、In:Ga:Zn=4:2:3またはその近傍とは、原子数

の総和に対して、Inが4の場合、Gaが1以上3以下(1≦Ga≦3)であり、Znが

2以上4以下(2≦Zn≦4)とする。また、In:Ga:Zn=5:1:6またはその

近傍とは、原子数の総和に対して、Inが5の場合、Gaが0.1より大きく2以下(0

.1<Ga≦2)であり、Znが5以上7以下(5≦Zn≦7)とする。また、In:G

a:Zn=1:1:1またはその近傍とは、原子数の総和に対して、Inが1の場合、G

aが0.1より大きく2以下(0.1<Ga≦2)であり、Znが0.1より大きく2以

下(0.1<Zn≦2)とする。In the present specification and the like, In: Ga: Zn = 4: 2: 3 or its vicinity means that when In is 4, Ga is 1 or more and 3 or less (1 ≦ Ga ≦) with respect to the total number of atoms. 3), and Zn is 2 or more and 4 or less (2 ≦ Zn ≦ 4). Further, In: Ga: Zn = 5: 1: 6 or its vicinity means that when In is 5, Ga is larger than 0.1 and 2 or less (0) with respect to the total number of atoms.

.. 1 <Ga ≦ 2), and Zn is 5 or more and 7 or less (5 ≦ Zn ≦ 7). In addition, In: G

a: Zn = 1: 1: 1 or its vicinity means G when In is 1 with respect to the total number of atoms.

It is assumed that a is greater than 0.1 and 2 or less (0.1 <Ga ≦ 2), and Zn is greater than 0.1 and 2 or less (0.1 <Zn ≦ 2).

(実施の形態1)

本実施の形態では、本発明の一態様である金属酸化物について説明する。(Embodiment 1)

In this embodiment, a metal oxide which is one aspect of the present invention will be described.

本発明の一態様の金属酸化物は、少なくともインジウムを含むことが好ましい。特にイン

ジウムおよび亜鉛を含むことが好ましい。また、それらに加えて、元素M(元素Mは、ガ

リウム、アルミニウム、シリコン、ホウ素、イットリウム、銅、バナジウム、ベリリウム

、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウ

ム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムなどから選ば

れた一種、または複数種)が含まれていてもよい。The metal oxide of one aspect of the present invention preferably contains at least indium. In particular, it preferably contains indium and zinc. In addition to them, element M (element M is gallium, aluminum, silicon, boron, yttrium, copper, vanadium, beryllium, titanium, iron, nickel, germanium, zirconium, molybdenum, lanthanum, cerium, neodymium, hafnium, It may contain one or more selected from tantalum, tungsten, gallium and the like.

また、本発明の一態様の金属酸化物は、窒素を有すると好ましい。具体的には、本発明の

一態様の金属酸化物において、SIMSにより得られる窒素濃度が、1×1016ato

ms/cm3以上、好ましくは1×1017atoms/cm3以上2×1022ato

ms/cm3以下とすればよい。なお、金属酸化物に窒素を添加すると、バンドギャップ

が狭くなり、導電性が向上する傾向がある。従って、本明細書等において、本発明の一態

様である金属酸化物は、窒素などが添加された金属酸化物も含むものとする。また、窒素

を有する金属酸化物を金属酸窒化物(Metal Oxynitride)と呼称しても

よい。Moreover, it is preferable that the metal oxide of one aspect of the present invention has nitrogen. Specifically, in the metal oxide of one aspect of the present invention, the nitrogen concentration obtained by SIMS is 1 × 1016 ato.

ms / cm3 or more, preferably 1 × 1017 atoms / cm3 or more 2 × 1022 atto

It may be ms / cm3 or less. When nitrogen is added to the metal oxide, the band gap tends to be narrowed and the conductivity tends to be improved. Therefore, in the present specification and the like, the metal oxide according to one aspect of the present invention also includes the metal oxide to which nitrogen or the like is added. Further, a metal oxide having nitrogen may be referred to as a metal oxynitride.

ここで、金属酸化物が、インジウム、元素M及び亜鉛を有する場合を考える。なお、金属

酸化物が有するインジウム、元素M、及び亜鉛の原子数比のそれぞれの項を[In]、[

M]、および[Zn]とする。Here, consider the case where the metal oxide has indium, the element M, and zinc. The terms of the atomic number ratios of indium, element M, and zinc of the metal oxide are [In] and [

Let it be M] and [Zn].

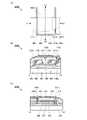

<金属酸化物の構成>

本発明におけるCAC(Cloud-Aligned composite)構成を有す

る金属酸化物の概念図を図1に示す。なお、本明細書において、本発明の一態様である金

属酸化物が、半導体の機能を有する場合、CAC(Cloud-Alignedcomp

osite)-OS(OxideSemiconductor)と定義する。<Composition of metal oxide>

FIG. 1 shows a conceptual diagram of a metal oxide having a CAC (Cloud-Aligned compete) configuration in the present invention. In the present specification, when the metal oxide according to one aspect of the present invention has a semiconductor function, CAC (Cloud-Indexedcomp) is used.

It is defined as (osite) -OS (OxideSemiconductor).

CAC-OSとは、例えば、図1に示すように、金属酸化物を構成する元素が偏在するこ

とで、各元素を主成分とする領域001、および領域002を形成し、各領域が、混合し

、モザイク状に形成される。つまり、金属酸化物を構成する元素が、0.5nm以上10

nm以下、好ましくは、1nm以上2nm以下、またはその近傍のサイズで偏在した材料

の一構成である。なお、以下では、金属酸化物において、一つあるいはそれ以上の金属元

素が偏在し、該金属元素を有する領域が、0.5nm以上10nm以下、好ましくは、1

nm以上2nm以下、またはその近傍のサイズで混合した状態をモザイク状、またはパッ

チ状ともいう。With CAC-OS, for example, as shown in FIG. 1, the elements constituting the metal oxide are unevenly distributed to form a

It is a composition of a material unevenly distributed in a size of nm or less, preferably 1 nm or more and 2 nm or less, or in the vicinity thereof. In the following, in the metal oxide, one or more metal elements are unevenly distributed, and the region having the metal element is 0.5 nm or more and 10 nm or less, preferably 1.

A state in which the mixture is in a size of nm or more and 2 nm or less or in the vicinity thereof is also referred to as a mosaic shape or a patch shape.

例えば、CAC構成を有するIn-M-Zn酸化物とは、インジウム酸化物(以下、In

OX1(X1は0よりも大きい実数)とする。)、またはインジウム亜鉛酸化物(以下、

InX2ZnY2OZ2(X2、Y2、およびZ2は0よりも大きい実数)とする。)と

、元素Mを含む酸化物などと、に材料が分離することでモザイク状となり、モザイク状の

InOX1、またはInX2ZnY2OZ2が、膜中に分布した構成(以下、クラウド状

ともいう。)である。For example, the In—M—Zn oxide having a CAC configuration is an indium oxide (hereinafter, In).

Let it be OX1 (X1 is a real number larger than 0). ), Or indium zinc oxide (hereinafter,

InX2 ZnY2 OZ2 (X2, Y2, and Z2 are real numbers larger than 0). ) And an oxide containing the element M, etc., to form a mosaic, and the mosaic-like InOX1 or InX2 ZnY2OZ2 is distributed in the film (hereinafter, also referred to as cloud-like). It is said.).

別言すると、本発明の一態様の金属酸化物は、In酸化物、In-M酸化物、M酸化物、

MーZn酸化物、In-Zn酸化物、及びIn-M-Zn酸化物の中から選ばれた、少な

くとも2以上の複数の酸化物または複数の材料を有する。In other words, the metal oxide of one aspect of the present invention includes In oxide, In-M oxide, M oxide, and the like.

It has at least two or more oxides or materials selected from M-Zn oxides, In-Zn oxides, and In-M-Zn oxides.

代表的には、本発明の一態様の金属酸化物は、In酸化物、In-Zn酸化物、In-A

l-Zn酸化物、In-Ga-Zn酸化物、In-Y-Zn酸化物、In-Cu-Zn酸

化物、In-V-Zn酸化物、In-Be-Zn酸化物、In-B-Zn酸化物、In-

Si-Zn酸化物、In-Ti-Zn酸化物、In-Fe-Zn酸化物、In-Ni-Z

n酸化物、In-Ge-Zn酸化物、In-Zr-Zn酸化物、In-Mo-Zn酸化物

、In-La-Zn酸化物、In-Ce-Zn酸化物、In-Nd-Zn酸化物、In-

Hf-Zn酸化物、In-Ta-Zn酸化物、In-W-Zn酸化物、及びIn-Mg-

Zn酸化物の中から選ばれた、少なくとも2以上を有する。すなわち、本発明の一態様の

金属酸化物を、複数の材料または複数の成分を有する複合金属酸化物ともいえる。Typically, the metal oxide of one aspect of the present invention is In oxide, In—Zn oxide, In—A.

l-Zn oxide, In-Ga-Zn oxide, In-Y-Zn oxide, In-Cu-Zn oxide, In-V-Zn oxide, In-Be-Zn oxide, In-B- Zn oxide, In-

Si-Zn oxide, In-Ti-Zn oxide, In-Fe-Zn oxide, In-Ni-Z

n-oxide, In-Ge-Zn oxide, In-Zr-Zn oxide, In-Mo-Zn oxide, In-La-Zn oxide, In-Ce-Zn oxide, In-Nd-Zn oxidation Thing, In-

Hf-Zn Oxide, In-Ta-Zn Oxide, In-W-Zn Oxide, and In-Mg-

It has at least 2 or more selected from Zn oxides. That is, the metal oxide of one aspect of the present invention can be said to be a composite metal oxide having a plurality of materials or a plurality of components.

ここで、図1に示す概念が、CAC構成を有するIn-M-Zn酸化物であると仮定する

。その場合、領域001が元素Mを含む酸化物を主成分とする領域、また、領域002が

InX2ZnY2OZ2、またはInOX1を主成分とする領域であるといえる。このと

き、元素Mを含む酸化物が主成分である領域と、InX2ZnY2OZ2、またはInO

X1が主成分である領域と、少なくともZnを有する領域とは、周辺部が不明瞭である(

ボケている)ため、それぞれ明確な境界が観察できない場合がある。Here, it is assumed that the concept shown in FIG. 1 is an In—M—Zn oxide having a CAC configuration. In that case, it can be said that the

The peripheral portion of the region containingX1 as the main component and the region containing at least Zn is unclear (

Because it is out of focus), it may not be possible to observe clear boundaries.

つまり、CAC構成を有するIn-M-Zn酸化物は、元素Mを含む酸化物が主成分であ

る領域と、InX2ZnY2OZ2、またはInOX1が主成分である領域とが、混合し

ている金属酸化物である。従って、金属酸化物を複合金属酸化物と記載する場合がある。

なお、本明細書において、例えば、領域002の元素Mに対するInの原子数比が、領域

001の元素Mに対するInの原子数比よりも大きいことを、領域002は、領域001

と比較して、Inの濃度が高いとする。That is, in the In—M—Zn oxide having a CAC configuration, a region containing an oxide containing an element M as a main component and a region containing InX2 ZnY2 OZ2 or In OX1 as a main component are mixed. It is a metal oxide. Therefore, the metal oxide may be referred to as a composite metal oxide.

In the present specification, for example, the

It is assumed that the concentration of In is higher than that of.

なお、CAC構成を有する金属酸化物とは、組成の異なる二種類以上の膜の積層構造は含

まないものとする。例えば、Inを主成分とする膜と、元素Mを含む酸化物を主成分とす

る膜との2層からなる構造は、含まない。The metal oxide having a CAC structure does not include a laminated structure of two or more types of films having different compositions. For example, it does not include a structure consisting of two layers, a film containing In as a main component and a film containing an oxide containing an element M as a main component.

また、CAC構成において、結晶構造は副次的な要素である。従って、CAC構成を有す

るIn-M-Zn酸化物において、領域001、および領域002における結晶構造は、

特に限定されない。また、領域001、および領域002は、それぞれ、異なる結晶構造

を有していてもよい。Also, in the CAC configuration, the crystal structure is a secondary element. Therefore, in the In—M—Zn oxide having a CAC configuration, the crystal structure in the

Not particularly limited. Further, the

例えば、CAC構成を有するIn-M-Zn酸化物において、非単結晶構造を有する酸化

物半導体であることが好ましい。非単結晶構造として、例えば、CAAC-OS、多結晶

酸化物半導体、nc-OS(nanocrystallineoxidesemicon

ductor)、擬似非晶質酸化物半導体(a-likeOS:amorphous-l

ikeoxidesemiconductor)および非晶質酸化物半導体などがある。For example, in the In—M—Zn oxide having a CAC structure, an oxide semiconductor having a non-single crystal structure is preferable. As a non-single crystal structure, for example, CAAC-OS, polycrystalline oxide semiconductor, nc-OS (nanocrystallineoxidesemicon)

ductor), pseudo-amorphous oxide semiconductor (a-likeOS: amorphous-l)

There are ikeoxidesemiconductor) and amorphous oxide semiconductors.

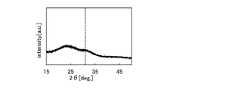

なお、CAAC-OSは、CAAC構造を有する。CAAC構造とは、c軸配向性を有し

、かつa-b面方向において複数のナノ結晶が連結し、歪みを有した結晶構造の酸化物半

導体である。なお、歪みとは、複数のナノ結晶が連結する領域において、格子配列の揃っ

た領域と、別の格子配列の揃った領域と、の間で格子配列の向きが変化している箇所を指

す。The CAAC-OS has a CAAC structure. The CAAC structure is an oxide semiconductor having a c-axis orientation and a crystal structure in which a plurality of nanocrystals are connected in the ab plane direction and has strain. The strain refers to a region where the orientation of the lattice arrangement changes between a region in which the lattice arrangement is aligned and a region in which another lattice arrangement is aligned in the region where a plurality of nanocrystals are connected.

ナノ結晶は、六角形を基本とするが、正六角形状とは限らず、非正六角形状である場合が

ある。また、歪みにおいて、五角形、および七角形などの格子配列を有する場合がある。

従って、CAAC-OSにおいて、歪み近傍においても、明確な結晶粒界(グレインバウ

ンダリーともいう)を確認することはできない。即ち、格子配列の歪みによって、結晶粒

界の形成が抑制されていることがわかる。これは、CAAC-OSが、a-b面方向にお

いて、酸素原子の配列が稠密でないことや、金属元素が置換することで原子間の結合距離

が変化することなどによって、歪みを許容することができるためと考えられる。Although nanocrystals are basically hexagonal, they are not limited to regular hexagonal shapes and may have non-regular hexagonal shapes. In addition, in distortion, it may have a lattice arrangement such as a pentagon and a heptagon.

Therefore, in CAAC-OS, a clear grain boundary (also referred to as grain boundary) cannot be confirmed even in the vicinity of strain. That is, it can be seen that the formation of grain boundaries is suppressed by the distortion of the lattice arrangement. This is because CAAC-OS allows distortion due to the fact that the arrangement of oxygen atoms is not dense in the ab plane direction and that the bond distance between atoms changes due to the substitution of metal elements. It is thought that it can be done.

nc-OSは、微小な領域(例えば、1nm以上10nm以下の領域、特に1nm以上3

nm以下の領域)において原子配列に周期性を有する。また、nc-OSは、異なるナノ

結晶間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。した

がって、nc-OSは、分析方法によっては、a-likeOSや非晶質酸化物半導体と

区別が付かない場合がある。The nc-OS is a minute region (for example, a region of 1 nm or more and 10 nm or less, particularly a region of 1 nm or more and 3).

The atomic arrangement has periodicity in the region below nm). In addition, nc-OS has no regularity in crystal orientation between different nanocrystals. Therefore, no orientation is observed in the entire film. Therefore, nc-OS may be indistinguishable from a-like OS and amorphous oxide semiconductors depending on the analysis method.

a-likeOSは、nc-OSと非晶質酸化物半導体との間の構造を有する酸化物半導

体である。a-likeOSは、鬆または低密度領域を有する。即ち、a-likeOS

は、nc-OSおよびCAAC-OSと比べて、不安定な構造である。The a-likeOS is an oxide semiconductor having a structure between nc-OS and an amorphous oxide semiconductor. The a-likeOS has a void or low density region. That is, a-likeOS

Has an unstable structure as compared with nc-OS and CAAC-OS.

例えば、CAC-OSは、CAAC構造を有することが好ましい。CAAC構造は、領域

001、または領域002を含む範囲で形成される場合がある。つまり、CAC-OSに

おいて、CAAC-OSとなる領域は、数nmから数十nmの範囲で形成される。For example, the CAC-OS preferably has a CAAC structure. The CAAC structure may be formed in a

CAAC-OSは結晶性の高い酸化物半導体である。一方、CAAC-OSは、明確な結

晶粒界を確認することはできないため、結晶粒界に起因する電子移動度の低下が起こりに

くいといえる。従って、CAAC-OSを有することで、金属酸化物としての物理的性質

が安定するため、熱に強く、信頼性が高い金属酸化物を提供することができる。CAAC-OS is a highly crystalline oxide semiconductor. On the other hand, in CAAC-OS, since a clear crystal grain boundary cannot be confirmed, it can be said that the decrease in electron mobility due to the crystal grain boundary is unlikely to occur. Therefore, by having CAAC-OS, the physical properties of the metal oxide are stabilized, so that it is possible to provide a metal oxide that is resistant to heat and has high reliability.

具体的には、In-Ga-Zn酸化物におけるCAC-OS(なお、CAC-OSの中で

もIn-Ga-Zn酸化物を、特にCAC-IGZOと呼称してもよい。)について説明

する。In-Ga-Zn酸化物におけるCAC-OSは、InOX1、またはInX2Z

nY2OZ2と、インジウムガリウム亜鉛酸化物(以下、InaGabZncOd(a、

b、c、およびd0よりも大きい実数)とする。)などと、に材料が分離することでモザ

イク状となり、モザイク状のInOX1、またはInX2ZnY2OZ2がクラウド状で

ある金属酸化物である。Specifically, CAC-OS in In-Ga-Zn oxide (Note that In-Ga-Zn oxide may be particularly referred to as CAC-IGZO among CAC-OS) will be described. CAC-OS in In-Ga-Zn oxide is InOX1 or InX2 Z.

nY2 OZ2 and indium gallium zinc oxide (hereinafter referred to as Ina Gab ZncOd (a,

b, c, and a real number larger than d0). ) And the like, and the material is separated to form a mosaic, and the mosaic-like InOX1 or InX2 ZnY2 OZ2 is a cloud-like metal oxide.

つまり、In-Ga-Zn酸化物におけるCAC-OSは、InaGabZncOdが主

成分である領域と、InX2ZnY2OZ2、またはInOX1が主成分である領域とが

、混合している構成を有する複合金属酸化物である。また、InaGabZncOdが主

成分である領域と、InX2ZnY2OZ2、またはInOX1が主成分である領域とは

、周辺部が不明瞭である(ボケている)ため、明確な境界が観察できない場合がある。That is, in the CAC-OS in the In-Ga-Zn oxide, the region in which Ina Gab ZncOd is the main component and the region in which InX2 ZnY2 OZ2 or In OX1 is the main component are formed. It is a composite metal oxide having a mixed composition. Further, the peripheral portion of the region where Ina Gab ZncOd is the main component and the region where InX2 ZnY2 OZ2 or InOX1 is the main component is unclear (blurred). , Clear boundaries may not be observable.

例えば、図1に示す概念図において、領域001がInaGabZncOdを主成分とす

る領域に相当し、領域002がInX2ZnY2OZ2、またはInOX1を主成分とす

る領域に相当する。なお、InaGabZncOdを主成分とする領域、及びInX2Z

nY2OZ2、またはInOX1を主成分とする領域を、それぞれナノ粒子と呼称しても

よい。当該ナノ粒子は、粒子の径が0.5nm以上10nm以下、代表的には1nm以上

2nm以下である。また、上記ナノ粒子は、周辺部が不明瞭である(ボケている)ため、

明確な境界が観察できない場合がある。For example, in the conceptual diagram shown in FIG. 1, the

The regions containing nY2 OZ2 or InOX1 as main components may be referred to as nanoparticles. The nanoparticles have a particle diameter of 0.5 nm or more and 10 nm or less, typically 1 nm or more and 2 nm or less. In addition, since the peripheral part of the nanoparticles is unclear (blurred),

Clear boundaries may not be observable.

なお、領域001、および領域002のサイズは、エネルギー分散型X線分光法(EDX

:EnergyDispersiveX-rayspectroscopy)を用いて取

得したEDXマッピングで評価することができる。例えば、領域001は、断面写真のE

DXマッピングにおいて、領域001の径が、0.5nm以上10nm以下、または1n

m以上2nm以下で観察される場合がある。また、領域の中心部から周辺部にかけて、主

成分である元素の密度は、徐々に小さくなる。例えば、EDXマッピングでカウントでき

る元素の個数(以下、存在量ともいう)が、中心部から周辺部に向けて傾斜すると、断面

写真のEDXマッピングにおいて、領域の周辺部が不明瞭な(ボケた)状態で観察される

。例えば、InaGabZncOdが主成分である領域において、Ga原子は、中心部か

ら周辺部にかけて徐々に減少し、代わりに、In原子、およびZn原子が増加することで

、InX2ZnY2OZ2が主成分である領域へと段階的に変化する。従って、EDXマ

ッピングにおいて、InaGabZncOdが主成分である領域の周辺部は不明瞭な(ボ

ケた)状態で観察される。The sizes of

: EnergyDispersiveX-rayspectropy) can be evaluated by EDX mapping acquired. For example, the

In DX mapping, the diameter of

It may be observed at m or more and 2 nm or less. Further, the density of the element as the main component gradually decreases from the central portion to the peripheral portion of the region. For example, when the number of elements that can be counted by EDX mapping (hereinafter, also referred to as abundance) is inclined from the central part toward the peripheral part, the peripheral part of the region is unclear (blurred) in the EDX mapping of the cross-sectional photograph. Observed in the state. For example, in the region where Ina Gab ZncOd is the main component, the Ga atom gradually decreases from the central part to the peripheral part, and instead, the In atom and the Zn atom increase, so that InX2 It gradually changes to the region where ZnY2 OZ2 is the main component. Therefore, in the EDX mapping, the peripheral portion of the region in which Ina Gab ZncOd is the main component is observed in an unclear (blurred) state.

なお、CAC構成を有するIn-Ga-Zn酸化物における結晶構造は、特に限定されな

い。また、領域001、および領域002は、それぞれ、異なる結晶構造を有していても

よい。The crystal structure of the In—Ga—Zn oxide having a CAC structure is not particularly limited. Further, the

ここで、In-Ga-Zn-O系の金属酸化物をIGZOと示す場合があるが、IGZO

は通称であり、In、Ga、Zn、およびOによる1つの化合物をいう場合がある。In

-Ga-Zn-O系の金属酸化物の一例としては、結晶性の化合物が挙げられる。結晶性

の化合物は、単結晶構造、多結晶構造、またはCAAC(c-axisalignedc

rystalline)構造を有する。なお、CAAC構造とは、複数のIGZOのナノ

結晶がc軸配向を有し、かつa-b面においては配向せずに連結した層状の結晶構造であ

る。Here, the In—Ga—Zn—O-based metal oxide may be referred to as IGZO, but IGZO

Is a common name and may refer to one compound of In, Ga, Zn, and O. In

An example of a -Ga—Zn—O based metal oxide is a crystalline compound. Crystalline compounds can be single crystal, polycrystalline, or CAAC (c-axisalignedc).

It has a rystalline) structure. The CAAC structure is a layered crystal structure in which a plurality of IGZO nanocrystals have a c-axis orientation and are connected without being oriented on the ab plane.

例えば、CAC構成を有するIn-Ga-Zn酸化物は、非単結晶構造を有する酸化物半

導体であることが好ましい。特に、CAC構成を有するIn-Ga-Zn酸化物は、CA

AC-IGZOを有することが好ましい。また、CAAC-IGZOとなる範囲には、領

域001を有することが好ましい。CAAC-IGZOを有することで、金属酸化物とし

ての物理的性質が安定するため、熱に強く、信頼性が高いIn-Ga-Zn酸化物を提供

することができる。For example, the In—Ga—Zn oxide having a CAC structure is preferably an oxide semiconductor having a non-single crystal structure. In particular, the In-Ga-Zn oxide having a CAC configuration is CA.

It is preferable to have AC-IGZO. Further, it is preferable to have

なお、In-Ga-Zn酸化物におけるCAC-OSにおける結晶性は、電子線回折で評

価することができる。例えば、電子線回折パターン像において、リング状に輝度の高い領

域、およびリング状に輝度の高い領域内に、複数のスポットが観察される場合がある。The crystallinity of In-Ga-Zn oxide in CAC-OS can be evaluated by electron diffraction. For example, in the electron diffraction pattern image, a plurality of spots may be observed in a ring-shaped high-luminance region and a ring-shaped high-luminance region.

ここで、InX2ZnY2OZ2、またはInOX1が主成分である領域は、InaGa

bZncOdなどが主成分である領域と比較して、導電性が高い領域である。つまり、I

nX2ZnY2OZ2、またはInOX1が主成分である領域を、キャリアが流れること

により、酸化物半導体としての導電性が発現する。従って、InX2ZnY2OZ2、ま

たはInOX1が主成分である領域が、酸化物半導体中にクラウド状に分布することで、

高い電界効果移動度(μ)が実現できる。なお、InX2ZnY2OZ2、またはInO

X1が主成分である領域は、導電体の性質に近い、半導体の領域ともいえる。Here, the region in which InX2 ZnY2 OZ2 or InOX1 is the main component is Ina Ga.

b This is a region having high conductivity as compared with the region in which ZncOd or the like is the main component. That is, I

When a carrier flows through a region containing nX2 ZnY2 OZ2 or InOX1 as a main component, conductivity as an oxide semiconductor is exhibited. Therefore, the region containing InX2 ZnY2 OZ2 or InOX1 as the main component is distributed in the oxide semiconductor in a cloud shape.

High field effect mobility (μ) can be realized. InX2 ZnY2 OZ2 or InO

The region in whichX1 is the main component can be said to be a semiconductor region that is close to the properties of a conductor.

一方、InaGabZncOdなどが主成分である領域は、InX2ZnY2OZ2、ま

たはInOX1が主成分である領域と比較して、導電性が低い領域である。つまり、In

aGabZncOdなどが主成分である領域が、金属酸化物中に分布することで、リーク

電流を抑制し、良好なスイッチング動作を実現できる。なお、InaGabZncOdな

どが主成分である領域は、絶縁体の性質に近い、半導体の領域ともいえる。On the other hand, the region in which Ina Gab ZncOd or the like is the main component is a region having lower conductivity than the region in which InX2 ZnY2 OZ2 or InOX1 is the main component. In other words, In

Since the region containinga Gab ZncOd or the like as a main component is distributed in the metal oxide, leakage current can be suppressed and good switching operation can be realized. It should be noted that the region in which Ina Gab ZncOd or the like is the main component can be said to be a semiconductor region close to the properties of an insulator.

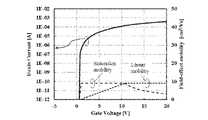

従って、In-Ga-Zn酸化物におけるCAC-OSを半導体素子に用いた場合、In

aGabZncOdなどに起因する性質と、InX2ZnY2OZ2、またはInOX1

に起因する性質とが、相補的に作用することにより、高いオン電流(Ion)、高い電界

効果移動度(μ)、および、低いオフ電流(Ioff)を実現することができる。Therefore, when CAC-OS in In-Ga-Zn oxide is used for the semiconductor element, In

Properties caused bya Gab ZncOd , etc., and InX2 ZnY2 OZ2 , or In OX1

By complementing the properties caused by the above, high on-current (Ion ), high field-effect mobility (μ), and low off-current (Ioff ) can be realized.

また、In-Ga-Zn酸化物におけるCAC-OSを用いた半導体素子は、信頼性が高

い。従って、In-Ga-Zn酸化物におけるCAC-OSは、ディスプレイをはじめと

するさまざまな半導体装置に最適である。Further, the semiconductor device using CAC-OS in In—Ga—Zn oxide has high reliability. Therefore, CAC-OS in In-Ga-Zn oxide is most suitable for various semiconductor devices such as displays.

<金属酸化物を有するトランジスタ>

続いて、上記金属酸化物を半導体としてトランジスタに用いる場合について説明する。<Transistor with metal oxide>

Subsequently, a case where the metal oxide is used as a semiconductor in a transistor will be described.

なお、上記金属酸化物を半導体としてトランジスタに用いることで、電界効果移動度が高

く、かつ、スイッチング特性が高いトランジスタを実現することができる。また、信頼性

の高いトランジスタを実現することができる。By using the metal oxide as a semiconductor in a transistor, it is possible to realize a transistor having high field effect mobility and high switching characteristics. In addition, a highly reliable transistor can be realized.

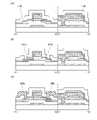

図2(A)は、上記金属酸化物をチャネル形成領域に用いたトランジスタの模式図である

。図2(A)において、トランジスタは、ソースと、ドレインと、第1のゲートと、第2

のゲートと、第1のゲート絶縁部と、第2のゲート絶縁部と、チャネル部と、を有する。

トランジスタは、ゲートに印加する電位によって、チャネル部の抵抗を制御することがで

きる。即ち、第1のゲート、または第2のゲートに印加する電位によって、ソースとドレ

インとの間の導通(トランジスタがオン状態)・非導通(トランジスタがオフ状態)を制

御することができる。FIG. 2A is a schematic diagram of a transistor using the metal oxide in the channel forming region. In FIG. 2A, the transistor has a source, a drain, a first gate, and a second.

It has a gate, a first gate insulating portion, a second gate insulating portion, and a channel portion.

The transistor can control the resistance of the channel portion by the potential applied to the gate. That is, conduction (transistor is on) and non-conduction (transistor is off) between the source and the drain can be controlled by the potential applied to the first gate or the second gate.

ここで、チャネル部は、第1のバンドギャップを有する領域001と、第2のバンドギャ

ップを有する領域002と、がクラウド状であるCAC-OSを有している。なお、第1

のバンドギャップは、第2のバンドギャップよりも大きいものとする。Here, the channel portion has a CAC-OS in which a

The bandgap of is larger than the second bandgap.

例えば、チャネル部のCAC-OSとして、CAC構成を有するIn-Ga-Zn酸化物

を用いる場合について説明する。CAC構成を有するIn-Ga-Zn酸化物は、領域0

01として、領域002よりもGaの濃度が高いInaGabZncOdを主成分とする

領域と、領域002として、領域001よりもInの濃度が高いInX2ZnY2OZ2

、またはInOX1が主成分である領域と、に材料が分離することでモザイク状となり、

InOX1、またはInX2ZnY2OZ2が、膜中に分布した構成(クラウド状)であ

る。なお、InaGabZncOdを主成分とする領域001は、InX2ZnY2OZ

2、またはInOX1が主成分である領域002よりも、大きなバンドギャップを有する

。For example, a case where an In-Ga-Zn oxide having a CAC configuration is used as the CAC-OS of the channel portion will be described. The In-Ga-Zn oxide having a CAC configuration has

As 01, a region whose main component is Ina Gab ZncOd , which has a higher concentration of Ga than

, Or the region where InOX1 is the main component, and the material separates into a mosaic.

InOX1 or InX2 ZnY2 OZ2 is distributed in the film (cloud-like). The

2 or has a larger bandgap than the

ここで、CAC-OSをチャネル部に有する図2(A)に示すトランジスタの伝導モデル

について説明する。図2(B)は、図2(A)に示すトランジスタのソースとドレインと

の間におけるエネルギー準位の分布を説明する模式図である。また、図2(C)は、図2

(A)に示すトランジスタにおいて、X-X’で示す実線上における伝導バンド図である

。なお、各伝導帯において、実線は伝導帯下端のエネルギーを示す。また、Efで示す一

点破線は電子の擬フェルミ準位のエネルギーを示す。また、ここでは、第1のゲート電圧

として、ゲートとソースとの間にマイナスの電圧を印加し、ソースとドレインとの間にド

レイン電圧(Vd>0)を印加している。Here, a conduction model of the transistor shown in FIG. 2A having a CAC-OS in the channel portion will be described. FIG. 2B is a schematic diagram illustrating the distribution of energy levels between the source and drain of the transistor shown in FIG. 2A. Further, FIG. 2 (C) is shown in FIG.

In the transistor shown in (A), it is a conduction band diagram on the solid line shown by XX'. In each conduction band, the solid line indicates the energy at the lower end of the conduction band. The one-dot dashed line indicated by Ef indicates the energy of the quasi-Fermi level of the electron. Further, here, as the first gate voltage, a negative voltage is applied between the gate and the source, and a drain voltage (Vd > 0) is applied between the source and the drain.

図2(A)に示すトランジスタに、マイナスのゲート電圧を印加すると、図2(B)に示

すように、ソースとドレインとの間に、領域001に由来する伝導帯CB001と、領域

002に由来する伝導帯CB002と、が形成される。ここで、第1のバンドギャップは

第2のバンドギャップよりも大きいため、伝導帯CB001におけるポテンシャル障壁は

、伝導帯CB002のポテンシャル障壁よりも大きい。つまり、チャネル部におけるポテ

ンシャル障壁の最大値は、領域001に起因する値をとる。従って、CAC-OSをチャ

ネル部に用いることで、リーク電流を抑制し、スイッチング特性が高いトランジスタとす

ることができる。When a negative gate voltage is applied to the transistor shown in FIG. 2 (A), as shown in FIG. 2 (B), the conduction band CB001 derived from the

また、図2(C)に示すように、第1のバンドギャップを有する領域001は、第2のバ

ンドギャップを有する領域002より、バンドギャップが相対的に広いので、第1のバン

ドギャップを有する領域のEc端は、第2のバンドギャップを有する領域のEc端よりも

相対的に高い位置に存在しうる。Further, as shown in FIG. 2C, the

例えば、第1のバンドギャップを有する領域001の成分が、In-Ga-Zn酸化物(

In:Ga:Zn=1:1:1[原子数比])であり、第2のバンドギャップを有する領

域002の成分がIn-Zn酸化物(In:Zn=2:3[原子数比])である場合を仮

定する。この場合、第1のバンドギャップは、3.3eV、またはその近傍であり、第2

のバンドギャップは、2.4eV、またはその近傍となる。なお、バンドギャップの値は

、各材料の単膜をエリプソメータで測定して得られる値を用いる。For example, the component of

In: Ga: Zn = 1: 1: 1 [atomic number ratio]), and the component of

The bandgap of is 2.4 eV or its vicinity. As the bandgap value, a value obtained by measuring a single film of each material with an ellipsometer is used.

上記の仮定の場合、第1のバンドギャップと、第2のバンドギャップとの差は0.9eV

である。本発明の一態様においては、第1のバンドギャップと、第2のバンドギャップと

の差は、少なくとも0.1eV以上あればよい。ただし、第1のバンドギャップを有する

領域001に由来する価電子帯VB001の位置と、第2のバンドギャップを有する領域

002に由来する価電子帯VB002の位置が異なる場合があるので、第1のバンドギャ

ップと、第2のバンドギャップとの差が、好ましくは0.3eV以上、さらに好ましくは

0.4eV以上であるとよい。In the case of the above assumption, the difference between the first bandgap and the second bandgap is 0.9 eV.

Is. In one aspect of the present invention, the difference between the first bandgap and the second bandgap may be at least 0.1 eV or more. However, the position of the valence band VB001 derived from the

また、上記の仮定の場合、CAC-OS中にキャリアを流れる際に、第2のバンドギャッ

プ、すなわちナローバンドであるIn-Zn酸化物に起因してキャリアが流れる。この際

に、第2のバンドギャップから第1のバンドギャップ、すなわちワイドバンドであるIn

-Ga-Zn酸化物側にキャリアが溢れる。別言すると、ナローバンドであるIn-Zn

酸化物の方がキャリアを生成しやすく、当該キャリアは、ワイドバンドであるIn-Ga

-Zn酸化物に移動する。Further, in the case of the above assumption, when the carrier flows in the CAC-OS, the carrier flows due to the second band gap, that is, the narrow band In—Zn oxide. At this time, the second bandgap to the first bandgap, that is, the wide band In.

-Carriers overflow on the Ga-Zn oxide side. In other words, the narrow band In-Zn

Oxides are more likely to generate carriers, which are wideband In-Ga.

-Move to Zn oxide.

なお、チャネル部を形成する金属酸化物中において、領域001と、領域002とは、モ

ザイク状であり、領域001、および領域002は不規則に偏在している。そのため、X

-X’で示す実線上における伝導バンド図は一例である。In the metal oxide forming the channel portion, the

The conduction band diagram on the solid line indicated by -X'is an example.

基本的に、図3(A)に示すように、領域002が領域001に挟まれたバンドを形成し

ていればよい。または、領域001が領域002に挟まれたバンドを形成していればよい

。Basically, as shown in FIG. 3A, the

また、実際のCAC-OSでは、第1のバンドギャップを有する領域001と第2のバン

ドギャップを有する領域002との接合部は、領域の凝集形態や組成に揺らぎが生じてい

ると考えられる。従って、図3(B)、および図3(C)に示すように、バンドは不連続

ではなく、連続的に変化している場合がある。すなわち、CAC-OS中にキャリアが流

れる際に、第1のバンドギャップと、第2のバンドギャップとが連動すると言い換えても

良い。Further, in an actual CAC-OS, it is considered that the agglomeration form and composition of the region at the junction between the

図4に、図2(A)に示すトランジスタおいて、X-X’で示す実線上における概略バン

ドダイアグラムのモデルを示す。なお、第1のゲート電極に電圧を印加する場合、第2の

ゲート電極にも同じ電圧を同時に印加している。図4(A)には、第1のゲート電圧Vg

として、ゲートとソースとの間にプラスの電圧(Vg>0)を印加した状態(ONSta

te)を示す。図4(B)には、第1のゲート電圧Vgを印加しない(Vg=0)状態を

示す。図4(C)には、第1のゲート電圧Vgとして、ゲートとソースとの間にマイナス

の電圧(Vg<0)を印加した状態(OFFState)を示す。なお、各伝導帯におい

て、実線は伝導帯下端のエネルギーを示す。また、Efで示す一点鎖線は電子の擬フェル

ミ準位のエネルギーを示す。FIG. 4 shows a model of a schematic band diagram on a solid line indicated by XX'in the transistor shown in FIG. 2 (A). When a voltage is applied to the first gate electrode, the same voltage is also applied to the second gate electrode at the same time. FIG. 4 (A) shows the first gate voltage Vg .

As a result, a positive voltage (Vg > 0) is applied between the gate and the source (ONSta).

te) is shown. FIG. 4B shows a state in which the first gate voltage Vg is not applied (Vg = 0). FIG. 4C shows a state (OFFState) in which a negative voltage (Vg <0) is applied between the gate and the source as the first gate voltage Vg . In each conduction band, the solid line indicates the energy at the lower end of the conduction band. The alternate long and short dash line indicated by Ef indicates the energy of the quasi-Fermi level of electrons.

CAC-OSをチャネル部に有するトランジスタは、第1のバンドギャップを有する領域

001と第2のバンドギャップを有する領域002とが、電気的に相互作用を及ぼす。別

言すると、第1のバンドギャップを有する領域001と第2のバンドギャップを有する領

域002とが、相補的に機能する。In the transistor having CAC-OS in the channel portion, the

図4(A)に示すように、トランジスタをオン状態にする方向の電位(Vg>0)が、第

1のゲート電極に印加されると、Ec端の低い第2のバンドギャップを有する領域002

が主な伝導経路となり、電子が流れると同時に、第1のバンドギャップを有する領域00

1にも電子が流れる。このためトランジスタのオン状態において高い電流駆動力、つまり

大きなオン電流および高い電界効果移動度を得ることができる。As shown in FIG. 4A, when a potential (Vg > 0) in the direction of turning on the transistor is applied to the first gate electrode, a region having a second band gap with a low Ec end is applied. 002

Is the main conduction path, and at the same time as the electrons flow, the

Electrons also flow in 1. Therefore, a high current driving force, that is, a large on-current and a high field effect mobility can be obtained in the on state of the transistor.

一方、図4(B)、および図4(C)に示すように、第1のゲートにしきい値電圧未満の

電圧(Vg≦0)を印加することで、第1バンドギャップを有する領域001は、誘電体

(絶縁体)として振る舞うので、領域001中の伝導経路は遮断される。また、第2のバ

ンドギャップを有する領域002は、第1のバンドギャップを有する領域001と接して

いる。従って、第1のバンドギャップを有する領域001は、自らに加えて第2のバンド