JP5371143B2 - Method for manufacturing semiconductor device - Google Patents

Method for manufacturing semiconductor deviceDownload PDFInfo

- Publication number

- JP5371143B2 JP5371143B2JP2007265332AJP2007265332AJP5371143B2JP 5371143 B2JP5371143 B2JP 5371143B2JP 2007265332 AJP2007265332 AJP 2007265332AJP 2007265332 AJP2007265332 AJP 2007265332AJP 5371143 B2JP5371143 B2JP 5371143B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- tube

- film

- insulating layer

- opening

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Electroluminescent Light Sources (AREA)

- Electrodes Of Semiconductors (AREA)

- Drying Of Semiconductors (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Thin Film Transistor (AREA)

Abstract

Description

Translated fromJapanese本発明は、微少な領域を選択的にエッチング加工するための製造技術に関する。特にフラットパネルディスプレー等の表示装置に用いられる微細な開口を形成する集積回路基板の製造技術に関する。The present invention relates to a manufacturing technique for selectively etching a minute region. In particular, the present invention relates to a technique for manufacturing an integrated circuit substrate for forming fine openings used in a display device such as a flat panel display.

薄膜トランジスタ(以下、「TFT」とも記す。)及びそれを用いた電子回路は、半導体膜、絶縁膜及び導電膜などの各種薄膜を基板上に積層し、適宜フォトリソグラフィ技術により所定のパターンを形成して製造されている。フォトリソグラフィ技術とは、フォトマスクと呼ばれる透明な平板面上に光を通さない材料で形成した回路等のパターンを、光を利用して目的とする基板上に転写する技術であり、半導体集積回路等の製造工程において広く用いられている。A thin film transistor (hereinafter also referred to as “TFT”) and an electronic circuit using the thin film transistor are formed by laminating various thin films such as a semiconductor film, an insulating film, and a conductive film on a substrate and appropriately forming a predetermined pattern by a photolithography technique. Manufactured. Photolithographic technology is a technology that uses a light to transfer a circuit pattern or other pattern formed on a transparent flat plate called a photomask onto a target substrate. It is widely used in the manufacturing process.

従来のフォトリソグラフィ技術を用いた製造工程では、フォトレジストと呼ばれる感光性の有機樹脂材料を用いて形成されるマスクパターンの取り扱いだけでも、露光、現像、焼成、剥離といった多段階の工程が必要になる。従って、フォトリソグラフィ工程の回数が増える程、製造コストは必然的に上がってしまうことになる。このような問題点を改善するために、フォトリソグラフィ工程を削減してTFTを製造することが試みられている(例えば、特許文献1参照。)。特許文献1では、フォトリソグラフィ工程によって形成されたレジストマスクを、一回用いた後、膨潤により体積膨張をさせて異なる形状のレジストマスクとして再び用いている。

このように半導体集積回路等の製造工程では、フォトリソグラフィ工程が必須なものとなっている。フォトリソグラフィ工程は、工程数が増え煩雑になるばかりでなく、それに付随して高価なフォトマスクが必要となり、それがコスト上昇の要因となっている。さらに、フォトレジスト、現像液および剥離液などの有機溶剤を大量に使用するため、環境保全の要請から廃液処理に膨大なコストがかかっている。Thus, a photolithography process is indispensable in the manufacturing process of a semiconductor integrated circuit or the like. The photolithography process not only increases the number of processes and becomes complicated, but also requires an expensive photomask, which causes an increase in cost. Furthermore, a large amount of organic solvents such as a photoresist, a developing solution, and a stripping solution are used, so that enormous costs are incurred for waste liquid treatment due to environmental protection requirements.

そこで本発明は、フォトリソグラフィ工程を削減して半導体集積回路を製造する技術を提供することを目的とする。Therefore, an object of the present invention is to provide a technique for manufacturing a semiconductor integrated circuit by reducing the photolithography process.

本発明は、チューブを用いて選択的に薄膜に開口を形成する。本発明におけるチューブとは中空構造を有し先端が開口している細管のことである。従って、チューブは、先端にオリフィスが形成された中空管であるため、内部に処理剤などの材料を通し、オリフィスよりチューブ外部へ流出することができる。チューブを被加工膜に接して配置することによって、チューブ内部と外部とを遮断することができる。本発明においては、チューブ内部を通して物質の吐出又は吸引を行う。本発明においては、チューブを用いて、選択的に開口や導電層を形成することができる。In the present invention, an opening is selectively formed in a thin film using a tube. The tube in the present invention is a thin tube having a hollow structure and having an open end. Therefore, since the tube is a hollow tube having an orifice formed at the tip, a material such as a processing agent can be passed through the tube and can flow out of the tube from the orifice. By arranging the tube in contact with the film to be processed, the inside and the outside of the tube can be shut off. In the present invention, the substance is discharged or sucked through the tube. In the present invention, an opening and a conductive layer can be selectively formed using a tube.

本発明では、チューブを絶縁層の開口形成領域上に絶縁層に接して配置し、そのチューブを通して処理剤(エッチングガス又はエッチング液)を絶縁層に吐出(噴出)する。吐出(噴出)された処理剤(エッチングガス又はエッチング液)によって、絶縁層を選択的に除去し、絶縁層に開口を形成する。従って、導電層上に開口を有する絶縁層が形成され、絶縁層下の導電層が開口の底面に露出する。露出された導電層と接するように開口に導電膜を形成し、導電層と導電膜を絶縁層に設けられた開口において電気的に接続する。In the present invention, the tube is disposed in contact with the insulating layer on the opening forming region of the insulating layer, and the processing agent (etching gas or etching solution) is discharged (spouted) to the insulating layer through the tube. The insulating layer is selectively removed by the discharged processing agent (etching gas or etching solution), and an opening is formed in the insulating layer. Therefore, an insulating layer having an opening is formed on the conductive layer, and the conductive layer under the insulating layer is exposed on the bottom surface of the opening. A conductive film is formed in the opening so as to be in contact with the exposed conductive layer, and the conductive layer and the conductive film are electrically connected to each other in the opening provided in the insulating layer.

また、チューブを絶縁層に一部埋め込むように配置し、物理的な力によって絶縁層に第1の開口を形成し、その後、チューブからエッチングガスを噴出してさらに絶縁層を選択的に除去し、第2の開口を形成することもできる。つまりチューブの物理的な力で第1の開口を形成し、チューブより噴出されるエッチングガスの化学的な力によって第2の開口を形成してもよい。先にチューブよりエッチングガスを吐出して、第1の開口を形成し、チューブを絶縁層に挿入して第2の開口を形成してもよいし、エッチングガスを吐出しながら同時にチューブを絶縁層に挿入して開口を形成してもよい。In addition, the tube is arranged so as to be partially embedded in the insulating layer, the first opening is formed in the insulating layer by physical force, and then the etching gas is ejected from the tube to further remove the insulating layer selectively. A second opening can also be formed. That is, the first opening may be formed by the physical force of the tube, and the second opening may be formed by the chemical force of the etching gas ejected from the tube. The etching gas may be discharged from the tube first to form the first opening, and the tube may be inserted into the insulating layer to form the second opening. An opening may be formed by being inserted into the.

チューブから吐出される処理剤(エッチングガス又はエッチング液)は、チューブが耐えられるものであればエッチングする薄膜によって適宜選択することができる。例えば、幾層にも積層する多層配線などを作製する場合、何層にもわたって異なる薄膜に連続的な開口を形成する際に本発明を用いることができる。The treatment agent (etching gas or etchant) discharged from the tube can be appropriately selected depending on the thin film to be etched as long as the tube can withstand. For example, in the case of producing a multilayer wiring or the like laminated in several layers, the present invention can be used in forming continuous openings in different thin films over several layers.

さらに、本発明のチューブによって絶縁層に開口を形成した後、チューブを通して液状の膜形成材料(例えば導電性を有する組成物)を開口に吐出し、導電層を形成してもよい。開口が微細であると、液状の膜形成材料は表面張力の関係より開口に確実に充填されにくい場合があるが、本発明であると、開口に挿入されたチューブによって確実に開口に膜形成材料を充填でき、形状不良なく膜を形成することができる。Furthermore, after forming an opening in the insulating layer with the tube of the present invention, a liquid film forming material (for example, a conductive composition) may be discharged into the opening through the tube to form the conductive layer. If the opening is fine, the liquid film-forming material may not be reliably filled into the opening due to the surface tension. However, in the present invention, the film-forming material is reliably attached to the opening by the tube inserted into the opening. The film can be formed without a shape defect.

開口の形状はチューブ及びエッチング物質を吐出する吐出口の形状を反映するため、所望の形状が得られるようにチューブを設定すればよい。チューブは柱状(角柱、円柱、三角柱など)、針状などを用いることができる。また開口の深さ方向はチューブを設ける時の力と、チューブが設置される導電層の膜強度によって設定することができる。また、エッチング時間などのエッチング条件を設定することによっても膜厚方向の深さを選択できる。先端の尖った針状のチューブを用いて、導電層に一部埋め込むようにチューブを挿入し設置すると、導電層に凹部を有する開口を形成することができる。また開口形成後、開口を有する絶縁層をマスクとして開口底面に露出された導電層をエッチングによって除去してもよい。Since the shape of the opening reflects the shape of the discharge port for discharging the tube and the etching substance, the tube may be set so as to obtain a desired shape. The tube may have a columnar shape (such as a prism, a cylinder, or a triangular column), a needle shape, or the like. The depth direction of the opening can be set by the force when the tube is provided and the film strength of the conductive layer where the tube is installed. The depth in the film thickness direction can also be selected by setting etching conditions such as etching time. When a needle-like tube with a sharp tip is inserted and installed so as to be partially embedded in the conductive layer, an opening having a recess can be formed in the conductive layer. Further, after the opening is formed, the conductive layer exposed on the bottom surface of the opening may be removed by etching using the insulating layer having the opening as a mask.

本発明は、絶縁層の開口形成領域にチューブを絶縁層に接して配置する。従って、物理的に絶縁層の開口形成領域を設定できるため、確実に所望の位置に開口を形成することができる。従って、本発明を用いて半導体装置、表示装置を歩留まり良く作製することができる。In the present invention, the tube is disposed in contact with the insulating layer in the opening forming region of the insulating layer. Therefore, since the opening formation region of the insulating layer can be set physically, the opening can be surely formed at a desired position. Therefore, a semiconductor device and a display device can be manufactured with high yield by using the present invention.

本発明によってフォトリソグラフィ工程を用いることなく、選択的に薄膜に開口を形成することができるので工程及び材料を削減することができる。According to the present invention, since an opening can be selectively formed in a thin film without using a photolithography process, the number of processes and materials can be reduced.

本発明の表示装置の作製方法の一形態は、導電層を形成し、導電層上に絶縁層を形成し、絶縁層に細管を接して配置し、細管より処理剤を吐出し絶縁層に導電層に達する開口を形成し、開口に導電層と接するように導電膜を形成する。In one embodiment of the method for manufacturing a display device of the present invention, a conductive layer is formed, an insulating layer is formed over the conductive layer, a thin tube is placed in contact with the insulating layer, a treatment agent is discharged from the thin tube, and the conductive layer is conductive. An opening reaching the layer is formed, and a conductive film is formed in contact with the conductive layer in the opening.

本発明の表示装置の作製方法の一形態は、導電層を形成し、導電層上に絶縁層を形成し、絶縁層に細管を接して配置し、細管より処理剤を吐出し絶縁層に導電層に達する開口を形成し、開口に細管より導電性材料を含む組成物を吐出し導電層と接するように導電膜を形成する。In one embodiment of the method for manufacturing a display device of the present invention, a conductive layer is formed, an insulating layer is formed over the conductive layer, a thin tube is placed in contact with the insulating layer, a treatment agent is discharged from the thin tube, and the conductive layer is conductive. An opening reaching the layer is formed, a composition containing a conductive material is discharged from the thin tube into the opening, and a conductive film is formed so as to be in contact with the conductive layer.

本発明の表示装置の作製方法の一形態は、導電層を形成し、導電層上に第1の絶縁層を形成し、第1の絶縁層上に第2の絶縁層を形成し、第2の絶縁層に細管を挿入し第1の開口を形成し、細管より処理剤を吐出し第1の絶縁層に導電層に達する第2の開口を形成し、第1の開口及び第2の開口に導電層と接するように導電膜を形成する。In one embodiment of a method for manufacturing a display device of the present invention, a conductive layer is formed, a first insulating layer is formed over the conductive layer, a second insulating layer is formed over the first insulating layer, and a second insulating layer is formed. A thin tube is inserted into the insulating layer to form a first opening, a processing agent is discharged from the thin tube to form a second opening reaching the conductive layer in the first insulating layer, and the first opening and the second opening A conductive film is formed so as to be in contact with the conductive layer.

本発明の表示装置の作製方法の一形態は、導電層を形成し、導電層上に第1の絶縁層を形成し、第1の絶縁層上に第2の絶縁層を形成し、第2の絶縁層に細管を挿入し第1の開口を形成し、細管より処理剤を吐出し第1の絶縁層に導電層に達する第2の開口を形成し、第1の開口及び第2の開口に細管より導電性材料を含む組成物を吐出し導電層と接するように導電膜を形成する。In one embodiment of a method for manufacturing a display device of the present invention, a conductive layer is formed, a first insulating layer is formed over the conductive layer, a second insulating layer is formed over the first insulating layer, and a second insulating layer is formed. A thin tube is inserted into the insulating layer to form a first opening, a processing agent is discharged from the thin tube to form a second opening reaching the conductive layer in the first insulating layer, and the first opening and the second opening A conductive film is formed so as to be in contact with the conductive layer by discharging a composition containing a conductive material from the thin tube.

本発明の表示装置の作製方法の一形態は、ゲート電極層、ゲート絶縁層、半導体層、ソース電極層及びドレイン電極層を形成し、ソース電極層及びドレイン電極層上に絶縁層を形成し、絶縁層に細管を接して配置し、細管より処理剤を吐出し絶縁層にソース電極層又はドレイン電極層に達する開口を形成し、開口にソース電極層又はドレイン電極層と接するように画素電極層を形成する。In one embodiment of a method for manufacturing a display device of the present invention, a gate electrode layer, a gate insulating layer, a semiconductor layer, a source electrode layer, and a drain electrode layer are formed, and an insulating layer is formed over the source electrode layer and the drain electrode layer. A thin tube is placed in contact with the insulating layer, a processing agent is discharged from the thin tube, an opening reaching the source electrode layer or the drain electrode layer is formed in the insulating layer, and the pixel electrode layer is in contact with the source electrode layer or the drain electrode layer. Form.

本発明の表示装置の作製方法の一形態は、ソース領域及びドレイン領域を有する半導体層を形成し、半導体層上にゲート絶縁層を形成し、半導体層及びゲート絶縁層上にゲート電極層を形成し、半導体層、ゲート絶縁層、及びゲート電極層上に絶縁層を形成し、絶縁層に細管により第1の開口を形成し、細管より処理剤を吐出し絶縁層及びゲート絶縁層にソース領域及びドレイン領域に達する第2の開口を形成し、第1の開口及び第2の開口にソース領域と接するようにソース電極層を、ドレイン領域に接するようにドレイン電極層を形成する。In one embodiment of a method for manufacturing a display device of the present invention, a semiconductor layer having a source region and a drain region is formed, a gate insulating layer is formed over the semiconductor layer, and a gate electrode layer is formed over the semiconductor layer and the gate insulating layer. Then, an insulating layer is formed over the semiconductor layer, the gate insulating layer, and the gate electrode layer, a first opening is formed in the insulating layer by a thin tube, and a processing agent is discharged from the thin tube to form a source region in the insulating layer and the gate insulating layer. And a second opening reaching the drain region, a source electrode layer is formed in contact with the source region in the first opening and the second opening, and a drain electrode layer is formed in contact with the drain region.

上記構成において、処理剤を細管より吐出後、細管から吸引し開口より除去してもよい。処理剤としてエッチングガス、またはエッチング液を用いると、絶縁層を選択的に除去し開口を形成することができる。In the above configuration, after the treatment agent is discharged from the thin tube, it may be sucked from the thin tube and removed from the opening. When an etching gas or an etchant is used as the treatment agent, the insulating layer can be selectively removed and openings can be formed.

上記で形成する導電層の代わりに半導体層を用いることもできる。半導体材料を用いると半導体層とすることができる。表示装置を構成するいずれの導電層、半導体層に用いることができる。例えば導電層としては、配線層、ゲート電極層、ソース電極層、ドレイン電極層、及び画素電極層などに用いることができる。A semiconductor layer can also be used instead of the conductive layer formed above. When a semiconductor material is used, a semiconductor layer can be obtained. It can be used for any conductive layer or semiconductor layer constituting the display device. For example, the conductive layer can be used for a wiring layer, a gate electrode layer, a source electrode layer, a drain electrode layer, a pixel electrode layer, and the like.

本発明のエッチング装置の一形態は、中空構造を有し先端が開口している細管と、基板を載置するステージと、基板上の所定の位置に細管を移動させ設置する位置制御手段と、細管に処理剤を供給する材料貯蔵室と、細管より処理剤を吐出する吐出制御手段とを有する。One form of the etching apparatus of the present invention is a narrow tube having a hollow structure and an open end, a stage on which a substrate is placed, a position control means for moving and setting the thin tube to a predetermined position on the substrate, A material storage chamber for supplying the processing agent to the narrow tube, and a discharge control means for discharging the processing agent from the thin tube.

本発明のエッチング装置の一形態は、中空構造を有し先端が開口している細管と、基板を載置するステージと、基板上の所定の位置に細管を移動させ該細管の先端を被加工面に接触させる位置制御手段と、細管に処理剤を供給する材料貯蔵室と、細管より処理剤を吐出する吐出制御手段とを有する。One embodiment of the etching apparatus of the present invention includes a narrow tube having a hollow structure and an open end, a stage on which a substrate is placed, and the tube is moved to a predetermined position on the substrate to process the tip of the tube Position control means for contacting the surface, material storage chamber for supplying the processing agent to the narrow tube, and discharge control means for discharging the processing agent from the thin tube.

本発明のエッチング装置の一形態は、中空構造を有し先端が開口している細管と、基板を載置するステージと、基板上の所定の位置に細管を移動させ設置する位置制御手段と、細管に処理剤を供給する材料貯蔵室と、細管より処理剤を吐出する吐出制御手段と、吐出した処理剤を吸引する吸引制御手段とを有する。One form of the etching apparatus of the present invention is a narrow tube having a hollow structure and an open end, a stage on which a substrate is placed, a position control means for moving and setting the thin tube to a predetermined position on the substrate, A material storage chamber for supplying the processing agent to the narrow tube, a discharge control means for discharging the processing agent from the thin tube, and a suction control means for sucking the discharged processing agent.

本発明のエッチング装置の一形態は、中空構造を有し先端が開口している細管と、基板を載置するステージと、基板上の所定の位置に細管を移動させ該細管の先端を被加工面に接触させる位置制御手段と、細管に処理剤を供給する材料貯蔵室と、細管より処理剤を吐出する吐出制御手段と、吐出した処理剤を吸引する吸引制御手段とを有する。One embodiment of the etching apparatus of the present invention includes a narrow tube having a hollow structure and an open end, a stage on which a substrate is placed, and the tube is moved to a predetermined position on the substrate to process the tip of the tube Position control means for contacting the surface, material storage chamber for supplying the processing agent to the narrow tube, discharge control means for discharging the processing agent from the thin tube, and suction control means for sucking the discharged processing agent.

上記本発明のエッチング装置を用いて、本発明の表示装置及び半導体装置を作製することができる。The display device and the semiconductor device of the present invention can be manufactured using the etching apparatus of the present invention.

本発明は表示機能を有する装置である表示装置にも用いることができ、本発明を用いる表示装置には、エレクトロルミネセンス(以下「EL」ともいう。)と呼ばれる発光を発現する有機物、無機物、若しくは有機物と無機物の混合物を含む層を、電極間に介在させた発光素子とTFTとが接続された発光表示装置や、液晶材料を有する液晶素子を表示素子として用いる液晶表示装置などがある。本発明において、表示装置とは、表示素子(液晶素子や発光素子など)を有する装置のことを言う。なお、基板上に液晶素子やEL素子などの表示素子を含む複数の画素やそれらの画素を駆動させる周辺駆動回路が形成された表示パネル本体のことでもよい。さらに、フレキシブルプリントサーキット(FPC)やプリント配線基盤(PWB)が取り付けられたもの(ICや抵抗素子や容量素子やインダクタやトランジスタなど)も含んでもよい。さらに、偏光板や位相差板などの光学シートを含んでいても良い。さらに、バックライトユニット(導光板やプリズムシートや拡散シートや反射シートや光源(LEDや冷陰極管など)を含んでいても良い)を含んでいても良い。The present invention can also be used for a display device that is a device having a display function. The display device using the present invention includes an organic substance, an inorganic substance, and an organic substance that emits light called electroluminescence (hereinafter also referred to as “EL”). Alternatively, there are a light-emitting display device in which a light-emitting element in which a layer containing a mixture of an organic substance and an inorganic substance is interposed between electrodes and a TFT are connected, and a liquid crystal display device in which a liquid crystal element having a liquid crystal material is used as a display element. In the present invention, a display device refers to a device having a display element (such as a liquid crystal element or a light emitting element). Note that a display panel body in which a plurality of pixels including a display element such as a liquid crystal element or an EL element and a peripheral driver circuit for driving these pixels are formed over a substrate may be used. Furthermore, a device to which a flexible printed circuit (FPC) or a printed wiring board (PWB) is attached (such as an IC, a resistor, a capacitor, an inductor, or a transistor) may also be included. Furthermore, an optical sheet such as a polarizing plate or a retardation plate may be included. Furthermore, a backlight unit (which may include a light guide plate, a prism sheet, a diffusion sheet, a reflection sheet, and a light source (such as an LED or a cold cathode tube)) may be included.

なお、表示素子や表示装置は、様々な形態を用いたり、様々な素子を有することが出来る。例えば、EL素子(有機EL素子、無機EL素子又は有機物及び無機物を含むEL素子)、電子放出素子、液晶素子、電子インク、グレーティングライトバルブ(GLV)、プラズマディスプレイ(PDP)、デジタルマイクロミラーデバイス(DMD)、圧電セラミックディスプレイ、カーボンナノチューブ、など、電気磁気的作用によりコントラストが変化する表示媒体を適用することができる。なお、EL素子を用いた表示装置としてはELディスプレイ、電子放出素子を用いた表示装置としてはフィールドエミッションディスプレイ(FED)やSED方式平面型ディスプレイ(SED:Surface−conduction Electron−emitter Display)など、液晶素子を用いた表示装置としては液晶ディスプレイ、透過型液晶ディスプレイ、半透過型液晶ディスプレイ、反射型液晶ディスプレイ、電子インクを用いた表示装置としては電子ペーパーがある。Note that the display element and the display device can have various forms or have various elements. For example, EL elements (organic EL elements, inorganic EL elements or EL elements including organic and inorganic substances), electron-emitting elements, liquid crystal elements, electronic ink, grating light valves (GLV), plasma displays (PDP), digital micromirror devices ( DMD), piezoelectric ceramic displays, carbon nanotubes, and the like, which can be applied to display media whose contrast is changed by an electromagnetic action. Note that an EL display is used as a display device using an EL element, and a liquid crystal display such as a field emission display (FED) or an SED type flat display (SED: Surface-Conduction Electron-Emitter Display) is used as a display device using an electron-emitting device. A display device using the element includes a liquid crystal display, a transmissive liquid crystal display, a transflective liquid crystal display, a reflective liquid crystal display, and a display device using electronic ink includes electronic paper.

また、本発明を用いて半導体素子(トランジスタ、メモリ素子やダイオードなど)を含む回路を有する装置や、プロセッサ回路を有するチップなどの半導体装置を作製することができる。なお、本発明において、半導体装置とは、半導体特性を利用することで機能しうる装置を指す。Further, by using the present invention, a device having a circuit including a semiconductor element (a transistor, a memory element, a diode, or the like) or a semiconductor device such as a chip having a processor circuit can be manufactured. Note that in the present invention, a semiconductor device refers to a device that can function by utilizing semiconductor characteristics.

本発明により、絶縁層にマスクを形成することなくコンタクトホールを形成することができるので、工程を簡略化することができる。また、フォトレジスト等を塗布して露光及び現像する必要がないので、加工に必要な原材料コストを削減することができる。さらに、コンタクトホールを確実に形成することができるので、半導体装置及び表示装置の製造歩留まりの向上を図ることができる。According to the present invention, a contact hole can be formed without forming a mask in an insulating layer, so that the process can be simplified. In addition, since it is not necessary to apply a photoresist or the like for exposure and development, it is possible to reduce raw material costs required for processing. Furthermore, since the contact hole can be formed reliably, the manufacturing yield of the semiconductor device and the display device can be improved.

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。Embodiments of the present invention will be described in detail with reference to the drawings. However, the present invention is not limited to the following description, and it is easily understood by those skilled in the art that modes and details can be variously changed without departing from the spirit and scope of the present invention. Therefore, the present invention should not be construed as being limited to the description of the embodiments below. Note that in structures of the present invention described below, the same portions or portions having similar functions are denoted by the same reference numerals in different drawings, and description thereof is not repeated.

(実施の形態1)

本実施の形態では、確実により簡略化した工程で低コストに作製することを目的としたコンタクトホールの形成方法について、図1を用いて説明する。(Embodiment 1)

In this embodiment mode, a method for forming a contact hole, which is intended to be manufactured at a low cost through a process that is surely simplified, will be described with reference to FIGS.

本発明は、チューブを用いて選択的に薄膜に開口を形成する。本発明におけるチューブとは中空構造を有し先端が開口している細管のことである。従って、チューブは、先端にオリフィスが形成された中空管であるため、内部に処理剤などの材料を通し、オリフィスよりチューブ外部へ流出することができる。チューブを被加工膜に接して配置することによって、薄膜においてチューブ内部と外部とを遮断することができる。本発明においては。チューブ内部を通して物質の吐出又は吸引を行う。本発明のチューブを用いて、選択的に開口や導電層を形成することができる。In the present invention, an opening is selectively formed in a thin film using a tube. The tube in the present invention is a thin tube having a hollow structure and having an open end. Therefore, since the tube is a hollow tube having an orifice formed at the tip, a material such as a processing agent can be passed through the tube and can flow out of the tube from the orifice. By disposing the tube in contact with the film to be processed, the inside and outside of the tube can be shut off in the thin film. In the present invention. The substance is discharged or sucked through the inside of the tube. An opening and a conductive layer can be selectively formed using the tube of the present invention.

本実施の形態では、チューブを絶縁層の開口形成領域上に絶縁層に接して配置し、そのチューブを通して処理剤(エッチングガス又はエッチング液)を絶縁層に吐出(噴出)する。吐出(噴出)された処理剤(エッチングガス又はエッチング液)によって、絶縁層を選択的に除去し、絶縁層に開口を形成する。従って、導電層上に開口を有する絶縁層が形成され、絶縁層下の導電層が開口の底面に露出する。露出された導電層と接するように開口に導電膜を形成し、導電層と導電膜を絶縁層に設けられた開口において電気的に接続する。In this embodiment mode, the tube is disposed in contact with the insulating layer over the opening formation region of the insulating layer, and a processing agent (etching gas or etching solution) is discharged (spouted) to the insulating layer through the tube. The insulating layer is selectively removed by the discharged processing agent (etching gas or etching solution), and an opening is formed in the insulating layer. Therefore, an insulating layer having an opening is formed on the conductive layer, and the conductive layer under the insulating layer is exposed on the bottom surface of the opening. A conductive film is formed in the opening so as to be in contact with the exposed conductive layer, and the conductive layer and the conductive film are electrically connected to each other in the opening provided in the insulating layer.

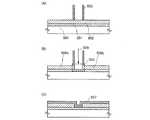

図1を用いて具体的に説明する。本実施の形態では、図1(A)に示すように、絶縁表面を有する基板500上に、導電層501を形成し、導電層501上に絶縁層502を形成する。絶縁層502の開口形成領域にチューブ503を絶縁層502に接して設ける。図1には、チューブ503を支持する手段を示していないが、チューブ503は絶縁層502に接触して保持されていればよい。例えば、チューブを基板上に設けて、基板を支持手段(支持基板)として用いたり、被処理膜上に支持手段として、支持膜を形成し、支持膜にチューブを挿入することでチューブを被処理膜上に保持してもよい。This will be specifically described with reference to FIG. In this embodiment, as illustrated in FIG. 1A, a

支持手段によって支持されたチューブは、移動制御手段によって、被処理膜上の所定の位置に被処理膜に接して設置される。まず、被処理膜の被加工面に対応する位置にチューブを移動する。次に被処理膜に接するようにチューブを移動させ、支持手段によって保持する。チューブを被処理膜に挿入する場合、チューブを被処理膜に挿入した状態で支持手段によって保持する。被処理膜の載置するステージを移動させ、チューブに接するようにしてもよい。The tube supported by the support means is placed in contact with the film to be processed at a predetermined position on the film to be processed by the movement control means. First, the tube is moved to a position corresponding to the processing surface of the film to be processed. Next, the tube is moved so as to be in contact with the film to be processed, and is held by the supporting means. When the tube is inserted into the film to be processed, the tube is held by the support means while being inserted into the film to be processed. The stage on which the film to be processed is placed may be moved so as to be in contact with the tube.

図40に支持膜520a、520bを用いてチューブ503を支持する例を示す。図40は図1に対応しており、支持膜520a、520bを形成する他は図1と同様である。図40において、絶縁層502に接して配置されるチューブ503は支持膜520a、520bによって支持されている。支持膜を形成した後、チューブを挿入して固定してもよいし、チューブを開口形成領域に設けた後、チューブ周囲を支持するように支持膜を形成してもよい。FIG. 40 shows an example in which the

エッチングガス509を吐出して絶縁層502に開口505を形成した後(図40(B)参照。)、支持膜520a、520bも除去する(図40(C)参照。)。絶縁層506a、506b、露出された導電層501上に導電膜507を形成し、開口505において導電層501と導電膜507とを電気的に接続する(図40(D)参照。)。After the

チューブ503を選択的に設けた状態でチューブ503を通してエッチングガス509を絶縁層502に噴出(吐出)する。噴出(吐出)されたエッチングガス509によって、絶縁層502を選択的に除去し、絶縁層502に開口505を形成する(図1(B)参照。)。An

チューブ503を除去し、開口505を有する絶縁層506a、506bを形成することができる。導電層501が露出された開口505に導電膜507を形成し、導電層501と導電膜507とを電気的に接続することができる(図1(C)参照。)。The

開口の形状はチューブの形状を反映するため、所望の形状が得られるようにチューブを設定すればよい。チューブは柱状(角柱、円柱、三角柱など)、針状などを用いることができる。また開口の深さ方向はチューブを設ける時の力と、チューブが設置される導電層の膜強度によって設定することができる。また、エッチング時間などのエッチング条件を設定することによっても膜厚方向の深さを選択できる。Since the shape of the opening reflects the shape of the tube, the tube may be set so as to obtain a desired shape. The tube may have a columnar shape (such as a prism, a cylinder, or a triangular column), a needle shape, or the like. The depth direction of the opening can be set by the force when the tube is provided and the film strength of the conductive layer where the tube is installed. The depth in the film thickness direction can also be selected by setting etching conditions such as etching time.

また、チューブの上面形状を、点状、円形、楕円形、矩形、または線状(厳密には細長い長方形状)と適宜設定すると、得られる絶縁層の開口の上面形状も同様にチューブ及びその吐出口形状を反映して形成することができる。In addition, when the top surface shape of the tube is appropriately set as a dotted, circular, elliptical, rectangular, or linear shape (strictly, a long and narrow rectangular shape), the top surface shape of the opening of the obtained insulating layer is similarly the tube and its discharge. It can be formed reflecting the shape of the outlet.

また、チューブは複数重なる構造でもよく、チューブが2重構造になっている例を図41に示す。本発明においてチューブは吐出を行うだけでなく、吸引もすることができる。図41は図1に対応しており、チューブ523のみが異なる例であり、他は図1と同様である。Further, a plurality of tubes may be stacked, and an example in which the tubes have a double structure is shown in FIG. In the present invention, the tube can perform not only discharge but also suction. FIG. 41 corresponds to FIG. 1, and is an example in which only the

図41(A)に示すチューブ523は、内側にチューブ525a、外側にチューブ525bを有している。チューブ525aはチューブ525bよりやや短く、絶縁層502との間に空間を有して配置される。図41(B)に示すようにチューブ523の内側のチューブ525a内を通ってエッチングガス526aが吐出され、絶縁層502を選択的に除去していく。同時に、外側のチューブ525bと内側のチューブ525aとの間を通って、エッチングガス及び絶縁層502のエッチングされた絶縁性材料526bが矢印の方向に吸引され開口より除去される。このようにチューブ内部を隔てて材料の供給と廃棄(除去)を同時に行ってもよい。エッチングによる残渣が開口よりすぐ除去されるので、絶縁層のエッチング効率(エッチング時間、エッチング速度)を向上させることができる。絶縁層506a、506b、露出された導電層501上に導電膜507を形成し、開口505において導電層501と導電膜507とを電気的に接続する(図41(C)参照。)。A

図2に示すように、チューブを絶縁層開口形成領域に配置する時に、チューブの先端を絶縁層に挿入し一部絶縁層に埋め込むようにしてもよい。絶縁表面を有する基板510上に、導電層511を形成し、導電層511上に絶縁層512を形成する。絶縁層512の開口形成領域にチューブ513を絶縁層512にチューブ513の先端が一部埋め込むようにして設ける(図2(A)参照。)。図2には、チューブ513を支持する手段を示していないが、チューブ513は絶縁層512に接触して保持されていればよい。例えば、チューブを基板上に設けて、基板を支持手段(支持基板)として用いたり、被処理膜上に支持手段として、支持膜を形成し、支持膜にチューブを挿入することでチューブを被処理膜上に保持してもよい。またチューブ513は絶縁層512に一部埋め込まれているため、絶縁層512も支えとして働く。As shown in FIG. 2, when the tube is disposed in the insulating layer opening formation region, the tip of the tube may be inserted into the insulating layer and partially embedded in the insulating layer. A

チューブ513を選択的に設けた状態でそのチューブ513を通してエッチングガス519を絶縁層512に噴出(吐出)する。噴出(吐出)されたエッチングガス519によって、絶縁層512を選択的に除去し、絶縁層512に開口515を形成する(図2(B)参照。)。With the

チューブ513を除去することによって、開口515を有する絶縁層516a、516bを形成することができる。開口515は、チューブの形状を反映するため、側面に段差を有する形状となる。導電層511が露出された開口515に導電膜517を形成し、導電層511と導電膜517とを電気的に接続することができる(図2(C)参照。)。By removing the

絶縁層を選択的に除去するため、チューブより吐出されるエッチング物質は、エッチングガスでもよいし、エッチング液でもよい。エッチングはエッチングガス、エッチング液、エッチング条件を適宜設定することによって、異方的、等方的にエッチングすることができる。液状のエッチング液を用いて、等方的にエッチングを行う例を図3に示す。In order to selectively remove the insulating layer, the etching substance discharged from the tube may be an etching gas or an etching solution. Etching can be performed anisotropically and isotropically by appropriately setting an etching gas, an etchant, and etching conditions. FIG. 3 shows an example of isotropic etching using a liquid etching solution.

図3(A)乃至(C)で用いるチューブは、先端が細い円錐形状の例であり、エッチング液のような液状材料を充填するのに適している。絶縁表面を有する基板530上に、導電層531を形成し、導電層531上に絶縁層532を形成する。絶縁層532の開口形成領域にチューブ533を絶縁層532に接して配置する(図3(A)参照。)。チューブ533内部にはエッチング液539が充填されている。The tubes used in FIGS. 3A to 3C are examples having a conical shape with a thin tip, and are suitable for filling a liquid material such as an etching solution. A

チューブ533を選択的に設けた状態でそのチューブ533を通してエッチング液539を絶縁層532に吐出する。吐出されたエッチング液539によって、絶縁層532を選択的に除去し、絶縁層532に開口535を形成する(図3(B)参照。)。With the

次にチューブ533を除去することによって、開口535を有する絶縁層536a、536bを形成することができる。開口535は、エッチング液539により等方的にエッチングされるため、図3(B)に示すようにチューブ533の吐出口より広い領域に開口が形成される。導電層531が露出された開口535に導電膜537を形成し、導電層531と導電膜537とを電気的に接続することができる(図3(C)参照。)。Next, by removing the

エッチング液によって絶縁層は溶解されるが、エッチング液と絶縁層形成材料の混在した溶液をチューブを通して吸引し、除去してもよい。本発明の中空構造を有し先端が開口している細管であるチューブは吐出を行うだけでなく、吸引もすることができる。Although the insulating layer is dissolved by the etching solution, a solution in which the etching solution and the insulating layer forming material are mixed may be sucked through the tube and removed. The tube, which is a thin tube having a hollow structure according to the present invention and having an open end, can not only discharge but also suction.

本発明において、エッチング液のような液状の材料をチューブを通して被処理膜を加工する場合、液状の材料(例えばエッチング液)に対して、撥液処理するとよい。撥液処理は、被処理膜上に撥液性を有する物質を含む膜を形成することによって行うことができる。被処理膜表面で液状の材料(エッチング液など)ははじかれるので、液状の材料(エッチング液など)が被処理膜とチューブとの間より流出しにくくすることができる。従って、被処理膜表面の凹凸などによってチューブを密着して配置できなかった場合でも、エッチング液などがチューブ外に流出(吐出)して被処理膜の処理領域外の領域を加工してしまうという不良を防ぐことができる。制御性よく被処理膜に所望の形状に開口を形成することができる。In the present invention, when a film to be processed is processed through a tube with a liquid material such as an etching solution, a liquid repellent treatment may be performed on the liquid material (for example, an etching solution). The liquid repellent treatment can be performed by forming a film containing a liquid repellent substance on the film to be processed. Since a liquid material (such as an etchant) is repelled on the surface of the film to be processed, the liquid material (such as an etchant) can be more unlikely to flow out between the film to be processed and the tube. Therefore, even when the tube cannot be placed in close contact due to the unevenness of the surface of the film to be processed, the etching solution or the like flows out (discharges) out of the tube, and the region outside the processing region of the film to be processed is processed. Defects can be prevented. An opening can be formed in a desired shape in the film to be processed with good controllability.

撥液性を有する物質として、フッ化炭素基(フッ化炭素鎖)を含む物質、あるいはシランカップリング剤を含む物質を用いることができる。シランカップリング剤は単分子膜を形成することができるため、分解、改質を効率よく行え、短時間でぬれ性を変化させることができる。また、シランカップリング剤は、フッ化炭素基(フッ化炭素鎖)を有するもののみでなく、アルキル基を有するものも基板に配列させることで、低ぬれ性を示すため、用いることが可能である。またシランカップリング剤は含まれる官能基がフッ化炭素基かアルキル基によって、そのぬれ性を低める効果が異なるので、必要なぬれ性が得られるように材料によって適宜設定することができる。As the substance having liquid repellency, a substance containing a fluorocarbon group (fluorocarbon chain) or a substance containing a silane coupling agent can be used. Since the silane coupling agent can form a monomolecular film, it can be efficiently decomposed and modified, and the wettability can be changed in a short time. Silane coupling agents can be used because they exhibit low wettability by arranging not only those having a fluorocarbon group (fluorocarbon chain) but also those having an alkyl group on the substrate. is there. Moreover, since the functional group contained in the silane coupling agent differs depending on the fluorocarbon group or the alkyl group in reducing the wettability, it can be appropriately set depending on the material so as to obtain the required wettability.

撥液性を有する物質として、フッ化炭素基(フッ化炭素鎖)を含む物質、あるいはシランカップリング剤を含む物質を用いることができる。シランカップリング剤は、Rn−Si−X(4−n)(n=1、2、3)の化学式で表される。ここで、Rは、アルキル基などの比較的不活性な基を含む物である。また、Xはハロゲン、メトキシ基、エトキシ基又はアセトキシ基など、基質表面の水酸基あるいは吸着水との縮合により結合可能な加水分解基からなる。As the substance having liquid repellency, a substance containing a fluorocarbon group (fluorocarbon chain) or a substance containing a silane coupling agent can be used. The silane coupling agent is represented by a chemical formula of Rn—Si—X(4-n) (n = 1, 2, 3). Here, R is a substance containing a relatively inert group such as an alkyl group. X is a hydrolyzable group such as halogen, methoxy group, ethoxy group or acetoxy group, which can be bonded by condensation with a hydroxyl group on the substrate surface or adsorbed water.

撥液性を有する物質として、シランカップリング剤のRに、アルキル基を有す物質であるアルコキシシランも用いることができ、例えば有機シランとしてオクタデシルトリメトキシシラン等を用いることができる。アルコキシシランとしては、炭素数2〜30のアルコキシシランが好ましい。代表的には、デシルトリメトキシシラン、エチルトリエトキシシラン、プロピルトリエトキシシラン、オクチルトリエトキシシラン、デシルトリエトキシシラン、ドデシルトリエトキシシラン、オクタデシルトリエトキシシラン(ODS)、エイコシルトリエトキシシラン、トリアコンチルトリエトキシシランがあげられる。なお、長鎖アルキル基を有するシラン化合物は、特にぬれ性を低下させることが可能であり好ましい。また、デシルトリクロロシラン、テトラデシルトリクロロシラン、オクタデシルトリクロロシラン、エイコシルトリクロロシラン、ドコシルトリクロロシラン等も用いることができる。As a substance having liquid repellency, alkoxysilane which is a substance having an alkyl group can be used for R of the silane coupling agent. For example, octadecyltrimethoxysilane or the like can be used as an organic silane. As alkoxysilane, C2-C30 alkoxysilane is preferable. Typically, decyltrimethoxysilane, ethyltriethoxysilane, propyltriethoxysilane, octyltriethoxysilane, decyltriethoxysilane, dodecyltriethoxysilane, octadecyltriethoxysilane (ODS), eicosyltriethoxysilane, tria An example is contitriethoxysilane. A silane compound having a long-chain alkyl group is particularly preferable because it can reduce wettability. Further, decyltrichlorosilane, tetradecyltrichlorosilane, octadecyltrichlorosilane, eicosyltrichlorosilane, docosyltrichlorosilane, and the like can also be used.

また、シランカップリング剤の代表例として、Rにフルオロアルキル基を有するフッ素系シランカップリング剤(フルオロアルキルシラン(FAS))を用いることにより、よりぬれ性を低めることができる。FASのRは、(CF3)(CF2)x(CH2)y(x:0以上10以下の整数、y:0以上4以下の整数)で表される構造を持ち、複数個のR又はXがSiに結合している場合には、R又はXはそれぞれすべて同じでも良いし、異なっていてもよい。代表的なFASとしては、ヘプタデカフルオロテトラヒドロデシルトリエトキシシラン、ヘプタデカフルオロテトラヒドロデシルトリクロロシラン、トリデカフルオロテトラヒドロオクチルトリクロロシラン、トリフルオロプロピルトリメトキシシラン、トリデカフルオロオクチルトリメトキシシラン等のフルオロアルキルシラン(以下、FASともいう。)が挙げられる。また、トリデカフルオロオクチルトリクロロシラン等の加水分解基がハロゲンであるカップリング剤も用いることができる。もちろん例示の化合物に限定される物ではない。Further, as a representative example of the silane coupling agent, wettability can be further reduced by using a fluorine-based silane coupling agent (fluoroalkylsilane (FAS)) having a fluoroalkyl group in R. R of FAS has a structure represented by (CF3 ) (CF2 )x (CH2 )y (x: an integer of 0 or more and 10 or less, y: an integer of 0 or more and 4 or less), and a plurality of R Alternatively, when X is bonded to Si, R and X may all be the same or different. As typical FAS, fluoroalkyl such as heptadecafluorotetrahydrodecyltriethoxysilane, heptadecafluorotetrahydrodecyltrichlorosilane, tridecafluorotetrahydrooctyltrichlorosilane, trifluoropropyltrimethoxysilane, tridecafluorooctyltrimethoxysilane, etc. Silane (hereinafter also referred to as FAS) can be given. In addition, a coupling agent such as tridecafluorooctyltrichlorosilane whose hydrolyzable group is halogen can also be used. Of course, the compounds are not limited to the exemplified compounds.

また、撥液性を有する物質としてチタネートカップリング剤、アルミネートカップリング剤を用いてもよい。例えば、イソプロピルトリイソオクタノイルチタネート、イソプロピル(ジオクチルパイロホスフェート)チタネート、イソプロピルトリステアロイルチタネート、イソプロピルトリス(ジオクチルホスフェート)チタネート、イソプロピルジメタクリルイソステアロイルチタネート、アセトアルコキシアルミニウムジイソプロピレート等が挙げられる。Further, a titanate coupling agent or an aluminate coupling agent may be used as the substance having liquid repellency. For example, isopropyl triisooctanoyl titanate, isopropyl (dioctyl pyrophosphate) titanate, isopropyl tristearoyl titanate, isopropyl tris (dioctyl phosphate) titanate, isopropyl dimethacrylisostearoyl titanate, acetoalkoxy aluminum diisopropylate and the like can be mentioned.

上記のような撥液性を有する物質を被形成領域に膜として形成するには、液状の物質を蒸発させ、被形成領域に形成する気相成膜法などを用いることができる。また、撥液性を有する物質はスピンコート法、ディップ法、液滴吐出法、印刷法(スクリーン印刷やオフセット印刷など)を用いて形成することもでき、溶媒に溶解した溶液としてもよい。In order to form the liquid repellent material as a film in the formation region, a vapor deposition method in which a liquid substance is evaporated and formed in the formation region can be used. The substance having liquid repellency can be formed by a spin coating method, a dip method, a droplet discharge method, a printing method (such as screen printing or offset printing), or a solution in a solvent.

撥液性を有する物質を含む溶液の溶媒としては、水、アルコール、ケトン、炭化水素系溶媒(脂肪族炭化水素、芳香族炭化水素、ハロゲン化炭化水素など)、及びエーテル系化合物、及びこれらの混合物を用いることができる。例えば、メタノール、エタノール、プロパノール、アセトン、ブタノン、n−ペンタン、n−ヘキサン、n−ヘプタン、n−オクタン、n−デカン、ジシクロペンタン、ベンゼン、トルエン、キシレン、デュレン、インデン、テトラヒドロナフタレン、デカヒドロナフタレン、スクワラン、四塩化炭素、クロロホルム、塩化メチレン、トリクロロエタン、ジエチルエーテル、ジオキサン、ジメトキシエタン又はテトラヒドロフランなどを用いる。上記溶液の濃度は特に限定はないが、0.001〜20wt%の範囲とすればよい。As a solvent of a solution containing a substance having liquid repellency, water, alcohol, ketone, hydrocarbon solvent (aliphatic hydrocarbon, aromatic hydrocarbon, halogenated hydrocarbon, etc.), ether compound, and these Mixtures can be used. For example, methanol, ethanol, propanol, acetone, butanone, n-pentane, n-hexane, n-heptane, n-octane, n-decane, dicyclopentane, benzene, toluene, xylene, durene, indene, tetrahydronaphthalene, deca Hydronaphthalene, squalane, carbon tetrachloride, chloroform, methylene chloride, trichloroethane, diethyl ether, dioxane, dimethoxyethane, tetrahydrofuran, or the like is used. The concentration of the solution is not particularly limited, but may be in the range of 0.001 to 20 wt%.

また、上記撥液性を有する物質に、ピリジン、トリエチルアミン、ジメチルアニリン等のアミンを混合してもよい。更に、ギ酸、酢酸等のカルボン酸を触媒として添加してもよい。Further, amines such as pyridine, triethylamine, dimethylaniline may be mixed with the liquid repellent material. Further, a carboxylic acid such as formic acid or acetic acid may be added as a catalyst.

上記のように撥液性を有する物質を液状の状態で被形成領域に付着させるスピンコート法等を用いて単分子膜を形成する際の処理は、処理温度は室温(約25℃)から150℃、処理時間は数分から12時間とすればよい。処理条件は、撥液性を有する物質の性質、溶液の濃度、処理温度、処理時間によって適宜設定すればよい。また、形成する薄膜を上記撥液性を有する物質を含む溶液を作成する際に用いることのできる溶媒で洗浄すると、未反応の撥液性を有する物質を除去することができる。この場合、超音波洗浄器等を用いてもよい。As described above, the processing temperature when forming a monomolecular film using a spin coat method or the like in which a liquid-repellent substance is attached to a formation region in a liquid state is from room temperature (about 25 ° C.) to 150 ° C. The treatment time may be from several minutes to 12 hours. The treatment conditions may be appropriately set depending on the properties of the substance having liquid repellency, the concentration of the solution, the treatment temperature, and the treatment time. In addition, when the thin film to be formed is washed with a solvent that can be used for preparing a solution containing the liquid repellent substance, the unreacted liquid repellent substance can be removed. In this case, an ultrasonic cleaner or the like may be used.

本発明で用いることのできる撥液性を有する物質を含む膜は膜厚0.3nm以上10nm以下という薄膜でもよい。なお、撥液性を有する物質を液状の状態で被形成領域に付着させるスピンコート法等を用いて形成する撥液性を有する物質の薄膜は非常に薄く、膜厚が0.3nm以上10nm以下の範囲の単分子膜となり得る。The film containing a liquid-repellent substance that can be used in the present invention may be a thin film with a thickness of 0.3 nm to 10 nm. Note that a thin film of a material having liquid repellency formed using a spin coating method or the like in which a substance having liquid repellency is attached to a formation region in a liquid state is very thin and has a thickness of 0.3 nm to 10 nm. It can be a monomolecular film in the range.

また、ぬれ性を低めるように制御し、低ぬれ性領域を形成する組成物の一例として、フッ化炭素(フルオロカーボン)基(フッ化炭素鎖)を有する材料(フッ素系樹脂)を用いることができる。フッ素系樹脂として、ポリテトラフルオロエチレン(PTFE;四フッ化エチレン樹脂)、パーフルオロアルコキシアルカン(PFA;四フッ化エチレンパーフルオロアルキルビニルエーテル共重合樹脂)、パーフルオロエチレンプロペンコーポリマー(PFEP;四フッ化エチレン−六フッ化プロピレン共重合樹脂)、エチレン−テトラフルオロエチレンコポリマー(ETFE;四フッ化エチレン−エチレン共重合樹脂)、ポリビニリデンフルオライド(PVDF;フッ化ビニリデン樹脂)、ポリクロロトリフルオロエチレン(PCTFE;三フッ化塩化エチレン樹脂)、エチレン−クロロトリフルオロエチレンコポリマー(ECTFE;三フッ化塩化エチレン−エチレン共重合樹脂)、ポリテトラフルオロエチレン−パーフルオロジオキソールコポリマー(TFE/PDD)、ポリビニルフルオライド(PVF;フッ化ビニル樹脂)等を用いることができる。In addition, as an example of a composition that is controlled to reduce wettability and forms a low wettability region, a material having a fluorocarbon (fluorocarbon) group (fluorocarbon chain) (fluorine-based resin) can be used. . Examples of fluorine resins include polytetrafluoroethylene (PTFE; tetrafluoroethylene resin), perfluoroalkoxyalkane (PFA; tetrafluoroethylene perfluoroalkyl vinyl ether copolymer resin), and perfluoroethylene propene copolymer (PFEP; four fluoropolymer). Ethylene-hexafluoropropylene copolymer resin), ethylene-tetrafluoroethylene copolymer (ETFE; tetrafluoroethylene-ethylene copolymer resin), polyvinylidene fluoride (PVDF; vinylidene fluoride resin), polychlorotrifluoroethylene (PCTFE; trifluoroethylene chloride resin), ethylene-chlorotrifluoroethylene copolymer (ECTFE; trifluoroethylene chloride-ethylene copolymer resin), polytetrafluoroethylene-perfluorodioxide Rukoporima (TFE / PDD), polyvinyl fluoride (PVF; a vinyl fluoride resin), or the like can be used.

また、無機材料、有機材料にCF4プラズマ等による処理を行うと、ぬれ性を低めることができる。例えば、有機材料としてポリビニルアルコール(PVA)のような水溶性樹脂を、H2O等の溶媒に混合した材料を用いることができる。また、PVAと他の水溶性樹脂を組み合わせて使用してもよい。In addition, when an inorganic material or an organic material is treated with CF4 plasma or the like, wettability can be reduced. For example, a material obtained by mixing a water-soluble resin such as polyvinyl alcohol (PVA) in a solvent such as H2 O as an organic material can be used. Moreover, you may use combining PVA and another water-soluble resin.

エッチングスとしては、Cl2、BCl3、SiCl4もしくはCCl4などを代表とする塩素系ガス、CF4、SF6もしくはNF3などを代表とするフッ素系ガス又はO2を適宜用いることができる。エッチング液としては、フッ酸、水酸化テトラメチルアンモニウム水溶液(TMAH)などを適宜用いるとよい。Etchings may be appropriately used a chlorine-based gas typified by Cl2 , BCl3 , SiCl4 or CCl4 , a fluorine-based gas typified by CF4 , SF6 or NF3, or O2. . As an etchant, hydrofluoric acid, tetramethylammonium hydroxide aqueous solution (TMAH), or the like may be used as appropriate.

本発明のチューブは、内部に空間を有し、材料を吐出、吸引できるものである。吐出はピエゾ素子のような素子により行うことができ、吸引はポンプ等で行えばよい。従ってチューブに接続して、材料を供給する供給手段と材料貯蔵室、吸収した材料を廃棄するまで保管する貯蔵庫を有してもよい。The tube of the present invention has a space inside and can discharge and suck materials. The ejection can be performed by an element such as a piezo element, and the suction can be performed by a pump or the like. Therefore, it may have a supply means for supplying the material, a material storage chamber, and a storage for storing the absorbed material until it is discarded, connected to the tube.

さらに、本発明のチューブによって絶縁層に開口を形成した後、チューブ内部を通して液状の膜形成材料(例えば導電性を有する組成物)を開口に吐出し、導電層を形成してもよい。Furthermore, after forming an opening in the insulating layer by the tube of the present invention, a liquid film forming material (for example, a conductive composition) may be discharged into the opening through the tube to form the conductive layer.

開口が微細であると、液状の膜形成材料は表面張力の関係より開口に確実に充填されにくい場合があるが、本発明であると、開口に挿入されたチューブによって確実に開口に膜形成材料を充填でき、形状不良なく膜を形成することができる。If the opening is fine, the liquid film-forming material may not be reliably filled into the opening due to the surface tension. However, in the present invention, the film-forming material is reliably attached to the opening by the tube inserted into the opening. The film can be formed without a shape defect.

チューブより吐出されるエッチングガスは、チューブが耐えられるものであればエッチングする薄膜によって適宜選択することができる。例えば、幾層にも積層する多層配線などを作製する場合、何層にもわたって異なる薄膜に連続的な開口を形成する際に本発明を用いることができる。The etching gas discharged from the tube can be appropriately selected depending on the thin film to be etched as long as the tube can withstand. For example, in the case of producing a multilayer wiring or the like laminated in several layers, the present invention can be used in forming continuous openings in different thin films over several layers.

また開口の深さ方向はチューブを設ける時の力と、チューブが設置される膜の膜強度によって設定することができる。先端の尖った針のようなチューブを用いると、膜に挿入する時の抵抗を低くすることができる。The depth direction of the opening can be set by the force when the tube is provided and the film strength of the film on which the tube is installed. When a tube such as a needle with a sharp tip is used, the resistance when inserted into the membrane can be lowered.

導電層501、511、531、導電膜507、517、537は蒸着法、スパッタリング法、PVD法(Physical Vapor Deposition)、減圧CVD法(LPCVD法)、またはプラズマCVD法等のCVD法(Chemical Vapor Deposition)などを用いて形成することができる。また、構成物が所望のパターンに転写、または描写できる方法、例えば各種印刷法(スクリーン(孔版)印刷、オフセット(平版)印刷、凸版印刷やグラビア(凹版)印刷など所望なパターンで形成される方法)、ディスペンサ法、選択的な塗布法なども用いることができる。The

導電層501、511、531、導電膜507、517、537として、Ag、Au、Ni、Pt、Pd、Ir、Rh、Ta、W、Ti、Mo、Al、Cu、Cr、Coから選ばれたうち一種又は複数の元素、又は前記元素を主成分とする合金材料もしくは化合物材料で形成すればよい。また、リン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜や、AgPdCu合金を用いてもよい。また、単層構造でも複数層の構造でもよく、例えば、窒化タングステン膜とモリブデン(Mo)膜との2層構造としてもよいし、膜厚50nmのタングステン膜、膜厚500nmのアルミニウムとシリコンの合金(Al−Si)膜、膜厚30nmの窒化チタン膜を順次積層した3層構造としてもよい。また、3層構造とする場合、第1の導電膜のタングステンに代えて窒化タングステンを用いてもよいし、第2の導電膜のアルミニウムとシリコンの合金(Al−Si)膜に代えてアルミニウムとチタンの合金膜(Al−Ti)を用いてもよいし、第3の導電膜の窒化チタン膜に代えてチタン膜を用いてもよい。The

導電層501、511、531、導電膜507、517、537としてまた、インジウム錫酸化物(ITO)、酸化珪素を含むインジウム錫酸化物(ITSO)、酸化亜鉛(ZnO)、酸化亜鉛にガリウム(Ga)をドープした導電性材料、インジウム亜鉛酸化物(IZO(indium zinc oxide))を用いても良い。また、導電層の代わりに半導体層を形成する場合は、半導体材料を用いればよく、例えば、シリコン(珪素)、ゲルマニウム、シリコンゲルマニウム、ガリウム砒素、酸化モリブデン、酸化スズ、酸化ビスマス、酸化バナジウム、酸化ニッケル、酸化亜鉛、ヒ化ガリウム、窒化ガリウム、酸化インジウム、リン化インジウム、窒化インジウム、硫化カドミウム、テルル化カドミウム、チタン酸ストロンチウムなどの無機半導体材料を用いることができる。As the

絶縁層502、512、532は、スパッタリング法、PVD法(Physical Vapor Deposition)、減圧CVD法(LPCVD法)、またはプラズマCVD法等のCVD法(Chemical Vapor Deposition)などにより形成することができる。また、液滴吐出法や、印刷法(スクリーン印刷やオフセット印刷などパターンが形成される方法)、スピンコート法などの塗布法、ディッピング法、ディスペンサ法などを用いることもできる。The insulating

絶縁層502、512、532は、酸化珪素、窒化珪素、酸化窒化珪素、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、ダイアモンドライクカーボン(DLC)、窒素含有炭素(CN)、ポリシラザン、その他の無機絶縁性材料を含む物質から選ばれた材料で形成することができる。また、シロキサンを含む材料を用いてもよい。また、有機絶縁性材料を用いてもよく、有機材料としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト又はベンゾシクロブテンを用いることができる。また、オキサゾール樹脂を用いることもできる。The insulating

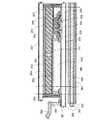

本発明を用いて半導体装置や表示装置を作製することができるが、図42に本発明のエッチング装置の例を示す。Although a semiconductor device and a display device can be manufactured using the present invention, FIG. 42 shows an example of an etching apparatus of the present invention.

図42に示すように、エッチング装置330は、チューブ301、位置制御手段302、吐出制御手段303、吐出材料貯蔵室304、吸引制御手段305、吸引材料貯蔵室306、コック307、コック308を有している。エッチング装置330は、成膜装置として機能することができる。チューブ301は位置制御手段302によって移動することができ、被処理膜に接するように配置される。吐出材料貯蔵室304とチューブ301とはコック307を介して接続されており、材料吐出時はコック307が開放され、吐出制御手段303によってチューブ301より材料が吐出される。一方、吸引材料貯蔵室306とチューブ301とはコック308を介して接続されており、材料吸引時はコック308が開放され、吸引制御手段305によってチューブ301より吐出した材料などが吸引され、吸引材料貯蔵室306へと送られる。吸引材料貯蔵室306に貯蔵された材料は廃棄、また再び吐出材料貯蔵室へ送られて再利用することができる。吐出制御手段303としてはピエゾ素子などを用いることができ、吸引制御手段305にはポンプなどを用いることができる。吐出、吸引の制御を的確に行うために真空計などを設けるとよい。As shown in FIG. 42, the etching apparatus 330 includes a tube 301, a position control unit 302, a discharge control unit 303, a discharge material storage chamber 304, a suction control unit 305, a suction material storage chamber 306, a cock 307, and a cock 308. ing. The etching apparatus 330 can function as a film formation apparatus. The tube 301 can be moved by the position control means 302 and is arranged so as to contact the film to be processed. The discharge material storage chamber 304 and the tube 301 are connected via a cock 307, the cock 307 is opened during material discharge, and the material is discharged from the tube 301 by the discharge control means 303. On the other hand, the suction material storage chamber 306 and the tube 301 are connected via a cock 308. When sucking the material, the cock 308 is opened, and the material discharged from the tube 301 is sucked by the suction control means 305. It is sent to the storage room 306. The material stored in the suction material storage chamber 306 can be discarded or sent again to the discharge material storage chamber for reuse. A piezo element or the like can be used as the discharge control means 303, and a pump or the like can be used as the suction control means 305. A vacuum gauge or the like may be provided in order to accurately control discharge and suction.

図42ではチューブによる吸引手段と吐出手段を備えた例を示したが、本発明はこれに限定されず、チューブによる吐出手段のみを備えてもよいし、チューブからの吐出、吸引を減圧下で行えるように減圧手段を設けてもよい。FIG. 42 shows an example in which a suction means and a discharge means using a tube are provided. However, the present invention is not limited to this, and only a discharge means using a tube may be provided, and discharge and suction from the tube may be performed under reduced pressure. A pressure reducing means may be provided so that it can be performed.

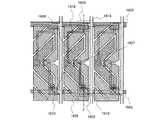

絶縁層に複数の開口を形成する場合、支持基板に複数のチューブを有するようなチューブ群を用いることができる。複数の開口を形成することのできるチューブ部の例を、図34を用いて説明する。In the case where a plurality of openings are formed in the insulating layer, a tube group having a plurality of tubes on the support substrate can be used. An example of a tube portion that can form a plurality of openings will be described with reference to FIG.

図34(A)はチューブ部を支持基板側より見た平面図であり、図34(B)(C)は図34(A)において線O−Pの断面図である。34A is a plan view of the tube portion viewed from the support substrate side, and FIGS. 34B and 34C are cross-sectional views taken along line OP in FIG. 34A.

図34(A)において、チューブ部353は支持基板350、チューブ351を有している。支持手段である支持基板350上に、開口形成領域と対応している場所に複数のチューブ351が設けられている。移動制御手段により移動可能な支持手段により、支持基板をチューブ351が被処理膜に接触するように移動し、被処理膜に対向してチューブ部353を設ければよい。移動制御手段により支持手段及びチューブは移動可能であり、チューブを被処理膜において膜厚方向上下、基板方向に上下左右に移動させ、被処理膜に対するチューブの位置を制御する。In FIG. 34A, the

チューブは、回路設計図面データから、絶縁層において所望の位置に開口を形成できるように設定すればよい。また、開口形成手段と被処理膜の形成される基板との位置関係は、予めチューブ部を支持する支持基板及び被処理膜の形成される基板にマーカを形成しておき位置合わせを行えばよい。The tube may be set so that an opening can be formed at a desired position in the insulating layer from the circuit design drawing data. Further, the positional relationship between the opening forming means and the substrate on which the film to be processed is formed may be adjusted by previously forming a marker on the support substrate that supports the tube portion and the substrate on which the film to be processed is formed. .

図34(B)において、チューブ351には制御素子354が設けられており、チューブ351の上下位置の移動を制御することができる。制御素子354としてはピエゾ素子などを用いることができる。図34(C)は制御素子によって選択的にチューブの位置が制御された例である。図34(C)において制御素子355aによりチューブ356aが移動し、チューブ356aの先端は選択されていない制御素子355bのチューブ356bの先端より距離d下に位置する。このように開口を形成する領域のみにチューブを選択的に基板上の被処理膜に配置して、所望の場所に開口を形成することができる。In FIG. 34B, a

絶縁層に開口を形成後、チューブの除去はチューブを物理的に引き抜く等して除去してもよいし、開口を有する絶縁層とエッチングの選択比が高い条件で、チューブをエッチング(ドライエッチング又はウエットエッチング)によって化学的に除去してもよい。絶縁層と導電層との密着強度が弱い場合は、エッチングによってチューブを除去するのが好ましい。また、チューブを形状変化することなく絶縁層より物理的手段により除去すると、除去作業が容易でありチューブを繰り返し再利用することができるため、コストを削減することができるという利点がある。After forming the opening in the insulating layer, the tube may be removed by physically pulling out the tube, or the tube is etched (dry etching or dry etching) under a condition where the etching ratio between the insulating layer having the opening and the etching is high. It may be chemically removed by wet etching. When the adhesion strength between the insulating layer and the conductive layer is weak, it is preferable to remove the tube by etching. Further, when the tube is removed from the insulating layer by physical means without changing its shape, there is an advantage that the removal work is easy and the tube can be reused repeatedly, thereby reducing the cost.

チューブはスパッタリング法、真空蒸着法、PVD法(Physical Vapor Deposition)、減圧CVD法(LPCVD法)、またはプラズマCVD法等のCVD法(Chemical Vapor Deposition)により薄膜を成膜した後、所望の形状にエッチングして形成することができる。また、選択的にパターンを形成できる液滴吐出法や、パターンが転写または描写できる印刷法(スクリーン印刷やオフセット印刷などパターンが形成される方法)、その他スピンコート法などの塗布法、ディッピング法、ディスペンサ法などを用いることもできる。また、インプリント技術、ナノメートルサイズの立体構造物を転写技術で形成できるナノインプリント技術を用いることもができる。インプリント、ナノインプリントは、フォトリソグラフィー工程を用いずに微細な立体構造物を形成できる技術である。The tube is formed into a desired shape after a thin film is formed by a sputtering method, a vacuum deposition method, a PVD method (Physical Vapor Deposition), a low pressure CVD method (LPCVD method), or a CVD method (Chemical Vapor Deposition) such as a plasma CVD method. It can be formed by etching. In addition, a droplet discharge method that can selectively form a pattern, a printing method that can transfer or depict a pattern (a method that forms a pattern such as screen printing or offset printing), other coating methods such as spin coating, dipping method, A dispenser method or the like can also be used. In addition, an imprint technique and a nanoimprint technique that can form a nanometer-sized three-dimensional structure by a transfer technique can also be used. Imprinting and nanoimprinting are techniques that can form fine three-dimensional structures without using a photolithography process.

無機材料でも有機材料又は珪素と酸素との結合で骨格構造が形成された材料で形成してもよい。絶縁膜の成膜を遮蔽する手段であるので、金属などの導電材料でも、樹脂などの絶縁材料でもよい。また、繊維などを用いることもできる。装置に設置することを考慮すると、比較的軽量で加工の容易なものが好ましい。微細な開口を形成する場合は、カーボンナノチューブなどの、ナノチューブ材料を用いることもできる。カーボンナノチューブなどの極細炭素繊維は、グラファイトナノファイバ、カーボンナノファイバ、チューブ状グラファイト、カーボンナノコーン、又はコーン状グラファイトなども用いることができる。An inorganic material or an organic material or a material in which a skeleton structure is formed by a bond of silicon and oxygen may be used. Since it is a means for shielding the formation of the insulating film, it may be a conductive material such as metal or an insulating material such as resin. Moreover, a fiber etc. can also be used. Considering the installation in the apparatus, a relatively light weight and easy processing is preferable. In the case of forming a fine opening, a nanotube material such as a carbon nanotube can be used. As the ultrafine carbon fiber such as carbon nanotube, graphite nanofiber, carbon nanofiber, tube-like graphite, carbon nanocone, cone-like graphite, or the like can also be used.

チューブの材料としては、酸化珪素、窒化珪素、酸化窒化珪素、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、ダイアモンドライクカーボン(DLC)、窒素含有炭素(CN)、ポリシラザン、その他の無機絶縁性材料を含む物質から選ばれた材料で形成することができる。また、シロキサンを含む材料を用いてもよい。また、エポキシ樹脂、フェノール樹脂、ノボラック樹脂、アクリル樹脂、メラミン樹脂、ウレタン樹脂、ベンゾシクロブテン、パリレン、フッ化アリーレンエーテル、ポリイミドなどの有機材料、シロキサン結合を有する樹脂などを用いることができる。Tube materials include silicon oxide, silicon nitride, silicon oxynitride, aluminum oxide, aluminum nitride, aluminum oxynitride, diamond-like carbon (DLC), nitrogen-containing carbon (CN), polysilazane, and other inorganic insulating materials. It can be formed of a material selected from substances. Further, a material containing siloxane may be used. Alternatively, an epoxy resin, a phenol resin, a novolac resin, an acrylic resin, a melamine resin, a urethane resin, benzocyclobutene, parylene, fluorinated arylene ether, a polyimide resin, a resin having a siloxane bond, or the like can be used.

開口を形成した後、液体で開口付近に残存する導電性材料や絶縁性材料(導電層又は絶縁層の除去された部分の残存物)を洗浄し、残存物を除去してもよい。この場合、洗浄に水などの無反応物質を用いてもよいし、絶縁層と反応する(溶解する)エッチング液などの薬液を用いてもよい。エッチング液を用いると開口がオーバーエッチングされ、ゴミ等が除去され表面がより平坦化される。また開口を広げることもできる。After the opening is formed, the conductive material or insulating material remaining in the vicinity of the opening with a liquid (residue of the removed portion of the conductive layer or the insulating layer) may be washed to remove the residue. In this case, an unreacted substance such as water may be used for cleaning, or a chemical solution such as an etching solution that reacts (dissolves) with the insulating layer may be used. When an etching solution is used, the opening is over-etched, dust and the like are removed, and the surface is flattened. The opening can also be widened.

このように複雑なフォトリソグラフィ工程、レジストマスク層の形成を行うことなく、導電層と導電層(導電膜)とを電気的に接続する開口(コンタクトホール)を絶縁層に形成することができる。Thus, an opening (contact hole) for electrically connecting the conductive layer and the conductive layer (conductive film) can be formed in the insulating layer without performing a complicated photolithography process and formation of a resist mask layer.

従って、本実施の形態によれば、絶縁層にマスクを形成することなくコンタクトホールを形成することができるので、工程を簡略化することができる。また、フォトレジスト等を塗布して露光及び現像する必要がないので、加工に必要な原材料コストを削減することができる。さらに、コンタクトホールを確実に形成することができるので、製造歩留まりの向上を図ることができる。Therefore, according to this embodiment mode, a contact hole can be formed without forming a mask in the insulating layer, so that the process can be simplified. In addition, since it is not necessary to apply a photoresist or the like for exposure and development, it is possible to reduce raw material costs required for processing. Furthermore, since the contact hole can be reliably formed, the manufacturing yield can be improved.

(実施の形態2)

本実施の形態では、確実により簡略化した工程で低コストに作製することを目的とした積層構造のコンタクトホールを形成する方法について説明する。詳しくは実施の形態1において、コンタクトホールが複数の積層する膜に亘って形成される例である。従って、同一部分又は同様な機能を有する部分は実施の形態1と同様な材料及び方法を用いればよく、その繰り返しの説明は省略する。(Embodiment 2)

In this embodiment mode, a method for forming a contact hole having a stacked structure for the purpose of manufacturing at a low cost through a process that is surely simplified will be described. Specifically, in Embodiment 1, the contact hole is formed over a plurality of stacked films. Accordingly, the same portion or a portion having a similar function may be formed using the same material and method as those in Embodiment Mode 1, and the description thereof is not repeated.

チューブを絶縁層に挿入し、一部埋め込むように配置し、物理的力によって絶縁層に第1の開口を形成し、その後、吐出口からエッチングガスを噴出してさらに絶縁層を選択的に除去し、第2の開口を形成することができる。つまりチューブの物理的な力で第1の開口を形成し、チューブより吐出される処理剤(エッチングガス又はエッチング液)の化学的な力によって第2の開口を形成してもよい。先にチューブより処理剤(エッチングガス又はエッチング液)を吐出して、第1の開口を形成し、チューブを絶縁層に挿入して第2の開口を形成してもよいし、エッチングガスを吐出しながら同時にチューブを絶縁層に挿入して開口を形成してもよい。Insert the tube into the insulating layer and place it so as to embed part of it, form a first opening in the insulating layer by physical force, and then eject the etching gas from the discharge port to further remove the insulating layer selectively Then, the second opening can be formed. That is, the first opening may be formed by a physical force of the tube, and the second opening may be formed by a chemical force of a processing agent (etching gas or etching solution) discharged from the tube. First, the processing agent (etching gas or etching solution) is discharged from the tube to form the first opening, and the tube may be inserted into the insulating layer to form the second opening, or the etching gas is discharged. At the same time, the tube may be inserted into the insulating layer to form the opening.

幾層にも積層する多層配線などを作製する場合、何層にもわたって異なる薄膜に連続的な開口を形成する際に本発明を用いることができる。In the case of producing a multilayer wiring or the like laminated in several layers, the present invention can be used when forming continuous openings in different thin films over several layers.

さらに、本発明のチューブによって絶縁層に開口を形成した後、チューブ内部を通してチューブより液状の膜形成材料(例えば導電性を有する組成物)を開口に吐出し、導電層を形成してもよい。開口が微細であると、液状の膜形成材料は表面張力の関係より開口に確実に充填されにくい場合があるが、本発明であると、開口に挿入されたチューブによって確実に開口に膜形成材料を充填でき、形状不良なく膜を形成することができる。Furthermore, after forming an opening in the insulating layer with the tube of the present invention, a liquid film-forming material (for example, a conductive composition) may be discharged from the tube into the opening through the tube to form the conductive layer. If the opening is fine, the liquid film-forming material may not be reliably filled into the opening due to the surface tension. However, in the present invention, the film-forming material is reliably attached to the opening by the tube inserted into the opening. The film can be formed without a shape defect.

開口の形状はチューブの形状を反映するため、所望の形状が得られるようにチューブを設定すればよい。チューブは柱状(角柱、円柱、三角柱など)、針状などを用いることができる。また開口の深さ方向はチューブを設ける時の力と、チューブが設置される被処理膜の膜強度によって設定することができる。また、エッチング時間などのエッチング条件を設定することによっても膜厚方向の深さを選択できる。先端の尖った針状のチューブを用いて、導電層に一部埋め込むようにチューブを設置すると、導電層に凹部を有する開口を形成することができる。また開口形成後、開口を有する絶縁層をマスクとして開口底面に露出された導電層をエッチングによって除去してもよい。Since the shape of the opening reflects the shape of the tube, the tube may be set so as to obtain a desired shape. The tube may have a columnar shape (such as a prism, a cylinder, or a triangular column), a needle shape, or the like. The depth direction of the opening can be set by the force when the tube is provided and the film strength of the film to be processed on which the tube is installed. The depth in the film thickness direction can also be selected by setting etching conditions such as etching time. When a tube is installed so as to be partially embedded in the conductive layer using a needle-like tube with a sharp tip, an opening having a recess can be formed in the conductive layer. Further, after the opening is formed, the conductive layer exposed on the bottom surface of the opening may be removed by etching using the insulating layer having the opening as a mask.

本発明によってフォトリソグラフィ工程を用いることなく選択的に開口を有する絶縁層を形成することができるので工程及び材料を削減することができる。According to the present invention, since an insulating layer having an opening can be formed selectively without using a photolithography process, the number of processes and materials can be reduced.

積層体に連続した開口を形成する例を図4に示す。図4(A)において、基板700上に、導電層701、第1の絶縁層708及び第2の絶縁層702が形成されている。次にチューブ703を第2の絶縁層702に挿入することによって物理的に第2の絶縁層702に第1の開口704を形成する。図4(B)の断面図においては、第2の絶縁層は、第2の絶縁層706aと第2の絶縁層706bとに分離される。チューブ703の吐出口の大きさによっては、チューブ703内部に第2の絶縁層702の一部が入る場合は、さらにチューブより処理剤(エッチングガス又はエッチング液)を吐出し、内部に進入した第2の絶縁層702を除去すればよい。An example of forming continuous openings in the laminate is shown in FIG. 4A, a

チューブ703からエッチングガス709を吐出してさらに第1の絶縁層を選択的に除去し、第1の絶縁層及び第2の絶縁層に連続した第2の開口705を形成することができる。図4(C)の断面図においては、第1の絶縁層は、第1の絶縁層790aと第1の絶縁層790bとに分離される。An

開口705は、チューブの形状を反映するため、側面に段差を有する形状となる。導電層701が露出された第2の開口705に導電膜707を形成し、導電層701と導電膜707とを電気的に接続することができる(図4(D)参照。)。The

つまりチューブの物理的な力で第1の開口を形成し、チューブより吐出(噴出)されるエッチングガスの化学的な力によって第2の開口を形成してもよい。先にチューブよりエッチングガスを吐出して、第1の開口を形成し、チューブを絶縁層に挿入して第2の開口を形成してもよいし、エッチングガスを吐出しながら同時にチューブを絶縁層に挿入して開口を形成してもよい。That is, the first opening may be formed by the physical force of the tube, and the second opening may be formed by the chemical force of the etching gas discharged (ejected) from the tube. The etching gas may be discharged from the tube first to form the first opening, and the tube may be inserted into the insulating layer to form the second opening. An opening may be formed by being inserted into the.

第2の絶縁層がチューブより物理的強度が弱い場合、図4のように開口を形成することができる。第2の絶縁層をスピンコートなどのウェットプロセスを用いて形成する場合、第2の絶縁層が硬化する前に開口を形成してもよい。勿論第2の絶縁層に加熱処理などを行い物理的強度を低下させて、チューブを挿入してもよい。When the second insulating layer has a physical strength weaker than that of the tube, an opening can be formed as shown in FIG. In the case where the second insulating layer is formed using a wet process such as spin coating, an opening may be formed before the second insulating layer is cured. Of course, the second insulating layer may be subjected to heat treatment or the like to reduce the physical strength, and the tube may be inserted.

図5に、図4においてチューブの先端が細い円錐形状の例を示す。基板730上に、導電層731、第1の絶縁層738及び第2の絶縁層732が形成されている。次にチューブ733を第2の絶縁層732に挿入することによって物理的に第2の絶縁層732に第1の開口734を形成する。図5(B)の断面図においては、第2の絶縁層は、第2の絶縁層736aと第2の絶縁層736bとに分離される。FIG. 5 shows an example in which the tip of the tube in FIG. A

チューブ733の吐出口からエッチング液739を吐出してさらに第1の絶縁層738を選択的に除去し、第1の絶縁層及び第2の絶縁層に連続した第2の開口735を形成することができる。図5(C)の断面図においては、第1の絶縁層は、第1の絶縁層791aと第1の絶縁層791bとに分離される。The

開口735は、チューブの形状を反映するため、側面に段差を有する形状となる。導電層731が露出された第2の開口735に導電膜737を形成し、導電層731と導電膜737とを電気的に接続することができる(図5(D)参照。)。チューブは断面形状が導電層に向かって先端が細くなる側辺にテーパーを有する形状である。開口735は、チューブ733の形状を反映し、開口の側辺がテーパーを有する形状となっている。Since the

さらに、本発明のチューブによって絶縁層に開口を形成した後、チューブより液状の膜形成材料(例えば導電性を有する組成物)を開口に吐出し、導電層を形成してもよい。図6(A)は、図5(C)と対応しており、基板750上に導電層751が形成され、チューブ753により第1の絶縁層792a、792b、第2の絶縁層756a、756bが形成されている。チューブ753内は、第1の絶縁層材料が溶解したエッチング液759を有している。Furthermore, after forming an opening in the insulating layer with the tube of the present invention, a liquid film forming material (for example, a conductive composition) may be discharged from the tube into the opening to form a conductive layer. FIG. 6A corresponds to FIG. 5C, in which a

第1の絶縁層材料が溶解したエッチング液759を吸引により除去し、開口755を形成する(図6(B)参照。)。チューブ753より液状の導電性を有する組成物749を開口755に吐出し、導電層757を形成する(図6(C)(D)参照。)よって、導電層751と導電層757とを電気的に接続することができる。The

開口が微細であると、液状の膜形成材料は表面張力の関係より開口に確実に充填されにくい場合があるが、本発明であると、開口に挿入されたチューブによって確実に開口に膜形成材料を充填でき、形状不良なく膜を形成することができる。If the opening is fine, the liquid film-forming material may not be reliably filled into the opening due to the surface tension. However, in the present invention, the film-forming material is reliably attached to the opening by the tube inserted into the opening. The film can be formed without a shape defect.

膜形成材料を含む組成物は、形成する膜によって適宜設定すればよく、導電膜を形成する場合は、導電性材料を含む組成物とすればよい。また絶縁膜を形成する場合は、同様に絶縁性材料を含む組成物、半導体膜を形成する場合は、半導体材料を含む組成物とすればよい。また、膜形成材料を含む組成物はフッ素を有する界面活性剤を含んでもよい。The composition containing the film forming material may be set as appropriate depending on the film to be formed. When the conductive film is formed, the composition containing the conductive material may be used. Similarly, when an insulating film is formed, a composition containing an insulating material may be used. When a semiconductor film is formed, a composition containing a semiconductor material may be used. Moreover, the composition containing the film forming material may contain a surfactant having fluorine.

膜として導電膜を形成する場合、吐出する組成物は、導電性材料を溶媒に溶解又は分散させたものを用いる。導電性材料とは、Ag、Au、Cu、Ni、Pt、Pd、Ir、Rh、W、Al等の一種又は複数種の金属の微粒子又は分散性ナノ粒子に相当する。また前記導電性材料には、Cd、Znの金属硫化物、Fe、Ti、Ge、Si、Zr、Baなどの酸化物、ハロゲン化銀の一種又は複数種の微粒子又は分散性ナノ粒子を混合してもよい。また、導電性材料として、透明導電膜として用いられるインジウム錫酸化物(ITO)、酸化珪素を含むインジウム錫酸化物(ITSO)、有機インジウム、有機スズ、酸化亜鉛、窒化チタン等を用いてもよい。導電性材料は、単一元素、又は複数種の元素の粒子を混合して用いることができる。但し、吐出する組成物は、比抵抗値を考慮して、金、銀、銅のいずれかの材料を溶媒に溶解又は分散させたものを用いることが好適であり、より好適には、低抵抗な銀、銅を用いるとよい。但し、銀、銅を用いる場合には、不純物対策のため、合わせてバリア膜を設けるとよい。バリア膜としては、窒化珪素膜やニッケルボロン(NiB)を用いることができる。In the case where a conductive film is formed as a film, a discharged composition is obtained by dissolving or dispersing a conductive material in a solvent. The conductive material corresponds to fine particles or dispersible nanoparticles of one or more kinds of metals such as Ag, Au, Cu, Ni, Pt, Pd, Ir, Rh, W, and Al. Further, the conductive material is mixed with metal sulfides of Cd and Zn, oxides such as Fe, Ti, Ge, Si, Zr, and Ba, one or more kinds of fine particles of silver halide, or dispersible nanoparticles. May be. As the conductive material, indium tin oxide (ITO) used as a transparent conductive film, indium tin oxide containing silicon oxide (ITSO), organic indium, organic tin, zinc oxide, titanium nitride, or the like may be used. . As the conductive material, particles of a single element or a plurality of kinds of elements can be mixed and used. However, it is preferable to use a composition in which any one of gold, silver, and copper is dissolved or dispersed in a solvent in consideration of a specific resistance value, and more preferably a low resistance composition. It is recommended to use silver or copper. However, when silver or copper is used, a barrier film may be provided as a countermeasure against impurities. As the barrier film, a silicon nitride film or nickel boron (NiB) can be used.

吐出する組成物は、導電性材料(絶縁性材料)を溶媒に溶解又は分散させたものであるが、他にも分散剤や、バインダーと呼ばれる熱硬化性樹脂が含まれている。特にバインダーに関しては、焼成時にクラックや不均一な焼きムラが発生するのを防止する働きを持つ。よって、形成される導電層には、有機材料が含まれることがある。含まれる有機材料は、加熱温度、雰囲気、時間により異なる。この有機材料は、金属粒子のバインダー、溶媒、分散剤、及び被覆剤として機能する有機樹脂などであり、代表的には、ポリイミド、アクリル、ノボラック樹脂、メラミン樹脂、フェノール樹脂、エポキシ樹脂、シリコーン樹脂、フラン樹脂、ジアリルフタレート樹脂等の有機樹脂が挙げられる。The composition to be discharged is one obtained by dissolving or dispersing a conductive material (insulating material) in a solvent, but additionally contains a dispersant and a thermosetting resin called a binder. In particular, the binder has a function of preventing occurrence of cracks and uneven baking during firing. Thus, the formed conductive layer may contain an organic material. The organic material contained varies depending on the heating temperature, atmosphere, and time. This organic material is a binder of metal particles, a solvent, a dispersant, an organic resin that functions as a coating agent, etc., typically polyimide, acrylic, novolac resin, melamine resin, phenol resin, epoxy resin, silicone resin And organic resins such as furan resin and diallyl phthalate resin.

また、導電性材料の周りに他の導電性材料がコーティングされ、複数の層になっている粒子でも良い。例えば、銅の周りにニッケルボロン(NiB)がコーティングされ、その周囲に銀がコーティングされている3層構造の粒子などを用いても良い。溶媒は、酢酸ブチル、酢酸エチル等のエステル類、イソプロピルアルコール、エチルアルコール等のアルコール類、メチルエチルケトン、アセトン等の有機溶剤等、又は水を用いる。組成物の粘度は20mPa・s以下が好適であり、これは、吐出時に乾燥が起こることを防止、又は吐出口から組成物を円滑に吐出できるようにするためである。また、組成物の表面張力は、40mN/m以下が好適である。但し、用いる溶媒や、用途に合わせて、組成物の粘度等は適宜調整するとよい。一例として、ITOや、有機インジウム、有機スズを溶媒に溶解又は分散させた組成物の粘度は5〜20mPa・s、銀を溶媒に溶解又は分散させた組成物の粘度は5〜20mPa・s、金を溶媒に溶解又は分散させた組成物の粘度は5〜20mPa・sに設定するとよい。Alternatively, particles in which a conductive material is coated with another conductive material to form a plurality of layers may be used. For example, particles having a three-layer structure in which nickel boron (NiB) is coated around copper and silver is coated around it may be used. As the solvent, esters such as butyl acetate and ethyl acetate, alcohols such as isopropyl alcohol and ethyl alcohol, organic solvents such as methyl ethyl ketone and acetone, and water are used. The viscosity of the composition is preferably 20 mPa · s or less, in order to prevent drying from occurring during discharge or to smoothly discharge the composition from the discharge port. The surface tension of the composition is preferably 40 mN / m or less. However, the viscosity and the like of the composition may be appropriately adjusted according to the solvent to be used and the application. As an example, the viscosity of a composition in which ITO, organic indium, or organic tin is dissolved or dispersed in a solvent is 5 to 20 mPa · s, the viscosity of a composition in which silver is dissolved or dispersed in a solvent is 5 to 20 mPa · s, The viscosity of the composition in which gold is dissolved or dispersed in a solvent is preferably set to 5 to 20 mPa · s.

膜として絶縁層を形成する場合は、エポキシ樹脂、フェノール樹脂、ノボラック樹脂、アクリル樹脂、メラミン樹脂、ウレタン樹脂、ベンゾシクロブテン、パリレン、フッ化アリーレンエーテル、ポリイミドなどの有機材料、シロキサン結合を有する樹脂を用いることができる。いずれの材料を用いるとしても、その表面張力と粘度は、溶媒の濃度を調整する、界面活性剤等を加えるなどを行い適宜調整する。When an insulating layer is formed as a film, an epoxy resin, a phenol resin, a novolac resin, an acrylic resin, a melamine resin, a urethane resin, an organic material such as benzocyclobutene, parylene, fluorinated arylene ether, a resin having a siloxane bond Can be used. Regardless of which material is used, its surface tension and viscosity are appropriately adjusted by adjusting the concentration of the solvent, adding a surfactant or the like.

チューブの径や所望のパターン形状などに依存するが、チューブの目詰まり防止や高精細なパターンの作製のため、導電体の粒子の径はなるべく小さい方が好ましく、好適には粒径0.1μm以下が好ましい。組成物は、電解法、アトマイズ法又は湿式還元法等の各種方法で形成されるものであり、その粒子サイズは、一般的に約0.01〜10μmである。但し、ガス中蒸発法で形成すると、分散剤で保護されたナノ粒子は約7nmと微細であり、またこのナノ粒子は、被覆剤を用いて各粒子の表面を覆うと、溶剤中に凝集がなく、室温で安定に分散し、液体とほぼ同じ挙動を示す。従って、被覆剤を用いることが好ましい。Although depending on the diameter of the tube and the desired pattern shape, the diameter of the conductor particles is preferably as small as possible to prevent clogging of the tube and the production of a high-definition pattern. The following is preferred. The composition is formed by various methods such as an electrolytic method, an atomizing method, or a wet reduction method, and its particle size is generally about 0.01 to 10 μm. However, when formed by a gas evaporation method, the nanoparticles protected by the dispersant are as fine as about 7 nm, and these nanoparticles are aggregated in the solvent when the surface of each particle is covered with a coating agent. And stably disperse at room temperature and shows almost the same behavior as liquid. Therefore, it is preferable to use a coating agent.

また、組成物を吐出する工程は、減圧下で行ってもよい。吐出時に基板を加熱しておいてもよい。組成物を吐出後、乾燥と焼成の一方又は両方の工程を行う。乾燥と焼成の工程は、両工程とも加熱処理の工程であるが、例えば、乾燥は100度(℃)で3分間、焼成は200〜550度(℃)で15分間〜60分間で行うもので、その目的、温度と時間が異なるものである。乾燥の工程、焼成の工程は、常圧下又は減圧下で、レーザ光の照射や瞬間熱アニール、加熱炉などにより行う。なお、この加熱処理を行うタイミング、加熱処理の回数は特に限定されない。乾燥と焼成の工程を良好に行うためには、そのときの温度は、基板の材質及び組成物の性質に依存するが、一般的には室温〜800度(℃)(好ましくは100〜550度(℃))とする。本工程により、組成物中の溶媒の揮発、又は化学的に分散剤を除去するとともに、周囲の樹脂が硬化収縮することで、ナノ粒子間を接触させ、融合と融着を加速する。The step of discharging the composition may be performed under reduced pressure. The substrate may be heated at the time of discharge. After discharging the composition, one or both steps of drying and baking are performed. The drying and firing steps are both heat treatment steps. For example, drying is performed at 100 degrees (C) for 3 minutes, and firing is performed at 200 to 550 degrees (C) for 15 minutes to 60 minutes. Its purpose, temperature and time are different. The drying process and the firing process are performed under normal pressure or reduced pressure by laser light irradiation, rapid thermal annealing, a heating furnace, or the like. Note that the timing of performing this heat treatment and the number of heat treatments are not particularly limited. In order to perform the drying and firing steps satisfactorily, the temperature at that time depends on the material of the substrate and the properties of the composition, but is generally room temperature to 800 ° C. (preferably 100 to 550 ° C.). (° C)). By this step, the solvent in the composition is volatilized or the dispersant is chemically removed, and the surrounding resin is cured and contracted to bring the nanoparticles into contact with each other, thereby accelerating fusion and fusion.

レーザ光の照射は、連続発振またはパルス発振の気体レーザ又は固体レーザを用いれば良い。前者の気体レーザとしては、エキシマレーザ、Arレーザ等が挙げられ、後者の固体レーザとしては、Cr、Nd等がドーピングされたYAG、YVO4、GdVO4等の結晶を使ったレーザ等が挙げられる。なお、レーザ光の吸収率の関係から、連続発振のレーザを用いることが好ましい。また、パルス発振と連続発振を組み合わせたレーザ照射方法を用いてもよい。但し、基板の耐熱性に依っては、レーザ光の照射による加熱処理は、該基板を破壊しないように、数マイクロ秒から数十秒の間で瞬間的に行うとよい。瞬間熱アニール(RTA)は、不活性ガスの雰囲気下で、紫外光乃至赤外光を照射する赤外ランプやハロゲンランプなどを用いて、急激に温度を上昇させ、数分〜数マイクロ秒の間で瞬間的に熱を加えて行う。この処理は瞬間的に行うために、実質的に最表面の薄膜のみを加熱することができ、下層の膜には影響を与えない。つまり、プラスチック基板等の耐熱性が弱い基板にも影響を与えない。For the laser light irradiation, a continuous wave or pulsed gas laser or solid-state laser may be used. Examples of the former gas laser include an excimer laser and an Ar laser, and examples of the latter solid-state laser include a laser using a crystal such as YAG, YVO4 or GdVO4 doped with Cr, Nd, or the like. . Note that it is preferable to use a continuous wave laser because of the absorption rate of the laser light. Further, a laser irradiation method combining pulse oscillation and continuous oscillation may be used. However, depending on the heat resistance of the substrate, the heat treatment by laser light irradiation may be performed instantaneously within a few microseconds to several tens of seconds so as not to destroy the substrate. Instantaneous thermal annealing (RTA) uses an infrared lamp or a halogen lamp that irradiates ultraviolet light or infrared light in an inert gas atmosphere, and rapidly raises the temperature for several minutes to several microseconds. This is done by applying heat instantaneously. Since this treatment is performed instantaneously, only the outermost thin film can be heated substantially without affecting the lower layer film. That is, it does not affect a substrate having low heat resistance such as a plastic substrate.

また、導電層などを組成物を吐出し形成した後、その平坦性を高めるために表面を圧力によってプレスして平坦化してもよい。プレスの方法としては、ローラー状のものを表面に走査する、又は平坦な板状な物で表面を垂直にプレスするなどにより、表面の凹凸を平坦化することができる。プレスする時に、加熱工程を行っても良い。また溶剤等によって表面を軟化、または融解させエアナイフで表面の凹凸部を除去しても良い。また、CMP法を用いて研磨しても良い。In addition, after the conductive layer or the like is formed by discharging a composition, the surface may be flattened by pressing with a pressure in order to enhance the flatness. As a pressing method, surface irregularities can be flattened by scanning a roller-like object on the surface or pressing the surface vertically with a flat plate-like object. A heating step may be performed when pressing. Alternatively, the surface may be softened or melted with a solvent or the like, and the surface irregularities may be removed with an air knife. Further, polishing may be performed using a CMP method.

このように導電性材料、又は絶縁性材料を含む組成物を吐出し、焼成することによって形成された導電層(または絶縁層)においては、スパッタ法などで形成した導電層(または絶縁層)が、多くは柱状構造を示すのに対し、多くの粒界を有する多結晶状態を示すことが多い。In such a conductive layer (or insulating layer) formed by discharging and baking a composition containing a conductive material or an insulating material, a conductive layer (or insulating layer) formed by a sputtering method or the like is used. Many exhibit a columnar structure, but often exhibit a polycrystalline state having many grain boundaries.