JP5202372B2 - 成膜装置のメタル汚染低減方法、半導体装置の製造方法、記憶媒体及び成膜装置 - Google Patents

成膜装置のメタル汚染低減方法、半導体装置の製造方法、記憶媒体及び成膜装置Download PDFInfo

- Publication number

- JP5202372B2 JP5202372B2JP2009027098AJP2009027098AJP5202372B2JP 5202372 B2JP5202372 B2JP 5202372B2JP 2009027098 AJP2009027098 AJP 2009027098AJP 2009027098 AJP2009027098 AJP 2009027098AJP 5202372 B2JP5202372 B2JP 5202372B2

- Authority

- JP

- Japan

- Prior art keywords

- processing container

- forming apparatus

- film forming

- film

- silicon nitride

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000000034methodMethods0.000titleclaimsdescription82

- 229910052751metalInorganic materials0.000titleclaimsdescription51

- 239000002184metalSubstances0.000titleclaimsdescription51

- 239000004065semiconductorSubstances0.000titleclaimsdescription44

- 238000011109contaminationMethods0.000titleclaimsdescription35

- 238000004519manufacturing processMethods0.000titleclaimsdescription17

- 238000003860storageMethods0.000titleclaimsdescription14

- 230000009467reductionEffects0.000titleclaimsdescription12

- 239000010408filmSubstances0.000claimsdescription201

- 239000007789gasSubstances0.000claimsdescription144

- 238000012545processingMethods0.000claimsdescription133

- 229910052581Si3N4Inorganic materials0.000claimsdescription60

- HQVNEWCFYHHQES-UHFFFAOYSA-Nsilicon nitrideChemical compoundN12[Si]34N5[Si]62N3[Si]51N64HQVNEWCFYHHQES-UHFFFAOYSA-N0.000claimsdescription60

- 238000004140cleaningMethods0.000claimsdescription43

- 230000008569processEffects0.000claimsdescription37

- QVGXLLKOCUKJST-UHFFFAOYSA-Natomic oxygenChemical compound[O]QVGXLLKOCUKJST-UHFFFAOYSA-N0.000claimsdescription29

- 239000001301oxygenSubstances0.000claimsdescription29

- 229910052760oxygenInorganic materials0.000claimsdescription29

- IJGRMHOSHXDMSA-UHFFFAOYSA-NAtomic nitrogenChemical compoundN#NIJGRMHOSHXDMSA-UHFFFAOYSA-N0.000claimsdescription23

- 239000010409thin filmSubstances0.000claimsdescription22

- 238000010438heat treatmentMethods0.000claimsdescription20

- MROCJMGDEKINLD-UHFFFAOYSA-NdichlorosilaneChemical compoundCl[SiH2]ClMROCJMGDEKINLD-UHFFFAOYSA-N0.000claimsdescription14

- 238000000576coating methodMethods0.000claimsdescription11

- 239000011248coating agentSubstances0.000claimsdescription10

- 229910052757nitrogenInorganic materials0.000claimsdescription10

- 239000002243precursorSubstances0.000claimsdescription7

- 229910052736halogenInorganic materials0.000claimsdescription3

- 150000002367halogensChemical class0.000claimsdescription3

- 238000006243chemical reactionMethods0.000claimsdescription2

- 150000002366halogen compoundsChemical class0.000claimsdescription2

- LXEXBJXDGVGRAR-UHFFFAOYSA-Ntrichloro(trichlorosilyl)silaneChemical compoundCl[Si](Cl)(Cl)[Si](Cl)(Cl)ClLXEXBJXDGVGRAR-UHFFFAOYSA-N0.000claimsdescription2

- 101100441092Danio rerio crlf3 geneProteins0.000claims1

- 235000012431wafersNutrition0.000description47

- XUIMIQQOPSSXEZ-UHFFFAOYSA-NSiliconChemical compound[Si]XUIMIQQOPSSXEZ-UHFFFAOYSA-N0.000description23

- 229910052710siliconInorganic materials0.000description23

- 239000010703siliconSubstances0.000description23

- 230000007246mechanismEffects0.000description20

- VYPSYNLAJGMNEJ-UHFFFAOYSA-Nsilicon dioxideInorganic materialsO=[Si]=OVYPSYNLAJGMNEJ-UHFFFAOYSA-N0.000description18

- 238000005755formation reactionMethods0.000description14

- 238000010926purgeMethods0.000description13

- 230000015572biosynthetic processEffects0.000description12

- 239000010453quartzSubstances0.000description10

- 238000005229chemical vapour depositionMethods0.000description9

- 239000006185dispersionSubstances0.000description9

- QJGQUHMNIGDVPM-UHFFFAOYSA-Nnitrogen groupChemical group[N]QJGQUHMNIGDVPM-UHFFFAOYSA-N0.000description9

- 238000000151depositionMethods0.000description8

- 229910052814silicon oxideInorganic materials0.000description8

- 229910004298SiO 2Inorganic materials0.000description5

- 230000000694effectsEffects0.000description5

- 239000003795chemical substances by applicationSubstances0.000description4

- 230000008021depositionEffects0.000description4

- 239000000428dustSubstances0.000description4

- 230000001965increasing effectEffects0.000description4

- 238000005121nitridingMethods0.000description4

- 239000002245particleSubstances0.000description4

- 238000013459approachMethods0.000description3

- 239000007800oxidant agentSubstances0.000description3

- 238000007789sealingMethods0.000description3

- 239000000758substrateSubstances0.000description3

- QGZKDVFQNNGYKY-UHFFFAOYSA-NAmmoniaChemical compoundNQGZKDVFQNNGYKY-UHFFFAOYSA-N0.000description2

- CBENFWSGALASAD-UHFFFAOYSA-NOzoneChemical compound[O-][O+]=OCBENFWSGALASAD-UHFFFAOYSA-N0.000description2

- 239000012528membraneSubstances0.000description2

- 229910001220stainless steelInorganic materials0.000description2

- 239000010935stainless steelSubstances0.000description2

- UFHFLCQGNIYNRP-UHFFFAOYSA-NHydrogenChemical compound[H][H]UFHFLCQGNIYNRP-UHFFFAOYSA-N0.000description1

- QCWXUUIWCKQGHC-UHFFFAOYSA-NZirconiumChemical compound[Zr]QCWXUUIWCKQGHC-UHFFFAOYSA-N0.000description1

- 229910021529ammoniaInorganic materials0.000description1

- 238000005336crackingMethods0.000description1

- 229910001873dinitrogenInorganic materials0.000description1

- 230000003028elevating effectEffects0.000description1

- 238000005516engineering processMethods0.000description1

- 239000011521glassSubstances0.000description1

- 229910052735hafniumInorganic materials0.000description1

- VBJZVLUMGGDVMO-UHFFFAOYSA-Nhafnium atomChemical compound[Hf]VBJZVLUMGGDVMO-UHFFFAOYSA-N0.000description1

- WMIYKQLTONQJES-UHFFFAOYSA-NhexafluoroethaneChemical compoundFC(F)(F)C(F)(F)FWMIYKQLTONQJES-UHFFFAOYSA-N0.000description1

- 239000001257hydrogenSubstances0.000description1

- 229910052739hydrogenInorganic materials0.000description1

- 239000011261inert gasSubstances0.000description1

- 238000009413insulationMethods0.000description1

- 230000010354integrationEffects0.000description1

- 239000011553magnetic fluidSubstances0.000description1

- 238000012423maintenanceMethods0.000description1

- 239000007769metal materialSubstances0.000description1

- 239000000203mixtureSubstances0.000description1

- 238000012986modificationMethods0.000description1

- 230000004048modificationEffects0.000description1

- 239000002052molecular layerSubstances0.000description1

- 230000003647oxidationEffects0.000description1

- 238000007254oxidation reactionMethods0.000description1

- 230000001590oxidative effectEffects0.000description1

- 230000035515penetrationEffects0.000description1

- 230000000737periodic effectEffects0.000description1

- 230000002093peripheral effectEffects0.000description1

- 239000002994raw materialSubstances0.000description1

- 230000009257reactivityEffects0.000description1

- 238000007790scrapingMethods0.000description1

- 238000001179sorption measurementMethods0.000description1

- 239000000126substanceSubstances0.000description1

- 238000011282treatmentMethods0.000description1

- 238000003466weldingMethods0.000description1

- 229910052726zirconiumInorganic materials0.000description1

Images

Classifications

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/44—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating

- C23C16/4401—Means for minimising impurities, e.g. dust, moisture or residual gas, in the reaction chamber

- C23C16/4405—Cleaning of reactor or parts inside the reactor by using reactive gases

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/22—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the deposition of inorganic material, other than metallic material

- C23C16/30—Deposition of compounds, mixtures or solid solutions, e.g. borides, carbides, nitrides

- C23C16/34—Nitrides

- C23C16/345—Silicon nitride

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/44—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating

- C23C16/4401—Means for minimising impurities, e.g. dust, moisture or residual gas, in the reaction chamber

- C23C16/4404—Coatings or surface treatment on the inside of the reaction chamber or on parts thereof

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S438/00—Semiconductor device manufacturing: process

- Y10S438/905—Cleaning of reaction chamber

Landscapes

- Chemical & Material Sciences (AREA)

- General Chemical & Material Sciences (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Engineering & Computer Science (AREA)

- Materials Engineering (AREA)

- Mechanical Engineering (AREA)

- Metallurgy (AREA)

- Organic Chemistry (AREA)

- Inorganic Chemistry (AREA)

- Chemical Vapour Deposition (AREA)

Description

成膜温度:800℃

プリカーサー:DCS

窒化剤:NH3

流量比DCS/NH3:90/270sccm

上記条件による高温部への成膜量(高温部の石英上における膜厚)tHは3000オングストローム(300nm)であったが、低温部への成膜量(低温部の石英上おける膜厚)tLは60オングストローム(6nm)しかなかった。膜厚tHと膜厚tLとの比tH/tLは50である(tH/tL=3000/60=50)。

成膜温度:600℃

プリカーサー:DCS

窒化剤:NH3

パージガス:N2

処理サイクル:DCS供給、N2パージ、NH3供給、N2パージ、DCS供給の繰り返し

上記条件による高温部への成膜量(高温部の石英上における膜厚)tHが900オングストローム(90nm)のとき、低温部Aへの成膜量(低温部Aの石英上における膜厚)tLは60オングストローム(6nm)となった。膜厚tHと膜厚tLとの比tH/tLは15である(tH/tL=900/60=15)。このまま、高温部におけるシリコン窒化膜の膜厚tHを3000オングストローム(300nm)とすると、低温部Aにおけるシリコン窒化膜の膜厚tLは180乃至200オングストローム(18乃至20nm)となる。膜厚tLが180乃至200オングストロームあれば、低温部Aにおけるメタルを封じ込める効果は充分なものにできる。また、高温部におけるシリコン窒化膜の膜厚tHは割れにくい膜厚を維持できるため、パーティクルの発生も抑制できる。

Claims (12)

- 真空保持可能な縦型で筒体状をなす処理容器と、前記処理容器内に配置され、被処理体を複数段に保持した状態で保持する保持部材と、前記処理容器の外周に設けられた加熱装置とを備えた成膜装置のメタル汚染低減方法であって、

前記処理容器内の内壁、及び前記保持部材の表面を、クリーニングガスを用いてクリーニングする工程と、

前記クリーニングされた前記処理容器の内壁、及び前記保持部材の表面に、MLD手法を用いてシリコン窒化膜を成膜し、前記処理容器の内壁、及び前記保持部材の表面をシリコン窒化膜により被覆する工程と、

を具備し、

前記処理容器内には高温部と低温部とがあり、

前記高温部における前記シリコン窒化膜の膜厚tHと、前記低温部における前記シリコン窒化膜の膜厚tLとの比tH/tLが1以上15以下であることを特徴とする成膜装置のメタル汚染低減方法。 - 前記シリコン窒化膜を成膜する際、前記低温部を加熱することを特徴とする請求項1に記載の成膜装置のメタル汚染低減方法。

- 前記シリコン窒化膜の膜厚の最大値tmaxは18nm以上300nm以下であることを特徴とする請求項1又は請求項2に記載の成膜装置のメタル汚染低減方法。

- 前記シリコン窒化膜は、成膜反応がCVDではなく、MLDとなる温度範囲にて成膜されることを特徴とする請求項1から請求項3のいずれか一項に記載の成膜装置のメタル汚染低減方法。

- 前記シリコン窒化膜は、プリカーサーとしてジクロルシランを用いる場合、温度550℃以上650℃以下の条件で成膜されることを特徴とする請求項4に記載の成膜装置のメタル汚染低減方法。

- 前記シリコン窒化膜は、プリカーサーとしてヘキサクロロジシランを用いる場合、温度450℃以上550℃以下の条件で成膜されることを特徴とする請求項4に記載の成膜装置のメタル汚染低減方法。

- 前記クリーニングガスは、ハロゲン、又はハロゲン化合物であることを特徴とする請求項1から請求項6のいずれか一項に記載の成膜装置のメタル汚染低減方法。

- 前記クリーニングガスは、

F2、CF4、C2F6、ClF3、COF2、NF3、及びHClのいずれかから選ばれることを特徴とする請求項7に記載の成膜装置のメタル汚染低減方法。 - 前記成膜装置は、被処理体に対して酸素又は窒素を含有する薄膜を成膜する成膜装置であって、前記被処理体への成膜処理時に、前記薄膜のソースガスと、前記酸素又は窒素を含有するガスとを交互に供給し、前記酸素又は窒素を含有する薄膜を成膜することを特徴とする請求項1から請求項8のいずれか一項に記載の成膜装置のメタル汚染低減方法。

- 真空保持可能な縦型で筒体状をなす処理容器と、前記処理容器内に配置され、半導体ウエハを複数段に保持した状態で保持する保持部材と、前記処理容器の外周に設けられた加熱装置とを備えた成膜装置を用いた半導体装置の製造方法であって、

前記処理容器の内壁、及び前記保持部材の表面に、MLD手法を用いてシリコン窒化膜を成膜し、前記処理容器の内壁、及び前記保持部材の表面をシリコン窒化膜により被覆する被覆工程と、

前記保持部材に複数段に保持された半導体ウエハに対して、酸素又は窒素を含有する薄膜を、この薄膜のソースガスと、前記酸素又は窒素を含有するガスとを交互に供給し、前記酸素又は窒素を含有する薄膜を成膜する成膜工程と、

前記成膜工程を所定回数実施した後、前記処理容器内の内壁、及び前記保持部材の表面を、クリーニングガスを用いてクリーニングするクリーニング工程と、を具備し、

前記クリーニング工程の後、前記被覆工程に戻るとともに、前記被覆工程を請求項1から請求項9のいずれか一項に記載の成膜装置のメタル汚染低減方法を用いて行うことを特徴とする半導体装置の製造方法。 - コンピュータ上で動作し、真空保持可能な縦型で筒体状をなす処理容器と、前記処理容器内に配置され、半導体ウエハを複数段に保持した状態で保持する保持部材と、前記処理容器の外周に設けられた加熱装置とを備えた成膜装置を制御するプログラムが記憶された記憶媒体であって、

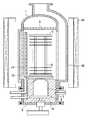

前記プログラムは、実行時に、請求項10に記載の半導体装置の製造方法を実行するように、コンピュータに前記成膜装置を制御させることを特徴とする記憶媒体。 - 下端に開口部を有する有天井の円筒体状の処理容器と、

前記処理容器の開口部に連結され、前記処理容器の内部に成膜ガスを導入するガス配管が接続される、円筒体状のマニホールドと、

前記マニホールドの開口部を、昇降することで開閉する蓋部と、

前記蓋部上に支持され、前記処理容器内に、被処理体を複数段に保持した状態で保持することが可能な保持部材と、

前記処理容器の外周に、前記保持部材を囲むように設けられた第1の加熱装置と、

前記蓋部の外部に設けられた第2の加熱装置と、

を具備し、

クリーニングされた前記処理容器の内壁、及び前記保持部材の表面に、MLD手法を用いてシリコン窒化膜を成膜し、前記処理容器の内壁、及び前記保持部材の表面をシリコン窒化膜により被覆する際、前記第2の加熱装置を用いて請求項2から請求項9のいずれか一項に記載の成膜装置のメタル汚染低減方法を行うことを特徴とする成膜装置。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009027098AJP5202372B2 (ja) | 2008-03-14 | 2009-02-09 | 成膜装置のメタル汚染低減方法、半導体装置の製造方法、記憶媒体及び成膜装置 |

| US12/401,214US7964516B2 (en) | 2008-03-14 | 2009-03-10 | Film formation apparatus for semiconductor process and method for using same |

| TW098108034ATWI415172B (zh) | 2008-03-14 | 2009-03-12 | 半導體製程用之膜形成設備及其使用方法 |

| CN2009101270420ACN101532126B (zh) | 2008-03-14 | 2009-03-13 | 半导体处理用的成膜装置及其使用方法 |

| KR1020090021395AKR101174953B1 (ko) | 2008-03-14 | 2009-03-13 | 반도체 처리용 성막 장치 및 그 사용 방법과, 컴퓨터로 판독 가능한 매체 |

| KR1020120057537AKR20120066617A (ko) | 2008-03-14 | 2012-05-30 | 반도체 처리용 성막 장치 및 그 사용 방법과, 컴퓨터로 판독 가능한 매체 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008066326 | 2008-03-14 | ||

| JP2008066326 | 2008-03-14 | ||

| JP2009027098AJP5202372B2 (ja) | 2008-03-14 | 2009-02-09 | 成膜装置のメタル汚染低減方法、半導体装置の製造方法、記憶媒体及び成膜装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009246340A JP2009246340A (ja) | 2009-10-22 |

| JP5202372B2true JP5202372B2 (ja) | 2013-06-05 |

Family

ID=41063511

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009027098AActiveJP5202372B2 (ja) | 2008-03-14 | 2009-02-09 | 成膜装置のメタル汚染低減方法、半導体装置の製造方法、記憶媒体及び成膜装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7964516B2 (ja) |

| JP (1) | JP5202372B2 (ja) |

| KR (2) | KR101174953B1 (ja) |

| CN (1) | CN101532126B (ja) |

| TW (1) | TWI415172B (ja) |

Families Citing this family (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5008957B2 (ja)* | 2006-11-30 | 2012-08-22 | 東京エレクトロン株式会社 | シリコン窒化膜の形成方法、形成装置、形成装置の処理方法及びプログラム |

| US8450834B2 (en)* | 2010-02-16 | 2013-05-28 | Taiwan Semiconductor Manufacturing Company, Ltd. | Spacer structure of a field effect transistor with an oxygen-containing layer between two oxygen-sealing layers |

| US8409352B2 (en)* | 2010-03-01 | 2013-04-02 | Hitachi Kokusai Electric Inc. | Method of manufacturing semiconductor device, method of manufacturing substrate and substrate processing apparatus |

| US8895457B2 (en) | 2010-03-08 | 2014-11-25 | Hitachi Kokusai Electric Inc. | Method of manufacturing semiconductor device and substrate processing apparatus |

| KR101147728B1 (ko)* | 2010-08-02 | 2012-05-25 | 주식회사 유진테크 | 사이클릭 박막 증착 방법 |

| JP5632687B2 (ja) | 2010-09-10 | 2014-11-26 | 株式会社日立国際電気 | 半導体装置の製造方法及び基板処理装置 |

| JP2012142386A (ja)* | 2010-12-28 | 2012-07-26 | Elpida Memory Inc | 窒化膜の形成方法 |

| JP2012195565A (ja)* | 2011-02-28 | 2012-10-11 | Hitachi Kokusai Electric Inc | 基板処理装置、基板処理方法及び半導体装置の製造方法 |

| JP6042656B2 (ja)* | 2011-09-30 | 2016-12-14 | 株式会社日立国際電気 | 半導体装置の製造方法、基板処理方法、基板処理装置およびプログラム |

| JP5807511B2 (ja) | 2011-10-27 | 2015-11-10 | 東京エレクトロン株式会社 | 成膜装置及びその運用方法 |

| CN103264025B (zh)* | 2013-05-31 | 2015-08-05 | 上海华力微电子有限公司 | 晶舟自动吹扫装置 |

| KR102162366B1 (ko)* | 2014-01-21 | 2020-10-06 | 우범제 | 퓸 제거 장치 |

| JP6131908B2 (ja)* | 2014-05-08 | 2017-05-24 | 豊田合成株式会社 | Iii族窒化物半導体の製造方法、発光素子の製造方法 |

| JP6347544B2 (ja)* | 2014-07-09 | 2018-06-27 | 株式会社日立国際電気 | 半導体装置の製造方法、基板処理装置およびプログラム |

| JP6647836B2 (ja)* | 2014-11-10 | 2020-02-14 | キヤノンメディカルシステムズ株式会社 | 磁気共鳴イメージング装置、画像処理装置及び画像処理方法 |

| US10121655B2 (en) | 2015-11-20 | 2018-11-06 | Applied Materials, Inc. | Lateral plasma/radical source |

| JP2018170387A (ja)* | 2017-03-29 | 2018-11-01 | 東京エレクトロン株式会社 | 成膜方法及び縦型熱処理装置 |

| JP6916766B2 (ja)* | 2018-08-27 | 2021-08-11 | 株式会社Kokusai Electric | 基板処理装置及び半導体装置の製造方法 |

| JP6956660B2 (ja)* | 2018-03-19 | 2021-11-02 | 東京エレクトロン株式会社 | クリーニング方法及び成膜装置 |

| JP6980125B2 (ja)* | 2018-09-25 | 2021-12-15 | 株式会社Kokusai Electric | 基板処理装置及び半導体装置の製造方法 |

| JP7258826B2 (ja)* | 2020-06-30 | 2023-04-17 | 株式会社Kokusai Electric | 基板処理方法、半導体装置の製造方法、基板処理装置、およびプログラム |

| US20220230855A1 (en)* | 2021-01-19 | 2022-07-21 | Changxin Memory Technologies, Inc. | Process apparatus and process method |

| JP7549556B2 (ja)* | 2021-03-18 | 2024-09-11 | キオクシア株式会社 | 半導体製造方法および半導体製造装置 |

Family Cites Families (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2708533B2 (ja)* | 1989-03-14 | 1998-02-04 | 富士通株式会社 | Cvd装置の残留ガス除去方法 |

| JPH09171968A (ja) | 1995-12-21 | 1997-06-30 | Toshiba Microelectron Corp | 熱処理装置及び半導体基板の熱処理方法 |

| JP3569376B2 (ja) | 1996-03-07 | 2004-09-22 | 株式会社ルネサステクノロジ | 半導体装置の製造方法 |

| US5976900A (en)* | 1997-12-08 | 1999-11-02 | Cypress Semiconductor Corp. | Method of reducing impurity contamination in semiconductor process chambers |

| JP2002313740A (ja) | 2001-04-17 | 2002-10-25 | Seiko Epson Corp | 半導体製造装置 |

| US6391803B1 (en) | 2001-06-20 | 2002-05-21 | Samsung Electronics Co., Ltd. | Method of forming silicon containing thin films by atomic layer deposition utilizing trisdimethylaminosilane |

| JP2003188159A (ja) | 2001-12-19 | 2003-07-04 | Seiko Epson Corp | Cvd装置及び半導体装置の製造方法 |

| US6825051B2 (en)* | 2002-05-17 | 2004-11-30 | Asm America, Inc. | Plasma etch resistant coating and process |

| JP3820212B2 (ja) | 2002-12-11 | 2006-09-13 | アプライド マテリアルズ インコーポレイテッド | Cvdチャンバクリーニング後にcvdチャンバをコンディショニングする方法 |

| JP4131677B2 (ja)* | 2003-03-24 | 2008-08-13 | 株式会社日立国際電気 | 半導体デバイスの製造方法及び基板処理装置 |

| US6974781B2 (en)* | 2003-10-20 | 2005-12-13 | Asm International N.V. | Reactor precoating for reduced stress and uniform CVD |

| JP5264039B2 (ja)* | 2004-08-10 | 2013-08-14 | 東京エレクトロン株式会社 | 薄膜形成装置及び薄膜形成方法 |

| JP2006165317A (ja)* | 2004-12-08 | 2006-06-22 | Elpida Memory Inc | 半導体製造装置のクリーニング方法 |

| TWI365919B (en)* | 2004-12-28 | 2012-06-11 | Tokyo Electron Ltd | Film formation apparatus and method of using the same |

| US20070292974A1 (en)* | 2005-02-17 | 2007-12-20 | Hitachi Kokusai Electric Inc | Substrate Processing Method and Substrate Processing Apparatus |

| JP5324026B2 (ja)* | 2006-01-18 | 2013-10-23 | 東京エレクトロン株式会社 | プラズマ処理装置およびプラズマ処理装置の制御方法 |

| KR101047230B1 (ko)* | 2006-03-28 | 2011-07-06 | 가부시키가이샤 히다치 고쿠사이 덴키 | 기판 처리 장치 |

| JP4410211B2 (ja)* | 2006-04-04 | 2010-02-03 | 東京エレクトロン株式会社 | 成膜装置及び成膜方法 |

| US20090155606A1 (en)* | 2007-12-13 | 2009-06-18 | Asm Genitech Korea Ltd. | Methods of depositing a silicon nitride film |

| JP2009209447A (ja)* | 2008-02-04 | 2009-09-17 | Hitachi Kokusai Electric Inc | 基板処理装置 |

- 2009

- 2009-02-09JPJP2009027098Apatent/JP5202372B2/jaactiveActive

- 2009-03-10USUS12/401,214patent/US7964516B2/enactiveActive

- 2009-03-12TWTW098108034Apatent/TWI415172B/zhnot_activeIP Right Cessation

- 2009-03-13CNCN2009101270420Apatent/CN101532126B/zhactiveActive

- 2009-03-13KRKR1020090021395Apatent/KR101174953B1/koactiveActive

- 2012

- 2012-05-30KRKR1020120057537Apatent/KR20120066617A/konot_activeCeased

Also Published As

| Publication number | Publication date |

|---|---|

| CN101532126B (zh) | 2013-05-15 |

| JP2009246340A (ja) | 2009-10-22 |

| KR20090098724A (ko) | 2009-09-17 |

| TWI415172B (zh) | 2013-11-11 |

| KR20120066617A (ko) | 2012-06-22 |

| US7964516B2 (en) | 2011-06-21 |

| TW200947527A (en) | 2009-11-16 |

| US20090233454A1 (en) | 2009-09-17 |

| KR101174953B1 (ko) | 2012-08-17 |

| CN101532126A (zh) | 2009-09-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5202372B2 (ja) | 成膜装置のメタル汚染低減方法、半導体装置の製造方法、記憶媒体及び成膜装置 | |

| JP5250600B2 (ja) | 成膜方法および成膜装置 | |

| JP6347543B2 (ja) | クリーニング方法、半導体装置の製造方法、基板処理装置およびプログラム | |

| US9587308B2 (en) | Cleaning method, method of manufacturing semiconductor device, substrate processing apparatus, and recording medium | |

| JP6101113B2 (ja) | 半導体装置の製造方法、クリーニング方法および基板処理装置並びにプログラム | |

| JP5514129B2 (ja) | 成膜方法、成膜装置、および成膜装置の使用方法 | |

| JP5346904B2 (ja) | 縦型成膜装置およびその使用方法 | |

| JP5258229B2 (ja) | 成膜方法および成膜装置 | |

| JP6826558B2 (ja) | クリーニング方法、半導体装置の製造方法、基板処理装置、およびプログラム | |

| KR20140109285A (ko) | 클리닝 방법, 반도체 장치의 제조 방법, 기판 처리 장치 및 기록 매체 | |

| JP6785809B2 (ja) | 処理容器内の部材をクリーニングする方法、半導体装置の製造方法、基板処理装置、およびプログラム | |

| JP5221089B2 (ja) | 成膜方法、成膜装置および記憶媒体 | |

| JP5575299B2 (ja) | 成膜方法および成膜装置 | |

| US20250308945A1 (en) | Cleaning method, method of manufacturing semiconductor device, and substrate processing apparatus | |

| CN110402482A (zh) | 半导体装置的制造方法、清洁方法、基板处理装置和程序 | |

| JP5201934B2 (ja) | 基板処理装置のメタル汚染低減方法 | |

| JP2011243620A (ja) | 成膜方法および成膜装置 | |

| US11618947B2 (en) | Method of cleaning, method of manufacturing semiconductor device, substrate processing apparatus, and recording medium | |

| JPWO2017199570A1 (ja) | クリーニング方法、半導体装置の製造方法、基板処理装置およびプログラム | |

| WO2025079541A1 (ja) | 成膜方法、半導体デバイスの製造方法、及び成膜システム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination | Free format text:JAPANESE INTERMEDIATE CODE: A621 Effective date:20101026 | |

| A977 | Report on retrieval | Free format text:JAPANESE INTERMEDIATE CODE: A971007 Effective date:20110907 | |

| A131 | Notification of reasons for refusal | Free format text:JAPANESE INTERMEDIATE CODE: A131 Effective date:20121120 | |

| A521 | Request for written amendment filed | Free format text:JAPANESE INTERMEDIATE CODE: A523 Effective date:20130117 | |

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) | Free format text:JAPANESE INTERMEDIATE CODE: A01 Effective date:20130205 | |

| A61 | First payment of annual fees (during grant procedure) | Free format text:JAPANESE INTERMEDIATE CODE: A61 Effective date:20130212 | |

| R150 | Certificate of patent or registration of utility model | Ref document number:5202372 Country of ref document:JP Free format text:JAPANESE INTERMEDIATE CODE: R150 | |

| FPAY | Renewal fee payment (event date is renewal date of database) | Free format text:PAYMENT UNTIL: 20160222 Year of fee payment:3 | |

| R250 | Receipt of annual fees | Free format text:JAPANESE INTERMEDIATE CODE: R250 | |

| R250 | Receipt of annual fees | Free format text:JAPANESE INTERMEDIATE CODE: R250 | |

| R250 | Receipt of annual fees | Free format text:JAPANESE INTERMEDIATE CODE: R250 | |

| R250 | Receipt of annual fees | Free format text:JAPANESE INTERMEDIATE CODE: R250 | |

| R250 | Receipt of annual fees | Free format text:JAPANESE INTERMEDIATE CODE: R250 | |

| R250 | Receipt of annual fees | Free format text:JAPANESE INTERMEDIATE CODE: R250 | |

| R250 | Receipt of annual fees | Free format text:JAPANESE INTERMEDIATE CODE: R250 | |

| R250 | Receipt of annual fees | Free format text:JAPANESE INTERMEDIATE CODE: R250 |