JP5089244B2 - 半導体装置 - Google Patents

半導体装置Download PDFInfo

- Publication number

- JP5089244B2 JP5089244B2JP2007135160AJP2007135160AJP5089244B2JP 5089244 B2JP5089244 B2JP 5089244B2JP 2007135160 AJP2007135160 AJP 2007135160AJP 2007135160 AJP2007135160 AJP 2007135160AJP 5089244 B2JP5089244 B2JP 5089244B2

- Authority

- JP

- Japan

- Prior art keywords

- wiring

- film

- semiconductor device

- trench

- barrier film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065semiconductorSubstances0.000titleclaimsdescription34

- 230000004888barrier functionEffects0.000claimsdescription70

- 238000009792diffusion processMethods0.000claimsdescription26

- 239000000463materialSubstances0.000claimsdescription16

- 229910004298SiO 2Inorganic materials0.000claimsdescription15

- 230000002265preventionEffects0.000claimsdescription11

- 229910052760oxygenInorganic materials0.000claimsdescription8

- 229910020177SiOFInorganic materials0.000claimsdescription6

- 238000009413insulationMethods0.000claimsdescription5

- 229910052748manganeseInorganic materials0.000claimsdescription5

- 229910052710siliconInorganic materials0.000claimsdescription4

- 239000010410layerSubstances0.000claimsdescription3

- 239000002344surface layerSubstances0.000claimsdescription3

- 150000001875compoundsChemical class0.000claimsdescription2

- 239000010949copperSubstances0.000description103

- 239000011229interlayerSubstances0.000description36

- 229910045601alloyInorganic materials0.000description34

- 239000000956alloySubstances0.000description34

- 239000011572manganeseSubstances0.000description26

- 238000000034methodMethods0.000description13

- 229910052751metalInorganic materials0.000description11

- 239000002184metalSubstances0.000description11

- 239000000470constituentSubstances0.000description7

- 229910052802copperInorganic materials0.000description5

- 239000011148porous materialSubstances0.000description5

- HBMJWWWQQXIZIP-UHFFFAOYSA-Nsilicon carbideChemical compound[Si+]#[C-]HBMJWWWQQXIZIP-UHFFFAOYSA-N0.000description5

- 229910010271silicon carbideInorganic materials0.000description5

- 229910000881Cu alloyInorganic materials0.000description4

- QVGXLLKOCUKJST-UHFFFAOYSA-Natomic oxygenChemical compound[O]QVGXLLKOCUKJST-UHFFFAOYSA-N0.000description4

- 239000001301oxygenSubstances0.000description4

- RYGMFSIKBFXOCR-UHFFFAOYSA-NCopperChemical compound[Cu]RYGMFSIKBFXOCR-UHFFFAOYSA-N0.000description3

- VYPSYNLAJGMNEJ-UHFFFAOYSA-NSilicium dioxideChemical compoundO=[Si]=OVYPSYNLAJGMNEJ-UHFFFAOYSA-N0.000description3

- 238000010438heat treatmentMethods0.000description3

- 238000004519manufacturing processMethods0.000description3

- 238000005498polishingMethods0.000description3

- 229910052814silicon oxideInorganic materials0.000description3

- IJGRMHOSHXDMSA-UHFFFAOYSA-NAtomic nitrogenChemical compoundN#NIJGRMHOSHXDMSA-UHFFFAOYSA-N0.000description2

- 238000000137annealingMethods0.000description2

- 230000015572biosynthetic processEffects0.000description2

- 239000011651chromiumSubstances0.000description2

- 238000001312dry etchingMethods0.000description2

- 238000005530etchingMethods0.000description2

- 239000011777magnesiumSubstances0.000description2

- 230000000149penetrating effectEffects0.000description2

- 238000005268plasma chemical vapour depositionMethods0.000description2

- 239000000126substanceSubstances0.000description2

- 239000000758substrateSubstances0.000description2

- 239000010936titaniumSubstances0.000description2

- OKTJSMMVPCPJKN-UHFFFAOYSA-NCarbonChemical compound[C]OKTJSMMVPCPJKN-UHFFFAOYSA-N0.000description1

- VYZAMTAEIAYCRO-UHFFFAOYSA-NChromiumChemical compound[Cr]VYZAMTAEIAYCRO-UHFFFAOYSA-N0.000description1

- PXGOKWXKJXAPGV-UHFFFAOYSA-NFluorineChemical compoundFFPXGOKWXKJXAPGV-UHFFFAOYSA-N0.000description1

- FYYHWMGAXLPEAU-UHFFFAOYSA-NMagnesiumChemical compound[Mg]FYYHWMGAXLPEAU-UHFFFAOYSA-N0.000description1

- PWHULOQIROXLJO-UHFFFAOYSA-NManganeseChemical compound[Mn]PWHULOQIROXLJO-UHFFFAOYSA-N0.000description1

- ZOKXTWBITQBERF-UHFFFAOYSA-NMolybdenumChemical compound[Mo]ZOKXTWBITQBERF-UHFFFAOYSA-N0.000description1

- RTAQQCXQSZGOHL-UHFFFAOYSA-NTitaniumChemical compound[Ti]RTAQQCXQSZGOHL-UHFFFAOYSA-N0.000description1

- 229910052782aluminiumInorganic materials0.000description1

- XAGFODPZIPBFFR-UHFFFAOYSA-NaluminiumChemical compound[Al]XAGFODPZIPBFFR-UHFFFAOYSA-N0.000description1

- 229910052799carbonInorganic materials0.000description1

- 238000005229chemical vapour depositionMethods0.000description1

- 229910052804chromiumInorganic materials0.000description1

- 239000011737fluorineSubstances0.000description1

- 229910052731fluorineInorganic materials0.000description1

- 238000001764infiltrationMethods0.000description1

- 230000008595infiltrationEffects0.000description1

- 229910052749magnesiumInorganic materials0.000description1

- 239000012528membraneSubstances0.000description1

- 150000002739metalsChemical class0.000description1

- 239000000203mixtureSubstances0.000description1

- 229910052750molybdenumInorganic materials0.000description1

- 239000011733molybdenumSubstances0.000description1

- 229910052757nitrogenInorganic materials0.000description1

- 238000000206photolithographyMethods0.000description1

- 238000007747platingMethods0.000description1

- 238000007517polishing processMethods0.000description1

- LIVNPJMFVYWSIS-UHFFFAOYSA-Nsilicon monoxideChemical class[Si-]#[O+]LIVNPJMFVYWSIS-UHFFFAOYSA-N0.000description1

- 238000004544sputter depositionMethods0.000description1

- 229910052715tantalumInorganic materials0.000description1

- GUVRBAGPIYLISA-UHFFFAOYSA-Ntantalum atomChemical compound[Ta]GUVRBAGPIYLISA-UHFFFAOYSA-N0.000description1

- 229910052719titaniumInorganic materials0.000description1

Images

Classifications

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/5329—Insulating materials

- H01L23/53295—Stacked insulating layers

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76829—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing characterised by the formation of thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers

- H01L21/76831—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing characterised by the formation of thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers in via holes or trenches, e.g. non-conductive sidewall liners

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76841—Barrier, adhesion or liner layers

- H01L21/76843—Barrier, adhesion or liner layers formed in openings in a dielectric

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/53204—Conductive materials

- H01L23/53209—Conductive materials based on metals, e.g. alloys, metal silicides

- H01L23/53228—Conductive materials based on metals, e.g. alloys, metal silicides the principal metal being copper

- H01L23/53238—Additional layers associated with copper layers, e.g. adhesion, barrier, cladding layers

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/5329—Insulating materials

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Description

この発明は、Cu(銅)を主成分とするCu配線を有する半導体装置に関する。

半導体装置の高集積化に伴い、配線のさらなる微細化が要求されてきている。配線の微細化による配線抵抗の増大を抑えるため、配線材料として、従来から用いられてきたAl(アルミニウム)に代えて、より導電性の高いCu(銅)を適用することが検討されている。

Cu配線は、Cuがドライエッチングなどによる微細なパターニングが困難であることから、いわゆるダマシン法によって形成される。このダマシン法では、まず、SiO2(酸化シリコン)からなる絶縁膜に、所定の配線パターンに対応した微細な配線溝が形成される。Cu膜は、配線溝を埋め尽くし、絶縁膜の表面全域を覆うような厚さに形成される。その後、CMP(Chemical Mechanical Polishing:化学的機械的研磨)法により、Cu膜が研磨される。このCu膜の研磨は、Cu膜の配線溝外の部分がすべて除去され、配線溝外の絶縁膜の表面が露出するまで続けられる。これにより、配線溝内にのみCu膜が残存し、配線溝内に埋設されたCu配線が得られる。

Cu配線は、Cuがドライエッチングなどによる微細なパターニングが困難であることから、いわゆるダマシン法によって形成される。このダマシン法では、まず、SiO2(酸化シリコン)からなる絶縁膜に、所定の配線パターンに対応した微細な配線溝が形成される。Cu膜は、配線溝を埋め尽くし、絶縁膜の表面全域を覆うような厚さに形成される。その後、CMP(Chemical Mechanical Polishing:化学的機械的研磨)法により、Cu膜が研磨される。このCu膜の研磨は、Cu膜の配線溝外の部分がすべて除去され、配線溝外の絶縁膜の表面が露出するまで続けられる。これにより、配線溝内にのみCu膜が残存し、配線溝内に埋設されたCu配線が得られる。

ところが、Cuは、Alに比べて、絶縁膜への拡散性が高い。このため、絶縁膜上にCu配線(Cu膜)が直に形成されると、絶縁膜中にCuが拡散し、配線間の短絡などを生じるおそれがある。そのため、絶縁膜とCu配線との間には、Cuの絶縁膜への拡散を防止するためのバリア膜が必要となる。

このバリア膜を形成する手法として、たとえば、Cu膜の形成に先立ち、配線溝が形成された絶縁膜上にCuとMn(マンガン)との合金からなるCuMn合金膜を形成し、Cu膜の形成後に熱処理を行なうことにより、合金膜中のMnを絶縁膜との界面に拡散させて、その界面にMnxSiyOz(x,y,z:零よりも大きい数)からなるバリア膜を形成する手法が提案されている(たとえば、特許文献1参照)。

このバリア膜を形成する手法として、たとえば、Cu膜の形成に先立ち、配線溝が形成された絶縁膜上にCuとMn(マンガン)との合金からなるCuMn合金膜を形成し、Cu膜の形成後に熱処理を行なうことにより、合金膜中のMnを絶縁膜との界面に拡散させて、その界面にMnxSiyOz(x,y,z:零よりも大きい数)からなるバリア膜を形成する手法が提案されている(たとえば、特許文献1参照)。

一方、配線の微細化にともなって、配線間距離が短くなるため、近接する配線間の電気容量(配線間容量)が大きくなるという問題を生じる。この問題は、比誘電率の小さい、いわゆるLow−k材料(たとえば、SiOC、SiOFなど)を絶縁膜材料として用いることにより解決することができる。

特開2005−277390号公報

ところが、Low−k材料からなる絶縁膜は、その内部に多数の空孔(ポア)が存在するので膜密度が小さいため、絶縁膜上にCuMn合金膜を形成すると、CuMn合金が絶縁膜中に容易に浸み込んでしまうという別の問題を生じる。また、配線溝の形成時に、空孔の一部が曝露することにより配線溝の内面に凹部が形成される場合がある。さらに、Low−k材料からなる絶縁膜は、SiO2からなる絶縁膜に比べてO(酸素)濃度が小さいため、MnxSiyOzからなるバリア膜が形成されにくいという問題もある。

これらの問題を解決するために、CuMn合金膜を厚く形成することが考えられる。しかし、CuMn合金膜の膜厚が厚くされると、MnxSiyOzバリア膜の形成に必要なMn以上の余剰MnがCu配線中に拡散してしまい、Cu配線の配線抵抗が増大してしまう。

そこで、この発明の目的は、Cu配線から低誘電率材料(Low−k材料)絶縁膜へのCuの拡散を防止することができるとともに、Cu配線の抵抗の増大を防止することができる半導体装置を提供することにある。

そこで、この発明の目的は、Cu配線から低誘電率材料(Low−k材料)絶縁膜へのCuの拡散を防止することができるとともに、Cu配線の抵抗の増大を防止することができる半導体装置を提供することにある。

上記目的を達成するための請求項1記載の発明は、Cuを主成分とする第1Cu配線と、前記第1Cu配線上に形成され、SiO2より比誘電率の小さい低誘電率材料からなる絶縁膜と、前記絶縁膜に、その表面から膜厚方向に貫通するように形成され、内部に前記第1Cu配線の上面が露出した配線溝と、前記配線溝の少なくとも側面上に形成され、SiO2またはSiCOからなり、前記絶縁膜よりも膜密度が大きい第1バリア膜と、前記配線溝に埋設され、前記第1Cu配線に電気的に接続されたCuを主成分とする第2Cu配線と、前記第1Cu配線の前記上面を含む前記第2Cu配線の前記配線溝との対向面を被覆し、Si、OおよびMnを含む化合物からなる第2バリア膜と、を含む、半導体装置である。

この半導体装置では、SiO2より比誘電率の小さい低誘電率材料からなる絶縁膜には、配線溝が形成されている。配線溝の少なくとも側面上には、SiO2またはSiCOからなる第1バリア膜が形成されている。配線溝には、Cuを主成分とする第2Cu配線が埋設されている。そして、第1Cu配線の上面を含む第2Cu配線の配線溝との対向面を被覆するように、第2バリア膜が形成されている。

第2バリア膜は、たとえば、Mnを含む金属膜(たとえば、CuMn合金膜)が配線溝内に形成され、Mnと絶縁膜または第1バリア膜中のSi、Oとが結合することにより形成される。このとき、配線溝の少なくとも側面上に、低誘電率材料より膜密度の大きいSiO2またはSiCOからなる第1バリア膜が形成されているため、金属膜の構成成分(たとえば、CuMn合金)が絶縁膜中に浸み込むことを防止することができる。そのため、金属膜の膜厚を薄くしても、第2バリア膜を構成するのに十分な量の金属膜の構成成分を確保することができる。

なお、膜密度とは、絶縁膜および第1バリア膜の一定体積中において、膜の構成成分が占める体積のことである。すなわち、同じ体積の第1バリア膜および絶縁膜を比較した場合、膜密度の大きい第1バリア膜内には、空孔(ポア)などの空間部分が少ないことを意味する。

また、配線溝の内面(たとえば、側面)に凹部が形成されている場合であっても、その凹部が第1バリア膜で塞がれる構成にすることにより、金属膜が形成される面を平坦化させることができる。そのため、凹部を塞いで配線溝の内面を平坦化するために金属膜の膜厚を厚くする必要がない。すなわち、金属膜の膜厚を薄くすることができる。

また、配線溝の内面(たとえば、側面)に凹部が形成されている場合であっても、その凹部が第1バリア膜で塞がれる構成にすることにより、金属膜が形成される面を平坦化させることができる。そのため、凹部を塞いで配線溝の内面を平坦化するために金属膜の膜厚を厚くする必要がない。すなわち、金属膜の膜厚を薄くすることができる。

このように、金属膜の膜厚を薄くすることができるため、金属膜に第2Cu配線の配線抵抗を増大させる抵抗成分(たとえば、Mn)が含まれている場合でも、当該抵抗成分は、第2バリア膜の構成成分として余ることなく使用される。そのため、Mnの第2Cu配線への拡散がない。その結果、第2Cu配線の配線抵抗が増大することを防止することができる。

また、第2Cu配線は、その配線溝との対向面が第2バリア膜で被覆されているので、第2Cu配線から絶縁膜へのCuの拡散を防止することができる。

また、第2Cu配線は、その配線溝との対向面が第2バリア膜で被覆されているので、第2Cu配線から絶縁膜へのCuの拡散を防止することができる。

また、第2Cu配線の配線溝との対向面を被覆する第2バリア膜は、MnxSiyOz(x,y,z:零よりも大きい数)からなる。このとき、絶縁膜よりO(酸素)の含有量が多い膜を第1バリア膜とすれば、配線溝内に形成される金属膜中のMnを容易にOと反応させることができるので、効率よく第2バリア膜(MnxSiyOz)を形成することができる。

請求項2記載の発明は、前記配線溝は、前記絶縁膜の表層部に形成されたトレンチと、前記トレンチの底面から前記第1Cu配線に達するビアホールとを含み、前記第1バリア膜は、前記トレンチの前記底面を露出させるように形成されており、前記第2バリア膜は、露出した前記トレンチの前記底面に接するように形成されている、請求項1に記載の半導体装置である。

請求項3記載の発明は、前記第1バリア膜が、Cを含有している、請求項1に記載の半導体装置である。

請求項4記載の発明は、前記第1バリア膜の元素含有量は、Cの含有量が50原子%〜70原子%、Oの含有量が4原子%〜11原子%である、請求項3に記載の半導体装置である。

請求項5記載の発明は、前記絶縁膜が、SiOCまたはSiOFからなる、請求項1〜4のいずれか一項に記載の半導体装置である。

請求項6記載の発明は、前記配線溝に埋設された前記第2Cu配線上には、拡散防止膜が形成されている、請求項1〜5のいずれか一項に記載の半導体装置である。

請求項7記載の発明は、前記拡散防止膜が、SiCからなる、請求項6に記載の半導体装置である。

請求項8記載の発明は、前記配線溝の前記側面に複数の凹部が形成されており、前記凹部は、前記第1バリア膜により塞がれている、請求項1〜7のいずれか一項に記載の半導体装置である。

請求項2記載の発明は、前記配線溝は、前記絶縁膜の表層部に形成されたトレンチと、前記トレンチの底面から前記第1Cu配線に達するビアホールとを含み、前記第1バリア膜は、前記トレンチの前記底面を露出させるように形成されており、前記第2バリア膜は、露出した前記トレンチの前記底面に接するように形成されている、請求項1に記載の半導体装置である。

請求項3記載の発明は、前記第1バリア膜が、Cを含有している、請求項1に記載の半導体装置である。

請求項4記載の発明は、前記第1バリア膜の元素含有量は、Cの含有量が50原子%〜70原子%、Oの含有量が4原子%〜11原子%である、請求項3に記載の半導体装置である。

請求項5記載の発明は、前記絶縁膜が、SiOCまたはSiOFからなる、請求項1〜4のいずれか一項に記載の半導体装置である。

請求項6記載の発明は、前記配線溝に埋設された前記第2Cu配線上には、拡散防止膜が形成されている、請求項1〜5のいずれか一項に記載の半導体装置である。

請求項7記載の発明は、前記拡散防止膜が、SiCからなる、請求項6に記載の半導体装置である。

請求項8記載の発明は、前記配線溝の前記側面に複数の凹部が形成されており、前記凹部は、前記第1バリア膜により塞がれている、請求項1〜7のいずれか一項に記載の半導体装置である。

以下では、この発明の実施の形態を、添付図面を参照して詳細に説明する。

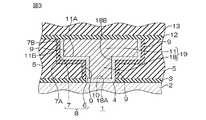

図1は、この発明の第1の実施形態に係る半導体装置の構造を説明するための図解的な断面図であって、図1(a)は、半導体装置の配線構造の要部拡大図である。図1(b)は、図1(a)における円Aで囲まれる部分の拡大図である。

この半導体装置1は、ダマシン配線構造による多層配線を有する半導体装置であって、半導体基板(図示せず)上にダマシン法で形成された第1Cu配線2を備えている。

図1は、この発明の第1の実施形態に係る半導体装置の構造を説明するための図解的な断面図であって、図1(a)は、半導体装置の配線構造の要部拡大図である。図1(b)は、図1(a)における円Aで囲まれる部分の拡大図である。

この半導体装置1は、ダマシン配線構造による多層配線を有する半導体装置であって、半導体基板(図示せず)上にダマシン法で形成された第1Cu配線2を備えている。

第1Cu配線2は、Cu(銅)を主成分とするCu合金からなる。Cu合金としては、Cuと、たとえば、Mg(マグネシウム)、Ti(チタン)、Mo(モリブデン)、Ta(タンタル)、Cr(クロム)などの金属との合金が挙げられ、これら金属が2種以上併用されたCu合金でもよい。

第1Cu配線2上には、たとえば、SiC(炭化シリコン)からなる第1拡散防止膜3が積層されている。

第1Cu配線2上には、たとえば、SiC(炭化シリコン)からなる第1拡散防止膜3が積層されている。

第1拡散防止膜3は、第1Cu配線2に含まれるCuが、後述する層間絶縁膜5に拡散することを防止するための膜である。第1拡散防止膜3には、その表面から膜厚方向に貫通する貫通孔4が形成されている。貫通孔4の形成により、第1Cu配線2は、その一部が第1拡散防止膜3から露出している。

第1拡散防止膜3の上には、層間絶縁膜5(絶縁膜)が積層されている。

第1拡散防止膜3の上には、層間絶縁膜5(絶縁膜)が積層されている。

層間絶縁膜5は、SiO2(酸化シリコン 比誘電率k=4.0〜4.2)より比誘電率の小さい低誘電率材料(Low−k材料)からなる。このようなLow−k材料としては、たとえば、SiOC(炭素添加酸化シリコン、比誘電率k=3以下)、SiOF(フッソ添加酸化シリコン、比誘電率k=3以下)などが挙げられる。なお、この実施形態では、層間絶縁膜5は、SiOCからなる。

SiOCの元素含有量は、たとえば、O(酸素)の含有量が38原子%〜46原子%、C(炭素)の含有量が23原子%〜37原子%である。また、SiOFの元素含有量は、たとえば、Oの含有量が55原子%〜57原子%、F(フッ素)の含有量が10原子%〜12原子%である。層間絶縁膜5をSiOCで形成することにより、たとえば、第1Cu配線2と第2Cu配線11(後述)との間の比誘電率を下げることができるので、第1Cu配線2および第2Cu配線11間の配線間容量の増大を防止することができる。

層間絶縁膜5には、その表面から膜厚方向に貫通する配線溝8が形成されている。

配線溝8は、層間絶縁膜5の表層部に所定のパターン(配線パターン)で形成されたトレンチ7と、このトレンチ7の底面7Aにおける貫通孔4の直上の位置から、貫通孔4に達するビアホール6とを備えている。前述したように、層間絶縁膜5はSiOCからなるので、層間絶縁膜5の内部には、多数の空孔(ポア)が存在する。そのため、図1(b)に示すように、配線溝8の内面(この実施形態では、トレンチ7の側面7Bおよびビアホール6の側面6B)には、配線溝8の形成時にそれらの空孔の一部が曝露することにより、複数の凹部14が存在する場合がある。

配線溝8は、層間絶縁膜5の表層部に所定のパターン(配線パターン)で形成されたトレンチ7と、このトレンチ7の底面7Aにおける貫通孔4の直上の位置から、貫通孔4に達するビアホール6とを備えている。前述したように、層間絶縁膜5はSiOCからなるので、層間絶縁膜5の内部には、多数の空孔(ポア)が存在する。そのため、図1(b)に示すように、配線溝8の内面(この実施形態では、トレンチ7の側面7Bおよびビアホール6の側面6B)には、配線溝8の形成時にそれらの空孔の一部が曝露することにより、複数の凹部14が存在する場合がある。

配線溝8の内面(この実施形態では、トレンチ7の側面7Bおよびビアホール6の側面6B)には、第1バリア膜9が形成されている。そのため、配線溝8の内面に凹部14が存在する場合であっても、この凹部14は、第1バリア膜9の一部で塞がれている(図1(b)参照)。

第1バリア膜9は、SiO2またはSiCO(酸素添加炭化シリコン)からなる。SiO2とは、SiOCに比べてO(酸素)含有量が多い材料である。また、SiO2からなる第1バリア膜9は、SiOCからなる層間絶縁膜5に比べて、その膜密度が大きい。なお、膜密度とは、第1バリア膜9および層間絶縁膜5の一定体積中において、膜の構成成分が占める体積のことである。すなわち、同じ体積の第1バリア膜9および層間絶縁膜5を比較した場合、膜密度の大きい第1バリア膜9内には、空孔(ポア)などの空間部分が少ないことを意味する。

第1バリア膜9は、SiO2またはSiCO(酸素添加炭化シリコン)からなる。SiO2とは、SiOCに比べてO(酸素)含有量が多い材料である。また、SiO2からなる第1バリア膜9は、SiOCからなる層間絶縁膜5に比べて、その膜密度が大きい。なお、膜密度とは、第1バリア膜9および層間絶縁膜5の一定体積中において、膜の構成成分が占める体積のことである。すなわち、同じ体積の第1バリア膜9および層間絶縁膜5を比較した場合、膜密度の大きい第1バリア膜9内には、空孔(ポア)などの空間部分が少ないことを意味する。

一方、SiCOとは、SiOCと元素組成が同じで、構成する元素の元素含有量が異なる材料である。より具体的には、SiCOの元素含有量は、たとえば、Cの含有量が50原子%〜70原子%、Oの含有量が4原子%〜11原子%である。また、SiCOからなる第1バリア膜9は、SiOCからなる層間絶縁膜5に比べて、その膜密度が大きい。なお、SiCOからなる絶縁膜として、SiOCからなる絶縁膜より、膜密度が大きく、且つ、Oの含有量が多い絶縁膜を形成することも可能であり、第1バリア膜9としては、このような絶縁膜であることが好ましい。

第1バリア膜9上の領域を含む配線溝8の内面、より具体的には、第1バリア膜9の表面、トレンチ7の底面7Aおよび第1Cu配線2の露出面上には、第2バリア膜10が形成されている。

第2バリア膜10は、たとえば、MnxSiyOz(x,y,z:零よりも大きい数)からなる。第2バリア膜10の膜厚は、トレンチ7の幅W1(平面視で長手方向と直交する方向の幅)およびビアホール6の幅(直径)W2によって異なるが、たとえば、トレンチ7の幅W1が100nm〜1000nm、ビアホール6の幅W2が100nm〜300nmの場合には、1.5nm〜25nmである。

第2バリア膜10は、たとえば、MnxSiyOz(x,y,z:零よりも大きい数)からなる。第2バリア膜10の膜厚は、トレンチ7の幅W1(平面視で長手方向と直交する方向の幅)およびビアホール6の幅(直径)W2によって異なるが、たとえば、トレンチ7の幅W1が100nm〜1000nm、ビアホール6の幅W2が100nm〜300nmの場合には、1.5nm〜25nmである。

そして、第2バリア膜10が形成された配線溝8には、Cu配線部19が埋設されている。すなわち、Cu配線部19の配線溝8との対向面(この実施形態では、Cu配線11(後述)の底面11Aおよび側面11B、ならびに接続ビア18(後述)の底面18Aおよび側面18B)は、第2バリア膜10で被覆されている。

Cu配線部19は、第1Cu配線2と同様にCuを主成分とするCu合金からなり、トレンチ7に埋設されている第2Cu配線11と、ビアホール6に埋設されている接続ビア18とを一体的に備えている。Cu配線部19が配線溝8に埋設されていることにより、第2Cu配線11の配線構造は、ダマシン配線構造となっている。

Cu配線部19は、第1Cu配線2と同様にCuを主成分とするCu合金からなり、トレンチ7に埋設されている第2Cu配線11と、ビアホール6に埋設されている接続ビア18とを一体的に備えている。Cu配線部19が配線溝8に埋設されていることにより、第2Cu配線11の配線構造は、ダマシン配線構造となっている。

そして、Cu配線部19(第2Cu配線11)および層間絶縁膜5上には、前述の第1拡散防止膜3および層間絶縁膜5と同様に、SiCからなる第2拡散防止膜12およびSiOCからなる層間絶縁膜13が、この順に積層されている。第2拡散防止膜12および層間絶縁膜13には、図示されていないが、第2Cu配線11と同様のCu配線が形成されており、このCu配線は、接続ビア(図示せず)を介して第2Cu配線11と電気的に接続されている。

なお、この半導体装置1には、図示および説明を省略するが、たとえば、外部との電気接続のための電極パッドなどが備えられている。

図2は、図1に示す半導体装置の製造方法を工程順に示す図解的な断面図である。

半導体装置1の製造に際しては、まず、半導体基板(図示せず)上に、第1Cu配線2がダマシン法で形成される。次に、図2(a)に示すように、第1Cu配線2上に、たとえば、プラズマCVD(Chemical Vapor Deposition:化学気相成長)法により、第1拡散防止膜3および層間絶縁膜5が順に形成される。

図2は、図1に示す半導体装置の製造方法を工程順に示す図解的な断面図である。

半導体装置1の製造に際しては、まず、半導体基板(図示せず)上に、第1Cu配線2がダマシン法で形成される。次に、図2(a)に示すように、第1Cu配線2上に、たとえば、プラズマCVD(Chemical Vapor Deposition:化学気相成長)法により、第1拡散防止膜3および層間絶縁膜5が順に形成される。

次に、図2(b)に示すように、層間絶縁膜5に、公知のフォトリソグラフィ技術およびエッチング技術により、配線溝8(ビアホール6およびトレンチ7)が形成される。これにより、第1拡散防止膜3の一部がビアホール6から露出する。

配線溝8が形成された後には、図2(c)に示すように、層間絶縁膜5の表面(配線溝8の内面を含む)および第1拡散防止膜3の露出面を覆うように、SiO2またはSiCOからなる酸化膜15が、たとえば、プラズマCVD法により形成される。酸化膜15が形成されることにより、配線溝8の内面に凹部14(図1(b)参照)が形成されていても、その凹部14は、酸化膜15によって塞がれる。

配線溝8が形成された後には、図2(c)に示すように、層間絶縁膜5の表面(配線溝8の内面を含む)および第1拡散防止膜3の露出面を覆うように、SiO2またはSiCOからなる酸化膜15が、たとえば、プラズマCVD法により形成される。酸化膜15が形成されることにより、配線溝8の内面に凹部14(図1(b)参照)が形成されていても、その凹部14は、酸化膜15によって塞がれる。

次いで、図2(d)に示すように、酸化膜15および第1拡散防止膜3が、第1拡散防止膜3の膜厚方向にエッチングされる。これらの膜のエッチングは、たとえば、ドライエッチングにより達成される。これにより、層間絶縁膜5およびトレンチ7上の酸化膜15は除去されて、残存した酸化膜15がビアホール6の側面6Bおよびトレンチ7の側面7Bを覆う第1バリア膜9になる。また、第1Cu配線2上の第1拡散防止膜3が除去されて、第1Cu配線2の上面が露出する。

続いて、図2(e)に示すように、たとえば、スパッタ法により、配線溝8の内面(第1バリア膜9の表面、トレンチ7の底面7Aおよび第1Cu配線2の露出面)を含む層間絶縁膜5の表面全域に、たとえば、CuとMnとの合金からなる合金膜16が被着される。この合金膜16には、たとえば、1原子%〜5原子%のMnが含まれている。また、合金膜16は、たとえば、トレンチ7の幅W1が100nm〜1000nm、ビアホール6の幅W2が100nm〜300nmの場合には、60nm〜100nmの膜厚となるように形成される。

次に、図2(f)に示すように、たとえば、めっき法により、合金膜16(層間絶縁膜5)上に、Cu膜17が形成される。このCu膜17は、配線溝8を埋め尽くし、合金膜16の表面全域を覆う厚みで形成される。

その後、層間絶縁膜5、第1バリア膜9、合金膜16、Cu膜17などを含む構造物がアニール炉(図示せず)に搬入され、N2(窒素)雰囲気下において、たとえば、400℃の温度条件で30分間にわたる熱処理(アニール処理)が行なわれる。この熱処理によって、図2(g)に示すように、合金膜16中のMnが、層間絶縁膜5および第1バリア膜9中のSiおよびOと結合し、合金膜16と層間絶縁膜5および第1バリア膜9との界面に、MnxSiyOz(x,y,z:零よりも大きい数)からなる合金膜16が形成される。

その後、層間絶縁膜5、第1バリア膜9、合金膜16、Cu膜17などを含む構造物がアニール炉(図示せず)に搬入され、N2(窒素)雰囲気下において、たとえば、400℃の温度条件で30分間にわたる熱処理(アニール処理)が行なわれる。この熱処理によって、図2(g)に示すように、合金膜16中のMnが、層間絶縁膜5および第1バリア膜9中のSiおよびOと結合し、合金膜16と層間絶縁膜5および第1バリア膜9との界面に、MnxSiyOz(x,y,z:零よりも大きい数)からなる合金膜16が形成される。

次いで、CMP(Chemical Mechanical Polishing:化学的機械的研磨)法により、Cu膜17および合金膜16が研磨される。この研磨処理は、図2(h)に示すように、Cu膜17および合金膜16の配線溝8外に形成されている不要部分がすべて除去される。つまり、配線溝8外の層間絶縁膜5の表面が露出し、その層間絶縁膜5の表面と配線溝8内のCu膜17の表面とが面一になるまで続けられる。これにより、配線溝8内にのみ、Cu膜17および合金膜16が残存し、配線溝8内に残存するCu膜17は、Cu配線部19となる。また、配線溝8内に残存する合金膜16は、Cu配線部19の配線溝8との対向面(Cu配線11の底面11Aおよび側面11B、ならびに接続ビア18の底面18Aおよび側面18B)を被覆する第2バリア膜10となる。

続いて、図2(i)に示すように、第1拡散防止膜3および層間絶縁膜5と同様の方法により、第2拡散防止膜12および層間絶縁膜13が形成されて、半導体装置1が得られる。

以上のように、配線溝8の内面(トレンチ7の側面7Bおよびビアホール6の側面6B)には、SiOCより膜密度の大きいSiO2またはSiCOからなる第1バリア膜9が形成されている。そのため、第2バリア膜10を形成する際に配線溝8の内面に被着されたCuMn合金(合金膜16)が層間絶縁膜5中に浸み込むことを防止することができる。そのため、合金膜16の膜厚を薄くしても、第2バリア膜10を構成するのに十分な量のMnを確保することができる。

以上のように、配線溝8の内面(トレンチ7の側面7Bおよびビアホール6の側面6B)には、SiOCより膜密度の大きいSiO2またはSiCOからなる第1バリア膜9が形成されている。そのため、第2バリア膜10を形成する際に配線溝8の内面に被着されたCuMn合金(合金膜16)が層間絶縁膜5中に浸み込むことを防止することができる。そのため、合金膜16の膜厚を薄くしても、第2バリア膜10を構成するのに十分な量のMnを確保することができる。

また、配線溝8の内面(トレンチ7の側面7Bおよびビアホール6の側面6B)の一部に凹部14が存在する場合であっても、その凹部14は第1バリア膜9で塞がれるので、合金膜16が形成される面を平坦化させることができる。そのため、凹部14を塞いで配線溝8の内面を平坦化するために合金膜16の膜厚を厚くする必要がない。すなわち、合金膜16の膜厚を薄くすることができる。

このように、合金膜16の膜厚を薄くすることができるため、合金膜16中のMnは、第2バリア膜10を形成する際に第2バリア膜10の構成成分として余ることなく、SiおよびOと結合する。そのため、Mnの第2Cu配線11への拡散がない。その結果、第2Cu配線11の配線抵抗が増大することを防止することができる。

また、Cu配線部19は、その配線溝8との対向面(Cu配線11の底面11Aおよび側面11B、ならびに接続ビア18の底面18Aおよび側面18B)が、第2バリア膜10で被覆されている。そのため、Cu配線部19から層間絶縁膜5へのCuの拡散を防止することができる。

また、Cu配線部19は、その配線溝8との対向面(Cu配線11の底面11Aおよび側面11B、ならびに接続ビア18の底面18Aおよび側面18B)が、第2バリア膜10で被覆されている。そのため、Cu配線部19から層間絶縁膜5へのCuの拡散を防止することができる。

さらに、同一体積中における、第1バリア膜9(SiO2またはSiCO)のOの含有量と層間絶縁膜5(SiOC)のOの含有量とを比較すると、第1バリア膜のOの含有量の方が多い。そのため、合金膜16中のMnを容易にOと反応させることができるので、効率よく第2バリア膜10(MnxSiyOz)を形成することができる。

以上、この発明の一実施形態を説明したが、この発明は他の実施形態で実施することもできる。

以上、この発明の一実施形態を説明したが、この発明は他の実施形態で実施することもできる。

たとえば、前述の実施形態では、第1バリア膜9は、ビアホール6の側面6Bおよびトレンチ7の側面7Bに形成されているとしたが、図3に示すように、第1バリア膜9は、配線溝8の内面全面(ビアホール6の側面6B、トレンチ7の側面7Bおよびトレンチ7の底面7A)に形成されていてもよい。

また、前述の実施形態では、層間絶縁膜5は、SiOCからなるとしたが、層間絶縁膜5は、SiOFで形成されていてもよい。

また、前述の実施形態では、層間絶縁膜5は、SiOCからなるとしたが、層間絶縁膜5は、SiOFで形成されていてもよい。

その他、特許請求の範囲に記載された事項の範囲で種々の設計変更を施すことが可能である。

1 半導体装置

5 層間絶縁膜

6 ビアホール

6B 側面

7 トレンチ

7A 底面

7B 側面

8 配線溝

9 第1バリア膜

10 第2バリア膜

11 第2Cu配線

11A 底面

11B 側面

15 酸化膜

16 合金膜

17 Cu膜

18 接続ビア

18A 底面

18B 側面

19 Cu配線部

5 層間絶縁膜

6 ビアホール

6B 側面

7 トレンチ

7A 底面

7B 側面

8 配線溝

9 第1バリア膜

10 第2バリア膜

11 第2Cu配線

11A 底面

11B 側面

15 酸化膜

16 合金膜

17 Cu膜

18 接続ビア

18A 底面

18B 側面

19 Cu配線部

Claims (8)

- Cuを主成分とする第1Cu配線と、

前記第1Cu配線上に形成され、SiO2より比誘電率の小さい低誘電率材料からなる絶縁膜と、

前記絶縁膜に、その表面から膜厚方向に貫通するように形成され、内部に前記第1Cu配線の上面が露出した配線溝と、

前記配線溝の少なくとも側面上に形成され、SiO2またはSiCOからなり、前記絶縁膜よりも膜密度が大きい第1バリア膜と、

前記配線溝に埋設され、前記第1Cu配線に電気的に接続されたCuを主成分とする第2Cu配線と、

前記第1Cu配線の前記上面を含む前記第2Cu配線の前記配線溝との対向面を被覆し、Si、OおよびMnを含む化合物からなる第2バリア膜と、を含む、半導体装置。 - 前記配線溝は、前記絶縁膜の表層部に形成されたトレンチと、前記トレンチの底面から前記第1Cu配線に達するビアホールとを含み、

前記第1バリア膜は、前記トレンチの前記底面を露出させるように形成されており、

前記第2バリア膜は、露出した前記トレンチの前記底面に接するように形成されている、請求項1に記載の半導体装置。 - 前記第1バリア膜が、Cを含有している、請求項1に記載の半導体装置。

- 前記第1バリア膜の元素含有量は、Cの含有量が50原子%〜70原子%、Oの含有量が4原子%〜11原子%である、請求項3に記載の半導体装置。

- 前記絶縁膜が、SiOCまたはSiOFからなる、請求項1〜4のいずれか一項に記載の半導体装置。

- 前記配線溝に埋設された前記第2Cu配線上には、拡散防止膜が形成されている、請求項1〜5のいずれか一項に記載の半導体装置。

- 前記拡散防止膜が、SiCからなる、請求項6に記載の半導体装置。

- 前記配線溝の前記側面に複数の凹部が形成されており、

前記凹部は、前記第1バリア膜により塞がれている、請求項1〜7のいずれか一項に記載の半導体装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007135160AJP5089244B2 (ja) | 2007-05-22 | 2007-05-22 | 半導体装置 |

| TW097118519ATW200849474A (en) | 2007-05-22 | 2008-05-20 | Semiconductor device |

| KR1020080046538AKR20080102983A (ko) | 2007-05-22 | 2008-05-20 | 반도체 장치 |

| US12/153,587US8198732B2 (en) | 2007-05-22 | 2008-05-21 | Semiconductor device |

| CN2008101079443ACN101312179B (zh) | 2007-05-22 | 2008-05-21 | 半导体器件 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007135160AJP5089244B2 (ja) | 2007-05-22 | 2007-05-22 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008294040A JP2008294040A (ja) | 2008-12-04 |

| JP5089244B2true JP5089244B2 (ja) | 2012-12-05 |

Family

ID=40071650

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007135160AExpired - Fee RelatedJP5089244B2 (ja) | 2007-05-22 | 2007-05-22 | 半導体装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8198732B2 (ja) |

| JP (1) | JP5089244B2 (ja) |

| KR (1) | KR20080102983A (ja) |

| CN (1) | CN101312179B (ja) |

| TW (1) | TW200849474A (ja) |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4589835B2 (ja)* | 2005-07-13 | 2010-12-01 | 富士通セミコンダクター株式会社 | 半導体装置の製造方法及び半導体装置 |

| WO2009001780A1 (ja)* | 2007-06-22 | 2008-12-31 | Rohm Co., Ltd. | 半導体装置およびその製造方法 |

| JP4415100B1 (ja)* | 2008-12-19 | 2010-02-17 | 国立大学法人東北大学 | 銅配線、半導体装置および銅配線形成方法 |

| US8168528B2 (en)* | 2009-06-18 | 2012-05-01 | Kabushiki Kaisha Toshiba | Restoration method using metal for better CD controllability and Cu filing |

| US8653664B2 (en) | 2009-07-08 | 2014-02-18 | Taiwan Semiconductor Manufacturing Company, Ltd. | Barrier layers for copper interconnect |

| US8653663B2 (en)* | 2009-10-29 | 2014-02-18 | Taiwan Semiconductor Manufacturing Company, Ltd. | Barrier layer for copper interconnect |

| US8461683B2 (en)* | 2011-04-01 | 2013-06-11 | Intel Corporation | Self-forming, self-aligned barriers for back-end interconnects and methods of making same |

| JP5930416B2 (ja)* | 2011-12-28 | 2016-06-08 | 国立大学法人東北大学 | 配線構造体、配線構造体を備えた半導体装置及びその半導体装置の製造方法 |

| WO2013125647A1 (ja)* | 2012-02-22 | 2013-08-29 | 東京エレクトロン株式会社 | 半導体装置の製造方法及び半導体装置 |

| US9343357B2 (en)* | 2014-02-28 | 2016-05-17 | Qualcomm Incorporated | Selective conductive barrier layer formation |

| US9418889B2 (en)* | 2014-06-30 | 2016-08-16 | Lam Research Corporation | Selective formation of dielectric barriers for metal interconnects in semiconductor devices |

| US9224686B1 (en)* | 2014-09-10 | 2015-12-29 | International Business Machines Corporation | Single damascene interconnect structure |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3716218B2 (ja)* | 2002-03-06 | 2005-11-16 | 富士通株式会社 | 配線構造及びその形成方法 |

| US6987059B1 (en)* | 2003-08-14 | 2006-01-17 | Lsi Logic Corporation | Method and structure for creating ultra low resistance damascene copper wiring |

| US7169698B2 (en)* | 2004-01-14 | 2007-01-30 | International Business Machines Corporation | Sacrificial inorganic polymer intermetal dielectric damascene wire and via liner |

| JP4478038B2 (ja) | 2004-02-27 | 2010-06-09 | 株式会社半導体理工学研究センター | 半導体装置及びその製造方法 |

| JP4679193B2 (ja)* | 2005-03-22 | 2011-04-27 | 株式会社東芝 | 半導体装置の製造方法及び半導体装置 |

| JP2007027347A (ja)* | 2005-07-15 | 2007-02-01 | Sony Corp | 半導体装置およびその製造方法 |

| JP4272191B2 (ja)* | 2005-08-30 | 2009-06-03 | 富士通マイクロエレクトロニクス株式会社 | 半導体装置の製造方法 |

- 2007

- 2007-05-22JPJP2007135160Apatent/JP5089244B2/janot_activeExpired - Fee Related

- 2008

- 2008-05-20KRKR1020080046538Apatent/KR20080102983A/konot_activeWithdrawn

- 2008-05-20TWTW097118519Apatent/TW200849474A/zhunknown

- 2008-05-21USUS12/153,587patent/US8198732B2/ennot_activeExpired - Fee Related

- 2008-05-21CNCN2008101079443Apatent/CN101312179B/zhnot_activeExpired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2008294040A (ja) | 2008-12-04 |

| US8198732B2 (en) | 2012-06-12 |

| KR20080102983A (ko) | 2008-11-26 |

| CN101312179B (zh) | 2013-03-20 |

| TW200849474A (en) | 2008-12-16 |

| US20080290517A1 (en) | 2008-11-27 |

| CN101312179A (zh) | 2008-11-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5089244B2 (ja) | 半導体装置 | |

| JP4741965B2 (ja) | 半導体装置およびその製造方法 | |

| JP4478038B2 (ja) | 半導体装置及びその製造方法 | |

| JP4819501B2 (ja) | 配線構造およびその製造方法 | |

| TWI440135B (zh) | 半導體裝置及半導體裝置之製造方法 | |

| US8102051B2 (en) | Semiconductor device having an electrode and method for manufacturing the same | |

| US9704740B2 (en) | Semiconductor device having insulating layers containing oxygen and a barrier layer containing manganese | |

| JP2009147137A (ja) | 半導体装置およびその製造方法 | |

| KR20030035909A (ko) | 반도체장치 및 그 제조방법 | |

| US20070023917A1 (en) | Semiconductor device having multilayer wiring lines and manufacturing method thereof | |

| JP2006019480A (ja) | 半導体装置の製造方法 | |

| JP2009141058A (ja) | 半導体装置およびその製造方法 | |

| JP5214913B2 (ja) | 半導体装置 | |

| JP3715626B2 (ja) | 半導体装置の製造方法および半導体装置 | |

| JP5190415B2 (ja) | 半導体装置 | |

| CN100380627C (zh) | 半导体器件及其制造方法 | |

| JP2007335578A (ja) | 半導体装置及びその製造方法 | |

| JP2006253666A (ja) | 半導体装置およびその製造方法 | |

| JP2008294403A (ja) | 半導体装置 | |

| JP4383262B2 (ja) | 半導体装置及びその製造方法 | |

| JP2008258311A (ja) | 半導体装置及び半導体装置の配線または電極形成方法 | |

| JP2012009617A (ja) | 半導体装置の製造方法、配線用銅合金、及び半導体装置 | |

| JP2010003906A (ja) | 半導体装置及びその製造方法 | |

| JP2006196642A (ja) | 半導体装置およびその製造方法 | |

| JP5288734B2 (ja) | 半導体装置およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination | Free format text:JAPANESE INTERMEDIATE CODE: A621 Effective date:20100512 | |

| A977 | Report on retrieval | Free format text:JAPANESE INTERMEDIATE CODE: A971007 Effective date:20120621 | |

| A131 | Notification of reasons for refusal | Free format text:JAPANESE INTERMEDIATE CODE: A131 Effective date:20120628 | |

| A521 | Written amendment | Free format text:JAPANESE INTERMEDIATE CODE: A523 Effective date:20120809 | |

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) | Free format text:JAPANESE INTERMEDIATE CODE: A01 Effective date:20120830 | |

| A01 | Written decision to grant a patent or to grant a registration (utility model) | Free format text:JAPANESE INTERMEDIATE CODE: A01 | |

| A61 | First payment of annual fees (during grant procedure) | Free format text:JAPANESE INTERMEDIATE CODE: A61 Effective date:20120911 | |

| FPAY | Renewal fee payment (event date is renewal date of database) | Free format text:PAYMENT UNTIL: 20150921 Year of fee payment:3 | |

| R150 | Certificate of patent or registration of utility model | Free format text:JAPANESE INTERMEDIATE CODE: R150 | |

| LAPS | Cancellation because of no payment of annual fees |