JP2018146730A - 表示装置、および表示装置の動作方法 - Google Patents

表示装置、および表示装置の動作方法Download PDFInfo

- Publication number

- JP2018146730A JP2018146730AJP2017040853AJP2017040853AJP2018146730AJP 2018146730 AJP2018146730 AJP 2018146730AJP 2017040853 AJP2017040853 AJP 2017040853AJP 2017040853 AJP2017040853 AJP 2017040853AJP 2018146730 AJP2018146730 AJP 2018146730A

- Authority

- JP

- Japan

- Prior art keywords

- scan chain

- image data

- register

- frame memory

- function

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 238000011017operating methodMethods0.000title1

- 238000012545processingMethods0.000claimsabstractdescription236

- 230000006870functionEffects0.000claimsabstractdescription166

- 230000015654memoryEffects0.000claimsabstractdescription153

- 239000004065semiconductorSubstances0.000claimsabstractdescription97

- 230000015572biosynthetic processEffects0.000claimsabstractdescription24

- 238000000034methodMethods0.000claimsdescription71

- 238000001514detection methodMethods0.000claimsdescription46

- 238000011068loading methodMethods0.000claimsdescription12

- 238000006243chemical reactionMethods0.000claimsdescription9

- 238000003909pattern recognitionMethods0.000claimsdescription6

- 230000003247decreasing effectEffects0.000abstract1

- 239000010410layerSubstances0.000description277

- 239000000758substrateSubstances0.000description70

- 239000004973liquid crystal related substanceSubstances0.000description63

- 229910044991metal oxideInorganic materials0.000description28

- 239000003990capacitorSubstances0.000description26

- 239000010408filmSubstances0.000description25

- 239000000463materialSubstances0.000description25

- 238000012937correctionMethods0.000description24

- 208000003443UnconsciousnessDiseases0.000description23

- 230000008569processEffects0.000description22

- 239000011701zincSubstances0.000description22

- 229910021417amorphous siliconInorganic materials0.000description21

- 230000007246mechanismEffects0.000description21

- 150000004706metal oxidesChemical class0.000description20

- 230000003287optical effectEffects0.000description19

- 230000008859changeEffects0.000description17

- 229910021420polycrystalline siliconInorganic materials0.000description17

- 238000010586diagramMethods0.000description16

- 101100420795Schizosaccharomyces pombe (strain 972 / ATCC 24843) sck1 geneProteins0.000description15

- PXHVJJICTQNCMI-UHFFFAOYSA-NNickelChemical compound[Ni]PXHVJJICTQNCMI-UHFFFAOYSA-N0.000description14

- 101001022948Homo sapiens LIM domain-binding protein 2Proteins0.000description12

- 102100035113LIM domain-binding protein 2Human genes0.000description12

- 230000000694effectsEffects0.000description11

- 229910052738indiumInorganic materials0.000description11

- 241000283973Oryctolagus cuniculusSpecies0.000description10

- 239000013078crystalSubstances0.000description10

- 229920005989resinPolymers0.000description10

- 239000011347resinSubstances0.000description10

- 101000631899Homo sapiens Ribosome maturation protein SBDSProteins0.000description9

- 102100028750Ribosome maturation protein SBDSHuman genes0.000description9

- 229910052733galliumInorganic materials0.000description9

- APFVFJFRJDLVQX-UHFFFAOYSA-Nindium atomChemical compound[In]APFVFJFRJDLVQX-UHFFFAOYSA-N0.000description9

- 230000001629suppressionEffects0.000description9

- 101100309620Schizosaccharomyces pombe (strain 972 / ATCC 24843) sck2 geneProteins0.000description8

- 229910052751metalInorganic materials0.000description8

- IJGRMHOSHXDMSA-UHFFFAOYSA-NAtomic nitrogenChemical compoundN#NIJGRMHOSHXDMSA-UHFFFAOYSA-N0.000description7

- 101001022957Homo sapiens LIM domain-binding protein 1Proteins0.000description7

- 239000012790adhesive layerSubstances0.000description7

- 239000011159matrix materialSubstances0.000description7

- 239000002184metalSubstances0.000description7

- 239000002245particleSubstances0.000description7

- 230000002093peripheral effectEffects0.000description7

- 102100033270Cyclin-dependent kinase inhibitor 1Human genes0.000description6

- GYHNNYVSQQEPJS-UHFFFAOYSA-NGalliumChemical compound[Ga]GYHNNYVSQQEPJS-UHFFFAOYSA-N0.000description6

- 101000944380Homo sapiens Cyclin-dependent kinase inhibitor 1Proteins0.000description6

- XLOMVQKBTHCTTD-UHFFFAOYSA-NZinc monoxideChemical compound[Zn]=OXLOMVQKBTHCTTD-UHFFFAOYSA-N0.000description6

- 229910052782aluminiumInorganic materials0.000description6

- 238000004891communicationMethods0.000description6

- 150000001875compoundsChemical class0.000description6

- 230000005669field effectEffects0.000description6

- 230000014509gene expressionEffects0.000description6

- 230000001678irradiating effectEffects0.000description6

- 238000004519manufacturing processMethods0.000description6

- 229910052759nickelInorganic materials0.000description6

- 229910052760oxygenInorganic materials0.000description6

- 238000011084recoveryMethods0.000description6

- 125000006850spacer groupChemical group0.000description6

- 239000000126substanceSubstances0.000description6

- 239000010936titaniumSubstances0.000description6

- XEEYBQQBJWHFJM-UHFFFAOYSA-NIronChemical compound[Fe]XEEYBQQBJWHFJM-UHFFFAOYSA-N0.000description5

- XAGFODPZIPBFFR-UHFFFAOYSA-NaluminiumChemical compound[Al]XAGFODPZIPBFFR-UHFFFAOYSA-N0.000description5

- 238000003491arrayMethods0.000description5

- 239000003086colorantSubstances0.000description5

- 230000000295complement effectEffects0.000description5

- 230000007423decreaseEffects0.000description5

- 239000011521glassSubstances0.000description5

- 239000001257hydrogenSubstances0.000description5

- 229910052739hydrogenInorganic materials0.000description5

- 238000003384imaging methodMethods0.000description5

- 239000012535impuritySubstances0.000description5

- 238000005499laser crystallizationMethods0.000description5

- VYPSYNLAJGMNEJ-UHFFFAOYSA-Nsilicon dioxideInorganic materialsO=[Si]=OVYPSYNLAJGMNEJ-UHFFFAOYSA-N0.000description5

- 229910052727yttriumInorganic materials0.000description5

- 229910052725zincInorganic materials0.000description5

- XKRFYHLGVUSROY-UHFFFAOYSA-NArgonChemical compound[Ar]XKRFYHLGVUSROY-UHFFFAOYSA-N0.000description4

- UFHFLCQGNIYNRP-UHFFFAOYSA-NHydrogenChemical compound[H][H]UFHFLCQGNIYNRP-UHFFFAOYSA-N0.000description4

- ZOKXTWBITQBERF-UHFFFAOYSA-NMolybdenumChemical compound[Mo]ZOKXTWBITQBERF-UHFFFAOYSA-N0.000description4

- 101100528972Saccharomyces cerevisiae (strain ATCC 204508 / S288c) RPD3 geneProteins0.000description4

- XUIMIQQOPSSXEZ-UHFFFAOYSA-NSiliconChemical compound[Si]XUIMIQQOPSSXEZ-UHFFFAOYSA-N0.000description4

- RTAQQCXQSZGOHL-UHFFFAOYSA-NTitaniumChemical compound[Ti]RTAQQCXQSZGOHL-UHFFFAOYSA-N0.000description4

- QVGXLLKOCUKJST-UHFFFAOYSA-Natomic oxygenChemical compound[O]QVGXLLKOCUKJST-UHFFFAOYSA-N0.000description4

- 239000000969carrierSubstances0.000description4

- 238000004040coloringMethods0.000description4

- 239000002131composite materialSubstances0.000description4

- 239000010949copperSubstances0.000description4

- 239000000945fillerSubstances0.000description4

- 229910052735hafniumInorganic materials0.000description4

- VBJZVLUMGGDVMO-UHFFFAOYSA-Nhafnium atomChemical compound[Hf]VBJZVLUMGGDVMO-UHFFFAOYSA-N0.000description4

- 239000000203mixtureSubstances0.000description4

- 229910052750molybdenumInorganic materials0.000description4

- 239000011733molybdenumSubstances0.000description4

- 239000001301oxygenSubstances0.000description4

- 230000000630rising effectEffects0.000description4

- 229910052710siliconInorganic materials0.000description4

- 239000010703siliconSubstances0.000description4

- 229910052715tantalumInorganic materials0.000description4

- GUVRBAGPIYLISA-UHFFFAOYSA-Ntantalum atomChemical compound[Ta]GUVRBAGPIYLISA-UHFFFAOYSA-N0.000description4

- 229910052719titaniumInorganic materials0.000description4

- WFKWXMTUELFFGS-UHFFFAOYSA-NtungstenChemical compound[W]WFKWXMTUELFFGS-UHFFFAOYSA-N0.000description4

- 229910052721tungstenInorganic materials0.000description4

- 239000010937tungstenSubstances0.000description4

- ZOXJGFHDIHLPTG-UHFFFAOYSA-NBoronChemical compound[B]ZOXJGFHDIHLPTG-UHFFFAOYSA-N0.000description3

- 229910052684CeriumInorganic materials0.000description3

- RYGMFSIKBFXOCR-UHFFFAOYSA-NCopperChemical compound[Cu]RYGMFSIKBFXOCR-UHFFFAOYSA-N0.000description3

- MYMOFIZGZYHOMD-UHFFFAOYSA-NDioxygenChemical compoundO=OMYMOFIZGZYHOMD-UHFFFAOYSA-N0.000description3

- 206010052128GlareDiseases0.000description3

- 229910052779NeodymiumInorganic materials0.000description3

- 239000004983Polymer Dispersed Liquid CrystalSubstances0.000description3

- HCHKCACWOHOZIP-UHFFFAOYSA-NZincChemical compound[Zn]HCHKCACWOHOZIP-UHFFFAOYSA-N0.000description3

- 230000009471actionEffects0.000description3

- 229910052796boronInorganic materials0.000description3

- GWXLDORMOJMVQZ-UHFFFAOYSA-NceriumChemical compound[Ce]GWXLDORMOJMVQZ-UHFFFAOYSA-N0.000description3

- 238000000576coating methodMethods0.000description3

- 229920001940conductive polymerPolymers0.000description3

- 239000004020conductorSubstances0.000description3

- 229910052802copperInorganic materials0.000description3

- 238000009792diffusion processMethods0.000description3

- 229910001882dioxygenInorganic materials0.000description3

- 238000009826distributionMethods0.000description3

- 230000009977dual effectEffects0.000description3

- 238000010894electron beam technologyMethods0.000description3

- 238000002149energy-dispersive X-ray emission spectroscopyMethods0.000description3

- 229910052732germaniumInorganic materials0.000description3

- GNPVGFCGXDBREM-UHFFFAOYSA-Ngermanium atomChemical compound[Ge]GNPVGFCGXDBREM-UHFFFAOYSA-N0.000description3

- 229910003437indium oxideInorganic materials0.000description3

- PJXISJQVUVHSOJ-UHFFFAOYSA-Nindium(iii) oxideChemical compound[O-2].[O-2].[O-2].[In+3].[In+3]PJXISJQVUVHSOJ-UHFFFAOYSA-N0.000description3

- 229910052746lanthanumInorganic materials0.000description3

- FZLIPJUXYLNCLC-UHFFFAOYSA-Nlanthanum atomChemical compound[La]FZLIPJUXYLNCLC-UHFFFAOYSA-N0.000description3

- 239000007769metal materialSubstances0.000description3

- 239000002105nanoparticleSubstances0.000description3

- QEFYFXOXNSNQGX-UHFFFAOYSA-Nneodymium atomChemical compound[Nd]QEFYFXOXNSNQGX-UHFFFAOYSA-N0.000description3

- 229910052757nitrogenInorganic materials0.000description3

- 230000001151other effectEffects0.000description3

- 238000005192partitionMethods0.000description3

- BASFCYQUMIYNBI-UHFFFAOYSA-NplatinumChemical compound[Pt]BASFCYQUMIYNBI-UHFFFAOYSA-N0.000description3

- 239000010409thin filmSubstances0.000description3

- 230000007704transitionEffects0.000description3

- 230000000007visual effectEffects0.000description3

- VWQVUPCCIRVNHF-UHFFFAOYSA-Nyttrium atomChemical compound[Y]VWQVUPCCIRVNHF-UHFFFAOYSA-N0.000description3

- YVTHLONGBIQYBO-UHFFFAOYSA-Nzinc indium(3+) oxygen(2-)Chemical compound[O--].[Zn++].[In+3]YVTHLONGBIQYBO-UHFFFAOYSA-N0.000description3

- 239000011787zinc oxideSubstances0.000description3

- PAYRUJLWNCNPSJ-UHFFFAOYSA-NAnilineChemical compoundNC1=CC=CC=C1PAYRUJLWNCNPSJ-UHFFFAOYSA-N0.000description2

- 238000012935AveragingMethods0.000description2

- CURLTUGMZLYLDI-UHFFFAOYSA-NCarbon dioxideChemical compoundO=C=OCURLTUGMZLYLDI-UHFFFAOYSA-N0.000description2

- FYYHWMGAXLPEAU-UHFFFAOYSA-NMagnesiumChemical compound[Mg]FYYHWMGAXLPEAU-UHFFFAOYSA-N0.000description2

- KAESVJOAVNADME-UHFFFAOYSA-NPyrroleChemical compoundC=1C=CNC=1KAESVJOAVNADME-UHFFFAOYSA-N0.000description2

- 229910052581Si3N4Inorganic materials0.000description2

- YTPLMLYBLZKORZ-UHFFFAOYSA-NThiopheneChemical compoundC=1C=CSC=1YTPLMLYBLZKORZ-UHFFFAOYSA-N0.000description2

- ATJFFYVFTNAWJD-UHFFFAOYSA-NTinChemical compound[Sn]ATJFFYVFTNAWJD-UHFFFAOYSA-N0.000description2

- GWEVSGVZZGPLCZ-UHFFFAOYSA-NTitan oxideChemical compoundO=[Ti]=OGWEVSGVZZGPLCZ-UHFFFAOYSA-N0.000description2

- 238000002441X-ray diffractionMethods0.000description2

- QCWXUUIWCKQGHC-UHFFFAOYSA-NZirconiumChemical compound[Zr]QCWXUUIWCKQGHC-UHFFFAOYSA-N0.000description2

- 238000004458analytical methodMethods0.000description2

- 229910052786argonInorganic materials0.000description2

- 238000013473artificial intelligenceMethods0.000description2

- 238000013528artificial neural networkMethods0.000description2

- 229910052790berylliumInorganic materials0.000description2

- ATBAMAFKBVZNFJ-UHFFFAOYSA-Nberyllium atomChemical compound[Be]ATBAMAFKBVZNFJ-UHFFFAOYSA-N0.000description2

- 230000005540biological transmissionEffects0.000description2

- 230000000903blocking effectEffects0.000description2

- DQXBYHZEEUGOBF-UHFFFAOYSA-Nbut-3-enoic acid;etheneChemical compoundC=C.OC(=O)CC=CDQXBYHZEEUGOBF-UHFFFAOYSA-N0.000description2

- 238000004364calculation methodMethods0.000description2

- 239000011651chromiumSubstances0.000description2

- 239000011248coating agentSubstances0.000description2

- 230000006835compressionEffects0.000description2

- 238000007906compressionMethods0.000description2

- PMHQVHHXPFUNSP-UHFFFAOYSA-Mcopper(1+);methylsulfanylmethane;bromideChemical compoundBr[Cu].CSCPMHQVHHXPFUNSP-UHFFFAOYSA-M0.000description2

- 238000000151depositionMethods0.000description2

- 230000008021depositionEffects0.000description2

- 239000002274desiccantSubstances0.000description2

- 239000010432diamondSubstances0.000description2

- 229910003460diamondInorganic materials0.000description2

- 230000005684electric fieldEffects0.000description2

- 239000005038ethylene vinyl acetateSubstances0.000description2

- 230000005281excited stateEffects0.000description2

- 239000005262ferroelectric liquid crystals (FLCs)Substances0.000description2

- 239000007789gasSubstances0.000description2

- 230000004313glareEffects0.000description2

- PCHJSUWPFVWCPO-UHFFFAOYSA-NgoldChemical compound[Au]PCHJSUWPFVWCPO-UHFFFAOYSA-N0.000description2

- 229910052737goldInorganic materials0.000description2

- 239000010931goldSubstances0.000description2

- 230000012447hatchingEffects0.000description2

- 238000010438heat treatmentMethods0.000description2

- AMGQUBHHOARCQH-UHFFFAOYSA-Nindium;oxotinChemical compound[In].[Sn]=OAMGQUBHHOARCQH-UHFFFAOYSA-N0.000description2

- 239000011261inert gasSubstances0.000description2

- 239000011810insulating materialSubstances0.000description2

- 238000009413insulationMethods0.000description2

- 229910052742ironInorganic materials0.000description2

- 229910052749magnesiumInorganic materials0.000description2

- 239000011777magnesiumSubstances0.000description2

- 238000002156mixingMethods0.000description2

- 239000002159nanocrystalSubstances0.000description2

- 239000010955niobiumSubstances0.000description2

- QGLKJKCYBOYXKC-UHFFFAOYSA-NnonaoxidotritungstenChemical compoundO=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1QGLKJKCYBOYXKC-UHFFFAOYSA-N0.000description2

- 229920001200poly(ethylene-vinyl acetate)Polymers0.000description2

- 229920002037poly(vinyl butyral) polymerPolymers0.000description2

- 229920000915polyvinyl chloridePolymers0.000description2

- 239000004800polyvinyl chlorideSubstances0.000description2

- 230000001681protective effectEffects0.000description2

- 239000011241protective layerSubstances0.000description2

- 239000000565sealantSubstances0.000description2

- 239000003566sealing materialSubstances0.000description2

- VSZWPYCFIRKVQL-UHFFFAOYSA-Nselanylidenegallium;seleniumChemical compound[Se].[Se]=[Ga].[Se]=[Ga]VSZWPYCFIRKVQL-UHFFFAOYSA-N0.000description2

- 230000035945sensitivityEffects0.000description2

- HQVNEWCFYHHQES-UHFFFAOYSA-Nsilicon nitrideChemical compoundN12[Si]34N5[Si]62N3[Si]51N64HQVNEWCFYHHQES-UHFFFAOYSA-N0.000description2

- 238000004544sputter depositionMethods0.000description2

- JBQYATWDVHIOAR-UHFFFAOYSA-NtellanylidenegermaniumChemical compound[Te]=[Ge]JBQYATWDVHIOAR-UHFFFAOYSA-N0.000description2

- 229920001187thermosetting polymerPolymers0.000description2

- 229910001887tin oxideInorganic materials0.000description2

- OGIDPMRJRNCKJF-UHFFFAOYSA-Ntitanium oxideInorganic materials[Ti]=OOGIDPMRJRNCKJF-UHFFFAOYSA-N0.000description2

- 229910001930tungsten oxideInorganic materials0.000description2

- 229910052720vanadiumInorganic materials0.000description2

- GPPXJZIENCGNKB-UHFFFAOYSA-NvanadiumChemical compound[V]#[V]GPPXJZIENCGNKB-UHFFFAOYSA-N0.000description2

- 238000007740vapor depositionMethods0.000description2

- 229910052726zirconiumInorganic materials0.000description2

- 239000004925Acrylic resinSubstances0.000description1

- 229920000178Acrylic resinPolymers0.000description1

- OKTJSMMVPCPJKN-UHFFFAOYSA-NCarbonChemical compound[C]OKTJSMMVPCPJKN-UHFFFAOYSA-N0.000description1

- VYZAMTAEIAYCRO-UHFFFAOYSA-NChromiumChemical compound[Cr]VYZAMTAEIAYCRO-UHFFFAOYSA-N0.000description1

- 229910002601GaNInorganic materials0.000description1

- JMASRVWKEDWRBT-UHFFFAOYSA-NGallium nitrideChemical compound[Ga]#NJMASRVWKEDWRBT-UHFFFAOYSA-N0.000description1

- 239000005264High molar mass liquid crystalSubstances0.000description1

- 239000004642PolyimideSubstances0.000description1

- BQCADISMDOOEFD-UHFFFAOYSA-NSilverChemical compound[Ag]BQCADISMDOOEFD-UHFFFAOYSA-N0.000description1

- 239000004990Smectic liquid crystalSubstances0.000description1

- 239000004974Thermotropic liquid crystalSubstances0.000description1

- 230000001133accelerationEffects0.000description1

- 229910045601alloyInorganic materials0.000description1

- 239000000956alloySubstances0.000description1

- 238000013459approachMethods0.000description1

- 230000004888barrier functionEffects0.000description1

- 238000005452bendingMethods0.000description1

- 230000008901benefitEffects0.000description1

- 239000011230binding agentSubstances0.000description1

- 229910052799carbonInorganic materials0.000description1

- 229910002092carbon dioxideInorganic materials0.000description1

- 239000001569carbon dioxideSubstances0.000description1

- 230000001413cellular effectEffects0.000description1

- 238000012508change requestMethods0.000description1

- 230000003098cholesteric effectEffects0.000description1

- 229910052804chromiumInorganic materials0.000description1

- 229910017052cobaltInorganic materials0.000description1

- 239000010941cobaltSubstances0.000description1

- GUTLYIVDDKVIGB-UHFFFAOYSA-Ncobalt atomChemical compound[Co]GUTLYIVDDKVIGB-UHFFFAOYSA-N0.000description1

- 229920001577copolymerPolymers0.000description1

- 229910021419crystalline siliconInorganic materials0.000description1

- 238000002425crystallisationMethods0.000description1

- 238000007872degassingMethods0.000description1

- 229910001873dinitrogenInorganic materials0.000description1

- 238000006073displacement reactionMethods0.000description1

- 238000005401electroluminescenceMethods0.000description1

- 238000002524electron diffraction dataMethods0.000description1

- 230000005686electrostatic fieldEffects0.000description1

- 230000002708enhancing effectEffects0.000description1

- 239000003822epoxy resinSubstances0.000description1

- 238000005530etchingMethods0.000description1

- 230000005284excitationEffects0.000description1

- 230000001747exhibiting effectEffects0.000description1

- 239000000284extractSubstances0.000description1

- 230000004438eyesightEffects0.000description1

- 239000000835fiberSubstances0.000description1

- 239000012530fluidSubstances0.000description1

- YZZNJYQZJKSEER-UHFFFAOYSA-Ngallium tinChemical compound[Ga].[Sn]YZZNJYQZJKSEER-UHFFFAOYSA-N0.000description1

- 230000005283ground stateEffects0.000description1

- 150000002431hydrogenChemical class0.000description1

- 229910010272inorganic materialInorganic materials0.000description1

- 239000011147inorganic materialSubstances0.000description1

- 239000012212insulatorSubstances0.000description1

- 239000007788liquidSubstances0.000description1

- 230000005389magnetismEffects0.000description1

- 238000013507mappingMethods0.000description1

- 238000005259measurementMethods0.000description1

- 238000000691measurement methodMethods0.000description1

- 229910021645metal ionInorganic materials0.000description1

- 239000011156metal matrix compositeSubstances0.000description1

- 150000002739metalsChemical class0.000description1

- 239000003094microcapsuleSubstances0.000description1

- 230000004048modificationEffects0.000description1

- 238000012986modificationMethods0.000description1

- -1moistureChemical compound0.000description1

- 230000006855networkingEffects0.000description1

- 229910052758niobiumInorganic materials0.000description1

- GUCVJGMIXFAOAE-UHFFFAOYSA-Nniobium atomChemical compound[Nb]GUCVJGMIXFAOAE-UHFFFAOYSA-N0.000description1

- 150000004767nitridesChemical class0.000description1

- 239000012788optical filmSubstances0.000description1

- 150000002894organic compoundsChemical group0.000description1

- 230000010355oscillationEffects0.000description1

- TWNQGVIAIRXVLR-UHFFFAOYSA-Noxo(oxoalumanyloxy)alumaneChemical compoundO=[Al]O[Al]=OTWNQGVIAIRXVLR-UHFFFAOYSA-N0.000description1

- KYKLWYKWCAYAJY-UHFFFAOYSA-Noxotin;zincChemical compound[Zn].[Sn]=OKYKLWYKWCAYAJY-UHFFFAOYSA-N0.000description1

- 229910052697platinumInorganic materials0.000description1

- 229920000767polyanilinePolymers0.000description1

- 229920000647polyepoxidePolymers0.000description1

- 229920001721polyimidePolymers0.000description1

- 229920000642polymerPolymers0.000description1

- 229920000128polypyrrolePolymers0.000description1

- 229920000123polythiophenePolymers0.000description1

- 238000005381potential energyMethods0.000description1

- 238000007639printingMethods0.000description1

- 239000002096quantum dotSubstances0.000description1

- 239000010453quartzSubstances0.000description1

- 230000005855radiationEffects0.000description1

- 230000006798recombinationEffects0.000description1

- 238000005215recombinationMethods0.000description1

- 238000009877renderingMethods0.000description1

- 239000000523sampleSubstances0.000description1

- 238000007493shaping processMethods0.000description1

- HBMJWWWQQXIZIP-UHFFFAOYSA-Nsilicon carbideChemical compound[Si+]#[C-]HBMJWWWQQXIZIP-UHFFFAOYSA-N0.000description1

- 229910010271silicon carbideInorganic materials0.000description1

- 239000000377silicon dioxideSubstances0.000description1

- 229910052814silicon oxideInorganic materials0.000description1

- 229920002050silicone resinPolymers0.000description1

- 229910052709silverInorganic materials0.000description1

- 239000004332silverSubstances0.000description1

- 239000002356single layerSubstances0.000description1

- 238000003860storageMethods0.000description1

- 230000001360synchronised effectEffects0.000description1

- 229930192474thiopheneNatural products0.000description1

- XOLBLPGZBRYERU-UHFFFAOYSA-Ntin dioxideChemical compoundO=[Sn]=OXOLBLPGZBRYERU-UHFFFAOYSA-N0.000description1

- 238000012546transferMethods0.000description1

- LEONUFNNVUYDNQ-UHFFFAOYSA-Nvanadium atomChemical compound[V]LEONUFNNVUYDNQ-UHFFFAOYSA-N0.000description1

- XLYOFNOQVPJJNP-UHFFFAOYSA-NwaterSubstancesOXLYOFNOQVPJJNP-UHFFFAOYSA-N0.000description1

Images

Landscapes

- Control Of El Displays (AREA)

- Liquid Crystal Display Device Control (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Controls And Circuits For Display Device (AREA)

Abstract

Description

本発明の一形態は、表示装置に関する。

なお本発明の一形態は、上記の技術分野に限定されない。本明細書等で開示する発明の技術分野は、物、方法、または、製造方法に関するものである。または、本発明の一形態は、プロセス、マシン、マニュファクチャ、または、組成物(コンポジション・オブ・マター)に関するものである。

そのため、より具体的に本明細書等で開示する本発明の一形態の技術分野としては、半導体装置、表示装置、電子機器、それらの駆動方法、または、それらの製造方法を一例としてあげることができる。なお、本明細書等において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指す。

近年、表示装置の性能の向上により、より高い輝度、より高いコントラストの表現が可能となっている。

一方、酸化物半導体を用いたトランジスタはオフ電流が非常に小さいため、液晶ディスプレイや有機ELディスプレイの画素に適用した場合、静止画を表示する際のリフレッシュ頻度を少なくし、消費電力を低減することができる。

また、オフ電流が小さいことを利用して、酸化物半導体を用いたトランジスタを不揮発性の記憶装置に用いた例が開示されている(特許文献2)。

本発明の一態様は、画像処理部において処理を行うことにより、処理前の画像データに比べて、画質の向上した画像データを提供することを課題の一とする。または、本発明の一態様は、画像処理部において処理を行うことにより、処理前の画像データに比べて、白とびの抑制された画像データを提供することを課題の一とする。または、本発明の一態様は、画像処理部において処理を行うことにより、処理前の画像データに比べて、黒つぶれの抑制された画像データを提供することを課題の一とする。または、本発明の一態様は、画像処理部において処理を行うことにより、処理前の画像データに比べて、よりダイナミックレンジの広い画像データを提供することを課題の一とする。ここでダイナミックレンジとは例えば、最も高い輝度と最も低い輝度との比である。

なお、本発明の一形態は、必ずしも上記の課題の全てを解決する必要はなく、少なくとも一つの課題を解決できるものであればよい。また、上記の課題の記載は、他の課題の存在を妨げるものではない。これら以外の課題は、明細書、特許請求の範囲、図面などの記載から自ずと明らかになるものであり、明細書、特許請求の範囲、図面などの記載から、これら以外の課題を抽出することが可能である。

本発明の一態様は、コントローラと、スキャンチェーンレジスタと、フレームメモリと、画像処理部と、を有し、フレームメモリは、画像データを格納する機能を有し、画像データは、各々の画素の輝度データを有し、画像処理部は、画像データを処理することにより、画像データにおける輝度の最大値の0.9倍より高い輝度を有する画素数を、画像処理後に減少させる機能を有し、スキャンチェーンレジスタは、画像処理部が処理を行うためのパラメータを格納する機能を有し、フレームメモリは、フレームメモリへの電源供給が遮断されている状態で、画像データを保持する機能を有し、スキャンチェーンレジスタは、電源供給が遮断されている状態で、パラメータを保持する機能を有し、スキャンチェーンレジスタを構成するトランジスタは、チャネル形成領域に酸化物半導体を有し、コントローラは、スキャンチェーンレジスタ、フレームメモリ、および画像処理部に対する電源供給を制御する機能を有する、表示装置である。

または、本発明の一態様は、コントローラと、スキャンチェーンレジスタと、フレームメモリと、画像処理部と、を有し、フレームメモリは、画像データを格納する機能を有し、画像データは、各々の画素の輝度データを有し、画像処理部は、画像データを処理することにより、画像データにおいて輝度の最大値の0.1倍より低い輝度を有する画素数を、画像処理後に増加させる機能を有し、フレームメモリは、フレームメモリへの電源供給が遮断されている状態で、画像データを保持する機能を有し、スキャンチェーンレジスタは、電源供給が遮断されている状態で、パラメータを保持する機能を有し、スキャンチェーンレジスタを構成するトランジスタは、チャネル形成領域に酸化物半導体を有し、コントローラは、スキャンチェーンレジスタ、フレームメモリ、および画像処理部に対する電源供給を制御する機能を有する、表示装置である。

または、本発明の一態様は、コントローラと、スキャンチェーンレジスタと、フレームメモリと、画像処理部と、を有し、フレームメモリは、画像データを格納する機能を有し、画像データは、各々の画素の輝度データを有し、スキャンチェーンレジスタは、画像データが有する輝度データと、輝度データの変換後の輝度データと、を対応づけたテーブルデータを有し、画像処理部に入力された画像データは、テーブルデータに基づき変換された後に画像処理部より出力され、スキャンチェーンレジスタは、画像処理部が処理を行うためのパラメータを格納する機能を有し、フレームメモリは、フレームメモリへの電源供給が遮断されている状態で、画像データを保持する機能を有し、スキャンチェーンレジスタは、電源供給が遮断されている状態で、パラメータを保持する機能を有し、スキャンチェーンレジスタを構成するトランジスタは、チャネル形成領域に酸化物半導体を有し、コントローラは、スキャンチェーンレジスタ、フレームメモリ、および画像処理部に対する電源供給を制御する機能を有する、表示装置である。

また、上記構成において、ヒストグラム検出回路を有し、ヒストグラム検出回路は、画像データが有する輝度データのヒストグラムを作成する機能を有することが好ましい。

または、本発明の一態様は、コントローラと、スキャンチェーンレジスタと、フレームメモリと、画像処理部と、を有し、フレームメモリは、画像データを格納する機能を有し、画像データは、各々の画素の輝度データを有し、画像処理部は、画像データを処理することにより、画像データが有する輝度の最大値を、画像処理後に高くする機能を有し、フレームメモリは、フレームメモリへの電源供給が遮断されている状態で、画像データを保持する機能を有し、スキャンチェーンレジスタは、電源供給が遮断されている状態で、パラメータを保持する機能を有し、スキャンチェーンレジスタを構成するトランジスタは、チャネル形成領域に酸化物半導体を有し、第1コントローラは、スキャンチェーンレジスタ、フレームメモリ、および画像処理部に対する電源供給を制御する機能を有する、表示装置である。

または、本発明の一態様は、コントローラと、スキャンチェーンレジスタと、フレームメモリと、画像処理部と、を有し、フレームメモリは、画像データを格納する機能を有し、画像データは、各々の画素の輝度データを有し、画像処理部は、画像データを処理することにより、画像データの階調を増加させる機能を有し、フレームメモリは、フレームメモリへの電源供給が遮断されている状態で、画像データを保持する機能を有し、スキャンチェーンレジスタは、電源供給が遮断されている状態で、パラメータを保持する機能を有し、スキャンチェーンレジスタを構成するトランジスタは、チャネル形成領域に酸化物半導体を有し、第1コントローラは、スキャンチェーンレジスタ、フレームメモリ、および画像処理部に対する電源供給を制御する機能を有する、表示装置である。

または、本発明の一態様は、コントローラと、レジスタと、フレームメモリと、画像処理部と、を有し、画像処理部は、検出回路を有し、レジスタは、スキャンチェーンレジスタと、揮発性のレジスタと、を有し、画像データは、各々の画素の輝度データを有し、フレームメモリは、フレームメモリへの電源供給が遮断されている状態で、画像データを保持する機能を有し、スキャンチェーンレジスタは、電源供給が遮断されている状態で、パラメータを保持する機能を有し、スキャンチェーンレジスタを構成するトランジスタは、チャネル形成領域に酸化物半導体を有し、コントローラは、スキャンチェーンレジスタ、フレームメモリ、および画像処理部に対する電源供給を制御する機能を有し、フレームメモリに画像データを格納する第1のステップと、検出回路により、フレームメモリに格納された画像データから第1の特徴を有する第1の領域を抽出する第2のステップと、抽出された第1の特徴に応じた第1のパラメータをスキャンチェーンレジスタに格納する第3のステップと、スキャンチェーンレジスタに格納された第1のパラメータを揮発性のレジスタにロードし、第1のパラメータを用いて画像処理を第1の領域に対して行う第4のステップと、を有する、表示装置の動作方法である。

また、上記構成において例えば、第1の特徴とは、白とび画素を有することである。また、上記構成において例えば、第1の特徴は、黒つぶれ画素を有することである。また、上記構成において例えば、第1の特徴は、パターン認識により認識された物体を有することである。

または、本発明の一態様は、コントローラと、レジスタと、フレームメモリと、画像処理部と、を有し、画像処理部は、検出回路を有し、レジスタは、第1のスキャンチェーンレジスタと、第2のスキャンチェーンレジスタと、揮発性のレジスタと、を有し、画像データは、各々の画素の輝度データを有し、フレームメモリは、フレームメモリへの電源供給が遮断されている状態で、画像データを保持する機能を有し、第1のスキャンチェーンレジスタおよび第2のスキャンチェーンレジスタは、電源供給が遮断されている状態で、パラメータを保持する機能を有し、第1のスキャンチェーンレジスタおよび第2のスキャンチェーンレジスタを構成するトランジスタは、チャネル形成領域に酸化物半導体を有し、コントローラは、第1のスキャンチェーンレジスタ、第2のスキャンチェーンレジスタ、フレームメモリ、および画像処理部に対する電源供給を制御する機能を有し、フレームメモリに画像データを格納する第1のステップと、検出回路により、フレームメモリに格納された画像データから第1の特徴を有する第1の領域を抽出する第2のステップと、抽出された第1の特徴に応じた第1のパラメータを第1のスキャンチェーンレジスタに格納する第3のステップと、第1のスキャンチェーンレジスタに格納された第1のパラメータを揮発性のレジスタにロードし、第1のパラメータを用いて画像処理を第1の領域に対して行う第4のステップと、検出回路により、フレームメモリに格納された画像データから第2の特徴を有する第2の領域を抽出する第5のステップと、抽出された第2の特徴に応じた第2のパラメータを第2のスキャンチェーンレジスタに格納する第6のステップと、第2のスキャンチェーンレジスタに格納された第2のパラメータを揮発性のレジスタにロードし、第2のパラメータを用いて画像処理を第2の領域に対して行う第7のステップと、を有する、表示装置の動作方法である。

本発明の一態様により、画像処理部において処理を行うことにより、処理前の画像データに比べて、画質の向上した画像データを提供することができる。また、本発明の一態様により、画像処理部において処理を行うことにより、処理前の画像データに比べて、白とびの抑制された画像データを提供することができる。また、本発明の一態様により、画像処理部において処理を行うことにより、処理前の画像データに比べて、黒つぶれの抑制された画像データを提供することができる。また、本発明の一態様により、画像処理部において処理を行うことにより、処理前の画像データに比べて、よりダイナミックレンジの広い画像データを提供することができる。

なお本発明の一形態の効果は、上記列挙した効果に限定されない。上記列挙した効果は、他の効果の存在を妨げるものではない。なお他の効果は、以下の記載で述べる、本項目で言及していない効果である。本項目で言及していない効果は、当業者であれば明細書又は図面等の記載から導き出せるものであり、これらの記載から適宜抽出することができる。なお、本発明の一形態は、上記列挙した効果、および他の効果のうち、少なくとも一つの効果を有するものである。従って本発明の一形態は、場合によっては、上記列挙した効果を有さない場合もある。

以下、実施の形態について図面を参照しながら説明する。ただし、実施の形態は多くの異なる態様で実施することが可能であり、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。したがって、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。

また、図面において、大きさ、層の厚さ、又は領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。なお図面は、理想的な例を模式的に示したものであり、図面に示す形状又は値などに限定されない。

また、本明細書にて用いる「第1」、「第2」、「第3」という序数詞は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

また、本明細書において、「上に」、「下に」などの配置を示す語句は、構成同士の位置関係を、図面を参照して説明するために、便宜上用いている。また、構成同士の位置関係は、各構成を描写する方向に応じて適宜変化するものである。したがって、明細書で説明した語句に限定されず、状況に応じて適切に言い換えることができる。

また、本明細書等において、トランジスタとは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子である。そして、ドレイン(ドレイン端子、ドレイン領域又はドレイン電極)とソース(ソース端子、ソース領域又はソース電極)の間にチャネル形成領域を有しており、チャネル形成領域を介して、ドレインとソースとの間に電流を流すことができるものである。なお、本明細書等において、チャネル領域とは、電流が主として流れる領域をいう。

また、ソースやドレインの機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書等においては、ソースやドレインの用語は、入れ替えて用いることができるものとする。

また、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタなどのスイッチング素子、抵抗素子、インダクタ、キャパシタ、その他の各種機能を有する素子などが含まれる。

また、本明細書等において、「平行」とは、二つの直線が−10°以上10°以下の角度で配置されている状態をいう。したがって、−5°以上5°以下の場合も含まれる。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。したがって、85°以上95°以下の場合も含まれる。

また、本明細書等において、「膜」という用語と、「層」という用語とは、互いに入れ替えることが可能である。例えば、「導電層」という用語を、「導電膜」という用語に変更することが可能な場合がある。又は、例えば、「絶縁膜」という用語を、「絶縁層」という用語に変更することが可能な場合がある。

また、本明細書等において、特に断りがない場合、オフ電流とは、トランジスタがオフ状態(非導通状態、遮断状態、ともいう)にあるときのドレイン電流をいう。オフ状態とは、特に断りがない場合、nチャネル型トランジスタでは、ゲートとソースの間の電圧Vgsがしきい値電圧Vthよりも低い状態、pチャネル型トランジスタでは、ゲートとソースの間の電圧Vgsがしきい値電圧Vthよりも高い状態をいう。例えば、nチャネル型のトランジスタのオフ電流とは、ゲートとソースの間の電圧Vgsがしきい値電圧Vthよりも低いときのドレイン電流をいう場合がある。

トランジスタのオフ電流は、Vgsに依存する場合がある。したがって、トランジスタのオフ電流がI以下である、とは、トランジスタのオフ電流がI以下となるVgsの値が存在することをいう場合がある。トランジスタのオフ電流は、所定のVgsにおけるオフ状態、所定の範囲内のVgsにおけるオフ状態、又は、十分に低減されたオフ電流が得られるVgsにおけるオフ状態、等におけるオフ電流を指す場合がある。

一例として、しきい値電圧Vthが0.5Vであり、Vgsが0.5Vにおけるドレイン電流が1×10−9Aであり、Vgsが0.1Vにおけるドレイン電流が1×10−13Aであり、Vgsが−0.5Vにおけるドレイン電流が1×10−19Aであり、Vgsが−0.8Vにおけるドレイン電流が1×10−22Aであるようなnチャネル型トランジスタを想定する。当該トランジスタのドレイン電流は、Vgsが−0.5Vにおいて、又は、Vgsが−0.5V乃至−0.8Vの範囲において、1×10−19A以下であるから、当該トランジスタのオフ電流は1×10−19A以下である、という場合がある。当該トランジスタのドレイン電流が1×10−22A以下となるVgsが存在するため、当該トランジスタのオフ電流は1×10−22A以下である、という場合がある。

また、本明細書等では、チャネル幅Wを有するトランジスタのオフ電流を、チャネル幅Wあたりを流れる電流値で表す場合がある。また、所定のチャネル幅(例えば1μm)あたりを流れる電流値で表す場合がある。後者の場合、オフ電流の単位は、電流/長さの次元を持つ単位(例えば、A/μm)で表される場合がある。

トランジスタのオフ電流は、温度に依存する場合がある。本明細書において、オフ電流は、特に記載がない場合、室温、60℃、85℃、95℃、又は125℃におけるオフ電流を表す場合がある。又は、当該トランジスタが含まれる半導体装置等の信頼性が保証される温度、又は、当該トランジスタが含まれる半導体装置等が使用される温度(例えば、5℃乃至35℃のいずれか一の温度)におけるオフ電流、を表す場合がある。トランジスタのオフ電流がI以下である、とは、室温、60℃、85℃、95℃、125℃、当該トランジスタが含まれる半導体装置等の信頼性が保証される温度、又は、当該トランジスタが含まれる半導体装置等が使用される温度(例えば、5℃乃至35℃のいずれか一の温度)、におけるトランジスタのオフ電流がI以下となるVgsの値が存在することを指す場合がある。

トランジスタのオフ電流は、ドレインとソースの間の電圧Vdsに依存する場合がある。本明細書において、オフ電流は、特に記載がない場合、Vdsが0.1V、0.8V、1V、1.2V、1.8V、2.5V、3V、3.3V、10V、12V、16V、又は20Vにおけるオフ電流を表す場合がある。又は、当該トランジスタが含まれる半導体装置等の信頼性が保証されるVds、又は、当該トランジスタが含まれる半導体装置等において使用されるVdsにおけるオフ電流、を表す場合がある。トランジスタのオフ電流がI以下である、とは、Vdsが0.1V、0.8V、1V、1.2V、1.8V、2.5V、3V、3.3V、10V、12V、16V、20V、当該トランジスタが含まれる半導体装置等の信頼性が保証されるVds、又は、当該トランジスタが含まれる半導体装置等において使用されるVds、におけるトランジスタのオフ電流がI以下となるVgsの値が存在することを指す場合がある。

上記オフ電流の説明において、ドレインをソースと読み替えてもよい。つまり、オフ電流は、トランジスタがオフ状態にあるときのソースを流れる電流をいう場合もある。

また、本明細書等では、オフ電流と同じ意味で、リーク電流と記載する場合がある。また、本明細書等において、オフ電流とは、例えば、トランジスタがオフ状態にあるときに、ソースとドレインとの間に流れる電流を指す場合がある。

なお、電圧とは2点間における電位差のことをいい、電位とはある一点における静電場の中にある単位電荷が持つ静電エネルギー(電気的な位置エネルギー)のことをいう。ただし、一般的に、ある一点における電位と基準となる電位(例えば接地電位)との電位差のことを、単に電位もしくは電圧と呼び、電位と電圧が同義語として用いられることが多い。このため、本明細書では特に指定する場合を除き、電位を電圧と読み替えてもよいし、電圧を電位と読み替えてもよいこととする。

(実施の形態1)

本実施の形態では、表示装置について説明する。特に、表示装置のコントローラICについて説明する。

本実施の形態では、表示装置について説明する。特に、表示装置のコントローラICについて説明する。

<<表示装置>>

図1は、表示装置の構成例を示すブロック図である。表示装置100は、表示ユニット110、タッチセンサユニット120を有する。

図1は、表示装置の構成例を示すブロック図である。表示装置100は、表示ユニット110、タッチセンサユニット120を有する。

<表示ユニット>

表示ユニット110は、画素アレイ111、ゲートドライバ113、およびコントローラIC115を有する。

表示ユニット110は、画素アレイ111、ゲートドライバ113、およびコントローラIC115を有する。

画素アレイ111は、複数の画素10を有し、それぞれの画素10はトランジスタを用いて駆動されるアクティブ型の素子である。また、画素10は、表示素子を有する。表示素子は例えば、透過素子、反射素子、発光素子、等である。透過素子として例えば透過型の液晶素子が挙げられる。反射素子として例えば反射型の液晶素子、電子ペーパー、等が挙げられる。発光素子として例えばEL素子が挙げられる。画素アレイ111のより具体的な構成例については、実施の形態2にて、説明する。

ゲートドライバ113は、表示素子を選択するためのゲート線を駆動する機能を有する。表示素子にデータ信号を供給するソース線を駆動するソースドライバは、コントローラIC115に設けられている。コントローラIC115は、表示装置100の動作を統括的に制御する機能を備える。コントローラIC115の数は、画素アレイの画素数に応じて決定される。

図1の例では、画素アレイ111と共にゲートドライバ113が同一基板上に集積されている例を示しているが、ゲートドライバ113を専用ICとすることもできる。あるいは、コントローラIC115に、ゲートドライバ113を組み込んでもよい。

ここでは、コントローラIC115の実装方式は、COG(Chip on Glass)方式としているが、実装方式に特段の制約はなく、COF(Chip on Flexible)方式、TAB(Tape Automated Bonding)方式などでもよい。タッチセンサユニット120のICの実装方式についても同様である。

なお、画素10に使用されるトランジスタは、チャネル形成領域に酸化物半導体を有するトランジスタ(「OSトランジスタ」ともいう。)であり、Siトランジスタに比べてオフ電流が低いトランジスタである。OSトランジスタは、酸化物半導体中の不純物濃度を低減し、酸化物半導体を真性または実質的に真性にすることで、オフ電流を極めて低くすることができる。

もしくは、画素10に使用されるトランジスタとして、オフ電流が低ければ酸化物半導体を適用しないトランジスタとすることができる。例えば、バンドギャップが大きい半導体を適用したトランジスタを適用してもよい。バンドギャップが大きい半導体とは、バンドギャップが2.2eV以上の半導体である。例えば、炭化ケイ素、窒化ガリウム、ダイヤモンドなどが挙げられる。

画素10に、オフ電流が低いトランジスタを用いることで、表示画面を書き換える必要がない場合(すなわち静止画を表示する場合)、一時的にゲートドライバ113およびソースドライバを停止することができる(以下、「アイドリングストップ」、もしくは「IDS駆動」と呼ぶ。)。IDS駆動によって、表示装置100の消費電力を低減することができる。

<タッチセンサユニット>

図1に示す、タッチセンサユニット120は、センサアレイ121、および周辺回路125を有する。周辺回路125は、タッチセンサドライバ(以下、「TSドライバ」と呼ぶ。)126、センス回路127を有する。周辺回路125は専用ICで構成することができる。

図1に示す、タッチセンサユニット120は、センサアレイ121、および周辺回路125を有する。周辺回路125は、タッチセンサドライバ(以下、「TSドライバ」と呼ぶ。)126、センス回路127を有する。周辺回路125は専用ICで構成することができる。

図2に、タッチセンサユニット120の構成例を示す。ここでは、タッチセンサユニット120が相互容量タッチセンサユニットである例を示す。センサアレイ121は、m本(mは1以上の整数)の配線DRL、n本(nは1以上の整数)の配線SNLを有する。配線DRLはドライブ線であり、配線SNLはセンス線である。ここでは、第α番の配線DRLを配線DRL<α>と呼び、第β番の配線SNLを配線SNL<β>と呼ぶこととする。容量CTαβは、配線DRL<α>と配線SNL<β>との間に形成される容量である。

m本の配線DRLはTSドライバ126に電気的に接続されている。TSドライバ126は配線DRLを駆動する機能を有する。n本の配線SNLはセンス回路127に電気的に接続されている。センス回路127は、配線SNLの信号を検出する機能を有する。TSドライバ126によって配線DRL<α>が駆動されているときの配線SNL<β>の信号は、容量CTαβの容量値の変化量の情報をもつ。n本の配線SNLの信号を解析することで、タッチの有無、タッチ位置などの情報を得ることができる。

<<コントローラIC>>

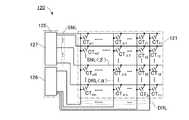

図3は、コントローラIC115の構成例を示すブロック図である。コントローラIC115は、インターフェース150、フレームメモリ151、デコーダ152、センサコントローラ153、コントローラ154、クロック生成回路155、画像処理部160、メモリ170、タイミングコントローラ173、レジスタ175、ソースドライバ180、およびタッチセンサコントローラ184を有する。

図3は、コントローラIC115の構成例を示すブロック図である。コントローラIC115は、インターフェース150、フレームメモリ151、デコーダ152、センサコントローラ153、コントローラ154、クロック生成回路155、画像処理部160、メモリ170、タイミングコントローラ173、レジスタ175、ソースドライバ180、およびタッチセンサコントローラ184を有する。

コントローラIC115とホスト140との通信は、インターフェース150を介して行われる。ホスト140からは、画像データ、各種制御信号等がコントローラIC115に送られる。また、コントローラIC115からは、タッチセンサコントローラ184が取得したタッチ位置などの情報が、ホスト140に送られる。なお、コントローラIC115が有するそれぞれの回路は、ホスト140の規格、表示装置100の仕様等によって、適宜取捨される。

フレームメモリ151は、コントローラIC115に入力された画像データを保存するためのメモリである。ホストから圧縮された画像データが送られる場合、フレームメモリ151は、圧縮された画像データを格納することが可能である。デコーダ152は、圧縮された画像データを伸長するための回路である。画像データを伸長する必要がない場合、デコーダ152は処理を行わない。または、デコーダ152を、フレームメモリ151とインターフェース150との間に、配置することもできる。

画像処理部160は、画像データに対して各種画像処理を行う機能を有する。例えば、画像処理部160は、ガンマ補正回路161、調光調色回路162、EL補正回路164、補正回路165を有する。

画像処理部160は、検出回路157と、補正回路165と、を有する。

検出回路157は、白とび画素、および黒つぶれ画素を検出する機能を有する。あるいは検出回路157は、白とび画素を有する領域、および黒つぶれ画素を有する領域、を検出する機能を有する。あるいは検出回路157は、パターン認識により画像が有する物体等を検出する機能を有する。また、検出回路157は、ヒストグラム生成回路159を有することが好ましい。ヒストグラム生成回路159は、階調、輝度、色彩度、等のデータを基にヒストグラムを生成する。例えば、ある領域、あるいは画面全体の画素が有する輝度のヒストグラム、色彩度のヒストグラム、等を生成することができる。

補正回路165は、ヒストグラム生成回路159が生成したヒストグラムを基に演算を行い、画像処理のためのパラメータを生成することができる。

補正回路165は、輝度の変換を行った後に画像の彩度の分布に著しい変化が生じる場合には、彩度の変換を行うことが好ましい。

本発明の一態様の表示装置は、より高い輝度を用いてダイナミックレンジを広げた画像を表示させることができる。

表示装置に入力される画像データでは、撮影された画像データに対してある領域の階調が圧縮される場合がある。例えば、輝度の高い領域の階調が圧縮される。本発明の一態様の表示装置は、圧縮された階調、ここでは例として輝度の高い領域において圧縮された階調、を伸長し、ダイナミックレンジの広い画像を表示させる。

画像処理部において、輝度の高い領域の階調を伸長する場合には、輝度の高い階調の画素の画像データに対してのみ、処理を行ってもよい。あるいは、輝度の高い階調の画素を有する領域、例として輝度の高い階調の画素を有する物体等、のみ、処理を行ってもよい。全ての階調の画素の画像データにおいてデータ処理を行う場合と比較して、処理を行う画像データの量を少なくすることができ、処理時間を短縮することができる。特に8Kなどの高精細画像データの場合、データ処理量が膨大となるため、処理を行う画像データの量をできる限り少なくすることが求められる。

ここで、画像処理部における処理を行った後、階調数が増加してもよい。あるいは、輝度の高い領域の階調を伸長して階調数を増加させた後、階調数が補正前の画像データと同一となるように補正を行ってもよい。

ここで画像処理部における処理により必ずしも画像データのダイナミックレンジを変化させなくてもよい。

EL補正回路164は、表示素子が例えば発光素子であり、ソースドライバ180が表示素子を流れる電流を検出する電流検出回路を備えている場合、設けられる。EL補正回路164は、ソースドライバ180の電流検出回路から送信される信号に基づいて、表示素子の輝度を調節する機能を有する。

画像処理部160で処理された画像データは、メモリ170を経て、ソースドライバ180に出力される。メモリ170は、画像データを一時的に格納するためのメモリである。ソースドライバ180は、入力された画像データを処理し、画素アレイ111のソース線に書き込む機能を有する。

タイミングコントローラ173は、ソースドライバ180、タッチセンサコントローラ184、表示ユニット110のゲートドライバ113で使用するタイミング信号を生成する機能を有する。

タッチセンサコントローラ184は、タッチセンサユニット120のTSドライバ126、センス回路127を制御する機能をもつ。センス回路127で読み出されたタッチ情報を含む信号は、タッチセンサコントローラ184で処理され、インターフェース150を介して、ホスト140に送出される。ホスト140は、タッチ情報を反映した画像データを生成し、コントローラIC115に送出する。なお、コントローラIC115で、画像データにタッチ情報を反映する構成も可能である。

クロック生成回路155は、コントローラIC115で使用されるクロック信号を生成する機能を有する。コントローラ154は、インターフェース150を介してホスト140から送られる各種制御信号を処理し、コントローラIC115内の各種回路を制御する機能を有する。また、コントローラ154は、コントローラIC115内の各種回路への電源供給を制御する機能を有する。以下、使われていない回路への電源供給を一時的に遮断することを、パワーゲーティングと呼ぶ。

レジスタ175は、コントローラIC115の動作に用いられるデータを格納する。レジスタ175が格納するデータには、画像処理部160が補正処理を行うために使用するパラメータ、タイミングコントローラ173が各種タイミング信号の波形生成に用いるパラメータなどがある。レジスタ175は、複数のレジスタで構成されるスキャンチェーンレジスタを備える。

センサコントローラ153には、光センサ143が電気的に接続されている。光センサ143には外光145を検知し、検知信号を生成する。センサコントローラ153は検知信号を基に、制御信号を生成する。センサコントローラ153で生成される制御信号は、例えば、コントローラ154に出力される。

画像処理部160は、表示装置100の仕様によって、RGB−RGBW変換回路など、他の処理回路を有している場合がある。RGB−RGBW変換回路とは、RGB(赤、緑、青)画像データを、RGBW(赤、緑、青、白)画像信号に変換する機能をもつ回路である。すなわち、表示装置100がRGBW4色の画素を有する場合、画像データ内のW(白)成分を、W(白)画素を用いて表示することで、消費電力を低減することができる。なお、RGB−RGBW変換回路はこれに限らず、例えば、RGB−RGBY(赤、緑、青、黄)変換回路などでもよい。

上記、補正のためのパラメータは、レジスタ175に格納することができる。また、上記以外にレジスタ175に格納できるパラメータとしては、EL補正回路164のデータ、ユーザーが設定した表示装置100の輝度、色調、省エネルギー設定(表示を暗くする、または表示を消す、までの時間)、タッチセンサコントローラ184の感度などがある。

<パワーゲーティング>

コントローラ154は、ホスト140から送られる画像データに変化がない場合、コントローラIC115内の一部回路をパワーゲーティングすることができる。具体的には、例えば、領域190内の回路(フレームメモリ151、デコーダ152、画像処理部160、メモリ170、タイミングコントローラ173、レジスタ175、ソースドライバ180)を指す。ホスト140から画像データに変化がないことを示す制御信号をコントローラIC115に送信し、当該制御信号をコントローラ154で検出した場合にパワーゲーティングする構成が可能である。

コントローラ154は、ホスト140から送られる画像データに変化がない場合、コントローラIC115内の一部回路をパワーゲーティングすることができる。具体的には、例えば、領域190内の回路(フレームメモリ151、デコーダ152、画像処理部160、メモリ170、タイミングコントローラ173、レジスタ175、ソースドライバ180)を指す。ホスト140から画像データに変化がないことを示す制御信号をコントローラIC115に送信し、当該制御信号をコントローラ154で検出した場合にパワーゲーティングする構成が可能である。

領域190内の回路は、画像データに関する回路と、表示ユニット110を駆動するための回路であるため、画像データに変化がない場合は、一時的に領域190内の回路を停止することができる。なお、画像データに変化がない場合でも、画素10に使用されるトランジスタがデータを保持できる時間(アイドリングストップが可能な時間)、および表示素子が液晶素子の場合には、焼き付き防止のため行う反転駆動の時間を考慮してもよい。

例えば、コントローラ154はタイマ機能を組み込むことで、タイマで測定した時間に基づいて、領域190内の回路への電源供給を再開するタイミングを決定してもよい。なお、フレームメモリ151もしくはメモリ170に画像データを保存しておき、当該画像データを反転駆動時に表示ユニット110に供給する画像データとする構成が可能である。このような構成とすることで、ホスト140から画像データを送信することなく反転駆動が実行できる。したがって、ホスト140からのデータ送信量を低減でき、コントローラIC115の消費電力を低減することができる。

以下、フレームメモリ151、レジスタ175の具体的な回路構成を説明する。なお、パワーゲーティングすることができる回路として説明した、領域190内の回路、センサコントローラ153、およびタッチセンサコントローラ184等は、この限りではない。コントローラIC115の構成、ホスト140の規格、表示装置100の仕様等によって、様々な組み合わせが考えられる。

<フレームメモリ151>

図4(A)に、フレームメモリ151の構成例を示す。フレームメモリ151は、制御部202、セルアレイ203、周辺回路208を有する。周辺回路208は、センスアンプ回路204、ドライバ205、メインアンプ206、入出力回路207を有する。

図4(A)に、フレームメモリ151の構成例を示す。フレームメモリ151は、制御部202、セルアレイ203、周辺回路208を有する。周辺回路208は、センスアンプ回路204、ドライバ205、メインアンプ206、入出力回路207を有する。

制御部202は、フレームメモリ151を制御する機能を有する。例えば、制御部202は、ドライバ205、メインアンプ206、および入出力回路207を制御する。

ドライバ205には、複数の配線WL、CSELが電気的に接続されている。ドライバ205は、複数の配線WL、CSELに出力する信号を生成する。

セルアレイ203は、複数のメモリセル209を有する。メモリセル209は、配線WL、LBL(またはLBLB)、BGLに、電気的に接続されている。配線WLはワード線であり、配線LBL、LBLBは、ローカルビット線である。図4(A)の例では、セルアレイ203の構成は、折り返しビット線方式であるが、開放ビット線方式とすることもできる。

図4(B)に、メモリセル209の構成例を示す。メモリセル209は、トランジスタMW1、容量素子CS1を有する。メモリセル209は、DRAM(ダイナミック・ランダム・アクセス・メモリ)のメモリセルと同様の回路構成を有する。ここでは、トランジスタMW1はバックゲートをもつトランジスタである。トランジスタMW1のバックゲートは、配線BGLに電気的に接続されている。配線BGLには、電圧Vbg_w1が入力される。

トランジスタMW1は、チャネル形成領域に酸化物半導体を有するトランジスタ(「OSトランジスタ」ともいう。)である。OSトランジスタはオフ電流が極めて小さいため、OSトランジスタでメモリセル209を構成することで、容量素子CS1から電荷がリークすることを抑えられるため、フレームメモリ151のリフレッシュ動作の頻度を低減できる。また、電源供給が遮断されても、フレームメモリ151は長時間画像データを保持することが可能である。また、電圧Vbg_w1を負電圧にすることで、トランジスタMW1の閾値電圧を正電位側にシフトさせることができ、メモリセル209の保持時間を長くすることができる。

ここでいう、オフ電流とは、トランジスタがオフ状態のときにソースとドレインとの間に流れる電流をいう。トランジスタがnチャネル型である場合、例えば、しきい値電圧が0V乃至2V程度であれば、ソースに対するゲートの電圧が負の電圧であるときの、ソースとドレインとの間に流れる電流をオフ電流と呼ぶことができる。また、オフ電流が極めて小さいとは、例えば、チャネル幅1μmあたりのオフ電流が100zA(z;ゼプト、10−21)以下であることをいう。オフ電流は小さいほど好ましいため、この規格化されたオフ電流が10zA/μm以下、あるいは1zA/μm以下とすることが好ましく、10yA/μm(y;ヨクト、10−24)以下であることがより好ましい。

酸化物半導体のバンドギャップは3.0eV以上であるため、OSトランジスタは熱励起によるリーク電流が小さく、また上掲のようにオフ電流が極めて小さい。チャネル形成領域に適用される酸化物半導体は、インジウム(In)および亜鉛(Zn)の少なくとも一方を含む酸化物半導体であることが好ましい。このような酸化物半導体としては、In−M−Zn酸化物(元素Mは、例えばAl、Ga、YまたはSn)が代表的である。電子供与体(ドナー)となる水分または水素等の不純物を低減し、かつ酸素欠損も低減することで、酸化物半導体をi型(真性半導体)にする、あるいはi型に限りなく近づけることができる。ここでは、このような酸化物半導体は高純度化された酸化物半導体と呼ぶことができる。例えば、チャネル形成領域に高純度化された酸化物半導体を適用することで、チャネル幅で規格化されたOSトランジスタのオフ電流を数yA/μm以上数zA/μm以下程度に低くすることができる。

セルアレイ203が有する複数のメモリセル209の、トランジスタMW1はOSトランジスタであるため、その他の回路のトランジスタは、例えば、シリコンウエハに作製されるSiトランジスタとすることができる。これにより、セルアレイ203をセンスアンプ回路204に積層して設けることができる。よって、フレームメモリ151の回路面積を縮小でき、コントローラIC115の小型化につながる。

セルアレイ203は、センスアンプ回路204に積層して設けられている。センスアンプ回路204は、複数のセンスアンプSAを有する。センスアンプSAは隣接する配線LBL、LBLB(ローカルビット線対)、配線GBL、GBLB(グローバルビット線対)、複数の配線CSELに電気的に接続されている。センスアンプSAは、配線LBLと配線LBLBとの電位差を増幅する機能を有する。

センスアンプ回路204には、4本の配線LBLに対して1本の配線GBLが設けられ、4本の配線LBLBに対して1本の配線GBLBが設けられているが、センスアンプ回路204の構成は、図5(A)の構成例に限定されない。

メインアンプ206は、センスアンプ回路204および入出力回路207に接続されている。メインアンプ206は、配線GBLと配線GBLBの電位差を増幅する機能を有する。メインアンプ206は省略することができる。

入出力回路207は、書き込みデータに対応する電位を配線GBLと配線GBLB、またはメインアンプ206に出力する機能、配線GBLと配線GBLBの電位、またはメインアンプ206の出力電位を読み出し、データとして外部に出力する機能を有する。配線CSELの信号によって、データを読み出すセンスアンプSA、およびデータを書き込むセンスアンプSAを選択することができる。よって、入出力回路207は、マルチプレクサなどの選択回路が不要であるため、回路構成を簡単化でき、占有面積を縮小することができる。

<レジスタ175>

図5乃至図7を参照して、レジスタ175の構成例を、図8を参照してレジスタ175の動作例を説明する。

図5乃至図7を参照して、レジスタ175の構成例を、図8を参照してレジスタ175の動作例を説明する。

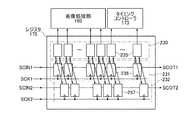

図5は、レジスタ175の構成例を示すブロック図である。レジスタ175は、レジスタ部230、およびスキャンチェーンレジスタ部231、232を有する。スキャンチェーンレジスタ部231と、スキャンチェーンレジスタ部232には、それぞれ異なるパラメータが保存されることが好ましい。例えば、一方にはあるフレームの画像に対する画像処理に用いるパラメータが保存され、他方には、該フレームの次のフレームの画像に対する画像処理に用いるパラメータが保存される。あるいは例えば、一方には第1の画像処理、ここでは例として第1の領域の白とび補正のためのパラメータが保存され、他方には同一フレームの第2の画像処理、ここでは例として第2の領域の黒つぶれ補正のためのパラメータが保存される。

レジスタ部230は、複数のレジスタ235を有する。スキャンチェーンレジスタ部231は、複数のレジスタ236、ノードSCIN1、SCOT1を有する。スキャンチェーンレジスタ部232は、複数のレジスタ237、ノードSCIN2、SCOT2を有する。ここではレジスタ175がスキャンチェーンレジスタ部を2つ有する例を示すが、レジスタ175は、不揮発性レジスタを有するスキャンチェーンレジスタ部を3以上有してもよい。

レジスタ236、237は、電源が遮断された状態でもデータが消失しない不揮発性レジスタである。レジスタ236、237を不揮発化するため、レジスタ236、237は、OSトランジスタを用いた保持回路を備えている。

他方、レジスタ235は揮発性レジスタである。レジスタ235の回路構成には特段の制約はなく、データを記憶することが可能な回路であればよく、ラッチ回路、フリップフロップ回路などで構成すればよい。画像処理部160、およびタイミングコントローラ173は、レジスタ部230にアクセスし、対応するレジスタ235からデータを取り込む。あるいは、画像処理部160、およびタイミングコントローラ173は、レジスタ部230から供給されるデータにしたがって、処理内容が制御される。

レジスタ175に格納しているデータを更新する場合、まず、スキャンチェーンレジスタ部231、232のデータを変更する。スキャンチェーンレジスタ部231のデータを変更するには、スキャンクロック信号SCK1をトグルさせながら、ノードSCIN1よりデータを入力する。ノードSCIN1より入力されたデータは、スキャンクロック信号SCK1に従い、各レジスタ236のデータを更新する。最終段のレジスタ236は、ノードSCOT1よりデータを出力する。同様に、スキャンチェーンレジスタ部232のデータを変更するには、スキャンクロック信号SCK2をトグルさせながら、ノードSCIN2よりデータを入力する。ノードSCIN2より入力されたデータは、スキャンクロック信号SCK2に従い、各レジスタ237のデータを更新する。最終段のレジスタ237のは、ノードSCOT2よりデータを出力する。

ここで、ノードSCIN1、ノードSCIN2より入力されるデータは、表示装置100の製造者が設定し、ホスト140から送信されるデータ、表示装置100の使用者が設定し、ホスト140から送信されるデータ、または、センサコントローラ153で生成される制御信号に対応し、コントローラ154から送信されるデータなどである。

スキャンチェーンレジスタ部231の各レジスタ236のデータを書き換えた後、各レジスタ236のデータを、レジスタ部230の各レジスタ235に一括してロードする。または、スキャンチェーンレジスタ部232の各レジスタ237のデータを書き換えた後、各レジスタ237のデータを、レジスタ部230の各レジスタ235に一括してロードする。

また、画像処理部160は、第1のパラメータを用いて画像データを処理する場合、スキャンチェーンレジスタ部231のデータを必要とし、第2のパラメータを用いて画像データを処理する場合、スキャンチェーンレジスタ部232のデータを必要とする。この場合、スキャンチェーンレジスタ部231、232のデータが変更されたか否かにかかわらず、スキャンチェーンレジスタ部231のデータをレジスタ部230に、または、スキャンチェーンレジスタ部232のデータをレジスタ部230に、ロードする。

これにより、画像処理部160、およびタイミングコントローラ173等は、一括して更新されたデータを使用して、各種処理を行うことができる。データの更新に同時性が保たれるため、コントローラIC115の安定した動作を実現できる。スキャンチェーンレジスタ部231、232とレジスタ部230とを備えることで、画像処理部160、およびタイミングコントローラ173が動作中でも、スキャンチェーンレジスタ部231、232のデータを更新することができる。

コントローラIC115のパワーゲーティング実行時には、レジスタ236、237において、保持回路にデータを格納(セーブ)してから電源を遮断する。電源復帰後、レジスタ236もしくはレジスタ237のデータを、レジスタ235に復帰(ロード)して通常動作を再開する。なお、レジスタ236もしくはレジスタ237に格納されているデータと、レジスタ235に格納されているデータとが整合しない場合は、レジスタ235のデータをレジスタ236もしくはレジスタ237にセーブした後、あらためて、レジスタ236、237の保持回路にデータを格納する構成が好ましい。データが整合しない場合としては、スキャンチェーンレジスタ部231、232のデータを変更している場合などが挙げられる。

図6、図7を用いて、レジスタ175の回路構成例を説明する。

レジスタ部230は、N個(Nは2以上の整数)のレジスタ235を有する。レジスタ部230には、信号LDA1、LDA2が入力される。信号LDA1、LDA2は、データのロードを制御するための信号である。

スキャンチェーンレジスタ部231、232は、それぞれ、N個のレジスタ236、237を有する。スキャンチェーンレジスタ部231には、スキャンクロック信号SCK1、信号SVA1、SVB1、LDB1が入力される。スキャンチェーンレジスタ部232には、スキャンクロック信号SCK2、信号SVA2、SVB2、LDB2が入力される。信号LDB1、LDB2はデータのロードを制御するための信号であり、信号SVA1、SVA2、SVB1、SVB2は、データのセーブを制御するための信号である。

なお、本明細書において、複数のレジスタ235のうち1個を特定する必要があるときは、レジスタ235[1]等と表記する。また、レジスタ235と記載した場合は、任意のレジスタ235を指している。他の要素についても同様である。

レジスタ235は、ラッチ回路30、MUX(マルチプレクサ)31を有する。レジスタ236は、セレクタ40、フリップフロップ回路41、保持回路42、ノードSDI1、SDO1を有する。レジスタ237は、セレクタ45、フリップフロップ回路46、保持回路47、ノードSDI2、SDO2を有する。ノードSDI1、SDI2はデータが入力されるノードであり、ノードSDO1、SDO2はデータが出力されるノードである。

<レジスタ235>

レジスタ235は揮発性レジスタである。ノードQ、Aは、ラッチ回路30の出力ノードであり、論理が同じデータを出力する。ノードQは、画像処理部160またはタイミングコントローラ173等に電気的に接続され、ノードAは、レジスタ236、237に電気的に接続されている。ラッチ回路30に特段の制約はなく、フリップフロップ回路など、他の回路を設けてもよい。

レジスタ235は揮発性レジスタである。ノードQ、Aは、ラッチ回路30の出力ノードであり、論理が同じデータを出力する。ノードQは、画像処理部160またはタイミングコントローラ173等に電気的に接続され、ノードAは、レジスタ236、237に電気的に接続されている。ラッチ回路30に特段の制約はなく、フリップフロップ回路など、他の回路を設けてもよい。

MUX31は、ラッチ回路30に入力するデータを選択する機能を有する。信号LDA1、LDA2は、MUX31の制御信号である。図6の例では、信号LDA1が“H“であり、かつLDA2が”L“である場合、ノードSDO1のデータによってラッチ回路30のデータが更新される。他方、信号LDA1が“L“であり、かつLDA2が”H“である場合、ノードSDO2のデータによってラッチ回路30のデータが更新される。

レジスタ236、237は、不揮発性レジスタである。図7を用いて、レジスタ236、237のより具体的な回路構成例を説明する。

<レジスタ236>

レジスタ236において、セレクタ40とフリップフロップ回路41とで、スキャンフリップフロップ回路が構成されている。スキャンチェーンレジスタ部231がシフトレジスタとして動作する場合、レジスタ236は、ノードSDI1からデータを取り込み、ノードSDO1からデータを出力する。ノードSDO1のデータは、次段のレジスタ236のノードSDI1に入力される。

レジスタ236において、セレクタ40とフリップフロップ回路41とで、スキャンフリップフロップ回路が構成されている。スキャンチェーンレジスタ部231がシフトレジスタとして動作する場合、レジスタ236は、ノードSDI1からデータを取り込み、ノードSDO1からデータを出力する。ノードSDO1のデータは、次段のレジスタ236のノードSDI1に入力される。

信号SVA1は、セレクタ40の制御信号である。信号SVA1が“H”である場合、セレクタ40は、フリップフロップ回路41の入力ノードと、レジスタ235のノードA間を導通し、信号SVA1が“L”である場合、セレクタ40はフリップフロップ回路41の入力ノードと、ノードSDI1間を導通する。

フリップフロップ回路41は、図7の回路構成に限定されず、様々なフリップフロップ回路を適用することができる。フリップフロップ回路41のノードN1、NB1に、保持回路42が電気的に接続されている。信号LDB1、SVB1は、保持回路42の制御信号である。

保持回路42は、フリップフロップ回路41が保持するデータを記憶するための回路であり、2個のメモリ回路43、44を有する。ここでは、メモリ回路43、44は3トランジスタ型のゲインセルで構成されている。メモリ回路43は、トランジスタM11乃至M13、容量素子CS1、ノードSN1を有し、メモリ回路44は、トランジスタM14乃至M16、容量素子CS2、ノードSN2を有する。ノードSN1、SN2は、メモリ回路43、44の保持ノードである。

メモリ回路43は、ノードN1のデータをバックアップし、バックアップしたデータをノードNB1にロードする機能を有し、メモリ回路44は、ノードNB1のデータをバックアップし、バックアップしたデータをノードN1にロードする機能を有する。信号SVB1に従い、メモリ回路43はノードN1のデータをノードSN1に書き込み、メモリ回路44はノードNB1のデータをノードSN2に書き込む。信号LDB1に従い、メモリ回路43はノードSN1のデータをノードNB1に書き込み、メモリ回路44はノードSN2のデータをノードN1に書き込む。

トランジスタM11、M14がOSトランジスタであるので、保持回路42は、電源が遮断された状態でも長時間データを保持することが可能である。レジスタ236において、トランジスタM11、M14以外のトランジスタは、Siトランジスタで構成してもよい。

<レジスタ237>

レジスタ237の回路構成は、レジスタ236と同様のため、レジスタ237の詳細な説明はレジスタ236の説明を援用する。

レジスタ237の回路構成は、レジスタ236と同様のため、レジスタ237の詳細な説明はレジスタ236の説明を援用する。

レジスタ237において、セレクタ45とフリップフロップ回路46とで、スキャンフリップフロップ回路が構成されている。セレクタ45は、信号SVA2に従い、ノードAまたはノードSDI2の一方を選択し、選択したノードとフリップフロップ回路46の入力ノード間を導通する。

フリップフロップ回路46のノードN2、NB2には、保持回路47が電気的に接続されている。保持回路47は、メモリ回路48、49を有する。メモリ回路48は、トランジスタM21乃至M23、容量素子CS3、ノードSN3を有する。メモリ回路49は、トランジスタM24乃至M26、容量素子CS4、ノードSN4を有する。メモリ回路48は、信号SVB2に従いフリップフロップ回路46のデータを格納し、信号LDB2に従い、保持しているデータをフリップフロップ回路46にロードする。

トランジスタM21、M24がOSトランジスタであるので、保持回路47は、電源が遮断された状態でも長時間データを保持することが可能である。トランジスタM21、トランジスタM24は、トランジスタMW1(図4(B))と同様にバックゲートを有するトランジスタであってもよい。トランジスタM11、M14についても同様である。

レジスタ237において、トランジスタM21、M24以外のトランジスタは、Siトランジスタで構成してもよい。

なお、図7には、フリップフロップ回路46の前段のインバータループの相補データを保持回路47でバックアップする例を示している。フリップフロップ回路46の後段のインバータループの相補データをバックアップできるように、保持回路47を設けてもよい。これは、レジスタ236でも同様である。保持回路42、47をこのような構成とすることで、バックアップしたデータのロードが非同期で行えるため、高速なデータのロードができる。これにより、パワーゲーティング時に、コントローラIC115を電源オフ状態から通常動作状態に復帰させる時間を短縮できる。

<レジスタ175の動作例>

図8を参照して、レジスタ175の動作例を説明する。図8は、レジスタ175の動作例を示すタイミングチャートである。図8において、T1、T2等は期間を表す。PLDDはレジスタ175に電位VDDを供給する配線である。電位VDDは電源電位である。また、ノードN1等の波形において、ハッチングで示されている箇所は、論理が“H”か“L”か定まらない不定値であることを示している。

図8を参照して、レジスタ175の動作例を説明する。図8は、レジスタ175の動作例を示すタイミングチャートである。図8において、T1、T2等は期間を表す。PLDDはレジスタ175に電位VDDを供給する配線である。電位VDDは電源電位である。また、ノードN1等の波形において、ハッチングで示されている箇所は、論理が“H”か“L”か定まらない不定値であることを示している。

期間T1では、スキャンチェーンレジスタ部231、232をスキャン動作させて、それぞれにデータを書書き込んでいる。この間、信号SVA1、SVABは“L”であり、スキャンクロック信号SCK1、SCK2はアクティブである。したがって、セレクタ40によって、ノードSDI1とフリップフロップ回路41の入力ノード間が導通され、セレクタ45によって、ノードSDI2とフリップフロップ回路46の入力ノード間が導通される。

スキャンチェーンレジスタ部231のN段のレジスタ236にデータを書き込むため、スキャンクロック信号SCK1に同期して、ノードSCIN1のデータが更新される。レジスタ236[k](kは1以上N以下の整数)において、スキャンクロック信号SCK1の立ち上がりエッジに同期して、ノードSDO1[k]のデータが更新され、スキャンクロック信号SCK1の立ち下がりエッジに同期して、ノードSDO1[k]のデータによって、ノードN1[k+1]が更新される。スキャンクロック信号SCK1がトグルを繰り返すことで、ノードSCIN1のデータが各段のレジスタ236をシフトしていく。ノードSCOT1から、各段のレジスタ236に格納されるデータを順次取得することができる。

スキャンチェーンレジスタ部232のシフト動作も、スキャンチェーンレジスタ部231と同様に実行される。スキャンクロック信号SCK2の立ち上がりエッジに同期して、ノードSDO2のデータが更新される。

期間T2では、レジスタ部230のデータの更新動作が行われる。信号LDA1が“H”に遷移することで、MUX31[k]によって、ノードSDO1[k]とラッチ回路30[k]の入力ノード間が導通される。ラッチ回路30[k]は、レジスタ236[k]が保持するデータDkを格納する。ノードQ[k]、A[k]からはデータDkが出力される。つまり、信号LDA1を“H”にすることで、スキャンチェーンレジスタ部231が保持しているデータD1乃至DNが、レジスタ部230に一括してロードされる。これにより、画像処理部160、およびタイミングコントローラ173が使用するパラメータなどを一括して変更することができる。

スキャンチェーンレジスタ部232が保持しているデータによって、レジスタ部230のデータを更新する場合は、信号LDA1を“L”に維持し、信号LDA2を“H”にすればよい。

なお、T2で、スキャンクロック信号SCK1および信号SVA1が“L”になることで、ノードN1[1]とノードSCIN1間が導通されるため、ノードN1[1]の電位は、ノードSCIN1の電位に応じて変化する。同様に、スキャンクロック信号SCK2および信号SVA2が“L”になることで、ノードN1[2]の電位は、ノードSCIN2の電位に応じて変換する。

期間T3では、レジスタ175は通常動作を行っている。ノードQ[1]乃至Q[N]から、期間T2で書き込まれたデータD1乃至DNを出力する。この間、スキャンチェーンレジスタ部231をスキャン動作させて、スキャンチェーンレジスタ部231のデータ変更を行ってもよい。スキャンチェーンレジスタ部231のデータを変更した後、信号LDA1を“H”にすることで、レジスタ部230のデータを書き換えてもよい。スキャンチェーンレジスタ部232についても同様である。

期間T10では、パワーゲーティング動作が行われる。パワーゲーティング動作は、レジスタ175のバックアップ動作、電源オフ動作、レジスタ175のリカバリ動作に大別される。

期間T4では、レジスタ175のバックアップ動作が行われる。まず、信号SVA1を“H”にし、その後、スキャンクロック信号SCK1を“H”にすることで、レジスタ部230が格納しているデータD1乃至DNを、スキャンチェーンレジスタ部231のフリップフロップ回路41に書き込む。図8の例では、信号の制御を簡単化するため、スキャンクロック信号SCK2をスキャンクロック信号SCK1と共に、“H”にしているが、“L”で維持してもよい。

信号SVA1が“H”になることで、セレクタ40はラッチ回路30のノードAとフリップフロップ回路41の入力ノード間を導通する。スキャンクロック信号SCK1が“L”であるため、フリップフロップ回路41のノードN1にノードAのデータが書き込まれる。スキャンクロック信号SCK1が“H”に遷移することで、ノードN1とノードA間が非導通状態になり、かつノードN1[1]とノードSCIN1間が非導通状態になる。

なお、レジスタ部230が格納しているデータが、スキャンチェーンレジスタ部232からロードされたデータである場合、レジスタ部230のデータはスキャンチェーンレジスタ部232でバックアップされる。この場合は、信号SVA2を“H”にし、その後、スキャンクロック信号SCK2を“H”する。

次に、スキャンチェーンレジスタ部231、232のバックアップ動作が行われる。この間、信号SVB1、SVB2を“H”にする。信号SVB1が“H”になることで、フリップフロップ回路41のノードN1、NB1のデータが保持回路42のノードSN1、SN2に書き込まれる。信号SVB2が“H”になることで、フリップフロップ回路46のノードN1、NB1のデータが保持回路47のノードSN3、SN4に書き込まれる。

信号SVB1、SVB2を“L”にすることで、レジスタ175のバックアップ動作が終了する。

期間T5は、電源オフ動作が行われる。配線PLDDへの電位VDDの供給を停止する。配線PLDDは徐々に放電される。配線PLDDの電位が低下するため、ラッチ回路30、フリップフロップ回路41、46のデータは消失するが、保持回路42、47のデータは消失しない。

期間T6は、スキャンチェーンレジスタ部231、232のリカバリ動作が行われる。まず、配線PLDDに電位VDDの供給を開始する。配線PLDDの電位は上昇し、やがて電位VDDになる。

次に、信号LDB1、LDB2を“H”にし、かつスキャンクロック信号SCK1、SCL2を1クロック入力する。信号LDB1が“H”になることで、保持回路42は、ノードSN1、SN2のデータをフリップフロップ回路41のノードN1、NB1に書き込む。スキャンクロック信号SCK1の立ち上がりエッジに同期して、ノードN1のデータがノードSDO1に入力される。信号LDB2が“H”になることで、保持回路47は、ノードSN3、SN4のデータを、フリップフロップ回路46のノードN2、NB2に書き込む。スキャンクロック信号SCK2の立ち上がりエッジに同期して、ノードN2のデータはノードSDO2に入力される。

信号LDB1、LDB2を“L”にすることで、リカバリ動作が終了する。

期間T7では、レジスタ部230のリカバリ動作が行われる。期間T3の状態にレジスタ部230を復帰させるため、信号LDA1を“H”にする。期間T7のリカバリ動作は、期間T3のレジスタ部230のデータ更新動作と同じ動作であり、スキャンチェーンレジスタ部231が保持しているデータD1乃至DNが、一括してレジスタ部230にロードされる。信号LDA1を“L”にすることで、リカバリ動作が終了する。

期間T8ではレジスタ175は通常動作を行い、ノードQ[1]乃至Q[N]から、期間T7で書き込まれたデータD1乃至DNを出力する。

<コントローラICの他の構成例>

以下に、コントローラICの他の構成例を説明する。

以下に、コントローラICの他の構成例を説明する。

図9に、ソースドライバを内蔵しないコントローラICの構成例を示す。図10に示すコントローラIC117は、コントローラIC115の変形例であり、領域191を有する。コントローラ154は、領域191内の回路への電源供給を制御する。

領域191には、ソースドライバが設けられていない。そのため、表示ユニット110は、ソースドライバIC186を有する。ソースドライバIC186の数は、画素アレイ111の画素数に応じて決定される。

ゲートドライバ113と同様に、画素アレイ111の基板上にソースドライバを作製してもよい。

コントローラIC117に、TSドライバ126およびセンス回路127の一方または双方を設けてもよい。コントローラIC115も同様である。

検出回路157は、輪郭の検出を行うことができる。例えば、画像が有する物体等の認識を行うことができる。

また検出回路157により認識された物体等の輪郭を、補正回路165により強調する処理(エッジ強調処理)を行ってもよい。

また検出回路157は、白とびの検出、および黒つぶれの検出を行うことができる。白とびは例えば、ある輝度以上の画素がある個数以上隣接する場合、とすることができる。黒つぶれは例えば、ある輝度以下の画素がある個数以上隣接する場合、とすることができる。白とびが検出された画素を「白とび画素」、黒つぶれが検出された画素を「黒つぶれ画素」と呼ぶ。

なお、スキャンチェーンレジスタ部231およびスキャンチェーンレジスタ部232に例えば、白とびや、黒つぶれに対応する輝度、個数など特徴的なパラメータを格納し、検出回路157は該パラメータを用いて検出を行ってもよい。あるいはレジスタ175が、不揮発性レジスタを有する第3のスキャンチェーンレジスタを有し、第3のスキャンチェーンレジスタに検出回路157が処理を行うためのパラメータが格納されてもよい。

検出回路157がヒストグラム生成回路159を有する場合には、画像データのヒストグラムを作成し、解析を行うことにより白とびや黒つぶれを検出できる場合がある。

白とび画素が検出された場合には例えば、輝度の高い領域の階調を拡張させる処理を行う。ここで白とび画素が有する画像データについてのみ処理を行ってもよいし、全ての画像データについて処理を行ってもよい。

黒つぶれ画素が検出された場合には例えば、輝度の低い領域の階調を拡張させる処理を行う。ここで黒つぶれ画素が有する画像データについてのみ処理を行ってもよいし、全ての画像データについて処理を行ってもよい。

白とび画素や、黒つぶれ画素について、周囲の画素値に基づき補正データを作成することができる。該補正データに基づき、画像処理を行えばよい。例えば、輝度の高い領域の階調を拡張させる際に、白とび画素と隣接する画素の情報を用いて、白とび画素の輝度を推測してもよい。また例えば、輝度の低い領域の階調を拡張させる際に、黒つぶれ画素と隣接する画素の情報を用いて、黒つぶれ画素の輝度を推測してもよい。

ここで、インターフェース150に与えられる画像データが階調、あるいは輝度が圧縮されたデータであり、かつ、圧縮前の画像データとの差分データがインターフェース150に与えられる場合には、画像処理として、画像データに該差分データを加算する処理を行ってもよい。

<<動作例>>

表示装置100に関するコントローラIC115とレジスタ175の動作例について、出荷前と、表示装置100を有する電子機器の起動時、および通常動作時に分けて説明する。

表示装置100に関するコントローラIC115とレジスタ175の動作例について、出荷前と、表示装置100を有する電子機器の起動時、および通常動作時に分けて説明する。

<出荷前>

出荷前には、表示装置100の仕様等に関するパラメータを、レジスタ175に格納する。これらのパラメータには、例えば、画素数、タッチセンサ数、タイミングコントローラ173が各種タイミング信号の生成に用いるパラメータ、ソースドライバ180が表示素子を流れる電流を検出する電流検出回路を備えている場合、EL補正回路164の補正データ等がある。また、白とび、および黒つぶれを抑制するための画像処理に用いるパラメータが格納される。これらのパラメータは、レジスタ175以外に、専用のROMを設けて格納してもよい。

出荷前には、表示装置100の仕様等に関するパラメータを、レジスタ175に格納する。これらのパラメータには、例えば、画素数、タッチセンサ数、タイミングコントローラ173が各種タイミング信号の生成に用いるパラメータ、ソースドライバ180が表示素子を流れる電流を検出する電流検出回路を備えている場合、EL補正回路164の補正データ等がある。また、白とび、および黒つぶれを抑制するための画像処理に用いるパラメータが格納される。これらのパラメータは、レジスタ175以外に、専用のROMを設けて格納してもよい。

<起動時>

表示装置100を有する電子機器の起動時には、ホスト140より送られるユーザー設定等のパラメータを、レジスタ175に格納する。これらのパラメータには、例えば、表示の輝度や色調、タッチセンサの感度、省エネルギー設定(表示を暗くする、または表示を消す、までの時間)、また、ガンマ補正のカーブやテーブル等がある。なお、当該パラメータをレジスタ175に格納する際、コントローラ154からレジスタ175にクロック信号CK1乃至CK4及び当該クロック信号CK1乃至CK4に同期して当該パラメータに相当するデータが送信される。

表示装置100を有する電子機器の起動時には、ホスト140より送られるユーザー設定等のパラメータを、レジスタ175に格納する。これらのパラメータには、例えば、表示の輝度や色調、タッチセンサの感度、省エネルギー設定(表示を暗くする、または表示を消す、までの時間)、また、ガンマ補正のカーブやテーブル等がある。なお、当該パラメータをレジスタ175に格納する際、コントローラ154からレジスタ175にクロック信号CK1乃至CK4及び当該クロック信号CK1乃至CK4に同期して当該パラメータに相当するデータが送信される。

<通常動作>

通常動作には、動画等を表示している状態、静止画を表示している状態、表示を行わない状態等に分けられる。動画等を表示している状態は、画像処理部160、およびタイミングコントローラ173等は動作中であるが、レジスタ175のデータ変更は、スキャンチェーンレジスタ部231または232に対して行われるため、画像処理部160等への影響はない。スキャンチェーンレジスタ部231または232のデータ変更が終わった後、スキャンチェーンレジスタ部231または232のデータをレジスタ部230へ一括してロードすることで、レジスタ175のデータ変更が完了する。また、画像処理部160等は当該データに対応した動作に切り替わる。

通常動作には、動画等を表示している状態、静止画を表示している状態、表示を行わない状態等に分けられる。動画等を表示している状態は、画像処理部160、およびタイミングコントローラ173等は動作中であるが、レジスタ175のデータ変更は、スキャンチェーンレジスタ部231または232に対して行われるため、画像処理部160等への影響はない。スキャンチェーンレジスタ部231または232のデータ変更が終わった後、スキャンチェーンレジスタ部231または232のデータをレジスタ部230へ一括してロードすることで、レジスタ175のデータ変更が完了する。また、画像処理部160等は当該データに対応した動作に切り替わる。

[パラメータの一例]

画像処理部160が画像処理に用いるパラメータは、スキャンチェーンレジスタ部231または232に格納され、画像処理を行う際にはレジスタ部230にロードされる。

画像処理部160が画像処理に用いるパラメータは、スキャンチェーンレジスタ部231または232に格納され、画像処理を行う際にはレジスタ部230にロードされる。

パラメータの設定方式には、テーブル方式、関数近似方式がある。画像処理に用いるパラメータの一例を、図10(A)および(B)に示す。

図10(A)は、テーブル方式の一例を示す。図10(A)の横軸は画像処理前のデータ:Y(図中のData Y)、縦軸は画像処理後のデータ:Z(図中のData Z)をそれぞれ表す。スキャンチェーンレジスタ部231または232は例えば、画像データYnに対して、補正された画像データZnをパラメータとしてテーブルに格納される。テーブル方式では、当該テーブルに対応するパラメータを格納するレジスタを多数必要とするが、補正の自由度が高い。

一方、あらかじめ経験的に画像データYに対して、補正された画像データZを決められる場合には、図10(B)のように、関数近似方式を採用する構成が有効である。a1、a2、b2等がパラメータである。図10(B)に示すように、YとZとの関係が数式で決められている。YがY1以下の領域においてはZ=(a1)×Yの関係を有し、YがY1より大きくY2以下の領域においてはZ=(a2)×Y+(b2)の関係を有し、YがY2より大きい領域においてはZ=(a3)×Y+(b3)の関係を有する。スキャンチェーンレジスタ部231または232にはこれらの関係を表す式が格納される。図10(B)は区間毎に線形近似する方法を示しているが、非線形関数で近似する方法も可能である。関数近似方式では、補正の自由度は低いが、関数を定義するパラメータを格納するレジスタが少なくて済む。

画像処理前の画像データを用いて作成されたヒストグラムの解析結果を基に、画像処理を施すことが好ましい。また、ヒストグラムの解析を行うことにより、白とびや黒とびを検出できる場合がある。

タイミングコントローラ173が使用するパラメータは、例えば、図10(C)に示すように、タイミングコントローラ173の生成信号が、基準信号に対して“L”(または“H”)となるタイミングを示すものである。パラメータRa(またはRb)は、基準信号に対して“L”(または“H”)となるタイミングが、クロック何周期分であるかを示している。

図11(A)および(B)はヒストグラム生成回路を用いて作成された画像処理前のデータ:Yのヒストグラムである。横軸として、画像データが有する輝度を用いる。例えば、図11(A)では、図11(B)と比較して、輝度の高い領域において分布の偏りがみられる。図11(B)では白とびが発生している可能性があるため、白とびを抑制する画像処理を施すことが好ましい。なお、図11(A)では輝度の高い領域において、裾が凹の形状を有し単調減少するのに対し、図11(B)では輝度の最大値において輝度が単調減少する様子がみられず、むしろ増加する傾向がみられ、飽和がみられる。このような傾向は、白とびに繋がる場合がある。ここで減少および増加とは、ヒストグラムのカーブにおいて1回乃至数回の平均化処理を行った後に減少する傾向、および増加する傾向、がみられる場合を指してもよい。平均化処理として移動平均を用いてもよい。また、凹の形状を有するとは例えば、変化率が増加する場合や、二回微分が正の値を有する場合を指し、凸の形状を有するとは例えば、変化率が減少する場合や、二回微分が負の値を有する場合を指す。

<動作例2>

ここで一例として、白とびを抑制する画像処理を行う場合について、図12に示すフロー図を用いて説明する。

ここで一例として、白とびを抑制する画像処理を行う場合について、図12に示すフロー図を用いて説明する。

まずステップS000において、処理を開始する。次にステップS101において、画像データがインターフェース150に与えられる。与えられた画像データはフレームメモリ151に格納される。フレームメモリ151に格納された画像データはデコーダ152において伸長された後、検出回路157に入力される。

次にステップS102において、フレームメモリに格納された画像データについて、検出回路157が検出を行う。画像データにおいて白とび画素が検出された場合には、次のステップにおいて、画像処理を行う。なお、画像データにおいて白とび画素が検出されない場合でも、より優れた画質を提供するために、画像処理を行ってもよい。

次にステップS103において、画像処理を行う領域と、画像処理の内容を選択する。ここでは一例として、白とびが検出された領域において、白とび抑制の画像処理を行う。また、白とび抑制の画像処理を行う前に、エッジ処理を行ってもよい。画像処理の内容が選択されたら、次のステップにおいて画像処理のためのパラメータをレジスタに格納する。

次にステップS104において、画像処理に用いるパラメータをスキャンチェーンレジスタ部231または232に格納する。画像処理に用いるパラメータがあらかじめスキャンチェーンレジスタ部231または232に格納されている場合には、ステップS104をスキップしてもよい。あるいはステップS104において、あらかじめ格納されている値の変更を行ってもよい。

ここで白とび検出と黒つぶれ検出を連続で行う場合には例えば、ステップS104において、スキャンチェーンレジスタ部231に白とび抑制の画像処理を行うためのパラメータを、スキャンチェーンレジスタ部232に黒つぶれ抑制の画像処理を行うためのパラメータを、それぞれ保存する。

次にステップS105において、スキャンチェーンレジスタ部231または232に格納されたパラメータをレジスタ部230にロードし、該パラメータを基に画像データに処理を施す。処理後の画像データは、メモリ170に格納される。

ここで白とび検出と黒つぶれ検出を連続で行う場合には例えば、ステップS105において、スキャンチェーンレジスタ部231からレジスタ部230にパラメータをロードし、白とび抑制の画像処理を行った後、スキャンチェーンレジスタ部232からレジスタ部230にパラメータをロードし、黒つぶれ抑制の画像処理を行う。

最後に、ステップS200により、処理を終了する。

メモリ170に格納された画像データは、ソースドライバ180に出力される。メモリ170は、画像データを一時的に格納するためのメモリである。メモリ170は1フレーム分もしくは複数フレーム分の画像データを格納するフレームメモリとする構成、1行分もしくは複数行数分の画像データを格納するラインメモリとする構成が可能である。

なお、ステップS101乃至ステップS106において、「白とび画素」を「黒つぶれ画素」に置き換え、画像処理に用いるパラメータを「白とびを抑制する画像処理に用いるパラメータ(以降、パラメータW)から「黒つぶれを抑制する画像処理に用いるパラメータ(以降、パラメータB)に変更して処理を行うことにより、黒つぶれを抑制する画像処理とすることができる。また例えば、スキャンチェーンレジスタ部231にパラメータW、スキャンチェーンレジスタ部232にパラメータBと、が格納され、ステップS104において、パラメータWをレジスタ部230にロードして画像データに処理を施した後、続けて、パラメータBをレジスタ部230にロードして画像データに処理を施してもよい。

<動作例3>

以下には画像認識を行い、認識された結果に基づき画像処理を行う一例を図13に示すフロー図を用いて説明する。

以下には画像認識を行い、認識された結果に基づき画像処理を行う一例を図13に示すフロー図を用いて説明する。

まずステップS300において、処理を開始する。次にステップS301において、画像データがインターフェース150に与えられる。与えられた画像データはフレームメモリ151に格納される。フレームメモリ151に格納された画像データはデコーダ152において伸長された後、検出回路157に入力される。

次にステップS302において、フレームメモリに格納された画像データについて、検出回路157が検出を行う。ここでは一例として、画像のパターン認識を用いて、物体などを抽出する。例えば図14(A)に示すように、パターン認識を行い、画像に「うさぎ991」と「人間の女性992」が認識される例を示す。パターン認識には例えば、いわゆるAI(Artificial Intelligence)を用いた画像処理を用いることができる。例えば、ニューラルネットワーク(ディープニューラルネットワークなど)を用いた画像処理を用いることができる。ここでフレームメモリに格納される画像データは、1フレームの全体の画像データでもよいし、1フレームのうち、一部の領域が保存された時点において、検出回路157が検出を開始してもよい。このような場合には例えば、1フレームが、数回に分けてフレームメモリに保存される。またこのような場合に例えば、1フレームのうち「うさぎ911」を有する領域の画像データが保存された時点において、検出回路157が検出を開始し、「うさぎ991」が認識される場合がある。

次にステップS303において、画像処理を行う領域と、画像処理の内容を選択する。ここでは、第1の画像処理として「うさぎ991が検出された領域」に対して、第1の画像処理を行い、第2の画像処理として、「人間の女性992が検出された領域」に対して、第2の画像処理を行う。画像処理の内容が選択されたら、次のステップにおいて画像処理のためのパラメータをレジスタに格納する。

次にステップS304乃至ステップS305の処理を、画像処理を行う領域の数と、その処理内容に応じ、繰り返し行う。ここでは例えばまず、「うさぎ991が検出された領域」に対してステップS304乃至ステップS305の処理を行った後、「人間の女性992が検出された領域」に対してステップS304乃至ステップS305の処理を行う。ここで、スキャンチェーンレジスタ部231およびスキャンチェーンレジスタ部232には例えば、うさぎに特徴的なパラメータや、人間の女性に特徴的なパラメータが格納され、検出回路157は該パラメータを用いて検出を行うことが好ましい。

ステップS304において、画像処理に用いるパラメータをスキャンチェーンレジスタ部231または232に格納する。画像処理に用いるパラメータがあらかじめスキャンチェーンレジスタ部231または232に格納されている場合には、ステップS304をスキップしてもよい。あるいはステップS304において、あらかじめ格納されている値の変更を行ってもよい。スキャンチェーンレジスタ部231およびスキャンチェーンレジスタ部232に保存される画像処理用のパラメータは例えば、画像処理を行う対象物に対応したパラメータ、例えばうさぎや、人間の女性の、それぞれの色彩、輝度カーブ、等の特徴に近づくような画像処理を行うためのパラメータが格納される。またパラメータとして、人間の女性の輪郭において、白とびしやすい領域、例えば頬の領域、に関する情報を有することが好ましい。このように白とびしやすい領域に対して、白とび抑制の処理を行うことが好ましい。

ここで、第k回目の繰り返しにおいて用いるパラメータをスキャンチェーンレジスタ部231に保存し、第k+1回目の繰り返しにおいて用いるパラメータをスキャンチェーンレジスタ部232に保存し、スキャンチェーンレジスタ部231および232のパラメータを交互にレジスタ部230にロードする構成が可能である。このような構成とすることにより、スキャンチェーンレジスタにパラメータを繰り返し保存する必要がなく、したがって、パラメータの保存に要する時間を削減できるので、画像処理の演算速度を高めることができる。

次にステップS305において、スキャンチェーンレジスタ部231または232に格納されたパラメータをレジスタ部230にロードし、該パラメータを基に画像データに処理を施す。処理後の画像データは、レジスタ部230に格納される。最後に、ステップS400により、処理を終了する。

レジスタ部230に格納された画像データは、メモリ170を経て、ソースドライバ180に出力される。メモリ170は、画像データを一時的に格納するためのメモリである。

以上の処理を行うことにより、図14(B)に示すように、うさぎ991および人間の女性992がより明確に表現された画像を実現することができる。例えば、うさぎの陰影、人間の女性の顔の陰影、等がより明確に表現された画像となる。

[白とび抑制]

白とびとは例えば、画像データの輝度の高い領域、より具体的には画像データにおける輝度の最大値の0.9倍より高い輝度を有する領域、あるいは階調値が高い領域において充分な階調数で表現できない領域、もしくは、当該領域で表示コントラストの違いを十分には認識できない現象を指す。すなわち、本来は好ましい画像に比べて、階調が圧縮されている領域を指す。白つぶれの抑制とは例えば、画像データの輝度の高いい領域、あるいは階調値が高い領域において、表示装置の視認者の視覚特性に合わせて、よりはっきりとした画像を提供することを指す。

白とびとは例えば、画像データの輝度の高い領域、より具体的には画像データにおける輝度の最大値の0.9倍より高い輝度を有する領域、あるいは階調値が高い領域において充分な階調数で表現できない領域、もしくは、当該領域で表示コントラストの違いを十分には認識できない現象を指す。すなわち、本来は好ましい画像に比べて、階調が圧縮されている領域を指す。白つぶれの抑制とは例えば、画像データの輝度の高いい領域、あるいは階調値が高い領域において、表示装置の視認者の視覚特性に合わせて、よりはっきりとした画像を提供することを指す。

図15(A)は、輝度データ:XL(図中においてData XL)と輝度データ:YL(図中においてData YL)の関係を表すグラフである。輝度データ:XLは例えば、撮像装置で撮像した本来の画像データ、すなわち、より質の高い画像を提供できる画像データに対応する。また、表示装置の最高輝度が撮像装置で撮像可能な最高輝度より低い場合に、表示装置に合わせて高輝度側の画像データの階調を圧縮する必要がある。このようにして生成されたデータが輝度データ:YLに対応する。

本発明の一態様の表示装置において、最高輝度がより高い表示装置を用いるものとし、画像処理により輝度データ:XLにより近い画像データが提供されることが好ましい。

輝度データ:XLは例えば画像データの輝度の高い領域を圧縮する前のデータ、例えば撮像直後のデータである。ただし、撮像装置の受光部の性能により、撮像された時点の画像データにおいて既に輝度の高い領域が圧縮されている場合もある。

輝度データ:YLは、インターフェース150に与えられる画像データが有する輝度データである。輝度データ:YLにおいては、輝度データ:XLと比較して、輝度の高い領域の階調が圧縮されているため、画像処理部160において例えば、図12(B)に示すように、圧縮された階調を伸長させる処理を行い、輝度データ:ZL(図中においてData ZL)を作成する。本処理により、白とび画素が減少する。例えば本処理により、輝度の最大値近傍の領域を占める画素数が減少する。例えば本処理により、輝度の最大値の0.8倍より高い輝度、あるいは0.9倍より高い輝度、を有する画素数が減少する。

ここで図15(A)に示すように輝度データ:YLの輝度の最大値はL2であり、図15(B)に示すように輝度データ:Zの輝度の最大値はL3であり、図15(B)においてはL3はL2より大きい値を有するが、図15(C)に示すように画像処理を行った後、L3がL2に一致するようにレベル調整を行ってもよい。ここでL2’は、表示装置の最高輝度に相当する。

[黒つぶれ抑制]

黒つぶれとは例えば、画像データの輝度の低い領域、より具体的には画像データにおいて輝度の最大値の0.1倍より低い輝度を有する領域、もしくは、当該領域で表示コントラストの違いを十分には認識できない現象を指す。黒つぶれの抑制とは例えば、画像データの輝度の低い領域、あるいは階調値が低い領域において、表示装置の視認者の視覚特性に合わせて、よりはっきりとした画像を提供することを指す。

黒つぶれとは例えば、画像データの輝度の低い領域、より具体的には画像データにおいて輝度の最大値の0.1倍より低い輝度を有する領域、もしくは、当該領域で表示コントラストの違いを十分には認識できない現象を指す。黒つぶれの抑制とは例えば、画像データの輝度の低い領域、あるいは階調値が低い領域において、表示装置の視認者の視覚特性に合わせて、よりはっきりとした画像を提供することを指す。

図15(D)は、輝度データ:XL、輝度データ:YLおよび輝度データ:ZLの関係を表すグラフである。図12において、インターフェース150に与えられる輝度データ:YLに対して、視認者の視覚特性に合わせ、輝度の低い領域の階調を伸長させたデータが輝度データ:Zである。輝度データZにおいては、輝度の低い領域の階調、ここでは輝度がL4以下の領域の階調を伸長させるのとともに、輝度がL4より大きい領域の階調は圧縮を行うことにより輝度データ:Zの輝度の最大値を、輝度データ:YLの最大値L5と一致させている。なお、画像処理部160における画像処理の前後において、画像データの階調数は一致しなくてもよい。

例えば、画像処理前の画像データが8ビットの256階調のデータで、画像処理後の画像データが12ビットの4096階調のデータであってもよい。このような場合には輝度がL4より大きい領域の階調は圧縮は、輝度がL4以下の領域に対して相対的に圧縮されることを指し、処理前の画像データに比べれば輝度がL4以下の領域と、輝度がL4より大きい領域のいずれにおいても、階調は伸長される。

本処理により、黒つぶれ画素が減少する。例えば本処理により、輝度の最小値近傍の領域を占める画素数が減少する。例えば本処理により、輝度の最大値の0.2倍より低い輝度、あるいは0.1倍より低い輝度、を有する画素数が増加する。

[パラメータWおよびパラメータB]

パラメータWおよびパラメータBとして例えば、テーブルデータを用いることができる。画像データは例えば、各画素に対応するデータ、例えば輝度データ、階調値、等を有する。画像処理には例えば、各画素が有する輝度データ:YLと、該輝度データの変換後の輝度データ:ZLと、を対応付けるテーブルデータを用いることができる。

パラメータWおよびパラメータBとして例えば、テーブルデータを用いることができる。画像データは例えば、各画素に対応するデータ、例えば輝度データ、階調値、等を有する。画像処理には例えば、各画素が有する輝度データ:YLと、該輝度データの変換後の輝度データ:ZLと、を対応付けるテーブルデータを用いることができる。

あるいは、パラメータWおよびパラメータBとして例えば、輝度データ:YLと輝度データ:ZLの関係をあらわす数式を用いることができる。ここで該数式は、輝度の数値範囲ごとに応じてそれぞれ異なる数式であってもよい。

全ての画素の画像データに対して画像処理を行ってもよいが、ある条件を満たす画素の画像データのみに対して画像処理を行うことにより、画像処理に要する時間を短縮することができる。

外光の明るさに応じて、画像処理のパラメータを変更してもよい。一例として、外光が明るい場合には、輝度が低い領域の階調がより認識しづらい場合がある。このような場合には、外光の明るさに応じたパラメータをレジスタ175に格納し、光センサ143が検知する外光の明るさに応じたパラメータを用いて処理を行えばよい。

[IDS駆動]

静止画を表示中でIDS駆動が可能な状態では、レジスタ175は、例えば、領域190内の他の回路と同様、パワーゲーティングすることができる。この場合、スキャンチェーンレジスタ部231または232のデータを更新中であれば、レジスタ部230のデータをスキャンチェーンレジスタ部231または232にセーブすることが好ましい。

静止画を表示中でIDS駆動が可能な状態では、レジスタ175は、例えば、領域190内の他の回路と同様、パワーゲーティングすることができる。この場合、スキャンチェーンレジスタ部231または232のデータを更新中であれば、レジスタ部230のデータをスキャンチェーンレジスタ部231または232にセーブすることが好ましい。

パワーゲーティングから復帰する際は、信号RS、LDに従い、スキャンチェーンレジスタ部231および232のデータをレジスタ部230にロードする。このようにして、パワーゲーティング前と同じ状態で、レジスタ175のデータは有効となる。なお、パワーゲーティングの状態であっても、ホスト140よりレジスタ175のパラメータ変更要求があった場合、レジスタ175のパワーゲーティングを解除し、パラメータを変更することができる。

表示を行わない状態では、例えば、領域190内の回路(レジスタ175を含む)は、パワーゲーティングすることができる。この場合、ホスト140も停止することがあるが、フレームメモリ151およびレジスタ175は不揮発性であるので、パワーゲーティングから復帰する際には、ホスト140の復帰を待たずに、パワーゲーティング前の表示(静止画)を行うことができる。

例えば、折りたたみ式の携帯電話の表示部に表示装置100を適用する場合、開閉センサ144の信号によって、携帯電話が折りたたまれ、表示装置100の表示面が使用されないことが検出されたとき、領域190内の回路に加えて、センサコントローラ153、およびタッチセンサコントローラ184等をパワーゲーティングすることができる。

携帯電話が折りたたまれたとき、ホスト140の規格によっては、ホスト140が停止する場合がある。ホスト140が停止した状態で、携帯電話が再び展開されても、フレームメモリ151およびレジスタ175は不揮発性であるので、ホスト140から画像データ、各種制御信号等が送られる前に、フレームメモリ151内の画像データを表示することができる。

以上のように、レジスタ175はスキャンチェーンレジスタ部231および232と、レジスタ部230を有し、スキャンチェーンレジスタ部231または232に対してデータ変更を行うことで、画像処理部160およびタイミングコントローラ173等へ影響を与えることなく、スムーズなパラメータ変更を行うことができる。また、スキャンチェーンレジスタ部231および232の各レジスタは、OSトランジスタを用いた不揮発性レジスタであるため、表示装置の動作状況に合わせたパワーゲーティングが容易である。また、フレームメモリ151も不揮発性であるため、電源供給が再開された時、速やかに表示を再開することができる。パワーゲーティング状態への移行と復帰をスムーズに行うことができ、低消費電力化が可能なシステムを実現することができる。

(実施の形態2)

本実施の形態では、上記実施の形態に示す表示装置の詳細について説明を行う。

本実施の形態では、上記実施の形態に示す表示装置の詳細について説明を行う。

《ブロック図》

図16(A)は、表示ユニット90の構成を説明するためのブロック図である。表示ユニット90は、画素アレイ91と、ゲートドライバ34aと、ゲートドライバ34bと、ソースドライバ32と、を有する。図16(A)において、ゲートドライバ34a、34bは、画素アレイ91の左右にそれぞれ設けられている。

図16(A)は、表示ユニット90の構成を説明するためのブロック図である。表示ユニット90は、画素アレイ91と、ゲートドライバ34aと、ゲートドライバ34bと、ソースドライバ32と、を有する。図16(A)において、ゲートドライバ34a、34bは、画素アレイ91の左右にそれぞれ設けられている。

また、表示ユニット90は、各々が略平行に配設され、且つ、ゲートドライバ34a、34bによって電位が制御され複数の走査線GLと、各々が略平行に配設され、且つ、ソースドライバ32によって電位が制御される複数の信号線SLと、を有する。さらに、画素アレイ91はマトリクス状に配設された複数の画素36を有する。

画素アレイ91において、各走査線GLは、画素36のうち、いずれかの行に配設された複数の画素36と電気的に接続される。また、各信号線SLは、画素36のうち、いずれかの列に配設された複数の画素36に電気的に接続される。

また、ゲートドライバ34a、34bおよびソースドライバ32(以下、まとめて駆動回路と呼ぶ)が有するトランジスタは、画素36を構成するトランジスタと同時に形成することができる。

また、駆動回路部の一部または全部を他の基板上に形成して、表示ユニット90と電気的に接続してもよい。例えば、駆動回路部の一部または全部を、単結晶基板を用いたICチップで形成し、表示ユニット90と電気的に接続してもよい。上記ICチップの数は1つに限らず、画素36の数に応じて必要なだけ設ければよい。例えば、COG(Chip on glass)法またはCOF(Chip on Film)法を用いて、上記ICチップを表示ユニット90に設けることができる。

図16(B)は、図16(A)の画素アレイ91を、画素アレイ31a、31b、31c、31dの4つに分割し、ソースドライバ32をソースドライバ32a、32bの2つに分けて画素アレイの上下に配置した例を示している。画素アレイ31a、31bに含まれる画素36は、信号線SLaを介して、ソースドライバ32aと電気的に接続される。画素アレイ31c、31dに含まれる画素36は、信号線SLbを介して、ソースドライバ32bと電気的に接続される。なお、画素アレイ91の分割数は4つに限らず、任意の数で分割を行ってもよい。

図16(B)に示す構成は、1本の信号線に接続される画素36の数を少なくすることができる。すなわち、1本の信号線に接続される容量を小さくすることができる。その結果、表示ユニット90は、信号線に画像データを書き込む時間を短縮することができる。図16(B)に示す構成は、特に8K(7680×4320)など、高精細な表示ユニットに適用することが好ましい。例えば、4K(3840×2160)の画素数をもつ画素アレイを、画素アレイ31a乃至31dにそれぞれ適用することで、8Kの画素数をもつ表示ユニット90を実現することができる。

図17(A)は、図16(A)の信号線SLを、信号線SL1、SL2の2本に分割した例を示している。同じ列に配置された複数の画素36は、信号線SL1または信号線SL2と、交互に、電気的に接続される。

図17(A)に示す構成は、1本の信号線に接続される画素36の数を少なくすることができる。その結果、表示ユニット90は、信号線に画像データを書き込む時間を短縮することができる。

また、図16(B)に示す構成は、画素アレイと画素アレイの間に繋ぎ目が生じ、その影響が表示画像に表れてしまうが、図17(A)に示す構成は繋ぎ目が存在しないため、上述の問題を回避することができる。その結果、表示ユニット90は、繋ぎ目のない滑らかな画像を表示することができる。

なお、信号線SLを分割する数は2本に限定されない、例えば、図17(B)は信号線SLを信号線SL1、SL2、SL3、SL4の4本に分割した例である。

表示ユニット90は、図17(B)に示す構成にすることで、1本の信号線に接続される画素36の数をさらに少なくすることができる。その結果、表示ユニット90は、信号線に画像データを書き込む時間をより短縮することができる。また、繋ぎ目のない滑らかな画像を表示することができる。

《画素回路》

次に、上述の画素36に用いることができる回路構成について、図18を用いて説明を行う。

次に、上述の画素36に用いることができる回路構成について、図18を用いて説明を行う。

図18(A)に示す画素36は、トランジスタ3431と、容量素子3233と、液晶素子3432と、を有する。

トランジスタ3431のソース電極またはドレイン電極の一方は、信号線SLに電気的に接続され、他方はノード3436に電気的に接続される。トランジスタ3431のゲート電極は走査線GLに電気的に接続される。トランジスタ3431は、ノード3436へのデータ信号の書き込みを制御する機能を有する。

容量素子3233の一対の電極の一方は、特定の電位が供給される配線(以下、「容量線CL」ともいう。)に電気的に接続され、他方は、ノード3436に電気的に接続される。容量線CLの電位は、画素36の仕様に応じて適宜設定される。容量素子3233は、ノード3436に書き込まれたデータを保持する機能を有する。

液晶素子3432の一対の電極の一方は共通の電位(コモン電位)が与えられ、他方はノード3436に電気的に接続される。液晶素子3432に含まれる液晶は、ノード3436に書き込まれる電位により配向状態が決定される。

液晶素子3432のモードとしては、例えば、TNモード、STNモード、VAモード、ASM(Axially Symmetric Aligned Micro−cell)モード、OCB(Optically Compensated Birefringence)モード、FLC(Ferroelectric Liquid Crystal)モード、AFLC(AntiFerroelectric Liquid Crystal)モード、MVAモード、PVA(Patterned Vertical Alignment)モード、IPSモード、FFSモード、またはTBA(Transverse Bend Alignment)モードなどを用いてもよい。また、他の例として、ECB(Electrically Controlled Birefringence)モード、PDLC(Polymer Dispersed Liquid Crystal)モード、PNLC(Polymer Network Liquid Crystal)モード、ゲストホストモードなどがある。ただし、これに限定されず、様々なモードを用いることができる。

図18(B)に示す画素36は、トランジスタ3431と、容量素子3233と、トランジスタ3232と、発光素子3125と、を有する。

トランジスタ3431のソース電極またはドレイン電極の一方はデータ信号が与えられる信号線SLに電気的に接続され、他方はノード3435に電気的に接続される。トランジスタ3431のゲート電極はゲート信号が与えられる走査線GLに電気的に接続される。トランジスタ3431はデータ信号のノード3435への書き込みを制御する機能を有する。

容量素子3233の一対の電極の一方はノード3435に電気的に接続され、他方はノード3437に電気的に接続される。容量素子3233はノード3435に書き込まれたデータを保持する保持容量としての機能を有する。

トランジスタ3232のソース電極またはドレイン電極の一方は電位供給線VL_aに電気的に接続され、他方はノード3437に電気的に接続される。トランジスタ3232のゲート電極はノード3435に電気的に接続される。トランジスタ3232は、発光素子3125に流れる電流を制御する機能を有する。

発光素子3125のアノードまたはカソードの一方は電位供給線VL_bに電気的に接続され、他方はノード3437に電気的に接続される。

発光素子3125としては、例えば有機エレクトロルミネセンス素子(有機EL素子ともいう)などを用いることができる。ただし、これに限定されず、例えば無機材料からなる無機EL素子を用いても良い。

例えば、電位供給線VL_aはVDDを供給する機能を有する。また、電位供給線VL_bはVSSを供給する機能を有する。また、電位供給線VL_cはVSSを供給する機能を有する。

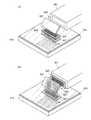

《断面図》

次に、表示ユニット90の構成例を示す断面図を図19および図20を用いて説明を行う。

次に、表示ユニット90の構成例を示す断面図を図19および図20を用いて説明を行う。

図19(A)、(B)に示す表示ユニット90は電極4015を有しており、電極4015はFPC4018が有する端子と異方性導電層4019を介して、電気的に接続されている。また、電極4015は、絶縁層4112、絶縁層4111、および絶縁層4110に形成された開口において配線4014と電気的に接続されている。電極4015は、第1の電極層4030と同じ導電層から形成されている。

また第1の基板4001上に設けられた画素36は、トランジスタを有しており、図19(A)では、画素36に含まれるトランジスタ3431を例示し、図19(B)では、画素36に含まれるトランジスタ3232を例示している。

また、トランジスタ3431、3232は、絶縁層4102上に設けられている。また、トランジスタ3431、3232は、絶縁層4102上に形成された電極517を有し、電極517上に絶縁層4103が形成されている。絶縁層4103上に半導体層512が形成されている。半導体層512上に電極510及び電極511が形成され、電極510及び電極511上に絶縁層4110及び絶縁層4111が形成され、絶縁層4110及び絶縁層4111上に電極516が形成されている。電極510及び電極511は、配線4014と同じ導電層で形成されている。

トランジスタ3431、3232において、電極517はゲート電極としての機能を有し、電極510はソース電極またはドレイン電極の一方としての機能を有し、電極511はソース電極またはドレイン電極の他方としての機能を有し、電極516はバックゲート電極としての機能を有する。

トランジスタ3431、3232はボトムゲート及びバックゲートを有することで、オン電流を増大させることができる。また、トランジスタの閾値を制御することができる。なお、電極516は、製造工程を簡略化するため、場合によっては省略してもよい。

トランジスタ3431、3232において、半導体層512はチャネル形成領域としての機能を有する。半導体層512として、結晶シリコン、多結晶シリコン、非晶質シリコン、酸化物半導体、有機半導体、などを用いればよい。また、必要に応じて、半導体層512の導電率を高めるため、または、トランジスタの閾値を制御するために、半導体層512に不純物を導入してもよい。

非晶質シリコンを用いたトランジスタは、多結晶シリコンを用いたトランジスタ等に比べ、工程が簡単で、コストが安い。また大型の基板で作製しやすいといった利点がある。なお、一般に、トランジスタに用いる非晶質シリコンは水素を多く含む。このため、水素を多く含む非晶質シリコンを「水素化アモルファスシリコン」または「a−Si:H」という場合がある。また、非晶質シリコンは、多結晶シリコンよりも低温で形成できるため、作製工程中の最高温度を下げることができる。よって、基板、導電層、および絶縁層などに、耐熱性の低い材料を用いることができる。このように、非晶質シリコンは生産性が極めて高い。本発明の一態様の表示装置を大型のディスプレイに用いる場合には特に、非晶質シリコンを用いることが好ましい。

多結晶シリコンを用いたトランジスタは、非晶質シリコンを用いたトランジスタと比較して、電界効果移動度をより高くすることができる。よって、トランジスタに接続される負荷が大きい場合においても、高い駆動周波数で動作させることができる。

多結晶シリコンは例えば、非晶質シリコンをレーザを用いて結晶化させるにより作製することができる。また、非晶質シリコンの一部の領域のみを結晶化させてもよい。

また、酸化物半導体をチャネル領域に有するトランジスタは、非晶質シリコンを用いたトランジスタと比較して、電界効果移動度をより高くすることができる。よって、トランジスタに接続される負荷が大きい場合においても、高い駆動周波数で動作させることができる。また、酸化物半導体をチャネル領域に有するトランジスタは、生産性が高く、大型の基板で作成しやすいといった利点がある。また酸化物半導体をチャネル領域に有するトランジスタはオフ電流が極めて低く、酸化物半導体をチャネル領域に有するトランジスタを用いた表示装置は消費電力を低減できる場合がある。

半導体層512として金属酸化物を用いた場合、半導体層512はインジウム(In)を含むことが好ましい。半導体層512がインジウムを含む金属酸化物の場合、半導体層512はキャリア移動度(電子移動度)が高くなる。また、半導体層512は、元素Mを含む酸化物半導体であると好ましい。元素Mは、好ましくは、アルミニウム(Al)、ガリウム(Ga)またはスズ(Sn)などとする。そのほかの元素Mに適用可能な元素としては、ホウ素(B)、シリコン(Si)、チタン(Ti)、鉄(Fe)、ニッケル(Ni)、ゲルマニウム(Ge)、イットリウム(Y)、ジルコニウム(Zr)、モリブデン(Mo)、ランタン(La)、セリウム(Ce)、ネオジム(Nd)、ハフニウム(Hf)、タンタル(Ta)、タングステン(W)などがある。ただし、元素Mとして、前述の元素を複数組み合わせても構わない場合がある。元素Mは、例えば、酸素との結合エネルギーが高い元素である。例えば、酸素との結合エネルギーがインジウムよりも高い元素である。また、半導体層512は、亜鉛(Zn)を含む金属酸化物であると好ましい。亜鉛を含む金属酸化物は結晶化しやすくなる場合がある。

半導体層512は、インジウムを含む金属酸化物に限定されない。半導体層512は、例えば、亜鉛スズ酸化物、ガリウムスズ酸化物などの、インジウムを含まず、亜鉛を含む金属酸化物、ガリウムを含む金属酸化物、スズを含む金属酸化物などであっても構わない。

また、図19(A)、(B)に示す表示ユニット90は、容量素子3233を有する。容量素子3233は、電極511と電極4021が絶縁層4103を介して重なる領域を有する。電極4021は、電極517と同じ導電層で形成されている。

図19(A)は、表示素子として液晶素子を用いた液晶表示ユニットの一例である。図19(A)において、表示素子である液晶素子3432は、第1の電極層4030、第2の電極層4031、及び液晶層4008を含む。なお、液晶層4008を挟持するように配向膜として機能する絶縁層4032、絶縁層4033が設けられている。第2の電極層4031は第2の基板4006側に設けられ、第1の電極層4030と第2の電極層4031は液晶層4008を介して重畳する。

またスペーサ4035は絶縁層を選択的にエッチングすることで得られる柱状のスペーサであり、第1の電極層4030と第2の電極層4031との間隔(セルギャップ)を制御するために設けられている。なお球状のスペーサを用いていても良い。

表示素子として、液晶素子を用いる場合、サーモトロピック液晶、低分子液晶、高分子液晶、高分子分散型液晶、強誘電性液晶、反強誘電性液晶等を用いることができる。これらの液晶材料は、条件により、コレステリック相、スメクチック相、キュービック相、カイラルネマチック相、等方相等を示す。

また、液晶材料の固有抵抗は、1×109Ω・cm以上であり、好ましくは1×1011Ω・cm以上であり、さらに好ましくは1×1012Ω・cm以上である。なお、本明細書における固有抵抗の値は、20℃で測定した値とする。

トランジスタ3431にOSトランジスタを用いた場合、トランジスタ3431は、オフ状態における電流値(オフ電流値)を低くすることができる。よって、画像信号等の電気信号の保持時間を長くすることができ、電源オン状態では書き込み間隔も長く設定できる。よって、リフレッシュ動作の頻度を少なくすることができるため、消費電力を抑制する効果を奏する。

また、表示ユニットにおいて、ブラックマトリクス(遮光層)、偏光部材、位相差部材、反射防止部材などの光学部材(光学基板)などを適宜設けてもよい。例えば、偏光基板及び位相差基板による円偏光を用いてもよい。また、光源としてバックライト、サイドライトなどを用いてもよい。

図19(B)は、表示素子としてEL素子などの発光素子を用いた表示ユニットの一例である。EL素子は有機EL素子と無機EL素子に区別される。

有機EL素子は、電圧を印加することにより、一方の電極から電子、他方の電極から正孔がそれぞれEL層に注入される。そして、それらキャリア(電子および正孔)が再結合することにより、発光性の有機化合物が励起状態を形成し、その励起状態が基底状態に戻る際に発光する。このようなメカニズムから、このような発光素子は、電流励起型の発光素子と呼ばれる。なお、EL層は、発光性の化合物以外に、正孔注入性の高い物質、正孔輸送性の高い物質、正孔ブロック材料、電子輸送性の高い物質、電子注入性の高い物質、またはバイポーラ性の物質(電子輸送性及び正孔輸送性が高い物質)などを有していてもよい。EL層は、蒸着法(真空蒸着法を含む)、転写法、印刷法、インクジェット法、塗布法などの方法で形成することができる。

無機EL素子は、その素子構成により、分散型無機EL素子と薄膜型無機EL素子とに分類される。分散型無機EL素子は、発光材料の粒子をバインダ中に分散させた発光層を有するものであり、発光メカニズムはドナー準位とアクセプター準位を利用するドナー−アクセプター再結合型発光である。薄膜型無機EL素子は、発光層を誘電体層で挟み込み、さらにそれを電極で挟んだ構造であり、発光メカニズムは金属イオンの内殻電子遷移を利用する局在型発光である。

図19(B)は、発光素子3125として有機EL素子を用いた例を説明する。

図19(B)において、発光素子3125は、画素36に設けられたトランジスタ3232と電気的に接続している。なお発光素子3125の構成は、第1の電極層4030、発光層4511、第2の電極層4031の積層構造であるが、この構成に限定されない。発光素子3125から取り出す光の方向などに合わせて、発光素子3125の構成は適宜変えることができる。

隔壁4510は、有機絶縁材料、又は無機絶縁材料を用いて形成する。特に感光性の樹脂材料を用い、第1の電極層4030上に開口部を形成し、その開口部の側面が連続した曲率を持って形成される傾斜面となるように形成することが好ましい。

発光層4511は、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。

発光素子3125に酸素、水素、水分、二酸化炭素等が侵入しないように、第2の電極層4031および隔壁4510上に保護層を形成してもよい。保護層としては、窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、DLC(Diamond Like Carbon)などを形成することができる。また、第1の基板4001、第2の基板4006、及びシール材4005によって封止された空間には充填材4514が設けられ密封されている。このように、外気に曝されないように気密性が高く、脱ガスの少ない保護フィルム(貼り合わせフィルム、紫外線硬化樹脂フィルム等)やカバー材でパッケージング(封入)することが好ましい。

充填材4514としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂または熱硬化樹脂を用いることができ、PVC(ポリビニルクロライド)、アクリル樹脂、ポリイミド、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)などを用いることができる。また、充填材4514に乾燥剤が含まれていてもよい。

シール材4005には、ガラスフリットなどのガラス材料や、二液混合型の樹脂などの常温で硬化する硬化樹脂、光硬化性の樹脂、熱硬化性の樹脂などの樹脂材料を用いることができる。また、シール材4005に乾燥剤が含まれていてもよい。

また、必要であれば、発光素子の射出面に偏光板、又は円偏光板(楕円偏光板を含む)、位相差板(λ/4板、λ/2板)、カラーフィルタなどの光学フィルムを適宜設けてもよい。また、偏光板又は円偏光板に反射防止膜を設けてもよい。例えば、表面の凹凸により反射光を拡散し、映り込みを低減できるアンチグレア処理を施すことができる。

また、発光素子をマイクロキャビティ構造とすることで、色純度の高い光を取り出すことができる。また、マイクロキャビティ構造とカラーフィルタを組み合わせることで、映り込みが低減し、表示画像の視認性を高めることができる。

第1の電極層4030、第2の電極層4031は、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、インジウム錫酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。

また、第1の電極層4030、第2の電極層4031はタングステン(W)、モリブデン(Mo)、ジルコニウム(Zr)、ハフニウム(Hf)、バナジウム(V)、ニオブ(Nb)、タンタル(Ta)、クロム(Cr)、コバルト(Co)、ニッケル(Ni)、チタン(Ti)、白金(Pt)、アルミニウム(Al)、銅(Cu)、銀(Ag)などの金属、またはその合金、もしくはその金属窒化物から一種以上を用いて形成することができる。

また、第1の電極層4030、第2の電極層4031として、導電性高分子(導電性ポリマーともいう)を含む導電性組成物を用いて形成することができる。導電性高分子としては、いわゆるπ電子共役系導電性高分子を用いることができる。例えば、ポリアニリンまたはその誘導体、ポリピロールまたはその誘導体、ポリチオフェンまたはその誘導体、もしくは、アニリン、ピロールおよびチオフェンの2種以上からなる共重合体またはその誘導体等が挙げられる。

発光素子3125が光を外部に取り出すため、少なくとも第1の電極層4030または第2の電極層4031の一方が透明であればよい。表示ユニットは、光の取り出し方によって、上面射出(トップエミッション)構造と、下面射出(ボトムエミッション)構造と、両面射出(デュアルエミッション)構造に分類される。上面射出構造は、基板4006から光を取り出す場合をいう。下面射出構造は、基板4001から光を取り出す場合をいう。両面射出構造は、基板4006と基板4001の両方から光を取り出す場合をいう。例えば、上面射出構造の場合、第2の電極層4031を透明にすればよい。例えば、下面射出構造の場合、第1の電極層4030を透明にすればよい。例えば、両面射出構造の場合、第1の電極層4030及び第2の電極層4031を透明にすればよい。

図20(A)は、図19(A)に示すトランジスタ3431に、トップゲート型のトランジスタを設けた場合の断面図を示している。同様に、図20(B)は、図19(B)に示すトランジスタ3232に、トップゲート型のトランジスタを設けた場合の断面図を示している。

図20(A)、(B)のトランジスタ3431、3232において、電極517はゲート電極としての機能を有し、電極510はソース電極またはドレイン電極の一方としての機能を有し、電極511はソース電極またはドレイン電極の他方としての機能を有する。

図20(A)、(B)のその他の構成要素の詳細については、図19(A)、(B)の記載を参照すればよい。

本実施の形態は、少なくともその一部を本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

(実施の形態3)

本実施の形態では、トランジスタの半導体層に用いることのできる多結晶シリコンの結晶化方法及びレーザ結晶化装置の一例について説明する。

本実施の形態では、トランジスタの半導体層に用いることのできる多結晶シリコンの結晶化方法及びレーザ結晶化装置の一例について説明する。

結晶性の良好な多結晶シリコン層を形成するには、基板上に非晶質シリコン層を設け、当該非晶質シリコン層にレーザ光を照射して結晶化することが好ましい。例えば、レーザ光を線状ビームとし、当該線状ビームを非晶質シリコン層に照射しながら基板を移動させることで、基板上の所望の領域に多結晶シリコン層を形成することができる。

線状ビームを用いた方法は、スループットが比較的良好である。一方で、ある領域に対してレーザ光が相対的に移動しながら複数回照射される方法であるため、レーザ光の出力変動及びそれに起因するビームプロファイルの変化による結晶性のばらつきが生じやすい。例えば、当該方法で結晶化させた半導体層を表示装置の画素が有するトランジスタに用いると、結晶性のばらつきに起因したランダムな縞模様が表示に見えることがある。

また、線状ビームの長さは基板の一辺の長さ以上であることが理想的であるが、線状ビームの長さは、レーザ発振器の出力と光学系の構成によって制限される。したがって、大型基板の処理では基板面内を折り返してレーザ照射することが現実的である。そのため、レーザ光をオーバーラップして照射する領域が生じる。当該領域の結晶性は、他の領域の結晶性と異なりやすいため、当該領域では表示ムラが生じることがある。

上記のような問題を抑えるために、基板上に形成した非晶質シリコン層に局所的にレーザ照射を行って結晶化させてもよい。局所的なレーザ照射では、結晶性のばらつきの少ない多結晶シリコン層を形成しやすい。

図21(A)は、基板上に形成した非晶質シリコン層に局所的にレーザ照射を行う方法を説明する図である。

光学系ユニット821から射出されるレーザ光826は、ミラー822で反射されてマイクロレンズアレイ823に入射する。マイクロレンズアレイ823は、レーザ光826を集光して複数のレーザビーム827を形成する。

ステージ815には、非晶質シリコン層840を形成した基板830が固定される。非晶質シリコン層840に複数のレーザビーム827を照射することで、複数の多結晶シリコン層841を同時に形成することができる。

マイクロレンズアレイ823が有する個々のマイクロレンズは、表示装置の画素ピッチに合わせて設けることが好ましい。又は、画素ピッチの整数倍の間隔で設けてもよい。いずれの場合においても、レーザ照射とステージ815のX方向又はY方向の移動を繰り返すことで、全ての画素に対応した領域に多結晶シリコン層を形成することができる。

例えば、マイクロレンズアレイ823が画素ピッチでX方向にM行、Y方向にN列(M、Nは自然数)のマイクロレンズを有するとき、まず所定の開始位置でレーザ光を照射し、M行N列の多結晶シリコン層を形成する。そして、Y方向にM行分の距離だけ移動させてレーザ光を照射し、M行2N列の多結晶シリコン層841を形成する。当該工程を繰り返し行うことで所望の領域に複数の多結晶シリコン層841を形成することができる。また、折り返してレーザ照射工程を行う場合は、X方向にN列分の距離だけ移動させてレーザ照射を行い、さらにY方向にM行分の距離の移動とレーザ光の照射を繰り返せばよい。

なお、レーザ光の発振周波数とステージ815の移動速度を適切に調整すれば、ステージ815を一方向に移動させながらレーザ照射を行う方法でも、画素ピッチで多結晶シリコン層を形成することができる。

レーザビーム827のサイズは、例えば、一つのトランジスタの半導体層全体が含まれる程度の面積とすることができる。又は、一つのトランジスタのチャネル領域全体が含まれる程度の面積とすることができる。又は、一つのトランジスタのチャネル領域の一部が含まれる程度の面積とすることができる。これらは、必要とするトランジスタの電気特性に応じて使い分ければよい。

なお、一つの画素に複数のトランジスタを有する表示装置を対象とした場合、レーザビーム827は、一つの画素内の各トランジスタの半導体層全体が含まれる程度の面積とすることができる。また、レーザビーム827は、複数の画素が有するトランジスタの半導体層全体が含まれる程度の面積としてもよい。