JP2014522066A - Interoperation of I/O devices with computing hosts - Google Patents

Interoperation of I/O devices with computing hostsDownload PDFInfo

- Publication number

- JP2014522066A JP2014522066AJP2014525104AJP2014525104AJP2014522066AJP 2014522066 AJP2014522066 AJP 2014522066AJP 2014525104 AJP2014525104 AJP 2014525104AJP 2014525104 AJP2014525104 AJP 2014525104AJP 2014522066 AJP2014522066 AJP 2014522066A

- Authority

- JP

- Japan

- Prior art keywords

- command

- data

- map

- standard

- computing host

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0628—Interfaces specially adapted for storage systems making use of a particular technique

- G06F3/0655—Vertical data movement, i.e. input-output transfer; data movement between one or more hosts and one or more storage devices

- G06F3/0659—Command handling arrangements, e.g. command buffers, queues, command scheduling

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0602—Interfaces specially adapted for storage systems specifically adapted to achieve a particular effect

- G06F3/0604—Improving or facilitating administration, e.g. storage management

- G06F3/0607—Improving or facilitating administration, e.g. storage management by facilitating the process of upgrading existing storage systems, e.g. for improving compatibility between host and storage device

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0602—Interfaces specially adapted for storage systems specifically adapted to achieve a particular effect

- G06F3/061—Improving I/O performance

- G06F3/0611—Improving I/O performance in relation to response time

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0668—Interfaces specially adapted for storage systems adopting a particular infrastructure

- G06F3/0671—In-line storage system

- G06F3/0673—Single storage device

- G06F3/0679—Non-volatile semiconductor memory device, e.g. flash memory, one time programmable memory [OTP]

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/10—Address translation

- G06F12/1027—Address translation using associative or pseudo-associative address translation means, e.g. translation look-aside buffer [TLB]

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0668—Interfaces specially adapted for storage systems adopting a particular infrastructure

- G06F3/067—Distributed or networked storage systems, e.g. storage area networks [SAN], network attached storage [NAS]

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Human Computer Interaction (AREA)

- Techniques For Improving Reliability Of Storages (AREA)

- Information Retrieval, Db Structures And Fs Structures Therefor (AREA)

- Signal Processing For Digital Recording And Reproducing (AREA)

Abstract

Translated fromJapaneseDescription

Translated fromJapanese 関連出願の相互参照

本出願の優先権利益の主張を、(それがある場合には、適宜)添付の出願データシート、請求、または送達状において行う。本出願の種類によって許容される範囲内で、本出願はこの参照によりあらゆる目的で以下の出願を組み込むものであり、以下の出願はすべて、発明がなされた時点において本出願と所有者を同じくするものである。 CROSS-REFERENCE TO RELATED APPLICATIONS A claim to priority benefit of this application, if any, is made in the attached Application Data Sheet, claim, or transmittal letter, as appropriate. To the extent permitted by the nature of this application, this application incorporates by this reference for all purposes the following applications, all of which are commonly owned with this application at the time the invention was made:

2011年8月9日付で出願された、Earl T.COHENを筆頭発明者とする、「I/O DEVICE AND COMPUTING HOST INTEROPERATION」という名称の、米国仮出願(整理番号第SF−11−15号および出願番号第61/521,739号);2011年9月6日付で出願された、Earl T.COHENを筆頭発明者とする、「I/O DEVICE AND COMPUTING HOST INTEROPERATION」という名称の、米国仮出願(整理番号第SF−11−15A号および出願番号第61/531,551号);および2011年10月5日付で出願された、Earl T.COHENを筆頭発明者とする、「I/O DEVICE AND COMPUTING HOST INTEROPERATION」という名称の、米国仮出願(整理番号第SF−11−15B号および出願番号第61/543,666号)。U.S. Provisional Application No. SF-11-15 and Application No. 61/521,739, filed August 9, 2011, entitled "I/O DEVICE AND COMPUTSING HOST INTEROPERATION," with Earl T. COHEN as lead inventor; U.S. Provisional Application No. SF-11-15A and Application No. 61/531,551, filed September 6, 2011, entitled "I/O DEVICE AND COMPUTSING HOST INTEROPERATION," with Earl T. COHEN as lead inventor; and U.S. Provisional Application No. SF-11-15A and Application No. 61/531,551, filed October 5, 2011, entitled "I/O DEVICE AND COMPUTSING HOST INTEROPERATION," with Earl T. COHEN as lead inventor. U.S. Provisional Application No. SF-11-15B and Application No. 61/543,666, entitled "I/O DEVICE AND COMPUTSING HOST INTEROPERATION," with COHEN as lead inventor.

分野:コンピューティングホストおよび入出力デバイスの技術の進歩が、使用の性能、効率、及び有用性の改善を提供するために必要とされる。Area: Advances in computing host and input/output device technology are needed to provide improved performance, efficiency, and usability of use.

関連技術:公知である、または周知であるものとして明記されない限り、コンテキスト、定義、または比較を目的とするものを含む本明細書における技法および概念の言及は、そのような技法または概念が以前から公知であり、あるいは先行技術の一部であることの容認と解釈すべきではない。特許、特許出願、および出版物を含む、本明細書で引用されるあらゆる参照文献は(それがある場合には)、具体的に組み込まれているか否かを問わず、あらゆる目的で、この参照によりその全体が本明細書に組み込まれるものである。Related Art: Unless expressly stated as known or well known, reference to techniques and concepts herein, including for purposes of context, definition, or comparison, should not be construed as an admission that such techniques or concepts were previously known or part of the prior art. All references cited herein, including patents, patent applications, and publications, if any, are hereby incorporated by this reference in their entirety for all purposes, whether or not specifically incorporated.

本発明は多くの方法で実施されてよく、例えば、プロセス、製造品、装置、システム、組成物、ならびに、コンピュータ可読記憶媒体(ディスクといった光学的大容量記憶装置および/または磁気的大容量記憶装置、フラッシュストレージといった不揮発性記憶を有する集積回路など)や、プログラム命令が光通信リンクまたは電子通信リンク上で送られるコンピュータネットワークといったコンピュータ可読媒体として実施されてよい。詳細な説明では、上記の分野における使用のコスト、収益性、性能、効率、および有用性の改善を可能にする本発明の1つ若しくはそれ以上の実施形態の説明を行う。詳細な説明は、詳細な説明の残りの部分の理解を容易にするための概説を含む。概説は、本明細書で説明する概念に従うシステム、方法、製造品、およびコンピュータ可読媒体の1つ若しくはそれ以上の例示的実施形態を含む。結論の項でより詳細に論じるように、本発明は、発行される特許請求の範囲内のあらゆる可能な改変形態および変形形態を包含するものである。The present invention may be implemented in many ways, for example, as a process, an article of manufacture, an apparatus, a system, a composition of matter, and a computer readable medium, such as an optical mass storage device such as a disk and/or a magnetic mass storage device, an integrated circuit having non-volatile storage such as flash storage, and a computer network in which program instructions are transmitted over optical or electronic communication links. The detailed description provides a description of one or more embodiments of the present invention that enable improvements in cost, profitability, performance, efficiency, and usefulness of use in the above fields. The detailed description includes an overview to facilitate understanding of the remainder of the detailed description. The overview includes one or more exemplary embodiments of systems, methods, articles of manufacture, and computer readable media according to the concepts described herein. As discussed in more detail in the concluding section, the present invention is intended to embrace all possible modifications and variations within the scope of the issued claims.

図面の参照符号の一覧

本発明の1つ若しくはそれ以上の実施形態の詳細な説明を、以下で、本発明の選択された詳細を図示する添付の図を併用して行う。本発明を実施形態との関連で説明する。実施形態は、本明細書では、単なる例示であると理解されるものであり、本発明は、明確に、本明細書中の実施形態のいずれか若しくは全部に、またはいずれか若しくは全部によって限定されるものではなく、本発明は、多数の代替形態、改変形態、および均等物を包含するものである。説明が単調にならないように、様々な言葉によるラベル(これに限定されるものではないが、最初の、最後の、ある一定の、様々な、別の、他の、特定の、選択の、いくつかの、目立ったなど)が実施形態のセットを区別するために適用される場合がある。本明細書で使用する場合、そのようなラベルは、明確に、質を伝えるためのものでも、いかなる形の好みや先入観を伝えるためのものでもなく、単に、別々のセットを都合よく区別するためのものにすぎない。開示するプロセスのいくつかの動作の順序は本発明の範囲内で変更可能である。多様な実施形態がプロセス、方法、および/またはプログラム命令の各特徴の差異を説明するのに使用される場合は常に、所定の、または動的に決定される基準に従って、複数の多様な実施形態にそれぞれ対応する複数の動作モードの1つの静的選択および/または動的選択を行う他の実施形態が企図されている。以下の説明では、本発明の十分な理解を提供するために、多数の具体的詳細を示す。それらの詳細は例として示すものであり、本発明は、それらの詳細の一部または全部がなくても、特許請求の範囲に従って実施されうる。わかりやすくするために、本発明に関連した技術分野で公知の技術資料は、本発明が不必要に曖昧になることのないように詳細に説明していない。A detailed description of one or more embodiments of the present invention is provided below in conjunction with the accompanying figures illustrating selected details of the invention. The present invention is described in connection with the embodiments. The embodiments are understood herein to be merely exemplary, and the present invention is not expressly limited to or by any or all of the embodiments herein, and the present invention encompasses numerous alternatives, modifications, and equivalents. To avoid monotony in the description, various worded labels (including but not limited to first, last, certain, various, another, other, particular, selection, several, prominent, etc.) may be applied to distinguish sets of embodiments. As used herein, such labels are not intended to expressly convey a quality or any form of preference or prejudice, but merely to conveniently distinguish between separate sets. The order of some operations of the disclosed processes may be changed within the scope of the present invention. Whenever various embodiments are used to describe differences in the respective features of a process, method, and/or program instructions, other embodiments are contemplated that statically and/or dynamically select one of a plurality of operating modes, each corresponding to a plurality of various embodiments, according to predetermined or dynamically determined criteria. In the following description, numerous specific details are set forth to provide a thorough understanding of the invention. These details are provided by way of example, and the invention may be practiced according to the claims without some or all of these details. For the sake of clarity, technical materials known in the art related to the invention have not been described in detail so as not to unnecessarily obscure the invention.

概説

この概説は、詳細な説明のより迅速な理解を助けるために含まれるにすぎず、本発明は、(それがある場合には、明示的な例を含む)この概説で提示される概念だけに限定されるものではなく、どんな概説の段落も、必然的に、主題全体の縮約された見方であり、網羅的な、または限定的な記述であることを意味するものではない。例えば、以下の概説は、スペースおよび編成によりある一定の実施形態だけに限定される概要情報を提供するものである。特許請求の範囲が究極的にそこに導かれることになる実施形態を含む多くの他の実施形態があり、それらを本明細書の残りの部分にわたって論じる。 Overview This overview is included merely to aid in a quicker comprehension of the detailed description, and the present invention is not limited to only the concepts presented in this overview (including explicit examples, if any), and any overview paragraph is necessarily a condensed view of the entire subject matter and is not meant to be an exhaustive or limiting description. For example, the following overview provides summary information that is limited to only certain embodiments due to space and organization. There are many other embodiments, including those to which the claims will ultimately be directed, which are discussed throughout the remainder of this specification.

頭字語

ここで定義される様々な縮めた表現の略語(例えば、頭字語)の少なくとも一部が本明細書において使用される特定の要素を指す。 Acronyms At least some of the various contraction abbreviations (eg, acronyms) defined herein refer to particular elements used herein.

ある実施形態では、ソリッドステートディスク(SSD)といった入出力デバイスが、ホストインターフェースを介して、本明細書では単にホストとも呼ぶホスト・コンピューティング・システムに接続される。様々な実施形態によれば、接続は、PCIe、SATA、SAS、USB、イーサネット(登録商標)、ファイバチャネル、または2台の電子デバイスを接続するのに適した任意の他のインターフェースを含む1若しくはそれ以上のホストインターフェースを介したものである。別の実施形態では、ホストインターフェースは、電気信号インターフェースおよびホストプロトコルを含む。ホストプロトコルは、入出力デバイスにデータを送り、入出力デバイスからデータを受け取るコマンドを含む、入出力デバイスと通信するための標準コマンドを定義する。In one embodiment, an I/O device, such as a solid state disk (SSD), is connected to a host computing system, also referred to herein simply as a host, via a host interface. According to various embodiments, the connection is through one or more host interfaces, including PCIe, SATA, SAS, USB, Ethernet, Fibre Channel, or any other interface suitable for connecting two electronic devices. In another embodiment, the host interface includes an electrical signal interface and a host protocol. The host protocol defines standard commands for communicating with the I/O device, including commands for sending data to and receiving data from the I/O device.

ホスト・コンピューティング・システムは、本明細書でコンピューティングホストと呼ぶ(または単に「ホスト」と呼ぶ場合もある)1若しくはそれ以上の処理要素を含む。様々な実施形態によれば、コンピューティングホストは、オペレーティングシステムおよび/またはハイパーバイザといった監視ソフトウェア、監視ソフトウェアと入出力デバイスとの間で通信するためのドライバ、アプリケーションソフトウェア、ならびにBIOS、のうちの1若しくはそれ以上を実行する。別の実施形態では、ドライバの一部分の一部または全部またはコピーがBIOS、オペレーティングシステム、ハイパーバイザ、およびアプリケーションのうちの1若しくはそれ以上に組み込まれる。さらに別の実施形態では、アプリケーションは、バイパスモードでドライバを介してコマンドを送ることによって、および/または入出力デバイスとの直接通信を有することによって、入出力デバイスとより直接的に通信することができるようになっている。入出力デバイスとの直接通信を有するアプリケーションの一例は、PCIe入出力デバイスの仮想機能(VF)によって提供される。ドライバは入出力デバイスの一次機能と通信して入出力デバイスを全体にわたって構成し、1若しくはそれ以上のアプリケーションが、それぞれの仮想機能によって入出力デバイスと直接通信する。仮想機能は、アプリケーションの各々が入出力デバイスの少なくとも一部分をアプリケーションの専用入出力デバイスとして扱うことを可能にする。A host computing system includes one or more processing elements, referred to herein as a computing host (or sometimes simply as a "host"). According to various embodiments, the computing host executes one or more of the following: monitoring software, such as an operating system and/or a hypervisor, drivers for communicating between the monitoring software and the I/O devices, application software, and a BIOS. In another embodiment, some or all of a portion of the driver or a copy is incorporated into one or more of the BIOS, the operating system, the hypervisor, and the application. In yet another embodiment, an application is able to communicate more directly with an I/O device by sending commands through the driver in a bypass mode and/or by having direct communication with the I/O device. One example of an application having direct communication with an I/O device is provided by a virtual function (VF) of a PCIe I/O device. A driver communicates with a primary function of the I/O device to configure the I/O device throughout, and one or more applications communicate directly with the I/O device through their respective virtual functions. The virtual functions allow each of the applications to treat at least a portion of the I/O device as the application's dedicated I/O device.

ホストプロトコルの標準コマンドは、ホストプロトコルが標準化される時点の入出力デバイスの特徴および機能のセットを提供する。入出力デバイスの中には、標準ホストプロトコルでサポートされていない特徴および/または機能を有し、よって、コンピューティングホストが標準ホストプロトコルを使用して制御することができないものがある。したがって、ある実施形態では、非標準の特徴および/または機能が、以下のうちの1若しくはそれ以上を含む技術によってホストプロトコルに追加される:予約コマンドコードを使用すること;ベンダ特有のコマンドを使用すること;既存のコマンド内の予約フィールドを使用すること;不使用のアドレスビットといった、特定の入出力デバイスによって使用されないコマンドのある特定のフィールド内のビットを使用すること;SATAにおけるSET FEATURESコマンドによるものと同様に、機能レジスタに新しい特徴を追加すること;コマンドを集約し、および/または融合することによるもの;ならびに当分野で公知の他の技術。非標準の特徴および/または機能の使用は、任意選択で、入出力デバイスと通信することができるようにした非標準のドライバおよび/またはアプリケーションの使用と組み合わされる。The standard commands of the host protocol provide a set of features and functions of the I/O device at the time the host protocol is standardized. Some I/O devices have features and/or functions that are not supported by the standard host protocol and therefore cannot be controlled by a computing host using the standard host protocol. Thus, in some embodiments, non-standard features and/or functions are added to the host protocol by techniques including one or more of the following: using reserved command codes; using vendor-specific commands; using reserved fields in existing commands; using bits in certain fields of the command that are not used by a particular I/O device, such as unused address bits; adding new features to a feature register, similar to the SET FEATURES command in SATA; by aggregating and/or fusing commands; and other techniques known in the art. The use of non-standard features and/or functions is optionally combined with the use of non-standard drivers and/or applications that are capable of communicating with the I/O device.

本明細書において、標準コマンドの非標準修飾子とは、上記の技術のいずれかを使用して、標準ホストプロトコルでサポートされていない非標準の特徴および/または機能で標準コマンドを拡張することを指す。様々な実施形態では、非標準修飾子(またはその部分)を、任意選択で、(標準)コマンドによって使用され、または(標準)コマンドと共に提供されるヒントと呼ぶ。第1の例では、非標準修飾子は、ホストプロトコル内でコマンドの一部として符号化され、もっぱらそのコマンドのみに影響を及ぼす(「一度に1つ」のヒントなど)。第2の例では、非標準修飾子は、ホストプロトコル内でコマンドの一部として符号化され、例えば後続のコマンドのうちの1つに対する別の非標準修飾子によって一時的に使用不可とされない限り、または、例えば別のコマンドに対する別の非標準修飾子によって、すべてのそれ以後のコマンドについて使用不可とされない限り、後続のコマンドに対して有効のままである(「スティッキーな」ヒントなど)。第3の例では、非標準修飾子は、SATAにおけるSET FEATURESコマンドによるものと同様に、モード設定コマンドによって構成レジスタにおいて使用可能とされ、例えば別のモード設定コマンドによって明示的に使用不可とされない限り有効のままである。これらの例の多くの組み合わせおよび変形が可能である。As used herein, a non-standard modifier of a standard command refers to extending a standard command with non-standard features and/or functionality not supported by the standard host protocol using any of the techniques described above. In various embodiments, the non-standard modifier (or a portion thereof) is optionally referred to as a hint used by or provided with the (standard) command. In a first example, the non-standard modifier is encoded as part of the command in the host protocol and affects only that command (e.g., a "one at a time" hint). In a second example, the non-standard modifier is encoded as part of the command in the host protocol and remains in effect for subsequent commands (e.g., a "sticky" hint) unless it is temporarily disabled, e.g., by another non-standard modifier for one of the subsequent commands, or disabled for all subsequent commands, e.g., by another non-standard modifier for another command. In a third example, non-standard modifiers are enabled in the configuration register by a mode set command, similar to the SET FEATURES command in SATA, and remain in effect unless explicitly disabled, e.g., by another mode set command. Many combinations and variations of these examples are possible.

様々な実施形態によれば、非標準の特徴および/または機能は、以下のうちの1若しくはそれ以上に影響を及ぼす:コマンドの実行;コマンドの能力および/または性能;コマンドと関連付けられたデータの扱いおよび/または処理;複数のコマンド間の関係;複数のコマンドのデータ間の関係;コマンドのデータが切り捨てられるという指示;コマンドのデータが訂正不能であるという指示;コマンドのデータタイプの仕様;コマンドのデータのデータアクセスタイプの仕様;複数のコマンドのデータについてのデータ順序付けの仕様;複数のコマンドのデータ間のデータ関係の仕様;任意の他のデータ値、データタイプ、データシーケンス、データ関係、データ宛先、またはデータプロパティの仕様;能力および/または性能といった入出力デバイスのプロパティ;ならびに、入出力デバイスの動作および/またはコマンドおよび/若しくはデータの処理、および/またはデータの記憶、取得および/若しくは再利用に影響を及ぼす任意の他の特徴および/または機能。According to various embodiments, the non-standard features and/or functions affect one or more of the following: execution of a command; the capabilities and/or performance of a command; the handling and/or processing of data associated with a command; relationships between multiple commands; relationships between data of multiple commands; an indication that data of a command is to be truncated; an indication that data of a command is uncorrectable; a specification of a data type for a command; a specification of a data access type for the data of the command; a specification of data ordering for data of multiple commands; a specification of data relationships between data of multiple commands; a specification of any other data value, data type, data sequence, data relationship, data destination, or data property; properties of the I/O device, such as capabilities and/or performance; and any other features and/or functions that affect the operation of the I/O device and/or the processing of commands and/or data, and/or the storage, retrieval, and/or reuse of data.

ある実施形態および/または使用シナリオでは、コマンドが複数のLBAのうちの1つを含み、マップが、任意選択で、および/または選択的に、コマンドのLBAをマップの複数のエントリのうちの1つと関連付ける。マップのエントリの各々は、入出力デバイスのNVM内の位置、および/またはLBAと関連付けられたデータがNVMに存在しない(割り当てられていない、割り当て解除されている、削除されている、NVMから切り捨てられているなど)という指示を含む。様々な実施形態によれば、コマンドを受け取ったことに応答して、入出力デバイスは以下のうちの1若しくはそれ以上を実行する:LBAと関連付けられたマップのエントリにアクセスする;LBAと関連付けられたマップのエントリにコマンドの非標準修飾子の指示を記憶する;LBAと関連付けられたマップのエントリから前のコマンドの非標準修飾子の指示を取得する;およびコマンドを受け取ったことに応答して入出力デバイスによって実行される他の動作。マップのエントリからの非標準修飾子を記憶し、および/または取得することにより、非標準修飾子の影響を、LBAのうちの特定のものと関連付け、および/または複数のコマンドにわたって持続させることが可能になる。例えば、コマンドは、複数のデータバンドのうちの1固定データバンドであるデータ宛先を指定する特定の非標準修飾子を含む。指定の固定データバンドにコマンドのデータを記憶することに加えて、特定の非標準修飾子の指示も、コマンドのLBAと関連付けられたマップのエントリに記憶される。コマンドのデータのその後の再利用動作では、コマンドのLBAと関連付けられたマップのエントリにアクセスし、特定の非標準修飾子の指示に従って、再利用動作にデータを再利用して指定の固定データバンド戻させることが可能になる。In certain embodiments and/or usage scenarios, the command includes one of a plurality of LBAs, and the map optionally and/or selectively associates the LBA of the command with one of a plurality of entries in the map. Each of the entries in the map includes a location in the NVM of the I/O device and/or an indication that the data associated with the LBA is not present in the NVM (not allocated, deallocated, deleted, truncated from the NVM, etc.). According to various embodiments, in response to receiving the command, the I/O device performs one or more of the following: accesses the entry in the map associated with the LBA; stores an indication of the command's non-standard qualifier in the entry in the map associated with the LBA; retrieves an indication of the non-standard qualifier of a previous command from the entry in the map associated with the LBA; and other actions performed by the I/O device in response to receiving the command. Storing and/or retrieving the non-standard qualifier from the entry in the map allows the effect of the non-standard qualifier to be associated with a particular one of the LBAs and/or to persist across multiple commands. For example, the command includes a particular non-standard modifier that specifies a data destination that is a fixed data band of multiple data bands. In addition to storing the command's data in the specified fixed data band, an indication of the particular non-standard modifier is also stored in an entry of the map associated with the command's LBA. A subsequent reclamation operation of the command's data can access the entry of the map associated with the command's LBA and follow the indication of the particular non-standard modifier to cause the reclamation operation to reclaim the data back into the specified fixed data band.

データのタイプを指定する非標準修飾子の例には、圧縮不能といったデータの圧縮性の仕様(specification)や、データベースジャーナルとしての使用といったデータの使用モデルの仕様が含まれる。場合によっては、(仕様や、マップに記録されている以前に提供された仕様といった)特定のタイプのものであると(例えば、入出力デバイスおよび/またはホストによって)識別されたデータは、任意選択で、および/または選択的に、入出力デバイスによってより効率よく処理される。ある使用シナリオでは、例えば、データベース・ジャーナル・タイプのものであると識別されたデータは、任意選択で、および/または選択的に、複数のデータバンドのうちの、データベース・ジャーナルの類型データのために確保されたデータベース・ジャーナル用データバンドに記憶される。様々な実施形態において、データベース・ジャーナル用データバンドは、固定サイズのものであり、一杯になると、データベース・ジャーナル用データバンド内の最も古いデータは、任意選択で、および/または選択的に、自動削除される。Examples of non-standard qualifiers for specifying a type of data include a specification of the compressibility of the data, such as incompressible, or a specification of a usage model of the data, such as use as a database journal. In some cases, data identified (e.g., by the I/O device and/or host) as being of a particular type (such as a specification or a previously provided specification recorded in a map) is optionally and/or selectively processed more efficiently by the I/O device. In one usage scenario, for example, data identified as being of a database journal type is optionally and/or selectively stored in a database journal data band of multiple data bands reserved for database journal type data. In various embodiments, the database journal data band is of a fixed size, and when full, the oldest data in the database journal data band is optionally and/or selectively automatically deleted.

データアクセスタイプを指定する非標準修飾子の例には、読み出し/書き込みアクセスタイプの仕様、略読み出しアクセスタイプ(read−mostly access type)の仕様、略書き込みアクセスタイプの仕様(write−mostly access type)、追記型(読み出し専用ともいう)アクセスタイプの仕様、および一時アクセスタイプの仕様が含まれる。場合によっては、(仕様や、マップに記録されている以前に提供された仕様といった)特定のアクセスタイプを有するものであると(例えば、入出力デバイスおよび/またはホストによって)識別されたデータは、任意選択で、および/または選択的に、入出力デバイスによってより効率よく処理される。第1の例では、データが読み取られ、または書き込まれる相対頻度を特定することは、任意選択で、および/または選択的に、入出力デバイスが、データの書き込み、アクセス、読み出し、および/または再利用をより効率よく可能にするようなやり方で、および/またはそのような位置にデータを都合よく記憶することを可能にする。第2の例では、入出力デバイスによって追記型であると識別されているデータへの標準書き込みアクセスが、任意選択で、および/または選択的に、誤りとして扱われる。Examples of non-standard qualifiers that specify data access types include a read/write access type specification, a read-mostly access type specification, a write-mostly access type specification, a write-only access type specification, and a temporary access type specification. In some cases, data identified (e.g., by the I/O device and/or host) as having a particular access type (such as a specification or a previously provided specification recorded in a map) is optionally and/or selectively processed more efficiently by the I/O device. In a first example, identifying the relative frequency at which data is read or written optionally and/or selectively allows the I/O device to conveniently store the data in a manner and/or location that allows the data to be written, accessed, read, and/or reused more efficiently. In a second example, standard write accesses to data that is identified by the I/O device as being write-once are optionally and/or selectively treated as an error.

ある実施形態では、一時アクセスタイプの仕様は、データが入出力デバイスによって記憶されることを可能にし、さらに、任意選択で、および/または選択的に、入出力デバイスが、コンピューティングホストからそうするよう求めるコマンドを受け取っていなくても、データを削除し、および/または削減すること(「自動削減」など)を可能にする。例えば、ストレージの特定の部分が一時的であると識別することが、任意選択で、および/または選択的に、入出力デバイスが、ストレージのその部分を再利用するのではなく削減することを可能にする。様々な実施形態によれば、入出力デバイスによって削除され、または削減された一時データへのコンピューティングホストによるその後のアクセスは、以下のうちの1若しくはそれ以上を返す:データが削除され、または削減されたという指示;誤り指示;特定のパターンおよび/または値を含むデータ;ならびにデータが入出力デバイスによって削除され、または削減されたというコンピューティングへの任意の他の指示。In some embodiments, the specification of a temporary access type allows the data to be stored by the I/O device and further, optionally and/or selectively, allows the I/O device to delete and/or reduce the data (e.g., "auto-reducing") even without receiving a command from the computing host to do so. For example, identifying a particular portion of storage as temporary may optionally and/or selectively allow the I/O device to reduce rather than reclaim that portion of storage. According to various embodiments, subsequent access by the computing host to the temporary data deleted or reduced by the I/O device returns one or more of the following: an indication that the data has been deleted or reduced; an error indication; data containing a particular pattern and/or value; and any other indication to the computing host that the data has been deleted or reduced by the I/O device.

様々な実施形態において、リセット後一時アクセスタイプの仕様は、データが入出力デバイスによって記憶されることを可能にし、さらに、任意選択で、および/または選択的に、入出力デバイスが、コンピューティングホストからそうするよう求めるコマンドを受け取っていなくても、ただし、入出力デバイスおよび/または入出力デバイスを含むシステムの後続の電源サイクルおよび/またはリセットの後に限って、データを削除し、および/または削減すること(「自動切り捨て」など)を可能にする。例えば、ページファイルといったある特定のオペレーティング・システム・データおよび/またはメムキャッシュディー(memcached)アプリケーションのデータといった特定のアプリケーションのデータは、システムの電源サイクルおよび/またはリセットの後で無効になる。ある実施形態では、リセット後一時アクセスタイプの指示は、2ビットカウンタといったカウンタを含む。グローバルカウンタの値を使用して、リセット後一時アクセスタイプの指示のカウンタが初期化される。グローバルカウンタは、入出力デバイスおよび/またはシステムの電源サイクルおよび/またはリセットごとに増分される。リセット後一時アクセスタイプの指示を有する、入出力デバイスのNVMの一部分といったストレージの特定の部分が、リセット後一時アクセスタイプの指示のカウンタがグローバルカウンタと一致するかどうかに従って、再利用のためにストレージのその特定の部分を処理するときに、選択的に切り捨てられる。さらに別の実施形態では、複数のグローバルカウンタがあり、グローバルカウンタの各々は、任意選択で、および/または選択的に、独立に増分され、リセット後一時アクセスタイプの指示は、グローバルカウンタの個々のカウンタの仕様をさらに含む。ビットマスクや固定値といったカウンタ以外の技術が、様々な実施形態において、ストレージの特定の部分が再利用されるときに選択的に切り捨てられるべきであるかどうか識別するのに使用される。In various embodiments, the specification of the temporary access type after reset allows the data to be stored by the I/O device and, optionally and/or selectively, allows the I/O device to delete and/or reduce (e.g., "auto-truncate") the data even if it has not received a command to do so from the computing host, but only after a subsequent power cycle and/or reset of the I/O device and/or the system including the I/O device. For example, certain operating system data, such as a page file, and/or certain application data, such as memcached application data, are invalidated after a power cycle and/or reset of the system. In one embodiment, the indication of temporary access type after reset includes a counter, such as a two-bit counter. The value of the global counter is used to initialize the counter of indications of temporary access type after reset. The global counter is incremented for each power cycle and/or reset of the I/O device and/or the system. A particular portion of storage, such as a portion of an I/O device's NVM, having an indication of a temporary access type after reset is selectively truncated when processing the particular portion of storage for reclamation according to whether a counter in the indication of the temporary access type after reset matches a global counter. In yet another embodiment, there are multiple global counters, each of which is optionally and/or selectively incremented independently, and the indication of the temporary access type after reset further includes a specification of an individual counter of the global counters. Techniques other than counters, such as bit masks or fixed values, are used in various embodiments to identify whether a particular portion of storage should be selectively truncated when reclaimed.

さらに別の実施形態では、電源サイクルおよび/またはリセットの指示は、リセット後一時アクセスタイプの指示を有するストレージの部分が後で再利用のために処理されるときにストレージのその部分が切り捨てられることが可能であることを指示するためにコンピューティングホストから提供される信号である。第1の例では、仮想機械を用いる環境において、コンピューティングホストから提供される信号は、仮想機械のリセットおよび/または終了の指示である。第2の例では、メムキャッシュディーアプリケーションを用い、コンピューティングホストから提供される信号は、メムキャッシュディーアプリケーションのリセットおよび/または終了の指示である。第3の例では、電源サイクルおよび/またはリセットの指示は、入出力デバイスの仮想機能の機能レベルのリセットである。ある使用シナリオでは、LBAの特定の範囲といった、仮想機能と関連付けられた入出力デバイスのNVMの部分だけが、機能レベルのリセットによる影響を受ける。In yet another embodiment, the power cycle and/or reset indication is a signal provided from a computing host to indicate that the portion of storage having a reset temporary access type indication may be truncated when that portion of storage is subsequently processed for reclamation. In a first example, in an environment using a virtual machine, the signal provided from the computing host is an indication to reset and/or terminate the virtual machine. In a second example, using a memcache-dee application, the signal provided from the computing host is an indication to reset and/or terminate the memcache-dee application. In a third example, the power cycle and/or reset indication is a function-level reset of a virtual function of an I/O device. In one usage scenario, only the portion of the NVM of the I/O device associated with the virtual function, such as a particular range of LBAs, is affected by the function-level reset.

データ順序付けを指定する非標準修飾子の例には、順次データ順序付けの仕様、およびアトミックデータ順序付けの仕様が含まれる。場合によっては、(仕様や、マップに記録されている以前に提供された仕様といった)特定のデータ順序付けのものであると(例えば、入出力デバイスおよび/またはホストによって)識別されたデータは、任意選択で、および/または選択的に、入出力デバイスによってより効率よく処理される。第1の例では、データが順次データ順序付けに属すると特定することは、任意選択で、および/または選択的に、入出力デバイスが、データの書き込み、アクセス、読み出し、および/または再利用をより効率よく可能にするようなやり方で、および/またはそのような位置にデータを都合よく記憶することを可能にする。第2の例では、データがアトミックデータ順序付けに属すると特定することは、任意選択で、および/または選択的に、入出力デバイスが、アトミックデータ順序付けのデータを1単位として都合よく扱うことを可能にし、アトミックデータ順序付けのデータの全部がコンピューティングホストによって識別可能であるように正常に書き込まれること、またはアトミックデータ順序付けのデータが全く書き込まれないことを保証することを可能にする。ある実施形態では、データのアトミックシーケンスを書き込むことは、シーケンスの開始および/または終了を指示するログ情報といったメタデータを書き込むことを含む。Examples of non-standard qualifiers that specify data ordering include a sequential data ordering specification and an atomic data ordering specification. In some cases, data identified (e.g., by the I/O device and/or host) as being of a particular data ordering (such as a specification or a previously provided specification recorded in a map) is optionally and/or selectively processed more efficiently by the I/O device. In a first example, identifying data as belonging to a sequential data ordering optionally and/or selectively allows the I/O device to conveniently store the data in a manner and/or location that allows the data to be written, accessed, read, and/or reused more efficiently. In a second example, identifying data as belonging to an atomic data ordering optionally and/or selectively allows the I/O device to conveniently treat the atomic data ordering data as a unit and ensure that either all of the atomic data ordering data is successfully written as identifiable by the computing host, or none of the atomic data ordering data is written. In one embodiment, writing an atomic sequence of data includes writing metadata, such as log information, that indicates the start and/or end of the sequence.

データ関係を指定する非標準修飾子の例には、複数のデータ項目間の読み出しおよび/または書き込みの関連付けの仕様が含まれる。場合によっては、(仕様や、マップに記録されている以前に提供された仕様といった)特定のデータ関係のものであると(例えば、入出力デバイスおよび/またはホストによって)識別されたデータは、任意選択で、および/または選択的に、入出力デバイスによってより効率よく処理される。例えば、2つのデータ項目間の読み出しデータ関係を特定することは、任意選択で、および/または選択的に、入出力デバイスが、データ項目のうちの第1の項目が読み取られるときに、データ項目のうちの第2の項目を都合よくプリフェッチすることを可能にする。ある使用例および/またはシナリオでは、第1のデータ項目はファイルシステム内のファイルのラベルであり、第2のデータ項目はファイルの対応する範囲である。様々な実施形態によれば、データ関係は以下のうちの1若しくはそれ以上である:1対1;1対多;多対1;多対多;書き込みコマンドと比較すると読み出しコマンドについては異なるなど、コマンドによって異なるデータ関係;およびデータ項目間の任意の他の関係。Examples of non-standard qualifiers for specifying data relationships include the specification of a read and/or write association between multiple data items. In some cases, data identified (e.g., by an I/O device and/or host) as being of a particular data relationship (such as a specification or a previously provided specification recorded in a map) is optionally and/or selectively processed more efficiently by an I/O device. For example, identifying a read data relationship between two data items optionally and/or selectively allows an I/O device to advantageously pre-fetch a second one of the data items when a first one of the data items is read. In one use case and/or scenario, the first data item is a label of a file in a file system and the second data item is a corresponding range of the file. According to various embodiments, the data relationship is one or more of the following: one-to-one; one-to-many; many-to-one; many-to-many; a data relationship that varies by command, such as different for a read command compared to a write command; and any other relationship between data items.

データ宛先を指定する非標準修飾子の例には、(特定のフラッシュ記憶要素や、例えばNVMの要素間でのデータ拡散を可能にするためのフラッシュ記憶要素の集合体といった)NVMの特定の部分の仕様、階層型ストレージ層の仕様、ストレージのタイプの仕様、および複数のデータバンドのうちの1つの仕様が含まれる。場合によっては、(仕様や、マップに記録されている以前に提供された仕様といった)特定のデータ宛先のものであると(例えば、入出力デバイスおよび/またはホストによって)識別されたデータは、任意選択で、および/または選択的に、入出力デバイスによってより効率よく処理される。第1の例では、データが指定のタイプのストレージに優先的に記憶されていることを特定することは、入出力デバイスが、任意選択で、および/または選択的に、SLCフラッシュ対MLCフラッシュ、フラッシュ対MRAM、あるいは揮発性メモリ対NVMといった、異なる特性の複数のメモリのうちの1つにデータを都合よく記憶することを可能にする。メモリの異なる特性は以下のうちの1若しくはそれ以上を含む:揮発性;アクセス時間、待ち時間、および/またはバンド幅といった性能;読み出し、書き込み、または消去の時間;能力;信頼性;寿命;低レベル誤り訂正および/または冗長性機能;高レベル誤り訂正および/または冗長性機能;ならびに他のメモリ特性。第2の例では、データが複数のデータバンドのうちの指定のデータバンドに記憶されるべきであることを特定することは、任意選択で、および/または選択的に、入出力デバイスが、データを指定のデータバンドに都合よく記憶して、書き込み速度、再利用速度、再利用頻度、書き込み増幅、およびデータストレージの他の特性のうちの1若しくはそれ以上を改善することを可能にする。Examples of non-standard qualifiers specifying data destinations include the specification of a particular portion of the NVM (such as a particular flash storage element or a collection of flash storage elements to allow data spreading among elements of the NVM), the specification of a hierarchical storage tier, the specification of a type of storage, and the specification of one of multiple data bands. In some cases, data identified (e.g., by the I/O device and/or host) as being of a particular data destination (such as a specification or a previously provided specification recorded in a map) is optionally and/or selectively processed more efficiently by the I/O device. In a first example, identifying that the data is preferentially stored in a specified type of storage allows the I/O device to optionally and/or selectively store the data advantageously in one of multiple memories of different characteristics, such as SLC flash vs. MLC flash, flash vs. MRAM, or volatile memory vs. NVM. The different characteristics of the memory include one or more of the following: volatility; performance such as access time, latency, and/or bandwidth; read, write, or erase time; capacity; reliability; lifetime; low level error correction and/or redundancy capabilities; high level error correction and/or redundancy capabilities; and other memory characteristics. In a second example, identifying that the data should be stored in a specified data band of the multiple data bands optionally and/or selectively enables an input/output device to advantageously store the data in the specified data band to improve one or more of write speed, reuse speed, reuse frequency, write amplification, and other characteristics of data storage.

コマンド関係を指定する非標準修飾子の例には、コマンド間の好ましい、または必要とされる相対順序を課すコマンド優先順位の仕様、および少なくともいくつかのタイプのコマンド間の境界を課すコマンドバリアの仕様が含まれる。例えば、書き込みコマンド・バリア・タイプのコマンドバリアは、読み出しコマンドに対しては透過的であるが、書き込みコマンドに対しては非透過的であり、書き込みコマンドバリアが、すべての以前に実行依頼された書き込みコマンドが書き込みコマンドバリアの完了の前に完了するよう保証することを可能にする。Examples of non-standard qualifiers that specify command relationships include the specification of command priority, which imposes a preferred or required relative order between commands, and the specification of command barriers, which impose boundaries between at least some types of commands. For example, a write command barrier type of command barrier is transparent to read commands but opaque to write commands, allowing the write command barrier to ensure that all previously submitted write commands complete before the completion of the write command barrier.

集約され、および/または融合されたコマンドの例は、1単位として扱われ、実行されないかまとめて実行されるかのどちらかである、2若しくはそれ以上のコマンドの組み合わせである。例えば、非標準修飾子は、融合コマンドシーケンスの開始、継続、または終了を指定する。融合コマンドシーケンスのコマンドは、すべてのコマンドが正常に完了しない限り、コマンドのいずれの影響も現れないようなアトミックなやり方で実行される。融合コマンドシーケンスの一例が比較−書き込みシーケンスであり、このシーケンスでは、後続の書き込みコマンドの影響は、先行する比較コマンドが、例えば比較が等しいことによって正常に行われた場合に限って現れる。様々な実施形態によれば、融合コマンドシーケンスのコマンドは、順次に、並列に、ホストプロトコルの順序付け規則によって決定される順序で、コマンドが入出力デバイスによって受け取られる順序で、および任意の順序で、のうちの1若しくはそれ以上のとして実行される。An example of an aggregated and/or fused command is a combination of two or more commands that are treated as a unit and are either not executed or executed together. For example, non-standard modifiers specify the beginning, continuation, or end of a fused command sequence. The commands of the fused command sequence are executed in an atomic manner such that the effect of any of the commands is not seen unless all of the commands complete successfully. An example of a fused command sequence is a compare-write sequence, where the effect of a subsequent write command is seen only if the preceding compare command was successful, e.g., by comparing equal. According to various embodiments, the commands of the fused command sequence are executed as one or more of: sequentially, in parallel, in an order determined by the ordering rules of the host protocol, in the order in which the commands are received by the I/O device, and in any order.

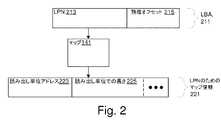

一部の実施形態では、SSDといった入出力装置がSSDコントローラを含む。SSDコントローラはホストインターフェースとSSDのNVMとの間のブリッジとして働き、SSDのホストインターフェースを介してコンピューティングホストから送られるホストプロトコルのコマンドを実行する。コマンドの少なくとも一部は、SSDに、コンピューティングホストから送られたデータおよびコンピューティングホストに送られるデータについて、それぞれ、NVMの書き込みおよび読み出しを行うよう指図する。別の実施形態では、SSDコントローラは、マップを使用してホストプロトコルのLBAとNVM内の物理的記憶アドレスとを変換することができるようになっている。別の実施形態では、マップの少なくとも一部分が、入出力装置の専用記憶(コンピューティングホストからは見えない)に使用される。例えば、コンピューティングホストからアクセスできないLBAの部分が、入出力装置によって、ログ、統計、または他の専用データへのアクセスを管理するのに使用される。In some embodiments, an I/O device, such as an SSD, includes an SSD controller. The SSD controller acts as a bridge between the host interface and the SSD's NVM, and executes host protocol commands sent from the computing host through the SSD's host interface. At least some of the commands instruct the SSD to write and read the NVM for data sent from and to the computing host, respectively. In another embodiment, the SSD controller is capable of translating between host protocol LBAs and physical storage addresses in the NVM using a map. In another embodiment, at least a portion of the map is used for the I/O device's private storage (not visible to the computing host). For example, portions of the LBAs that are not accessible to the computing host are used by the I/O device to manage access to logs, statistics, or other private data.

様々な実施形態によれば、マップは、1レベルマップ、2レベルマップ、マルチレベルマップ、直接マップ、連想マップ、およびホストプロトコルのLBAをNVM内の物理的記憶アドレスと関連付ける他の手段のうち1若しくはそれ以上である。例えば、ある実施形態では、2レベルマップは、LBAの第1の関数を、複数の第2レベル・マップ・ページのうち1つのNVM内のそれぞれのアドレスと関連付ける第1レベルマップを有し、第2レベル・マップ・ページの各々は、LBAの第2の関数をLBAに対応するデータのNVM内のそれぞれのアドレスと関連付ける。別の実施形態では、LBAの第1の関数およびLBAの第2の関数の例は、第2レベル・マップ・ページの各々に含まれる固定数のエントリによって除算されるときに得られる商および余りである。複数の第2レベル・マップ・ページをまとめて第2レベルマップと呼ぶ。本明細書では、マップの1若しくはそれ以上のエントリという場合、それは、1レベルマップ、2レベルマップの第1レベル、2レベルマップの第2レベル、マルチレベルマップの任意のレベル、またはエントリを有する任意の他の種類のマップを含む、任意の種類のマップの1若しくはそれ以上のエントリをいう。According to various embodiments, the map is one or more of a one-level map, a two-level map, a multi-level map, a direct map, an associative map, and other means of associating LBAs of the host protocol with physical storage addresses in the NVM. For example, in one embodiment, the two-level map has a first level map that associates a first function of the LBA with a respective address in the NVM of one of a plurality of second level map pages, each of which associates a second function of the LBA with a respective address in the NVM of data corresponding to the LBA. In another embodiment, examples of the first function of the LBA and the second function of the LBA are the quotient and remainder obtained when divided by a fixed number of entries contained in each of the second level map pages. The plurality of second level map pages are collectively referred to as the second level map. As used herein, a reference to one or more entries of a map refers to one or more entries of any type of map, including a one-level map, a first level of a two-level map, a second level of a two-level map, any level of a multi-level map, or any other type of map having entries.

様々な実施形態によれば、第2レベルマップ(またはマルチレベルマップの低レベル)のマップページの各々は、マップページの他のものと同数のエントリを含む、マップページの少なくとも他のいくつかと異なる数のエントリを含む、マップページの他のものと同じ粒度のエントリを含む、マップページの他のものと異なる粒度のエントリを含む、すべて同じ粒度ものであるエントリを含む、複数の粒度のものであるエントリを含む、マップページの内容の書式および/またはレイアウトを指定するそれぞれのヘッダを含む、ならびにマップページのエントリを表す任意の他の書式、レイアウト、または編成を有する、のうち1若しくはそれ以上である。例えば、第1の第2レベル・マップ・ページは、1エントリ当たり4KBの粒度の仕様を有し、第2の第2レベル・マップ・ページは、1エントリ当たり8KBの粒度、および第1の第2レベル・マップ・ページの半数だけのエントリの仕様を有する。According to various embodiments, each of the map pages of the second level map (or a lower level of a multi-level map) includes one or more of: the same number of entries as the others of the map page; a different number of entries than at least some of the others of the map page; entries of the same granularity as the others of the map page; entries of a different granularity than the others of the map page; entries that are all of the same granularity; entries that are of multiple granularities; includes a respective header that specifies the format and/or layout of the contents of the map page; and has any other format, layout, or organization that represents the entries of the map page. For example, a first second level map page has a specification of 4KB granularity per entry, and a second second level map page has a specification of 8KB granularity per entry and half as many entries as the first second level map page.

別の実施形態では、高レベルマップのエントリは、対応する低レベル・マップページの書式および/またはレイアウト情報を含む。例えば、第1レベルマップ内のエントリの各々は、関連付けられた第2レベル・マップ・ページ内のエントリについての粒度仕様を含む。In another embodiment, the entries of the higher level map include format and/or layout information for the corresponding lower level map page. For example, each entry in the first level map includes granularity specifications for entries in the associated second level map page.

ある実施形態では、マップは複数のエントリを有し、エントリの各々は、1若しくはそれ以上のLBAを、LBAのデータが記憶されているNVM内のそれぞれの位置を選択的に含む情報と関連付ける。例えば、LBAは512Bのセクタを指定し、マップ内の各エントリは、LBAの並んだ8セクタ(4KB)領域と関連付けられている。In one embodiment, the map has multiple entries, each of which associates one or more LBAs with information that optionally includes a respective location within the NVM where the data at the LBA is stored. For example, an LBA may specify a 512B sector, and each entry in the map may be associated with an aligned 8-sector (4KB) region of the LBA.

様々な実施形態によれば、マップのエントリの情報は、NVM内の位置、NVM内の読み出し単位のアドレス、NVMに記憶された関連付けられたLBAのデータを取得するために読み出すべき読み出し単位の数、NVMに記憶された関連付けられたLBAのデータのサイズであって、任意選択で、および/または選択的に1バイトより大きい粒度を有するサイズ、関連付けられたLBAのデータが切り捨てられているといった理由で、関連付けられたLBAのデータがNVMに存在しないという表示、関連付けられたLBAのデータに適用された任意の非標準修飾子を含む、関連付けられたLBAのデータの属性、および関連付けられたLBAのデータの任意の他のメタデータ、属性、または性質のうち1若しくはそれ以上を含む。According to various embodiments, the information in the map entry includes one or more of a location in the NVM, an address of the read unit in the NVM, a number of read units to read to obtain the associated LBA's data stored in the NVM, a size of the associated LBA's data stored in the NVM, optionally and/or selectively having a granularity greater than one byte, an indication that the associated LBA's data is not present in the NVM, such as because the associated LBA's data has been truncated, attributes of the associated LBA's data, including any non-standard modifiers applied to the associated LBA's data, and any other metadata, attributes, or properties of the associated LBA's data.

ある実施形態では、NVM内のアドレスは、アドレスのうち1つを表すのに必要とされるビット数を低減させるために領域へグループ化される。例えば、入出力装置のLBAが64領域に分割され、NVMが、LBA領域の各々に1つずつ、64領域に分割される場合には、特定のLBAと関連付けられたマップエントリは、必要とするアドレスビット数が6少なくて済む。というのは、NVM内の領域のうち1つが特定のLBAの領域によって決定されうるからである。様々な実施形態によれば、LBAの領域とNVMの領域との間の関連付けは、同等性、1対1数値関数といった直接的関連付け、表ルックアップ、動的マッピング、および2セットの数を関連付ける任意の他の方法のうち1若しくはそれ以上によるものである。In some embodiments, addresses in the NVM are grouped into regions to reduce the number of bits required to represent one of the addresses. For example, if the LBAs of an I/O device are divided into 64 regions and the NVM is divided into 64 regions, one for each of the LBA regions, then a map entry associated with a particular LBA will require 6 fewer address bits because one of the regions in the NVM can be determined by the region of a particular LBA. According to various embodiments, the association between the region of the LBA and the region of the NVM is by one or more of the following: equality, a direct association such as a one-to-one numeric function, a table lookup, dynamic mapping, and any other method of associating two sets of numbers.

様々な実施形態では、NVM内の位置は、複数の読み出し単位のうち1つのアドレス、ならびに読み出し単位での長さおよび/または範囲を含む。長さは、NVMに記憶された複数のデータ項目のうち特定の1つのサイズであり、マップのエントリと関連付けられた特定のデータ項目は長さを含む。様々な実施形態によれば、長さは、1バイト、1より大きいバイト、1読み出し単位、読み出し単位の指定された小部分、データ項目のうち1つの最大許容圧縮率に従った粒度、および記憶使用量を追跡するのに使用される任意の他の粒度のうち1若しくはそれ以上の粒度を有する。範囲は、特定のデータ項目のそれぞれの部分を記憶する、整数の読み出し単位といった読み出し単位の数である。別の実施形態および/または使用シナリオでは、読み出し単位の範囲内の最初の読み出し単位および/または読み出し単位の範囲内の最後の読み出し単位は、任意選択で、および/または選択的に、データ項目のうち複数のデータ項目の一部または全部を記憶する。ある実施形態および/または使用シナリオでは、長さおよび/または範囲は、例えば、長さ(長さおよび/または範囲が符号化されるコンテキストではサイズともいう)を範囲からのオフセットとして記憶することによって、符号化されて記憶される。ある実施形態および/または使用シナリオでは、長さおよび/または範囲の未使用の符号化が、非標準修飾子の指示や、関連付けられたデータ項目がNVMに存在するかどうかについての指示といった追加情報を符号化する。In various embodiments, the location in the NVM includes an address of one of the read units, and a length and/or range in read units. The length is the size of a particular one of the data items stored in the NVM, and the particular data item associated with the entry of the map includes the length. According to various embodiments, the length has one or more of the following granularities: one byte, more than one byte, one read unit, a specified fraction of a read unit, a granularity according to the maximum allowable compression ratio of one of the data items, and any other granularity used to track storage usage. The range is the number of read units, such as an integer number of read units, that store respective portions of the particular data item. In another embodiment and/or usage scenario, the first read unit in the range of read units and/or the last read unit in the range of read units optionally and/or selectively store some or all of the data items of the data items. In some embodiments and/or usage scenarios, the length and/or range are stored encoded, for example, by storing the length (also called size in contexts where the length and/or range are encoded) as an offset from the range. In some embodiments and/or usage scenarios, unused encodings of the length and/or range encode additional information, such as an indication of non-standard modifiers or an indication of whether the associated data item is present in NVM.

NVM内の位置をアドレスおよび長さとして符号化することにより、NVMに記憶されたデータをサイズ変更することが可能になる。例えば、第1の4KB領域は400Bのサイズに圧縮され、全体が単一の読み出し単位に記憶され、1読み出し単位の長さを有し、他方第2の4KB領域は圧縮不能であり、1より大の読み出し単位にまたがり、1より大の読み出し単位の長さを有する。別の実施形態では、LBAの領域と関連付けられた記憶の読み出し単位での長さおよび/または範囲を有することにより、NVMの必要な部分だけを読み出すことでLBAの領域のデータを検索することを可能にする。By encoding locations in the NVM as addresses and lengths, it is possible to resize the data stored in the NVM. For example, a first 4KB region may be compressed to a size of 400B and stored entirely in a single read unit and have a length of 1 read unit, while a second 4KB region is not compressible, spans more than 1 read unit, and has a length of more than 1 read unit. In another embodiment, having a length and/or range in read units of storage associated with an LBA region allows data in an LBA region to be retrieved by reading only the required portion of the NVM.

ある実施形態では、マップのエントリの各々は、エントリと関連付けられたLBAの領域の属性を指定する、メタデータともいう情報を含む。別の実施形態では、メタデータの少なくとも一部は、例えば、領域の複数のLBAの各々について別々のメタデータ仕様を有することによって、領域の粒度より細かい粒度ものである。様々な実施形態によれば、メタデータは、領域と関連付けられたNVM内のデータに適用可能な、および/または領域と関連付けられたNVM内のデータの書き込み、データへのアクセス、データの読み出し、および/若しくはデータの再利用を変更し、および/または制御するのに使用されるべき1若しくはそれ以上の非標準修飾子を含む。In one embodiment, each of the map's entries includes information, also referred to as metadata, that specifies attributes of the region of the LBA associated with the entry. In another embodiment, at least a portion of the metadata is at a finer granularity than the granularity of the region, for example, by having separate metadata specifications for each of the region's multiple LBAs. According to various embodiments, the metadata includes one or more non-standard qualifiers that are applicable to data in the NVM associated with the region and/or that are to be used to modify and/or control writing, accessing, reading, and/or reusing data in the NVM associated with the region.

コマンドの非標準修飾子に応答してメタデータをマップのエントリに記憶することの一例として、拡張書き込みコマンドは、LBA、および書き込みコマンドのデータが一時的であることを指定する非標準修飾子を含む。書き込みコマンドのデータがNVMに記憶され、LBAと関連付けられたマップの特定のエントリが、書き込みコマンドのデータのNVM内の位置、およびLBAと関連付けられたデータの一時指定の指示を含むように更新される。マップのその特定のエントリにアクセスする、後続のコマンドや、再利用などの内部動作といった後続の動作は、LBAと関連付けられたデータの一時指定の指示を決定し、LBAと関連付けられたデータの一時指定の指示が存在する場合には異なるやり方で実行することができる。例えば、LBAと関連付けられたデータの一時指定の指示を有するLBAの再利用は、ある実施形態では、LBAと関連付けられたデータを再利用するのではなく、LBAと関連付けられたデータを削減することができるようになっている。As an example of storing metadata in an entry of a map in response to a non-standard modifier of a command, an extended write command includes an LBA and a non-standard modifier that specifies that the data of the write command is temporary. The data of the write command is stored in the NVM, and a particular entry of the map associated with the LBA is updated to include the location in the NVM of the data of the write command and an indication of the temporary designation of the data associated with the LBA. Subsequent operations, such as a subsequent command or internal operation such as reclamation, that access that particular entry of the map may determine the indication of the temporary designation of the data associated with the LBA and may be performed differently if an indication of the temporary designation of the data associated with the LBA is present. For example, reclaiming an LBA with an indication of the temporary designation of the data associated with the LBA may, in one embodiment, reduce the data associated with the LBA rather than reclaiming the data associated with the LBA.

ある実施形態では、入出力デバイスは、DRAMといった外部メモリを含み、外部メモリは、例えばDDR2またはDDR3インターフェースを介して、入出力デバイスの要素に直接接続される。様々な実施形態によれば、外部メモリは、以下のうちの1若しくはそれ以上のために使用される:入出力デバイスのマップの一部または全部を記憶するため;入出力デバイスのマルチレベルマップのレベルのうちの1若しくはそれ以上を記憶するため;入出力デバイスに送られた書き込みデータをバッファするため;入出力デバイスの内部状態を記憶するため;および入出力デバイスの任意の他のメモリストレージ。例えば、外部メモリは、マップへのアクセスを提供するのに使用されるが、外部メモリが揮発性である場合には、更新がNVM内のマップに選択的に記憶される。様々な実施形態および/または使用シナリオにおいて、更新は、任意選択で、条件付きで、および/または選択的に、即時に記憶され、および/または遅延される。別の実施形態および/または使用シナリオでは、すべての更新が記憶される。別の実施形態および/または使用シナリオでは、更新のうちの一部が(例えば、より古い更新が、そのより古い更新を記憶する前により新しい更新に取って代わられているために、または更新のうちの1若しくはそれ以上の記憶を省略することを可能にする回復技術のために)記憶されない。様々な実施形態によれば、外部メモリは以下のうちの1若しくはそれ以上である:SRAMである;DRAMである;MRAMまたは他のNVMである;DDRインターフェースを有する;DDR2またはDDR3インターフェースを有する;任意の他のメモリインターフェースを有する;および任意の他の揮発性または不揮発性の外部メモリデバイスである。In some embodiments, the I/O device includes an external memory, such as a DRAM, that is directly connected to elements of the I/O device, for example, via a DDR2 or DDR3 interface. According to various embodiments, the external memory is used for one or more of the following: to store some or all of the map of the I/O device; to store one or more of the levels of the multi-level map of the I/O device; to buffer write data sent to the I/O device; to store the internal state of the I/O device; and any other memory storage of the I/O device. For example, the external memory is used to provide access to the map, but if the external memory is volatile, updates are selectively stored to the map in the NVM. In various embodiments and/or usage scenarios, updates are optionally, conditionally, and/or selectively stored immediately and/or delayed. In other embodiments and/or usage scenarios, all updates are stored. In other embodiments and/or usage scenarios, some of the updates are not stored (e.g., because an older update has been superseded by a newer update before the older update was stored, or because of a recovery technique that allows for the storage of one or more of the updates to be omitted). According to various embodiments, the external memory is one or more of the following: SRAM; DRAM; MRAM or other NVM; has a DDR interface; has a DDR2 or DDR3 interface; has any other memory interface; and is any other volatile or non-volatile external memory device.

マルチレベルマップを有するいくつかの実施形態といった別の実施形態では、マップの下位レベルが、入出力デバイスのLBAと関連付けられたデータといったコンピューティングホストからのデータと共に入出力デバイスのNVMに記憶され、入出力デバイスは、任意選択で、および/または選択的に、直接接続されたDRAMを利用しない。マップの下位レベルのエントリへのアクセスは、少なくともときどきは、NVMを使用して行われる。In other embodiments, such as some embodiments having a multi-level map, the lower levels of the map are stored in the I/O device's NVM along with data from the computing host, such as data associated with the I/O device's LBAs, and the I/O device optionally and/or selectively does not utilize directly attached DRAM. Access to the lower level entries of the map is, at least sometimes, performed using the NVM.

ある実施形態では、マップのシャドウコピーがコンピューティングホストのメモリに記憶される。様々な実施形態において、入出力デバイスは、マップのシャドウコピーや内部状態といった情報を、コンピューティングホストのメモリに記憶する。様々な実施形態によれば、コンピューティングホストのメモリは、以下のうちの1若しくはそれ以上である:プロセッサに接続されたDRAMメモリといったコンピューティングホストのメインメモリ;コンピューティングホストのシステムアクセス可能メモリ;コンピューティングホストの入出力空間メモリ;コンピューティングホストのPCIeアドレス指定可能メモリ;DRAMメモリやSRAMメモリといった揮発性メモリ;フラッシュメモリやMRAMメモリといったNVM;入出力デバイスからアクセス可能であり、入出力デバイスに直接接続されていない任意のメモリ;および入出力デバイスとコンピューティングホストの両方からアクセス可能な任意のメモリ。In one embodiment, a shadow copy of the map is stored in the memory of the computing host. In various embodiments, the I/O device stores information, such as a shadow copy of the map and internal state, in the memory of the computing host. According to various embodiments, the memory of the computing host is one or more of the following: the main memory of the computing host, such as DRAM memory connected to the processor; the system accessible memory of the computing host; the I/O space memory of the computing host; the PCIe addressable memory of the computing host; volatile memory, such as DRAM memory or SRAM memory; NVM, such as flash memory or MRAM memory; any memory accessible to the I/O device and not directly connected to the I/O device; and any memory accessible to both the I/O device and the computing host.

様々な実施形態によれば、マップのシャドウコピーは、以下のうちの1若しくはそれ以上を含む:マップのエントリのうちの少なくともいくつか;マップのすべてのエントリ;マップの対応するエントリのサブセットを含むエントリ;マップの対応するエントリに従った情報を含むエントリ;マップのエントリに存在しない有効な指示および/または他の情報を含むエントリ;2レベルマップの第2レベルのエントリに対応するエントリのみ;マルチレベルマップの最低レベルのエントリに対応するエントリのみ;2レベルマップの第2レベルのページに対応するページ構造といったマップのページ構造に対応するページ構造;ならびにマップと論理的に整合性を有する任意の構造。According to various embodiments, the shadow copy of the map includes one or more of the following: at least some of the entries of the map; all of the entries of the map; entries that include a subset of the corresponding entries of the map; entries that include information according to the corresponding entries of the map; entries that include valid instructions and/or other information not present in the entries of the map; only the entries that correspond to the second level entries of a two-level map; only the entries that correspond to the lowest level entries of a multi-level map; page structures that correspond to the page structures of the map, such as page structures that correspond to the second level pages of a two-level map; and any structures that are logically consistent with the map.

別の実施形態では、マップのシャドウコピーは、以下のうちの1若しくはそれ以上を有する:マップの対応するエントリと同じ書式を有するエントリ;マップの対応するエントリと類似した書式を有するエントリ;およびマップの対応するエントリと異なる書式を有するエントリ。第1の例では、2レベルマップの第2レベルのページがNVMに圧縮形式で記憶され、マップの第2レベルのシャドウコピーが非圧縮形式で記憶される。第2の例では、マップのシャドウコピーのエントリのうちの1若しくはそれ以上を含むマップのシャドウコピーの複数の部分の各々が、マップに存在しない有効な指示を有する。有効な指示は、それらの部分が独立に初期化され、および/または更新されることを可能にする。第3の例では、マップのシャドウコピーのエントリの各々が、エントリと関連付けられたLBAのデータが1若しくはそれ以上の記憶層のうちのどれに存在するか指示する、マップに存在しない情報を有する。第4の例では、マップのエントリの各々が、エントリと関連付けられたLBAのデータのアーカイブ状態を指示する、マップのシャドウコピーに存在しない情報を有する。第5の例では、マップのシャドウコピーおよび/またはマップは、各エントリと関連付けられたLBAのデータのストレージ層を指示することができるようになっている。第6の例では、マップのシャドウコピーおよび/またはマップは、ホストによって読み出し可能な、および/または書き込み可能な、1エントリ当たり1若しくはそれ以上のビットを含む。第7の例では、マップのエントリの各々が、それぞれの長さおよびそれぞれの範囲を含み、マップのシャドウコピーの対応するエントリの各々が、それぞれの範囲を含み、それぞれの長さを含まない。In another embodiment, the shadow copy of the map has one or more of the following: entries having the same format as the corresponding entries of the map; entries having a similar format as the corresponding entries of the map; and entries having a different format than the corresponding entries of the map. In a first example, the second level pages of the two-level map are stored in the NVM in a compressed format and the second level shadow copy of the map is stored in an uncompressed format. In a second example, each of a plurality of portions of the shadow copy of the map that includes one or more of the entries of the shadow copy of the map has a valid indication not present in the map. The valid indication allows the portions to be initialized and/or updated independently. In a third example, each of the entries of the shadow copy of the map has information not present in the map that indicates in which of one or more storage layers the data of the LBA associated with the entry resides. In a fourth example, each of the entries of the map has information not present in the shadow copy of the map that indicates the archive state of the data of the LBA associated with the entry. In a fifth example, the shadow copy of the map and/or the map can indicate the storage layer of the data of the LBA associated with each entry. In a sixth example, the shadow copy of the map and/or the map includes one or more bits per entry that are readable and/or writable by the host. In a seventh example, each of the entries of the map includes a respective length and a respective range, and each of the corresponding entries of the shadow copy of the map includes a respective range and does not include a respective length.

ある実施形態では、入出力デバイスの電源オンやリセットといったリセットイベント時に、マップの初期シャドウコピーがコンピューティングホストのメモリに記憶される。様々な実施形態によれば、マップの初期シャドウコピーは、以下のうちの1若しくはそれ以上である:すべて無効;マップのコピー;マルチレベルマップの1つ若しくは複数のレベルのコピー;最初に使用されるものとして識別された部分といった、マップの少なくとも一部分のコピー;およびマップと整合性を有する任意の状態。別の実施形態では、マップのシャドウコピーは、LBAが参照される際に動的に更新される。第1の例では、LBAに対応するマップのシャドウコピー内のエントリが、LBAが最初にアクセスされるときに、初期状態から更新される。第2の例では、LBAに対応するマップのシャドウコピーの一部分が、LBAが最初にアクセスされるときに、初期状態から更新される。引き続き第2の例では、この部分は、LBAと関連付けられたエントリを含む第2レベルのマップページに対応するエントリといった、マップのシャドウコピーの複数のエントリを含む。In some embodiments, upon a reset event, such as a power-on or reset of an I/O device, an initial shadow copy of the map is stored in the memory of the computing host. According to various embodiments, the initial shadow copy of the map is one or more of the following: a fully invalidated copy of the map; a copy of one or more levels of a multi-level map; a copy of at least a portion of the map, such as a portion identified as being used for the first time; and any state consistent with the map. In another embodiment, the shadow copy of the map is dynamically updated as an LBA is referenced. In a first example, an entry in the shadow copy of the map that corresponds to the LBA is updated from an initial state when the LBA is first accessed. In a second example, a portion of the shadow copy of the map that corresponds to the LBA is updated from an initial state when the LBA is first accessed. Continuing with the second example, this portion includes multiple entries of the shadow copy of the map, such as an entry corresponding to a second level map page that includes an entry associated with the LBA.

ある実施形態では、入出力デバイスによって受け取られる1若しくはそれ以上のコマンドの各々は、入出力デバイスがコマンドの実行の少なくとも一部分としてマップを更新することを可能にする。これら1若しくはそれ以上のコマンドを、本明細書では、マップ更新コマンドと呼ぶ。様々な実施形態によれば、マップ更新コマンドは、書き込みコマンド、切り捨てコマンド、マップの少なくとも一部分を無効にするコマンド、およびマップを変更することができるようにした任意の他のコマンド、のうちの1若しくはそれ以上を含む。In some embodiments, each of the one or more commands received by the I/O device enables the I/O device to update the map as at least a portion of the execution of the command. These one or more commands are referred to herein as map update commands. According to various embodiments, the map update commands include one or more of a write command, a truncate command, a command to invalidate at least a portion of the map, and any other command that allows the map to be modified.

ある実施形態では、書き込みコマンドといったマップ更新コマンドは、LBAを含み、LBAに対応するマップのシャドウコピー内のエントリを無効にする。様々な実施形態によれば、以下のうちの1若しくはそれ以上である:無効化はマップ更新コマンドを発行するときにコンピューティングホストによって行われる;無効化はマップ更新コマンドを受け取り、および/または実行するときに入出力デバイスによって行われる;無効化は、LBAに対応するマップのシャドウコピー内のエントリ内の有効な指示をオフにすることを含む;および無効化は、LBAに対応するエントリを含むマップのシャドウコピーの複数のエントリを含むマップのシャドウコピーの一部分内の有効な指示をオフにすることを含む。マップ更新コマンドに応答してマップ更新コマンドのLBAに対応するマップのシャドウコピー内のエントリを無効にすることは、マップのシャドウコピー内のエントリへのその後のアクセスが、マップのシャドウコピー内のエントリの情報が無効であると決定することを可能にする。In some embodiments, a map update command, such as a write command, includes an LBA and invalidates an entry in the shadow copy of the map that corresponds to the LBA. According to various embodiments, one or more of the following: the invalidation is performed by the computing host when issuing the map update command; the invalidation is performed by the I/O device when receiving and/or executing the map update command; the invalidation includes turning off a valid indication in an entry in the shadow copy of the map that corresponds to the LBA; and the invalidation includes turning off a valid indication in a portion of the shadow copy of the map that includes multiple entries of the shadow copy of the map that includes the entry that corresponds to the LBA. Invalidating the entry in the shadow copy of the map that corresponds to the LBA of the map update command in response to the map update command allows a subsequent access to the entry in the shadow copy of the map to determine that the information in the entry in the shadow copy of the map is invalid.

ある実施形態および/または使用シナリオでは、入出力デバイスによって受け取られる書き込みコマンドが、書き込みコマンドのデータが入出力デバイスのNVMに書き込まれることを可能にする。入出力デバイスは、書き込みコマンドのデータが書き込まれるNVM内の位置を決定し、書き込みコマンドのLBAと関連付けられたマップ内のエントリを、NVM内の位置を含むように更新する。別の実施形態では、コンピューティングホストのメモリ内のマップのシャドウコピーも、書き込みコマンドのLBAと関連付けられたマップのシャドウコピー内のエントリがNVM内の位置を含むように更新される。In one embodiment and/or usage scenario, a write command received by an I/O device causes data of the write command to be written to an NVM of the I/O device. The I/O device determines a location in the NVM to which the data of the write command will be written and updates an entry in a map associated with the LBA of the write command to include the location in the NVM. In another embodiment, a shadow copy of the map in the memory of the computing host is also updated such that an entry in the shadow copy of the map associated with the LBA of the write command includes the location in the NVM.

ある実施形態および/または使用シナリオでは、切り捨てコマンドを受け取ったことに応答して、入出力デバイスは、切り捨てコマンドのLBAと関連付けられたマップ内のエントリを、LBAと関連付けられたデータがNVMに存在しないという指示を含むように更新する。別の実施形態では、コンピューティングホストのメモリ内のマップのシャドウコピーも、切り捨てコマンドのLBAと関連付けられたマップのシャドウコピー内のエントリがLBAと関連付けられたデータがNVMに存在しないという指示を含むように更新される。In one embodiment and/or usage scenario, in response to receiving the truncate command, the I/O device updates an entry in the map associated with the LBA of the truncate command to include an indication that data associated with the LBA is not present in the NVM. In another embodiment, a shadow copy of the map in the computing host's memory is also updated such that an entry in the shadow copy of the map associated with the LBA of the truncate command includes an indication that data associated with the LBA is not present in the NVM.

様々な実施形態によれば、マップのシャドウコピーの更新は、以下のうちの1若しくはそれ以上によって行われる:マップ更新コマンドといった特定のタイプのコマンドを発行したことに応答したコンピューティングホスト;入出力デバイスから更新情報を受け取ったことに応答したコンピューティングホスト;最近の更新を求めて入出力デバイスをポーリングし、更新情報を有する応答を受け取ったことに応答したコンピューティングホスト;PCIeアドレス空間内のマップのシャドウコピーにアクセスすることによってなど、コンピューティングホストのメモリ内のマップのシャドウコピーにアクセスすることによる入出力デバイス;ならびにコンピューティングホストおよび入出力デバイスを含むシステムの別のエージェント。更新情報は、マップの1若しくはそれ以上のエントリの少なくともいくつかのコンテンツに従った情報、および/または1若しくはそれ以上のエントリと関連付けられたそれぞれのLBAといった1若しくはそれ以上のエントリの指示を含む。様々な実施形態において、更新情報は、任意の書式で、または1若しくはそれ以上の入出力デバイスと1若しくはそれ以上のコンピューティングホストとの間で情報を伝える任意の技術によって伝えられる。第1の例では、SATAホストプロトコルを使用して、更新情報は、コンピューティングホストが読み出し可能なログページで伝えられる。第2の例では、NVM ExpressといったPCIeベースのホストプロトコルを使用して、更新情報は、少なくとも部分的に入出力デバイスがコンピューティングホストのメモリ内の領域を書き込み、コンピューティングホストに割り込みで知らせることによって伝えられる。According to various embodiments, the update of the shadow copy of the map is performed by one or more of the following: the computing host in response to issuing a particular type of command, such as a map update command; the computing host in response to receiving update information from an I/O device; the computing host in response to polling the I/O device for recent updates and receiving a response with the update information; the I/O device by accessing a shadow copy of the map in the computing host's memory, such as by accessing a shadow copy of the map in a PCIe address space; and another agent of the system, including the computing host and the I/O device. The update information includes information according to the content of at least some of the one or more entries of the map, and/or an indication of the one or more entries, such as the respective LBAs associated with the one or more entries. In various embodiments, the update information is conveyed in any format or by any technique that conveys information between one or more I/O devices and one or more computing hosts. In a first example, using a SATA host protocol, the update information is conveyed in a log page that is readable by the computing host. In a second example, using a PCIe-based host protocol such as NVM Express, updates are communicated at least in part by the I/O device writing to a location in the computing host's memory and notifying the computing host via an interrupt.

ある実施形態では、マップ更新コマンドのLBAと関連付けられたマップ内のエントリは、LBAと関連付けられ、NVMに記憶されたデータの長さおよび/または範囲を指定する情報をさらに含む。というのは、LBAと関連付けられ、NVMに記憶されたデータの長さおよび/または範囲を指定する情報がデータの圧縮率に応じて変動するからである。別の実施形態では、マップ更新コマンドのLBAと関連付けられたマップのシャドウコピー内のエントリは、任意選択で、および/または選択的に、LBAと関連付けられ、NVMに記憶されたデータの長さおよび/または範囲をさらに含む。様々な実施形態によれば、LBAと関連付けられ、NVMに記憶されたデータの長さおよび/または範囲は、任意選択で、および/または選択的に、さらに、以下のうちの1若しくはそれ以上を符号化することができるようになっている:LBAと関連付けられたデータの一部および/または全部が切り捨てられるという指示;LBAと関連付けられたデータの一部および/または全部が訂正不能であるという指示;ならびに、LBAと関連付けられたデータの一部および/または全部の任意の他のプロパティ。In one embodiment, the entry in the map associated with the LBA of the map update command further includes information specifying the length and/or range of the data associated with the LBA and stored in the NVM, since the information specifying the length and/or range of the data associated with the LBA and stored in the NVM varies depending on the compressibility of the data. In another embodiment, the entry in the shadow copy of the map associated with the LBA of the map update command optionally and/or selectively further includes the length and/or range of the data associated with the LBA and stored in the NVM. According to various embodiments, the length and/or range of the data associated with the LBA and stored in the NVM may optionally and/or selectively further encode one or more of the following: an indication that some and/or all of the data associated with the LBA is truncated; an indication that some and/or all of the data associated with the LBA is uncorrectable; and any other properties of some and/or all of the data associated with the LBA.

ある実施形態および/または使用シナリオでは、LBAと関連付けられ、NVMに記憶されたデータの長さを、マップ更新コマンドのLBAと関連付けられたマップのシャドウコピー内のエントリに記憶することは、マップ更新コマンドのLBAのデータを上書きするときなどに、後続のマップ更新コマンドにおいてLBAと関連付けられ、NVMに記憶されたデータの長さを提供するためのマップのシャドウコピーの使用を可能にする。LBAと関連付けられ、NVMに記憶されたデータの長さは、後続のマップ更新コマンドによってマップ更新コマンドのLBAのデータを上書きするときに、マップ更新コマンドのLBAのデータを含むNVMの領域における使用空間統計を調整するのに使用される。例えば、マップ更新コマンドのLBAのデータを含むNVMの領域についての使用空間統計が、後続のマップ更新コマンドによってマップ更新コマンドのLBAのデータを上書きするときに、LBAと関連付けられ、NVMに記憶されたデータの長さの分だけ減分される。In certain embodiments and/or usage scenarios, storing the length of the data associated with the LBA and stored in the NVM in an entry in the shadow copy of the map associated with the LBA of the map update command enables use of the shadow copy of the map to provide the length of the data associated with the LBA and stored in the NVM in a subsequent map update command, such as when overwriting the data at the LBA of the map update command. The length of the data associated with the LBA and stored in the NVM is used to adjust the used space statistics for the region of the NVM that includes the data at the LBA of the map update command when the data at the LBA of the map update command is overwritten by a subsequent map update command. For example, the used space statistics for the region of the NVM that includes the data at the LBA of the map update command is decremented by the length of the data associated with the LBA and stored in the NVM when the data at the LBA of the map update command is overwritten by a subsequent map update command.

ある実施形態では、LBAのところのデータを要求する読み出しコマンドといったマップ読み出し要求が、LBAに対応するマップのシャドウコピー内のエントリにアクセスすることができるようになっている。様々な実施形態によれば、以下のうちの1若しくはそれ以上である:アクセスは読み出しコマンドを発行するときにコンピューティングホストによって行われる;アクセスは読み出しコマンドを受け取り、および/または実行するときに入出力デバイスによって行われる;およびアクセスはLBAに対応するマップのシャドウコピー内のエントリの少なくとも一部分を読み取ることを含む。読み出しコマンドのLBAに対応するマップのシャドウコピー内のエントリにアクセスすることにより、マップにアクセスしなくても、マップの対応するエントリに従った情報が提供される。マルチレベルマップの下位レベルといったマップが入出力デバイスのNVMに記憶されるある実施形態および/または使用シナリオでは、マップのシャドウコピーへのアクセスは、より待ち時間が短く、LBAのところのデータにアクセスする待ち時間を都合よく向上させる。In some embodiments, a map read request, such as a read command requesting data at an LBA, may access an entry in the shadow copy of the map that corresponds to the LBA. According to various embodiments, one or more of the following: the access is made by a computing host when issuing the read command; the access is made by an I/O device when receiving and/or executing the read command; and the access includes reading at least a portion of an entry in the shadow copy of the map that corresponds to the LBA. Accessing an entry in the shadow copy of the map that corresponds to the LBA of the read command provides information according to the corresponding entry of the map without accessing the map. In some embodiments and/or usage scenarios in which a map, such as a lower level of a multi-level map, is stored in the NVM of the I/O device, accessing the shadow copy of the map has lower latency and advantageously improves the latency of accessing data at the LBA.

ある実施形態では、入出力デバイスからの特定のLBAに対応するデータを読み取るよう求める読み出し要求に応答して、コンピューティングホストは、特定のLBAに対応するマップのシャドウコピーのエントリの少なくとも一部分を読み取る。コンピューティングホストは、入出力デバイスに予めマッピングされた読み出しコマンドを送り、予めマッピングされた読み出しコマンドは、入出力デバイスのNVM内の位置といったマップのシャドウコピーのエントリの情報を含む。様々な実施形態において、予めマッピングされた読み出しコマンドは特定のLBAを提供しない。別の実施形態および/または使用シナリオでは、NVM内の位置はNVM内のそれぞれの範囲を含む。In one embodiment, in response to a read request from an I/O device to read data corresponding to a particular LBA, the computing host reads at least a portion of an entry in the shadow copy of the map corresponding to the particular LBA. The computing host sends a pre-mapped read command to the I/O device, where the pre-mapped read command includes information of the entry in the shadow copy of the map, such as a location in the NVM of the I/O device. In various embodiments, the pre-mapped read command does not provide a particular LBA. In another embodiment and/or usage scenario, the location in the NVM includes a respective range in the NVM.

ある実施形態では、入出力デバイスからの特定のLBAに対応するデータを読み取るよう求める読み出し要求に応答して、コンピューティングホストは、特定のLBAに対応するマップのシャドウコピーのエントリの少なくとも一部分を読み取ることができるようになっている。マップのシャドウコピーのエントリが有効でないことが、例えば有効指示によって指示される場合、コンピューティングホストは入出力デバイスに、特定のLBAを含む読み出しコマンドを送る。マップのシャドウコピーのエントリが有効であることが、例えば有効指示によって指示される場合、コンピューティングホストは入出力デバイスに、入出力デバイスのNVM内の位置といった、マップのシャドウコピーのエントリの情報を含む予めマッピングされた読み出しコマンドを送る。様々な実施形態において、予めマッピングされた読み出しコマンドは特定のLBAを提供しない。別の実施形態および/または使用シナリオでは、NVM内の位置はNVM内のそれぞれの範囲を含む。In some embodiments, in response to a read request from an I/O device to read data corresponding to a particular LBA, the computing host is adapted to read at least a portion of the entry in the shadow copy of the map corresponding to the particular LBA. If the entry in the shadow copy of the map is not valid, e.g., the validity indication indicates, the computing host sends a read command to the I/O device that includes the particular LBA. If the entry in the shadow copy of the map is valid, e.g., the validity indication indicates, the computing host sends a pre-mapped read command to the I/O device that includes information about the entry in the shadow copy of the map, such as a location in the NVM of the I/O device. In various embodiments, the pre-mapped read command does not provide a particular LBA. In other embodiments and/or usage scenarios, the location in the NVM includes a respective range in the NVM.

ある実施形態では、入出力デバイスが入出力デバイスのNVM内の位置を含む予めマッピングされた読み出しコマンドを受け取ったことに応答して、入出力デバイスは、その位置のところのNVMにアクセスして読み出しデータを取得することができるようになっている。入出力デバイスは、予めマッピングされた読み出しコマンドを受け取ったことに応答してマップにアクセスすることを省略する。予めマッピングされた読み出しコマンドに応答して、読み出しデータおよび/またはその処理済みバージョンが返される。In one embodiment, in response to an I/O device receiving a pre-mapped read command that includes a location in the I/O device's NVM, the I/O device can access the NVM at the location to obtain the read data. The I/O device omits accessing the map in response to receiving the pre-mapped read command. In response to the pre-mapped read command, the read data and/or a processed version thereof is returned.

ある実施形態では、入出力デバイスが特定のLBAに対応する入出力デバイスからのデータを読み取るよう求める読み出しコマンドを受け取ったことに応答して、入出力デバイスは、特定のLBAに対応するマップのシャドウコピーのエントリの少なくとも一部分を読み取ることができるようになっている。入出力デバイスは、マップにアクセスせずに、マップのシャドウコピーのエントリから特定のLBAのデータに対応するNVM内の位置を取得する。入出力デバイスは、NVM内のその位置のところのNVMにアクセスして読み出しデータを取得する。読み出しコマンドに応答して、読み出しデータおよび/またはその処理済みバージョンが返される。In one embodiment, in response to an I/O device receiving a read command requesting that the I/O device read data from the I/O device that corresponds to a particular LBA, the I/O device is adapted to read at least a portion of an entry in the shadow copy of the map that corresponds to the particular LBA. The I/O device obtains a location in the NVM that corresponds to the data at the particular LBA from the entry in the shadow copy of the map without accessing the map. The I/O device accesses the NVM at the location in the NVM to obtain the read data. In response to the read command, the read data and/or a processed version thereof is returned.

ある実施形態では、特定のLBAに対応する入出力デバイスからのデータを読み取るよう求める読み出しコマンドの受け取りに応答して、入出力デバイスは、特定のLBAに対応するマップのシャドウコピーのエントリの少なくとも一部分を読み取ることができるようになっている。マップのシャドウコピーのエントリが有効でないことが、例えば有効指示によって指示される場合、入出力デバイスはマップにアクセスして、特定のLBAのデータに対応するNVM内の位置を決定する。マップのシャドウコピーのエントリが有効であることが、例えば有効指示によって指示される場合、入出力デバイスは、マップにアクセスせずに、マップのシャドウコピーのエントリから特定のLBAのデータに対応するNVM内の位置を取得する。入出力デバイスは、NVM内の位置のところのNVMにアクセスして読み出しデータを取得する。読み出しコマンドに応答して、読み出しデータおよび/または処理済みバージョンが返される。In one embodiment, in response to receiving a read command to read data from the I/O device corresponding to a particular LBA, the I/O device is adapted to read at least a portion of an entry in the shadow copy of the map corresponding to the particular LBA. If the entry in the shadow copy of the map is not valid, e.g., indicated by a valid indication, the I/O device accesses the map to determine a location in the NVM corresponding to the data at the particular LBA. If the entry in the shadow copy of the map is valid, e.g., indicated by a valid indication, the I/O device obtains the location in the NVM corresponding to the data at the particular LBA from the entry in the shadow copy of the map without accessing the map. The I/O device accesses the NVM at the location in the NVM to obtain the read data. In response to the read command, the read data and/or a processed version are returned.