JP2014241424A - Semiconductor device - Google Patents

Semiconductor deviceDownload PDFInfo

- Publication number

- JP2014241424A JP2014241424AJP2014150498AJP2014150498AJP2014241424AJP 2014241424 AJP2014241424 AJP 2014241424AJP 2014150498 AJP2014150498 AJP 2014150498AJP 2014150498 AJP2014150498 AJP 2014150498AJP 2014241424 AJP2014241424 AJP 2014241424A

- Authority

- JP

- Japan

- Prior art keywords

- layer

- thin film

- wiring

- film transistor

- oxide semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Landscapes

- Thin Film Transistor (AREA)

- Liquid Crystal (AREA)

- Electroluminescent Light Sources (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Electrochromic Elements, Electrophoresis, Or Variable Reflection Or Absorption Elements (AREA)

- Shift Register Type Memory (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Abstract

Description

Translated fromJapanese本発明は、酸化物半導体を用いる表示装置及びその製造方法に関する。The present invention relates to a display device using an oxide semiconductor and a manufacturing method thereof.

液晶表示装置に代表されるように、ガラス基板等の平板に形成される薄膜トランジスタは

、アモルファスシリコン、多結晶シリコンによって作製されている。アモルファスシリコ

ンを用いた薄膜トランジスタは、電界効果移動度が低いもののガラス基板の大面積化に対

応することができ、一方、結晶シリコンを用いた薄膜トランジスタは電界効果移動度が高

いものの、レーザアニール等の結晶化工程が必要であり、ガラス基板の大面積化には必ず

しも適応しないといった特性を有している。As represented by a liquid crystal display device, a thin film transistor formed on a flat plate such as a glass substrate is made of amorphous silicon or polycrystalline silicon. A thin film transistor using amorphous silicon can cope with an increase in the area of a glass substrate although the field effect mobility is low. On the other hand, a thin film transistor using crystalline silicon has a high field effect mobility, but crystal such as laser annealing. Therefore, it has a characteristic that it is not necessarily adapted to increase the area of the glass substrate.

これに対し、酸化物半導体を用いて薄膜トランジスタを作製し、電子デバイスや光デバイ

スに応用する技術が注目されている。例えば、酸化物半導体層として酸化亜鉛、In−G

a−Zn−O系酸化物半導体を用いて薄膜トランジスタを作製し、表示装置のスイッチン

グ素子などに用いる技術が特許文献1、特許文献2、及び非特許文献1で開示されている

。In contrast, a technique in which a thin film transistor is manufactured using an oxide semiconductor and applied to an electronic device or an optical device has attracted attention. For example, zinc oxide, In-G as the oxide semiconductor layer

しかしながら、酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層のパ

ッシベーション層として、シラン、二酸化窒素、アンモニア、窒素等のいずれかを原料ガ

スとしたプラズマCVD法を用いて形成した窒化珪素層、または酸化珪素層を用いると、

薄膜トランジスタの電気特性の信頼性が低減するという問題がある。However, in a thin film transistor using an oxide semiconductor layer, as a passivation layer of the oxide semiconductor layer, a silicon nitride layer formed using a plasma CVD method using any one of silane, nitrogen dioxide, ammonia, nitrogen, or the like as a source gas, Or when using a silicon oxide layer,

There is a problem that reliability of electric characteristics of the thin film transistor is reduced.

そこで、薄膜トランジスタの電気特性の信頼性を高めることが可能な薄膜トランジスタ及

びその作製方法を提供することを課題の一つとする。また、画質を向上させることが可能

な表示装置及びその作製方法を提供することを課題の一つとする。Thus, it is an object to provide a thin film transistor that can improve the reliability of electric characteristics of the thin film transistor and a manufacturing method thereof. Another object is to provide a display device capable of improving image quality and a manufacturing method thereof.

ゲート電極と、ゲート電極に重畳する酸化物半導体層と、酸化物半導体層に接する有機樹

脂層と、酸化物半導体層及び有機樹脂層の間に設けられる配線とを有する薄膜トランジス

タである。The thin film transistor includes a gate electrode, an oxide semiconductor layer overlapping with the gate electrode, an organic resin layer in contact with the oxide semiconductor layer, and a wiring provided between the oxide semiconductor layer and the organic resin layer.

また、ゲート電極と、ゲート電極上に形成されるゲート絶縁層と、ゲート電極に重畳し、

且つゲート絶縁層上に形成される酸化物半導体層と、ゲート絶縁層及び酸化物半導体層上

に形成される配線と、酸化物半導体層及び配線に接する有機樹脂層とを有する薄膜トラン

ジスタである。A gate electrode, a gate insulating layer formed on the gate electrode, and the gate electrode,

In addition, the thin film transistor includes an oxide semiconductor layer formed over the gate insulating layer, a wiring formed over the gate insulating layer and the oxide semiconductor layer, and an organic resin layer in contact with the oxide semiconductor layer and the wiring.

また、上記薄膜トランジスタを駆動回路及び画素部に有する表示装置である。In addition, the display device includes the thin film transistor in a driver circuit and a pixel portion.

なお、酸化物半導体層は、InMO3(ZnO)m(m>0)で表記される薄膜であり、

Mは、ガリウム(Ga)、鉄(Fe)、ニッケル(Ni)、マンガン(Mn)及びコバル

ト(Co)から選ばれた一の金属元素または複数の金属元素を示す。例えばMとして、G

aの場合があることの他、GaとNiまたはGaとFeなど、Ga以外の上記金属元素が

含まれる場合がある。また、上記酸化物半導体層において、Mとして含まれる金属元素の

他に、不純物元素としてFe、Niその他の遷移金属元素、または該遷移金属の酸化物が

含まれているものがある。ここでは、当該薄膜のうちM=ガリウム(Ga)のものをIn

−Ga−Zn−O系非単結晶層とも呼ぶ。Note that the oxide semiconductor layer is a thin film represented by InMO3 (ZnO)m (m> 0),

M represents one metal element or a plurality of metal elements selected from gallium (Ga), iron (Fe), nickel (Ni), manganese (Mn), and cobalt (Co). For example, as M, G

In addition to the case of “a”, the metal element other than Ga, such as Ga and Ni or Ga and Fe, may be contained. In addition to the metal element included as M, the oxide semiconductor layer may include Fe, Ni, other transition metal elements, or an oxide of the transition metal as an impurity element. Here, M = gallium (Ga) of the thin film is In.

Also referred to as a —Ga—Zn—O-based non-single-crystal layer.

In−Ga−Zn−O系非単結晶層の結晶構造は、スパッタリング法で形成した後、20

0℃〜500℃、代表的には300〜400℃で10分〜100分の加熱を行っても、ア

モルファス構造がXRD(X線回析)測定で観察される。また、In−Ga−Zn−O系

非単結晶層用いることで、ゲート電圧±20Vにおいて、オン・オフ比が109以上、移

動度が10cm2/Vs以上の電気特性を有する薄膜トランジスタを作製することができ

る。The crystal structure of the In—Ga—Zn—O-based non-single-crystal layer is 20

Even if heating is performed at 0 to 500 ° C., typically 300 to 400 ° C. for 10 to 100 minutes, an amorphous structure is observed by XRD (X-ray diffraction) measurement. Further, by using an In—Ga—Zn—O-based non-single-crystal layer, a thin film transistor having an electrical property with an on / off ratio of 109 or more and a mobility of 10 cm2 / Vs or more at a gate voltage of ± 20 V is manufactured. be able to.

このような電気特性を有する薄膜トランジスタを駆動回路に用いることは有用である。例

えば、ゲート線駆動回路は、ゲート信号を順次転送するシフトレジスタ回路と、バッファ

回路などで構成され、ソース線駆動回路は、ゲート信号を順次転送するシフトレジスタと

、バッファ回路と、画素への映像信号の転送のオン・オフを切り替えるアナログスイッチ

などにより構成される。アモルファスシリコンを用いた薄膜トランジスタに比べ高い移動

度を有する酸化物半導体層を用いた薄膜トランジスタは、シフトレジスタ回路を高速駆動

させることができる。It is useful to use a thin film transistor having such electrical characteristics for a driver circuit. For example, the gate line driver circuit includes a shift register circuit that sequentially transfers gate signals and a buffer circuit, and the source line driver circuit includes a shift register that sequentially transfers gate signals, a buffer circuit, and an image to a pixel. It consists of an analog switch that switches on / off of signal transfer. A thin film transistor using an oxide semiconductor layer having higher mobility than a thin film transistor using amorphous silicon can drive a shift register circuit at high speed.

また、画素部を駆動する駆動回路の少なくとも一部の回路を酸化物半導体を用いた薄膜ト

ランジスタで構成する場合、全てnチャネル型TFTで形成され、図1(B)に示した回

路を基本単位として形成する。また、駆動回路において、ゲート電極とソース配線、或い

はドレイン配線を直接接続させることにより、良好なコンタクトを得ることができ、接触

抵抗を低減することができる。駆動回路において、ゲート電極とソース配線、或いはドレ

イン配線を他の導電層、例えば透明導電層を介して接続する場合、コンタクトホールの数

の増加、コンタクトホールの数の増加による占有面積の増大、または接触抵抗及び配線抵

抗の増大、さらには工程の複雑化を招く恐れがある。In the case where at least part of a driver circuit for driving the pixel portion is formed using a thin film transistor including an oxide semiconductor, the driver circuit is formed using n-channel TFTs, and the circuit illustrated in FIG. 1B is used as a basic unit. Form. In the driver circuit, a good contact can be obtained and contact resistance can be reduced by directly connecting the gate electrode and the source wiring or the drain wiring. In the driving circuit, when the gate electrode and the source wiring or the drain wiring are connected through another conductive layer, for example, a transparent conductive layer, the number of contact holes increases, the occupied area increases due to the increase in the number of contact holes, or There is a possibility that the contact resistance and the wiring resistance increase, and further the process becomes complicated.

また、薄膜トランジスタは静電気などにより破壊されやすいため、ゲート線またはソース

線に対して、駆動回路保護用の保護回路を同一基板上に設けることが好ましい。保護回路

は、酸化物半導体を用いた非線形素子を用いて構成することが好ましい。In addition, since the thin film transistor is easily broken by static electricity or the like, it is preferable to provide a protective circuit for protecting the driver circuit over the same substrate for the gate line or the source line. The protection circuit is preferably formed using a non-linear element using an oxide semiconductor.

なお、第1、第2として付される序数詞は便宜上用いるものであり、工程順または積層順

を示すものではない。また、本明細書において発明を特定するための事項として固有の名

称を示すものではない。The ordinal numbers attached as the first and second are used for convenience and do not indicate the order of steps or the order of lamination. In addition, a specific name is not shown as a matter for specifying the invention in this specification.

また、駆動回路を有する表示装置としては、液晶表示装置の他に、発光素子を用いた発光

表示装置や、電気泳動表示素子を用いた電子ペーパーとも称される表示装置がある。In addition to a liquid crystal display device, a display device including a driver circuit includes a light-emitting display device using a light-emitting element and a display device also called electronic paper using an electrophoretic display element.

発光素子を用いた発光表示装置においては、画素部に複数の薄膜トランジスタを有し、画

素部においてもある薄膜トランジスタのゲート電極と他の薄膜トランジスタのソース配線

、或いはドレイン配線を直接接続させる箇所を有している。また、発光素子を用いた発光

表示装置の駆動回路においては、薄膜トランジスタのゲート電極とその薄膜トランジスタ

のソース配線、或いはドレイン配線を直接接続させる箇所を有している。A light-emitting display device using a light-emitting element includes a plurality of thin film transistors in a pixel portion, and a portion in which a gate electrode of a thin film transistor in the pixel portion is directly connected to a source wiring or a drain wiring of another thin film transistor. Yes. In addition, a driver circuit of a light-emitting display device using a light-emitting element has a portion where a gate electrode of a thin film transistor and a source wiring or a drain wiring of the thin film transistor are directly connected.

酸化物半導体を用いた薄膜トランジスタにおいて、酸化物半導体に接する有機絶縁層を形

成することにより、電気特性の信頼性の高い薄膜トランジスタを作製することができる。

また、画質が向上した表示装置を作製することができる。In a thin film transistor using an oxide semiconductor, a thin film transistor with high electrical characteristics can be manufactured by forming an organic insulating layer in contact with the oxide semiconductor.

In addition, a display device with improved image quality can be manufactured.

以下、実施の形態について、図面を用いて詳細に説明する。但し、開示される発明は以下

の説明に限定されず、開示される発明の趣旨及びその範囲から逸脱することなくその形態

及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、開示され

る発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以

下に説明する発明の構成において、同一部分または同様な機能を有する部分には同一の符

号を異なる図面間で共通して用い、その繰り返しの説明は省略する。Hereinafter, embodiments will be described in detail with reference to the drawings. However, the disclosed invention is not limited to the following description, and it is easily understood by those skilled in the art that modes and details can be variously changed without departing from the spirit and scope of the disclosed invention. The Therefore, the disclosed invention is not construed as being limited to the description of the embodiments below. Note that in structures of the invention described below, the same portions or portions having similar functions are denoted by the same reference numerals in different drawings, and description thereof is not repeated.

(実施の形態1)

ここでは、2つのnチャネル型の薄膜トランジスタを用いてインバータ回路を構成する例

を基に、以下に説明する。(Embodiment 1)

Here, a description will be given below based on an example in which an inverter circuit is configured using two n-channel thin film transistors.

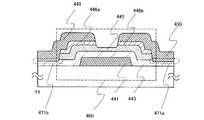

駆動回路のインバータ回路の断面構造を図1(A)に示す。なお、図1に示す第1薄膜ト

ランジスタ430、第2薄膜トランジスタ431は、逆スタガ型薄膜トランジスタであり

、酸化物半導体層上にソース領域またはドレイン領域を介して配線が設けられている薄膜

トランジスタの例である。A cross-sectional structure of the inverter circuit of the driver circuit is illustrated in FIG. Note that each of the first

図1(A)において、基板400上に第1ゲート電極401及び第2ゲート電極402が

形成される。第1ゲート電極401及び第2ゲート電極402上には、ゲート絶縁層40

3が形成される。また、第1ゲート電極401と重なる位置に、ゲート絶縁層403に接

する第1酸化物半導体層405が形成され、第2ゲート電極402と重なる位置に、ゲー

ト絶縁層403に接する第2酸化物半導体層407とが形成される。第1酸化物半導体層

405上には第1配線409、及び第2配線410が形成される。また、第1酸化物半導

体層405と、第1配線409、第2配線410の間に、ソース領域またはドレイン領域

として機能するn+層406a、406bが形成される。また、第2酸化物半導体層40

7と、第2配線410、第3配線411の間に、ソース領域またはドレイン領域として機

能するn+層408a、408bが形成される。また、第2配線410は、ゲート絶縁層

403に形成されたコンタクトホール404を介して、第2ゲート電極402と直接接続

する。また、第2酸化物半導体層407上には、第2配線410及び第3配線411が形

成される。また、第1酸化物半導体層405及び第2酸化物半導体層407に接する有機

絶縁層452が形成される。第1酸化物半導体層405及び第2酸化物半導体層407、

第1配線409〜第3配線411、及びゲート絶縁層403上に、組成物を塗布し、焼成

することで、第1酸化物半導体層405及び第2酸化物半導体層407に接する有機絶縁

層452を形成することができるため、電気特性の信頼性の高い薄膜トランジスタを作製

することができる。In FIG. 1A, a

3 is formed. In addition, a first

7, n+ layers 408 a and 408 b functioning as a source region or a drain region are formed between the

An organic insulating

基板400としては、透光性を有する基板を用いることが好ましく、透光性を有する基板

としては、コーニング社の7059ガラスや1737ガラスなどに代表されるバリウムホ

ウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板を用いることができる。As the

第1ゲート電極401及び第2ゲート電極402の材料は、アルミニウム、銅、モリブデ

ン、タングステンから選ばれた元素、またはから選ばれた元素、または上述した元素と、

チタン、タンタル、タングステン、モリブデン、クロム、ネオジム、スカンジウム等とを

有する合金、または上述した元素の窒化物を用いた単層または積層構造で形成する。The material of the

It is formed with a single layer or a stacked structure using an alloy containing titanium, tantalum, tungsten, molybdenum, chromium, neodymium, scandium, or the like, or a nitride of the above element.

例えば、第1ゲート電極401及び第2ゲート電極402の2層の積層構造としては、ア

ルミニウム層上にモリブデン層が積層された構造、または銅層上にモリブデン層を積層し

た構造、または銅層上に窒化チタン層若しくは窒化タンタル層を積層した積層構造、窒化

チタン層とモリブデン層とを積層した構造とすることが好ましい。3層の積層構造として

は、タングステン層または窒化タングステン層と、アルミニウムとシリコンの合金または

アルミニウムとチタンの合金と、窒化チタン層またはチタン層とを積層した構造とするこ

とが好ましい。For example, the two-layer structure of the

ゲート絶縁層403としては、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層ま

たは窒化酸化シリコン層を単層で、または積層して形成することができる。ゲート絶縁層

403を積層構造とする場合は、基板400上に窒化シリコン層または窒化酸化シリコン

層を形成し、その上に酸化シリコン層または酸化窒化シリコン層を形成する構造とするこ

とができる。The

また、第1ゲート電極401及び第2ゲート電極402を覆うゲート絶縁層403上には

、第1酸化物半導体層405と、第2酸化物半導体層407とを設ける。A first

第1酸化物半導体層405、第2酸化物半導体層407は、InMO3(ZnO)m(m

>0)で表記される層を形成する。なお、Mは、Ga、Fe、Ni、Mn及びCoから選

ばれた一の金属元素又は複数の金属元素を示す。例えばMとして、Gaの場合があること

の他、GaとNi又はGaとFeなど、Ga以外の上記金属元素が含まれる場合がある。

また、上記酸化物半導体において、Mとして含まれる金属元素の他に、不純物元素として

Fe、Niその他の遷移金属元素、又は該遷移金属の酸化物が含まれているものがある。

本明細書においてはこの薄膜をIn−Ga−Zn−O系非単結晶膜とも呼ぶ。また、第1

酸化物半導体層405、第2酸化物半導体層407の可動イオン、代表的にはナトリウム

の濃度は、5×1018/cm3以下、更には1×1018/cm3以下であると、薄膜

トランジスタの電気特性が変化することを抑制することができるため好ましい。The first

> 0) is formed. Note that M represents one metal element or a plurality of metal elements selected from Ga, Fe, Ni, Mn, and Co. For example, M may be Ga, and may contain the above metal elements other than Ga, such as Ga and Ni or Ga and Fe.

In addition to the metal element contained as M, some of the above oxide semiconductors contain Fe, Ni, other transition metal elements, or oxides of the transition metal as impurity elements.

In this specification, this thin film is also referred to as an In—Ga—Zn—O-based non-single-crystal film. The first

The concentration of mobile ions in the

本実施の形態では、ソース領域またはドレイン領域として機能するn+層406a、40

6b、408a、408bは、In−Ga−Zn−O系非単結晶層であり、第1酸化物半

導体層405、第2酸化物半導体層407の形成条件とは異なる形成条件で形成される、

より低抵抗な酸化物半導体層である。例えば、n+層406a、406b、408a、4

08bは、n型の導電型を有し、活性化エネルギー(ΔE)が0.01eV以上0.1e

V以下である。なお、本実施の形態では、n+層406a、406b、408a、408

bは、In−Ga−Zn−O系非単結晶層であり、少なくともアモルファス成分を含んで

いるものとする。n+層406a、406b、408a、408bは非晶質構造の中に結

晶粒(ナノクリスタル)を含む場合がある。このn+層406a、406b、408a、

408b中の結晶粒(ナノクリスタル)は直径1nm〜10nm、代表的には2nm〜4

nm程度である。In this embodiment, n+ layers 406a and 40 function as source regions or drain regions.

6b, 408a, and 408b are In—Ga—Zn—O-based non-single-crystal layers, which are formed under formation conditions different from the formation conditions of the first

It is a lower resistance oxide semiconductor layer. For example, n+ layers 406a, 406b, 408a, 4

08b has n-type conductivity, and its activation energy (ΔE) is 0.01 eV or more and 0.1 e.

V or less. Note that in this embodiment mode, the n+ layers 406a, 406b, 408a, 408

b is an In—Ga—Zn—O-based non-single-crystal layer, and includes at least an amorphous component. The n+ layers 406a, 406b, 408a, and 408b may include crystal grains (nanocrystals) in an amorphous structure. This n+ layer 406a, 406b, 408a,

The crystal grains (nanocrystals) in 408b have a diameter of 1 nm to 10 nm, typically 2 nm to 4 nm.

It is about nm.

n+層406a、406b、408a、408bを設けることにより、金属層である第1

配線409、第2配線410、第3配線411と、第1酸化物半導体層405、第2酸化

物半導体層407との間を良好な接合としてショットキー接合に比べて熱的にも安定動作

を有せしめる。また、チャネルのキャリアを供給する(ソース側)、またはチャネルのキ

ャリアを安定して吸収する(ドレイン側)、または抵抗成分を配線との界面に作らないた

めにも積極的にn+層を設けると効果的である。また低抵抗化により、高いドレイン電圧

でも良好な移動度を保持することができる。By providing the n+ layers 406a, 406b, 408a, and 408b, a first metal layer is formed.

As a good junction between the

第1配線409〜第3配線411の材料としては、アルミニウム、クロム、タンタル、チ

タン、モリブデン、タングステンから選ばれた元素、上述した元素を主成分とする合金、

または上述した元素を組み合わせた合金等がある。また、第1配線409〜第3配線41

1は、シリコンを含むアルミニウム層の単層構造や、チタン層の単層構造としてもよい。

また、第1配線409〜第3配線411は、2層構造としてもよく、アルミニウム層上に

チタン層を積層してもよい。As materials of the

Alternatively, there are alloys that combine the above-described elements. Also, the

1 may be a single layer structure of an aluminum layer containing silicon or a single layer structure of a titanium layer.

The

また、後の工程で、200℃〜600℃の熱処理を行う場合には、第1配線409〜第3

配線411に、当該熱処理に耐える耐熱性を持たせることが好ましい。アルミニウム単体

では耐熱性が劣り、また腐蝕しやすい等の問題点があるので、耐熱性導電性材料と組み合

わせて形成する。アルミニウムと組み合わせる耐熱性導電性材料としては、チタン、タン

タル、タングステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素、

上述した元素を主成分とする合金、上述した元素を複数組み合わせた合金、または上述し

た元素の窒化物で形成する。Further, when heat treatment at 200 ° C. to 600 ° C. is performed in a later process, the

It is preferable that the

An alloy containing the above-described element as a main component, an alloy combining a plurality of the above-described elements, or a nitride of the above-described element is used.

第1薄膜トランジスタ430は、第1ゲート電極401と、ゲート絶縁層403を介して

第1ゲート電極401と重なる第1酸化物半導体層405とを有し、第1配線409は、

接地電位の電源線(接地電源線)である。この接地電位の電源線は、負の電圧VDLが印

加される電源線(負電源線)としてもよい。The first

This is a ground potential power line (ground power line). The power supply line having the ground potential may be a power supply line (negative power supply line) to which a negative voltage VDL is applied.

また、第2薄膜トランジスタ431は、第2ゲート電極402と、ゲート絶縁層403を

介して第2ゲート電極402と重なる第2酸化物半導体層407とを有し、第3配線41

1は、正の電圧VDDが印加される電源線(正電源線)である。The second

図1(A)に示すように、第1酸化物半導体層405と第2酸化物半導体層407の両方

に電気的に接続する第2配線410は、ゲート絶縁層403に形成されたコンタクトホー

ル404を介して第2薄膜トランジスタ431の第2ゲート電極402と直接接続する。

直接接続させることにより、良好なコンタクトを得ることができ、接触抵抗を低減するこ

とができる。第2ゲート電極402と第2配線410を他の導電層、例えば透明導電層を

介して接続する場合に比べて、コンタクトホールの数の低減、コンタクトホールの数の低

減による占有面積の縮小を図ることができる。As shown in FIG. 1A, the

By direct connection, good contact can be obtained and contact resistance can be reduced. Compared to the case where the

有機絶縁層452は、組成物を塗布し焼成して形成することで、第1酸化物半導体層40

5及び第2酸化物半導体層407にダメージを与えず形成することができる。有機絶縁層

452として用いることが可能な有機材料としては、エポキシ樹脂、ポリイミド、アクリ

ル樹脂、ポリアクリロニトリル、ポリアミド、シリコーン樹脂、ポリエステル、シロキサ

ンポリマー、フッ素含有ポリマー、低誘電率材料(low−k材料)、PSG(リンガラ

ス)、BPSG(リンボロンガラス)等がある。The organic insulating

5 and the second

また、有機絶縁層452として、可視光の波長範囲のうち、任意の波長範囲の光を優先的

に透過させる機能を持たせてもよい。赤色波長範囲の光、青色波長範囲の光、及び緑色波

長範囲の光、それぞれを優先的に透過させる有機絶縁層を組み合わせて、カラーフィルタ

として機能させてもよい。しかしながら、着色層の組み合わせに関しては、これに限られ

ない。The organic insulating

本実施の形態では、第1酸化物半導体層405及び第2酸化物半導体層407に接して、

塗布法により形成される有機絶縁層452を形成するため、薄膜トランジスタの電気特性

の信頼性を向上させることができる。In this embodiment, in contact with the first

Since the organic insulating

また、駆動回路のインバータ回路の上面図を図1(C)に示す。図1(C)において、鎖

線Z1−Z2で切断した断面が図1(A)に相当する。A top view of the inverter circuit of the driver circuit is shown in FIG. In FIG. 1C, a cross section taken along the chain line Z1-Z2 corresponds to FIG.

なお、表示装置において、画素部を駆動するための駆動回路は、インバータ回路、容量、

抵抗などを用いて構成する。2つのnチャネル型薄膜トランジスタを組み合わせてインバ

ータ回路を形成する場合、エンハンスメント型トランジスタとデプレッション型トランジ

スタとを組み合わせて形成する場合(以下、EDMOS回路という)と、エンハンスメン

ト型薄膜トランジスタ同士で形成する場合(以下、EEMOS回路という)がある。なお

、nチャネル型薄膜トランジスタのしきい値電圧が正の場合は、エンハンスメント型トラ

ンジスタと定義し、nチャネル型薄膜トランジスタのしきい値電圧がゼロまたは負の場合

は、デプレッション型トランジスタと定義し、本明細書を通してこの定義に従うものとす

る。Note that in the display device, a driver circuit for driving the pixel portion includes an inverter circuit, a capacitor,

It is configured using resistors. When an inverter circuit is formed by combining two n-channel thin film transistors, an enhancement type transistor and a depletion type transistor are combined (hereinafter referred to as an EDMOS circuit), or an enhancement type thin film transistor (hereinafter referred to as an enhancement type thin film transistor). EEMOS circuit). Note that when the threshold voltage of the n-channel thin film transistor is positive, it is defined as an enhancement type transistor, and when the threshold voltage of the n-channel thin film transistor is zero or negative, it is defined as a depletion type transistor. This definition shall be followed throughout the document.

画素部と駆動回路は、同一基板上に形成し、画素部においては、マトリクス状に配置した

エンハンスメント型トランジスタを用いて画素電極への電圧印加のオン・オフを切り替え

る。この画素部に配置するエンハンスメント型トランジスタは、酸化物半導体を用いてお

り、その電気特性は、ゲート電圧±20Vにおいて、オン・オフ比が109以上であるた

め、リーク電流が少なく、低消費電力駆動を実現することができる。The pixel portion and the driver circuit are formed over the same substrate, and in the pixel portion, on / off of voltage application to the pixel electrode is switched using enhancement type transistors arranged in a matrix. The enhancement-type transistor disposed in this pixel portion uses an oxide semiconductor, and its electrical characteristics are such that an on / off ratio is 109 or more at a gate voltage of ± 20 V, so that there is little leakage current and low power consumption. Driving can be realized.

EDMOS回路の等価回路を図1(B)に示す。図1(A)及び図1(C)示す回路接続

は、図1(B)に相当し、第1薄膜トランジスタ430をエンハンスメント型のnチャネ

ル型トランジスタとし、第2薄膜トランジスタ431をデプレッション型のnチャネル型

トランジスタとする例である。An equivalent circuit of the EDMOS circuit is shown in FIG. 1A and 1C corresponds to FIG. 1B. The first

同一基板上にエンハンスメント型のnチャネル型トランジスタとデプレッション型のnチ

ャネル型トランジスタとを作製する方法は、例えば、第1酸化物半導体層405と第2酸

化物半導体層407とを異なる材料や異なる形成条件を用いて作製する。また、酸化物半

導体層の上下にゲート電極を設けてしきい値制御を行い、一方のTFTがノーマリーオン

となるようにゲート電極に電圧をかけ、もう一方のTFTがノーマリーオフとなるように

してEDMOS回路を構成してもよい。As a method for manufacturing an enhancement type n-channel transistor and a depletion type n-channel transistor over the same substrate, for example, the first

本実施の形態で示す薄膜トランジスタは、酸化物半導体層上に有機絶縁層が形成されるた

め、薄膜トランジスタの電気特性の信頼性を高めることができる。In the thin film transistor described in this embodiment, an organic insulating layer is formed over an oxide semiconductor layer; thus, reliability of electric characteristics of the thin film transistor can be improved.

(実施の形態2)

実施の形態1は、EDMOS回路の例を示したが、本実施の形態では、EEMOS回路の

等価回路を図2(A)に示す。また、EEMOSの上面図を図2(B)に示す。また、図

2に示すEEMOS回路の作製工程を図3に示す。図2(A)の等価回路においては、ど

ちらもエンハンスメント型のnチャネル型トランジスタとする組み合わせとする。(Embodiment 2)

Although

エンハンスメント型のnチャネル型トランジスタで作製できる図2(A)のEEMOS回

路を駆動回路に用いることで、画素部に用いるトランジスタと同様に、駆動回路において

も、エンハンスメント型のnチャネル型トランジスタを作製するため、作製工程が増大せ

ず、好ましいと言える。By using the EEMOS circuit in FIG. 2A which can be manufactured using an enhancement type n-channel transistor for a driver circuit, an enhancement type n-channel transistor is manufactured in the driver circuit as well as the transistor used for the pixel portion. Therefore, it can be said that the manufacturing process does not increase and is preferable.

なお、図2に示す第1薄膜トランジスタ460、第2薄膜トランジスタ461は、逆スタ

ガ型薄膜トランジスタであり、酸化物半導体層上にソース領域またはドレイン領域を介し

て配線が設けられている薄膜トランジスタの例である。Note that each of the first

また、図2(B)中の鎖線Y1−Y2で切断した断面が、図3(C)に相当する。A cross section taken along chain line Y1-Y2 in FIG. 2B corresponds to FIG.

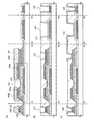

基板440上に、スパッタリング法により第1導電層を形成する。次に、第1フォトマス

クを用いたフォトリソグラフィ工程により形成したレジストマスクを用いて、選択的に第

1導電層のエッチングを行い、第1ゲート電極441及び第2ゲート電極442を形成す

る。この後、レジストマスクを除去する。A first conductive layer is formed over the

次に、第1ゲート電極401及び第2ゲート電極442を覆うゲート絶縁層443をプラ

ズマCVD法またはスパッタリング法を用いて形成する。ゲート絶縁層443は、CVD

法またはスパッタリング法等を用い、実施の形態1に列挙した材料を用いて形成すること

ができる。また、ゲート絶縁層443として、有機シランガスを用いたCVD法により酸

化シリコン層を形成することも可能である。有機シランガスとしては、珪酸エチル(TE

OS:化学式Si(OC2H5)4)、テトラメチルシラン(TMS:化学式Si(CH

3)4)、テトラメチルシクロテトラシロキサン(TMCTS)、オクタメチルシクロテ

トラシロキサン(OMCTS)、ヘキサメチルジシラザン(HMDS)、トリエトキシシ

ラン(SiH(OC2H5)3)、トリスジメチルアミノシラン(SiH(N(CH3)

2)3)等のシリコン含有化合物を用いることができる。Next, a

A method, a sputtering method, or the like can be used to form the material listed in

OS: chemical formula Si (OC2 H5 )4 ), tetramethylsilane (TMS: chemical formula Si (CH

3)4), tetramethylcyclotetrasiloxane (TMCTS), octamethylcyclotetrasiloxane (OMCTS), hexamethyldisilazane (HMDS), triethoxysilane(SiH(OC 2 H5) 3), trisdimethylaminosilane (SiH (N (CH3 )

A silicon-containing compound such as2 )3 ) can be used.

次いで、第2フォトマスクを用いたフォトリソグラフィ工程により形成したレジストマス

クを用いて、ゲート絶縁層443を選択的にエッチングして第2ゲート電極442に達す

るコンタクトホール444を形成する。この後、レジストマスクを除去する。ここまでの

段階での断面図が図3(A)に相当する。Next, the

次に、酸化物半導体層をスパッタリング法により形成し、さらにその上にn+層を形成す

る。なお、酸化物半導体層をスパッタリング法により形成する前に、アルゴンガスを導入

してプラズマを発生させる逆スパッタリングを行い、ゲート絶縁層443の表面及びコン

タクトホール444の底面に付着しているゴミを除去することが好ましい。逆スパッタリ

ングとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側にRF電源を用

いて電圧を印加して基板にプラズマを形成して表面を改質する方法である。なお、アルゴ

ン雰囲気に代えて窒素、ヘリウムなどを用いてもよい。また、アルゴン雰囲気に酸素、水

素、N2Oなどを加えた雰囲気で行ってもよい。また、アルゴン雰囲気にCl2、CF4

などを加えた雰囲気で行ってもよい。なお、逆スパッタリングを行うと、ゲート絶縁層4

03の表面が2〜10nm、好ましくは2〜10nm程度削られる。Next, an oxide semiconductor layer is formed by a sputtering method, and an n+ layer is further formed thereover. Note that before the oxide semiconductor layer is formed by a sputtering method, reverse sputtering that generates plasma by introducing argon gas is performed, so that dust attached to the surface of the

You may carry out in the atmosphere which added etc. When reverse sputtering is performed, the gate insulating layer 4

The surface of 03 is scraped by about 2 to 10 nm, preferably about 2 to 10 nm.

スパッタリング法にはスパッタリング用電源に高周波電源を用いるRFスパッタリング法

と、DCスパッタリング法があり、さらにパルス的にバイアスを与えるパルスDCスパッ

タリング法もある。RFスパッタリング法は主に絶縁層を形成する場合に用いられ、DC

スパッタリング法は主に金属層を形成する場合に用いられる。As the sputtering method, there are an RF sputtering method using a high-frequency power source as a sputtering power source and a DC sputtering method, and a pulse DC sputtering method for applying a bias in a pulsed manner. The RF sputtering method is mainly used when an insulating layer is formed.

The sputtering method is mainly used when a metal layer is formed.

また、材料の異なるターゲットを複数設置できる多元スパッタリング装置もある。多元ス

パッタリング装置は、同一チャンバーで異なる材料層を積層することも、同一チャンバー

で複数種類の材料を同時に放電させて形成することもできる。There is also a multi-source sputtering apparatus in which a plurality of targets of different materials can be installed. The multi-source sputtering apparatus can be formed by stacking different material layers in the same chamber or by simultaneously discharging a plurality of types of materials in the same chamber.

また、チャンバー内部に磁石機構を備えたマグネトロンスパッタリング法を用いるスパッ

タリング装置や、グロー放電を使わずマイクロ波を用いて発生させたプラズマを用いるE

CRスパッタリング法を用いるスパッタリング装置がある。Also, a sputtering apparatus using a magnetron sputtering method having a magnet mechanism inside the chamber, or an E using plasma generated using microwaves without using glow discharge.

There is a sputtering apparatus using a CR sputtering method.

また、形成方法として、成膜中にターゲット物質とスパッタリングガス成分とを化学反応

させてそれらの化合物薄膜を形成するリアクティブスパッタリング法や、成膜中に基板に

も電圧をかけるバイアススパッタリング法もある。As a forming method, there are a reactive sputtering method in which a target material and a sputtering gas component are chemically reacted during film formation to form a compound thin film thereof, and a bias sputtering method in which a voltage is applied to the substrate during film formation. .

本明細書のスパッタリングにおいては、上記したスパッタリング装置及びスパッタリング

方法を適宜用いることができる。In the sputtering of this specification, the above-described sputtering apparatus and sputtering method can be used as appropriate.

次いで、第3フォトマスクを用いて選択的に、酸化物半導体層及びn+層のエッチングを

行う。この後、レジストマスクを除去する。Next, the oxide semiconductor layer and the n+ layer are selectively etched using a third photomask. Thereafter, the resist mask is removed.

次に、スパッタリング法により第2導電層を形成する。次に、第4フォトマスクを用いた

フォトリソグラフィ工程により形成したレジストマスクを用いて選択的に第2導電層のエ

ッチングを行い、第1配線449、第2配線450、及び第3配線451を形成する。第

3配線451は、コンタクトホール444を介して第2ゲート電極442と直接接する。Next, a second conductive layer is formed by a sputtering method. Next, the second conductive layer is selectively etched using a resist mask formed by a photolithography process using a fourth photomask to form a

なお、第2導電層をスパッタリング法により形成する前に、アルゴンガスを導入してプラ

ズマを発生させる逆スパッタリングを行い、ゲート絶縁層443の表面、n+層の表面、

及びコンタクトホール444の底面に付着しているゴミを除去することが好ましい。なお

、アルゴン雰囲気に代えて窒素、ヘリウムなどを用いてもよい。また、アルゴン雰囲気に

酸素、水素、N2Oなどを加えた雰囲気で行ってもよい。また、アルゴン雰囲気にCl2

、CF4などを加えた雰囲気で行ってもよい。Note that before the second conductive layer is formed by a sputtering method, reverse sputtering in which an argon gas is introduced to generate plasma is performed, and the surface of the

It is preferable to remove dust attached to the bottom surface of the

, CF4 or the like.

なお、第2導電層のエッチングの際に、さらに、n+層及び酸化物半導体層の一部をエッ

チングして、n+層446a、446b、448a、448b、第1酸化物半導体層44

5、第2酸化物半導体層447を形成する。このエッチングで第1ゲート電極及び第2ゲ

ート電極と重なる部分の第1酸化物半導体層445、第2酸化物半導体層447の厚さは

薄くなる。この後、レジストマスクを除去する。このエッチングが終了した段階で第1薄

膜トランジスタ460と第2薄膜トランジスタ461が完成する。ここまでの段階での断

面図が図3(B)に相当する。Note that when the second conductive layer is etched, the n+ layer and a part of the oxide semiconductor layer are further etched to form the n+ layers 446a, 446b, 448a, 448b, and the first oxide semiconductor layer 44.

5. A second

ここで、第1薄膜トランジスタ460の拡大図を図43に示す。第2導電層をスパッタリ

ング法により形成する前に逆スパッタリングを行うと、ゲート絶縁層443の露出部が2

〜10nm、好ましくは2〜10nm程度削られるため、図43に示すように、ゲート絶

縁層443と、後に形成される第1配線449及び第2配線450が接する領域において

、ゲート絶縁層443に凹部471a、471bが形成される。Here, an enlarged view of the first

Since the thickness is reduced to about 10 nm, preferably about 2 to 10 nm, a recess is formed in the

また、第2導電層のエッチングを行い、第1配線449、第2配線450、及び第3配線

451を形成した後、逆スパッタリングすることで、図3(B)に示すように、第1配線

449、第2配線450、及び第3配線451の端部が湾曲する。Further, after the second conductive layer is etched to form the

次に、大気雰囲気下または窒素雰囲気下で200℃〜600℃の加熱処理を行う。この熱

処理によりIn−Ga−Zn−O系非単結晶層の原子レベルの再配列が行われる。この熱

処理によりキャリアの移動を阻害する歪が解放されるため、ここでの熱処理(光アニール

も含む)は重要である。なお、この加熱処理を行うタイミングは限定されず、酸化物半導

体層445、447の形成後であれば、いつ行ってもよい。Next, heat treatment is performed at 200 ° C. to 600 ° C. in an air atmosphere or a nitrogen atmosphere. By this heat treatment, rearrangement at the atomic level of the In—Ga—Zn—O-based non-single-crystal layer is performed. Since heat treatment releases strain that hinders carrier movement, heat treatment here (including optical annealing) is important. Note that the timing of performing this heat treatment is not limited and may be any time after the oxide semiconductor layers 445 and 447 are formed.

次に、有機絶縁層の材料である組成物を塗布し、大気雰囲気下または窒素雰囲気下で20

0℃〜600℃の加熱処理を行って、有機絶縁層452を形成する。有機絶縁層452は

、実施の形態1に示す材料を適宜用いることができる。図3(C)においては、非感光性

樹脂を用いて有機絶縁層452を形成した形態を示したため、コンタクトホールが形成さ

れる領域の断面において、有機絶縁層452の端部が角張っている。しかしながら、感光

性樹脂を用いて有機絶縁層452を形成すると、図44に示すように、コンタクトホール

が形成される領域の断面において、有機絶縁層452の端部は湾曲している。この結果、

後に形成される接続配線453や画素電極の被覆率が向上する。Next, a composition which is a material of the organic insulating layer is applied, and 20% in an air atmosphere or a nitrogen atmosphere.

A heat treatment at 0 ° C. to 600 ° C. is performed to form the organic insulating

The coverage of

また、組成物を塗布する代わりに、その材料に応じて、ディップ、スプレー塗布、インク

ジェット法、印刷法、ドクターナイフ、ロールコーター、カーテンコーター、ナイフコー

ター等を用いることができる。Further, instead of applying the composition, dip, spray coating, ink jet method, printing method, doctor knife, roll coater, curtain coater, knife coater or the like can be used depending on the material.

なお、酸化物半導体層445、447を形成した後の加熱処理をせず、有機絶縁層の材料

である組成物の加熱処理時に、酸化物半導体層445、447の加熱処理を兼ねてもよい

。Note that heat treatment after the oxide semiconductor layers 445 and 447 are formed may be combined with heat treatment of the oxide semiconductor layers 445 and 447 at the time of heat treatment of the composition that is a material of the organic insulating layer.

有機絶縁層452は、200nm〜5μm、好ましくは300nm〜1μmで形成する。The organic insulating

次に、第3導電層を形成する。次に、第5フォトマスクを用いたフォトリソグラフィ工程

により形成したレジストマスクを用いて第3導電層を選択的にエッチングして、第2配線

410と電気的に接続する接続配線453を形成する。ここまでの段階での断面図が図3

(C)に相当する。Next, a third conductive layer is formed. Next, the third conductive layer is selectively etched using a resist mask formed by a photolithography process using a fifth photomask, so that connection wirings 453 that are electrically connected to the

Corresponds to (C).

なお、レジストマスクをウェットエッチングで除去した後、大気雰囲気下または窒素雰囲

気下で200℃〜600℃の加熱処理を行ってもよい。Note that after the resist mask is removed by wet etching, heat treatment at 200 ° C. to 600 ° C. may be performed in an air atmosphere or a nitrogen atmosphere.

発光素子を用いた発光表示装置においては、画素部に複数の薄膜トランジスタを有し、画

素部においても、ある一つの薄膜トランジスタのゲート電極と他のトランジスタのソース

配線、或いはドレイン配線を直接接続させるためのコンタクトホールを有している。この

コンタクトホールは、第2フォトマスクを用いてゲート絶縁層にコンタクトホールを形成

する際に同じマスクを用いて形成することができる。In a light-emitting display device using a light-emitting element, a pixel portion includes a plurality of thin film transistors, and in the pixel portion, a gate electrode of one thin film transistor and a source wiring or a drain wiring of another transistor are directly connected. Has a contact hole. This contact hole can be formed using the same mask when the contact hole is formed in the gate insulating layer using the second photomask.

また、液晶表示装置や電子ペーパーにおいては、FPCなどの外部端子と接続するための

端子部において、ゲート配線に達するコンタクトホールを形成する際、第2フォトマスク

を用いてゲート絶縁層にコンタクトホールを形成する際に同じマスクを用いて形成するこ

とができる。In a liquid crystal display device or electronic paper, when a contact hole reaching a gate wiring is formed in a terminal portion for connecting to an external terminal such as an FPC, a contact hole is formed in the gate insulating layer using a second photomask. When forming, the same mask can be used.

なお、上述した工程順序は一例であって特に限定されない。例えば、フォトマスク数が1

枚増えるが、第2導電層をエッチングするフォトマスクと、n+層及び酸化物半導体層の

一部をエッチングするフォトマスクを別々に用いてエッチングを行ってもよい。In addition, the process sequence mentioned above is an example, and is not specifically limited. For example, the number of photomasks is 1

Although the number of the layers increases, the photomask for etching the second conductive layer and the photomask for etching part of the n+ layer and the oxide semiconductor layer may be separately used for etching.

以上の工程により、酸化物半導体層に接する有機絶縁層を形成することで、電気特性の信

頼性の高い薄膜トランジスタを作製することができる。By forming the organic insulating layer in contact with the oxide semiconductor layer through the above steps, a thin film transistor with high electrical characteristics can be manufactured.

(実施の形態3)

本実施の形態では、インバータ回路の作製において、実施の形態2とは異なる作製工程の

例を図4(A)、図4(B)、及び図4(C)を用いて説明する。(Embodiment 3)

In this embodiment, an example of a manufacturing process which is different from that in

基板440上に、スパッタリング法により第1導電層を形成する。次に、第1フォトマス

クを用いたフォトリソグラフィ工程により形成したレジストマスクを用いて、選択的に第

1導電層のエッチングを行い、第1ゲート電極441及び第2ゲート電極442を形成す

る。この後、レジストマスクを除去する。A first conductive layer is formed over the

次に、第1ゲート電極441及び第2ゲート電極442を覆うゲート絶縁層443をプラ

ズマCVD法またはスパッタリング法を用いて形成する。Next, a

次に、酸化物半導体層をスパッタリング法により形成し、さらにその上にn+層を形成す

る。Next, an oxide semiconductor layer is formed by a sputtering method, and an n+ layer is further formed thereover.

次いで、第2フォトマスクを用いたフォトリソグラフィ工程により形成したレジストマス

クを用いて、選択的に、酸化物半導体層及びn+層のエッチングを行う。こうして、第1

ゲート電極441とゲート絶縁層443を介して重なる酸化物半導体層454、及びn+

層455が形成され、第2ゲート電極442とゲート絶縁層443を介して重なる酸化物

半導体層456、n+層457が形成される。ここまでの段階での断面図が図4(A)に

相当する。Next, the oxide semiconductor layer and the n+ layer are selectively etched using a resist mask formed by a photolithography process using a second photomask. Thus, the first

An

The

次いで、第3フォトマスクを用いフォトリソグラフィ工程により形成したレジストマスク

を用いて、ゲート絶縁層443を選択的にエッチングして第2ゲート電極442に達する

コンタクトホール444を形成する。この後、レジストマスクを除去する。ここまでの段

階での断面図が図4(B)に相当する。Next, the

次いで、スパッタリング法により第2導電層を形成し、第4フォトマスクを用いて選択的

に第2導電層のエッチングを行い、第1配線449、第2配線450、及び第3配線45

1を形成する。Next, a second conductive layer is formed by a sputtering method, and the second conductive layer is selectively etched using a fourth photomask, whereby the

1 is formed.

なお、第2導電層をスパッタリング法により形成する前に、アルゴンガスを導入してプラ

ズマを発生させる逆スパッタリングを行い、ゲート絶縁層443の表面、n+層455、

457の表面、及びコンタクトホール444の底面に付着しているゴミを除去することが

好ましい。なお、アルゴン雰囲気に代えて窒素、ヘリウムなどを用いてもよい。また、ア

ルゴン雰囲気に酸素、水素、N2Oなどを加えた雰囲気で行ってもよい。また、アルゴン

雰囲気にCl2、CF4などを加えた雰囲気で行ってもよい。Note that before the second conductive layer is formed by a sputtering method, reverse sputtering that generates plasma by introducing argon gas is performed, and the surface of the

It is preferable to remove dust attached to the surface of 457 and the bottom surface of the

本実施の形態の工程においては、コンタクトホール444を形成した後、他の層を形成す

ることなく第2導電層を形成することができるため、実施の形態2に比べてコンタクトホ

ールの底面が曝される工程数が少ないため、ゲート電極の材料の材料選択の自由度が広が

る。これは、実施の形態2においては、コンタクトホール444で露出しているゲート電

極面に接して酸化物半導体層が形成されるため、酸化物半導体層のエッチング工程でゲー

ト電極の材料がエッチングされないエッチング条件またはゲート電極の材料を選択する必

要があるためである。In the process of this embodiment mode, after the

なお、第2導電層のエッチングの際に、さらに、n+層及び酸化物半導体層の一部をエッ

チングして、n+層446a、446b、448a、448b、第1酸化物半導体層44

5、第2酸化物半導体層447を形成する。このエッチングで第1ゲート電極及び第2ゲ

ート電極と重なる部分の第1酸化物半導体層445、第2酸化物半導体層447の厚さは

薄くなる。この後、レジストマスクを除去する。このエッチングが終了した段階で第1薄

膜トランジスタ460と第2薄膜トランジスタ461が完成する。Note that when the second conductive layer is etched, the n+ layer and a part of the oxide semiconductor layer are further etched to form the n+ layers 446a, 446b, 448a, 448b, and the first oxide semiconductor layer 44.

5. A second

第1薄膜トランジスタ460は、第1ゲート電極441と、ゲート絶縁層443を介して

第1ゲート電極441と重なる第1酸化物半導体層445とを有し、第1配線449は、

接地電位の電源線(接地電源線)である。この接地電位の電源線は、負の電圧VDLが印

加される電源線(負電源線)としてもよい。The first

This is a ground potential power line (ground power line). The power supply line having the ground potential may be a power supply line (negative power supply line) to which a negative voltage VDL is applied.

また、第2薄膜トランジスタ461は、第2ゲート電極442と、ゲート絶縁層443を

介して第2ゲート電極442と重なる第2酸化物半導体層447とを有し、第3配線45

1は、正の電圧VDDが印加される電源線(正電源線)である。The second

また、第1酸化物半導体層445と第1配線449との間にはn+層446aを設け、第

1酸化物半導体層445と第2配線450との間にはn+層446bを設ける。また、第

2酸化物半導体層447と第2配線450との間にはn+層448aを設け、第2酸化物

半導体層447と第3配線451との間にはn+層448bを設ける。Further, the first

ここまでの段階での断面図が図4(C)に相当する。A cross-sectional view of the steps so far corresponds to FIG.

次に、大気雰囲気下または窒素雰囲気下で200℃〜600℃の加熱処理を行う。なお、

この加熱処理を行うタイミングは限定されず、酸化物半導体層の形成後であれば、いつ行

ってもよい。Next, heat treatment is performed at 200 ° C. to 600 ° C. in an air atmosphere or a nitrogen atmosphere. In addition,

The timing for performing the heat treatment is not limited, and may be any time after the oxide semiconductor layer is formed.

次に、有機絶縁層の材料である組成物を塗布し、大気雰囲気下または窒素雰囲気下で20

0℃〜600℃の加熱処理を行って、有機絶縁層452を形成する。有機絶縁層452は

、実施の形態1に示す材料を適宜用いることができる。なお、第1酸化物半導体層445

、第2酸化物半導体層447を形成した後の加熱処理をせず、有機絶縁層の材料である組

成物の加熱処理時に、酸化物半導体層445、447の加熱処理を兼ねてもよい。Next, a composition which is a material of the organic insulating layer is applied, and 20% in an air atmosphere or a nitrogen atmosphere.

A heat treatment at 0 ° C. to 600 ° C. is performed to form the organic insulating

The heat treatment after the formation of the second

次に、第5フォトマスクを用いたフォトリソグラフィ工程により形成したレジストマスク

を用いて、有機絶縁層452を選択的にエッチングしてコンタクトホールを形成する。こ

の後、レジストマスクを除去する。なお、有機絶縁層452が感光性樹脂で形成される場

合、有機絶縁層452上にレジストを塗布せず、第5フォトマスクを用いて有機絶縁層を

露光現像して、有機絶縁層452にコンタクトホールを形成することができる。Next, a contact hole is formed by selectively etching the organic insulating

次に、第3導電層を形成する。次に、第6フォトマスクを用いたフォトリソグラフィ工程

により形成したレジストマスクを用いて第3導電層を選択的にエッチングして、第2配線

450と電気的に接続する接続配線453を形成する。ここまでの段階での断面図が図4

(D)に相当する。Next, a third conductive layer is formed. Next, the third conductive layer is selectively etched using a resist mask formed by a photolithography process using a sixth photomask, so that connection wirings 453 that are electrically connected to the

Corresponds to (D).

なお、レジストマスクをウェットエッチングで除去した場合、大気雰囲気下または窒素雰

囲気下で200℃〜600℃の加熱処理を行ってもよい。Note that when the resist mask is removed by wet etching, heat treatment at 200 ° C. to 600 ° C. may be performed in an air atmosphere or a nitrogen atmosphere.

発光素子を用いた発光表示装置においては、画素部に複数の薄膜トランジスタを有し、画

素部においてもある薄膜トランジスタのゲート電極と他のトランジスタのソース配線、或

いはドレイン配線を直接接続させるためのコンタクトホールを有している。このコンタク

ト部は、第3フォトマスクを用いてゲート絶縁層にコンタクトホールを形成する際に同じ

マスクを用いて形成することができる。In a light-emitting display device using a light-emitting element, a pixel portion includes a plurality of thin film transistors, and a contact hole for directly connecting a gate electrode of a thin film transistor in the pixel portion to a source wiring or a drain wiring of another transistor is provided. Have. This contact portion can be formed using the same mask when the contact hole is formed in the gate insulating layer using the third photomask.

また、液晶表示装置や電子ペーパーにおいては、FPCなどの外部端子と接続するための

端子部において、ゲート配線に達するコンタクトホールを形成する際、第3フォトマスク

を用いてゲート絶縁層にコンタクトホールを形成する際に同じマスクを用いて形成するこ

とができる。In a liquid crystal display device or electronic paper, when a contact hole reaching a gate wiring is formed in a terminal portion for connecting to an external terminal such as an FPC, a contact hole is formed in the gate insulating layer using a third photomask. When forming, the same mask can be used.

なお、上述した工程順序は一例であって特に限定されない。例えば、フォトマスク数が1

枚増えるが、第2導電層をエッチングするフォトマスクと、n+層及び酸化物半導体層の

一部をエッチングするフォトマスクを別々に用いてエッチングを行ってもよい。In addition, the process sequence mentioned above is an example, and is not specifically limited. For example, the number of photomasks is 1

Although the number of the layers increases, the photomask for etching the second conductive layer and the photomask for etching part of the n+ layer and the oxide semiconductor layer may be separately used for etching.

以上の工程により、酸化物半導体層に接する有機絶縁層を形成することで、電気特性の信

頼性の高い薄膜トランジスタを作製することができる。By forming the organic insulating layer in contact with the oxide semiconductor layer through the above steps, a thin film transistor with high electrical characteristics can be manufactured.

(実施の形態4)

本実施の形態では、実施の形態1または実施の形態2に示した駆動回路と同一基板上に形

成できる画素部の薄膜トランジスタ、及び端子部の作製工程について、図5乃至図12を

用いて説明する。(Embodiment 4)

In this embodiment, a manufacturing process of a thin film transistor in a pixel portion and a terminal portion that can be formed over the same substrate as the driver circuit described in

図5(A)において、基板100には、実施の形態1に示す基板400を適宜用いること

ができる。5A, the

次に、基板100全面に導電層を形成した後、第1フォトリソグラフィ工程を行って形成

したレジストマスクを用いたエッチングにより不要な部分を除去して、配線及び電極(ゲ

ート電極101を含むゲート配線、容量配線108、及び第1端子121)を形成する。

このとき少なくともゲート電極101の端部にテーパー形状が形成されるようにエッチン

グする。この後、レジストマスクを除去する。なお、この段階での上面図が図7に相当す

る。後に形成される酸化物半導体層、ソース電極層、ドレイン電極層、画素電極、コンタ

クトホールは破線で示されている。Next, after a conductive layer is formed over the entire surface of the

At this time, etching is performed so that at least an end portion of the

ゲート電極101を含むゲート配線と容量配線108、端子部の第1端子121は、実施

の形態1に示す第1ゲート電極401、第2ゲート電極402の材料を適宜用いて形成す

る。The gate wiring including the

次に、ゲート電極101上にゲート絶縁層102を全面に形成する。ゲート絶縁層102

は、実施の形態1に示すゲート絶縁層403の適宜用い、スパッタリング法などを用い、

厚さを50〜250nmとする。Next, a

The

The thickness is 50 to 250 nm.

なお、酸化物半導体層を形成する前に、アルゴンガスを導入してプラズマを発生させる逆

スパッタリングを行い、ゲート絶縁層の表面に付着しているゴミを除去することが好まし

い。なお、アルゴン雰囲気に代えて窒素、ヘリウムなどを用いてもよい。また、アルゴン

雰囲気に酸素、水素、N2Oなどを加えた雰囲気で行ってもよい。また、アルゴン雰囲気

にCl2、CF4などを加えた雰囲気で行ってもよい。Note that before the oxide semiconductor layer is formed, it is preferable to perform reverse sputtering in which an argon gas is introduced to generate plasma to remove dust attached to the surface of the gate insulating layer. Note that nitrogen, helium, or the like may be used instead of the argon atmosphere. Alternatively, an atmosphere in which oxygen, hydrogen, N2 O, or the like is added to an argon atmosphere may be used. Alternatively, an atmosphere in which Cl2 , CF4, or the like is added to an argon atmosphere may be used.

次に、ゲート絶縁層102上に、第1酸化物半導体層(本実施の形態では第1In−Ga

−Zn−O系非単結晶層)を形成する。プラズマ処理後、大気に曝すことなく第1In−

Ga−Zn−O系非単結晶層を形成することは、ゲート絶縁層と酸化物半導体層の界面に

ゴミや水分を付着させない点で有用である。Next, over the

-Zn-O-based non-single crystal layer). After the plasma treatment, the first In-

The formation of the Ga—Zn—O-based non-single-crystal layer is useful in that dust and moisture are not attached to the interface between the gate insulating layer and the oxide semiconductor layer.

ここでは、直径8インチのIn、Ga、及びZnを含む酸化物半導体ターゲット(In2

O3:Ga2O3:ZnO=1:1:1)を用いて、基板とターゲットの間との距離を1

70mm、圧力0.4Pa、直流(DC)電源0.5kW、アルゴンまたは酸素雰囲気下

で形成する。なお、パルス直流(DC)電源を用いると、ごみが軽減でき、膜厚分布も均

一となるために好ましい。第1In−Ga−Zn−O系非単結晶層の厚さは、5nm〜2

00nmとする。本実施の形態では第1In−Ga−Zn−O系非単結晶層の厚さを、1

00nmとする。Here, an oxide semiconductor target containing In, Ga, and Zn having an diameter of 8 inches (In2

O3 : Ga2 O3 : ZnO = 1: 1: 1), the distance between the substrate and the target is 1

It is formed in 70 mm, pressure 0.4 Pa, direct current (DC) power supply 0.5 kW, argon or oxygen atmosphere. Note that a pulse direct current (DC) power source is preferable because dust can be reduced and the film thickness can be uniform. The thickness of the first In—Ga—Zn—O-based non-single-crystal layer is 5 nm to 2 nm.

Set to 00 nm. In this embodiment, the thickness of the first In—Ga—Zn—O-based non-single-crystal layer is set to 1

Set to 00 nm.

次いで、大気に曝すことなく、第2酸化物半導体層(本実施の形態では第2In−Ga−

Zn−O系非単結晶層)をスパッタリング法で形成する。ここでは、In2O3:Ga2

O3:ZnO=1:1:1としたターゲットを用い、形成条件は、圧力を0.4Paとし

、電力を500Wとし、成膜温度を室温とし、アルゴンガス流量40sccmを導入して

、スパッタリングを行う。In2O3:Ga2O3:ZnO=1:1:1としたターゲッ

トを意図的に用いているにも関わらず、成膜直後で大きさ1nm〜10nmの結晶粒を含

むIn−Ga−Zn−O系非単結晶層が形成されることがある。なお、ターゲットの成分

比、成膜圧力(0.1Pa〜2.0Pa)、電力(250W〜3000W:8インチφ)

、温度(室温〜100℃)、反応性スパッタリングの形成条件などを適宜調節することで

結晶粒の有無や、結晶粒の密度や、直径サイズは、1nm〜10nmの範囲で調節されう

ると言える。第2In−Ga−Zn−O系非単結晶層の厚さは、5nm〜20nmとする

。勿論、層中に結晶粒が含まれる場合、含まれる結晶粒のサイズが厚さを超える大きさと

ならない。本実施の形態では第2In−Ga−Zn−O系非単結晶層の厚さは、5nmと

する。Next, the second oxide semiconductor layer (the second In—Ga— in this embodiment is not exposed to the atmosphere).

Zn—O-based non-single crystal layer) is formed by a sputtering method. Here, In2 O3 : Ga2

Using a target with O3 : ZnO = 1: 1: 1, the formation conditions were a pressure of 0.4 Pa, a power of 500 W, a film formation temperature of room temperature, an argon gas flow rate of 40 sccm, and sputtering. Do. In—Ga— containing crystal grains having a size of 1 nm to 10 nm immediately after film formation, despite the intentional use of a target of In2 O3 : Ga2 O3 : ZnO = 1: 1: 1. A Zn—O-based non-single crystal layer may be formed. In addition, target component ratio, film forming pressure (0.1 Pa to 2.0 Pa), power (250 W to 3000 W: 8 inches φ)

It can be said that the presence or absence of crystal grains, the density of crystal grains, and the diameter size can be adjusted in the range of 1 nm to 10 nm by appropriately adjusting the temperature (room temperature to 100 ° C.), the reactive sputtering formation conditions, and the like. The thickness of the second In—Ga—Zn—O-based non-single-crystal layer is 5 nm to 20 nm. Of course, when crystal grains are included in the layer, the size of the included crystal grains does not exceed the thickness. In this embodiment, the thickness of the second In—Ga—Zn—O-based non-single-crystal layer is 5 nm.

第1In−Ga−Zn−O系非単結晶層は、第2In−Ga−Zn−O系非単結晶層の形

成条件と異ならせる。例えば、第2In−Ga−Zn−O系非単結晶層の形成条件におけ

る酸素ガス流量とアルゴンガス流量の比よりも、第1In−Ga−Zn−O系非単結晶層

の形成条件における酸素ガス流量の占める比率が多い条件とする。具体的には、第2In

−Ga−Zn−O系非単結晶層の形成条件は、希ガス(アルゴン、またはヘリウムなど)

雰囲気下(または酸素ガス10%以下、アルゴンガス90%以上)とし、第1In−Ga

−Zn−O系非単結晶層の形成条件は、酸素雰囲気下(または酸素ガス流量とアルゴンガ

ス流量の比1:1)とする。The first In—Ga—Zn—O-based non-single-crystal layer is different from the formation conditions of the second In—Ga—Zn—O-based non-single-crystal layer. For example, the oxygen gas in the formation condition of the first In—Ga—Zn—O-based non-single-crystal layer is larger than the ratio of the oxygen gas flow rate to the argon gas flow rate in the formation condition of the second In—Ga—Zn—O-based non-single-crystal layer. The conditions are such that the ratio of flow rate is large. Specifically, the second In

The formation condition of the —Ga—Zn—O-based non-single-crystal layer is a rare gas (such as argon or helium).

Under an atmosphere (or oxygen gas 10% or less, argon gas 90% or more), the first In—Ga

The formation condition of the —Zn—O-based non-single-crystal layer is an oxygen atmosphere (or a ratio of an oxygen gas flow rate to an argon gas flow rate of 1: 1).

次に、第2フォトリソグラフィ工程を行ってレジストマスクを形成し、当該レジストマス

クを用いて、第1In−Ga−Zn−O系非単結晶層及び第2In−Ga−Zn−O系非

単結晶層をエッチングする。ここでは、エッチャントとしてITO07N(関東化学社製

)を用いたウェットエッチングにより、不要な部分を除去して第1In−Ga−Zn−O

系非単結晶層である酸化物半導体層109、第2In−Ga−Zn−O系非単結晶層であ

る酸化物半導体層111を形成する。なお、ここでのエッチングは、ウェットエッチング

に限定されずドライエッチングを用いてもよい。この段階での上面図を図5(B)に示し

た。なお、この段階での上面図が図8に相当する。後に形成されるソース電極、ドレイン

電極、画素電極、コンタクトホール等は破線で示されている。この後、レジストマスクを

除去する。Next, a second photolithography step is performed to form a resist mask, and the first In—Ga—Zn—O-based non-single crystal layer and the second In—Ga—Zn—O-based non-single crystal are formed using the resist mask. Etch the layer. Here, unnecessary portions are removed by wet etching using ITO07N (manufactured by Kanto Chemical Co., Inc.) as an etchant to remove the first In—Ga—Zn—O.

The

次いで、第3フォトリソグラフィ工程を行ってレジストマスクを形成し、当該レジストマ

スクを用いたエッチングにより、不要な部分を除去してゲート電極と同じ材料の配線や電

極に達するコンタクトホールを形成する。このコンタクトホールは後に形成する導電層と

直接接続するために設ける。例えば、駆動回路部において、ゲート電極とソース電極或い

はドレイン電極と直接接する薄膜トランジスタや、端子部のゲート配線と電気的に接続す

る端子を形成する場合にコンタクトホールを形成する。この後、レジストマスクを除去す

る。Next, a resist mask is formed by performing a third photolithography step, and unnecessary portions are removed by etching using the resist mask to form a contact hole reaching the wiring or electrode of the same material as the gate electrode. This contact hole is provided for direct connection to a conductive layer to be formed later. For example, a contact hole is formed when a thin film transistor in direct contact with a gate electrode and a source electrode or a drain electrode or a terminal electrically connected to a gate wiring in a terminal portion is formed in a driver circuit portion. Thereafter, the resist mask is removed.

次に、酸化物半導体層109及び酸化物半導体層111上に金属材料からなる導電層13

2を、スパッタリング法や真空蒸着法で形成する。この段階での断面図を図5(C)に示

す。Next, the conductive layer 13 made of a metal material over the

2 is formed by sputtering or vacuum deposition. A cross-sectional view at this stage is illustrated in FIG.

導電層132の材料としては、実施の形態1に示す第1配線409〜第3配線411の材

料を適宜用いることができる。As a material of the

次に、第4フォトリソグラフィ工程を行ってレジストマスク131を形成し、当該レジス

トマスクを用いたエッチングにより不要な部分を除去して、ソース電極またはドレイン電

極105a、105b、ソース領域またはドレイン領域として機能するn+層104a、

104b、及び接続電極120、第2端子122を形成する。この際のエッチング方法と

してウェットエッチングまたはドライエッチングを用いる。Next, a resist

104b, the

例えば導電層132としてアルミニウム層、またはアルミニウム合金層を用いる場合は、

燐酸と酢酸と硝酸を混ぜた溶液を用いたウェットエッチングを行うことができる。ここで

は、アンモニア過水(過酸化水素:アンモニア:水=5:2:2)を用いたウェットエッ

チングにより、チタン層で形成される導電層132をエッチングして、ソース電極または

ドレイン電極105a、105bを形成する。また、酸化物半導体層111をエッチング

して、n+層104a、104bを形成する。このエッチング工程において、酸化物半導

体層109の露出領域も一部エッチングされ、酸化物半導体層103となる。よってn+

層104a、104bの間の酸化物半導体層103のチャネル領域は、厚さの薄い領域と

なる。For example, when an aluminum layer or an aluminum alloy layer is used as the

Wet etching using a mixed solution of phosphoric acid, acetic acid and nitric acid can be performed. Here, the

A channel region of the

図6(A)においては、ソース電極またはドレイン電極105a、105b、n+層10

4a、104bのエッチングをアンモニア過水のエッチング材によって一度に行うため、

ソース電極またはドレイン電極105a、105b及、びn+層104a、104bの端

部は一致し、連続的な構造となっている。またウェットエッチングを用いるために、エッ

チングが等方的に行われ、ソース電極またはドレイン電極105a、105bの端部はレ

ジストマスク131より後退している。この後、レジストマスクを除去する。以上の工程

で酸化物半導体層103をチャネル形成領域とする薄膜トランジスタ170を作製するこ

とができる。この段階での断面図を図6(A)に示す。なお、この段階での上面図が図9

に相当する。後に形成される画素電極、コンタクトホール等は破線で示されている。In FIG. 6A, source or

In order to perform the etching of 4a and 104b at once with the etching agent of ammonia-water,

The end portions of the source or

It corresponds to. Pixel electrodes, contact holes, and the like that are formed later are indicated by broken lines.

さらに、露出している酸化物半導体層103のチャネル形成領域に、酸素ラジカル処理を

行ってもよい。酸素ラジカル処理を行うことにより薄膜トランジスタをノーマリーオフと

することができる。また、ラジカル処理を行うことにより、酸化物半導体層103のエッ

チングによるダメージを回復することができる。ラジカル処理はO2、N2O、好ましく

は酸素を含むN2、He、Ar雰囲気下で行うことが好ましい。また、上記雰囲気にCl

2、CF4を加えた雰囲気下で行ってもよい。なお、ラジカル処理は、無バイアスで行う

ことが好ましい。また、当該ラジカル処理により、ソース電極105a、ドレイン電極1

05b、接続電極120、及び第2端子122の端部が湾曲する。Further, oxygen radical treatment may be performed on the exposed channel formation region of the

2, CF4 and may be carried out in an atmosphere which was added. Note that the radical treatment is preferably performed without bias. Further, by the radical treatment, the

05b, the

なお、当該ラジカル処理を行わなかった場合は、図6(A)に示すように、ソース電極1

05a、ドレイン電極105b、接続電極120、及び第2端子122の端部は湾曲せず

、角張っている。When the radical treatment is not performed, as shown in FIG. 6A, the

The ends of 05a, the

また、この第4フォトリソグラフィ工程において、ソース電極またはドレイン電極105

a、105bと同じ材料である第2端子122を端子部に残す。なお、第2端子122は

ソース配線(ソース電極またはドレイン電極105a、105bを含むソース配線)と電

気的に接続されている。In the fourth photolithography step, the source electrode or the drain electrode 105

The

また、端子部において、接続電極120は、ゲート絶縁層に形成されたコンタクトホール

を介して端子部の第1端子121と直接接続される。なお、ここでは図示しないが、上述

した工程と同じ工程を経て駆動回路の薄膜トランジスタのソース配線あるいはドレイン配

線とゲート電極が直接接続される。In the terminal portion, the

次に、200℃〜600℃、代表的には300℃〜500℃の熱処理を行うことが好まし

い。ここでは炉に入れ、窒素雰囲気下で350℃、1時間の熱処理を行う。この熱処理に

よりIn−Ga−Zn−O系非単結晶層の原子レベルの再配列が行われる。この熱処理に

よりキャリアの移動を阻害する歪みが解放されるため、ここでの熱処理(光アニールも含

む)は重要である。なお、熱処理を行うタイミングは、第2In−Ga−Zn−O系非単

結晶層の形成後であれば特に限定されず、後に行われる有機絶縁層の形成後に行ってもよ

い。Next, it is preferable to perform heat treatment at 200 ° C. to 600 ° C., typically 300 ° C. to 500 ° C. Here, heat treatment is performed in a furnace at 350 ° C. for 1 hour in a nitrogen atmosphere. By this heat treatment, rearrangement at the atomic level of the In—Ga—Zn—O-based non-single-crystal layer is performed. The heat treatment (including optical annealing) is important because distortion that hinders carrier movement is released by this heat treatment. Note that the timing of performing the heat treatment is not particularly limited as long as it is after the formation of the second In—Ga—Zn—O-based non-single-crystal layer, and may be performed after the formation of the organic insulating layer to be performed later.

次に、酸化物半導体層103を覆う有機絶縁層107を形成する。有機絶縁層107は、

実施の形態1に示す有機絶縁層452に列挙した材料を適宜用いて形成することができる

。Next, an organic insulating

The materials listed for the organic insulating

次に、第5フォトリソグラフィ工程を行ってレジストマスクを形成し、当該レジストマス

クを用いて有機絶縁層107をエッチングして、ドレイン電極105bに達するコンタク

トホール125を形成する。また、ここでのエッチングにより第2端子122に達するコ

ンタクトホール127、接続電極120に達するコンタクトホール126も形成する。ま

た、ここでのエッチングにより、容量部における誘電体をゲート絶縁層102とするため

の開口部124も形成する。この後、レジストマスクを除去する。この段階での断面図を

図6(B)に示す。Next, a fifth photolithography step is performed to form a resist mask, and the organic insulating

次に、有機絶縁層107上に、透明導電層を成膜する。透明導電層の材料としては、酸化

インジウム(In2O3)や酸化インジウム酸化スズ合金(In2O3―SnO2、IT

Oと略記する)などをスパッタリング法や真空蒸着法などを用いて形成する。このような

材料のエッチング処理は塩酸系の溶液により行う。しかし、特にITOのエッチングは残

渣が発生しやすいので、エッチング加工性を改善するために酸化インジウム酸化亜鉛合金

(In2O3―ZnO)を用いても良い。Next, a transparent conductive layer is formed over the organic insulating

(Abbreviated as “O”) or the like using a sputtering method, a vacuum deposition method, or the like. Etching treatment of such a material is performed with a hydrochloric acid based solution. However, in particular, since etching of ITO is likely to generate a residue, an indium oxide-zinc oxide alloy (In2 O3 —ZnO) may be used to improve etching processability.

次に、第6フォトリソグラフィ工程を行ってレジストマスクを形成し、当該レジストマス

クを用いたエッチングにより不要な部分を除去して画素電極110を形成する。Next, a sixth photolithography step is performed to form a resist mask, and unnecessary portions are removed by etching using the resist mask, so that the

また、この第6フォトリソグラフィ工程において、容量部におけるゲート絶縁層102及

び有機絶縁層107を誘電体として、容量配線108と画素電極110とで保持容量が形

成される。In the sixth photolithography step, a storage capacitor is formed by the

また、この第6フォトリソグラフィ工程において、接続電極120及び第2端子122の

上方をレジストマスクで覆い、端子部に形成された透明導電層128、129を残す。透

明導電層128、129は、FPCとの接続に用いられる電極または配線となる。第1端

子121と直接接続された接続電極120上に形成された透明導電層128は、ゲート配

線の入力端子として機能する接続用の端子電極となる。第2端子122上に形成された透

明導電層129は、ソース配線の入力端子として機能する接続用の端子電極である。Further, in the sixth photolithography process, the

次に、レジストマスクを除去する。この段階での断面図を図6(C)に示す。なお、この

段階での上面図が図10に相当する。なお、レジストマスクをウェットエッチングで除去

した場合、大気雰囲気下または窒素雰囲気下で200℃〜600℃の加熱処理を行っても

よい。Next, the resist mask is removed. A cross-sectional view at this stage is illustrated in FIG. Note that a top view at this stage corresponds to FIG. Note that when the resist mask is removed by wet etching, heat treatment at 200 ° C. to 600 ° C. may be performed in an air atmosphere or a nitrogen atmosphere.

また、図11(A1)、図11(A2)は、この段階でのゲート配線端子部の上面図及び

断面図をそれぞれ図示している。図11(A1)は図11(A2)中のC1−C2線に沿

った断面図に相当する。図11(A1)において、有機絶縁層107上に形成される透明

導電層155は、入力端子として機能する接続用の端子電極である。また、図11(A1

)において、ゲート配線端子部では、ゲート配線と同じ材料で形成される第1端子151

と、ソース配線と同じ材料で形成される接続電極153とがゲート絶縁層102を介して

重なり直接接して導通させている。また、接続電極153及び透明導電層155が、有機

絶縁層107に設けられたコンタクトホールにおいて、直接接して導通させている。11A1 and 11A2 are a top view and a cross-sectional view of the gate wiring terminal portion at this stage, respectively. FIG. 11A1 corresponds to a cross-sectional view taken along line C1-C2 in FIG. In FIG. 11A1, the transparent

), The

And the

また、図11(B1)、及び図11(B2)は、ソース配線端子部の上面図及び断面図を

それぞれ図示している。また、図11(B1)は図11(B2)中のD1−D2線に沿っ

た断面図に相当する。図11(B1)において、有機絶縁層107上に形成される透明導

電層155は、入力端子として機能する接続用の端子電極である。また、図11(B1)

において、ソース配線端子部では、ゲート配線と同じ材料で形成される電極156が、ソ

ース配線と電気的に接続される第2端子150の下方にゲート絶縁層102を介して重な

る。ゲート配線と同じ材料で形成される電極156は、第2端子150とは電気的に接続

しておらず、電極156を第2端子150と異なる電位、例えばフローティング、GND

、0Vなどに設定すれば、ノイズ対策のための容量または静電気対策のための容量を形成

することができる。また、第2端子150は、有機絶縁層107に設けられたコンタクト

ホールにおいて、透明導電層155と直接接続している。11B1 and 11B2 are a top view and a cross-sectional view of the source wiring terminal portion, respectively. FIG. 11B1 corresponds to a cross-sectional view taken along line D1-D2 in FIG. In FIG. 11B1, a transparent

In the source wiring terminal portion, an

If set to 0V or the like, it is possible to form a capacitance for noise or a capacitance for static electricity. The

ゲート配線、ソース配線、及び容量配線は画素密度に応じて複数本設けられるものである

。また、端子部においては、ゲート配線と同電位の第1端子、ソース配線と同電位の第2

端子、容量配線と同電位の第3端子などが複数並べられて配置される。それぞれの端子の

数は、それぞれ任意な数で設ければ良いものとし、実施者が適宣決定すれば良い。A plurality of gate wirings, source wirings, and capacitor wirings are provided depending on the pixel density. In the terminal portion, a first terminal having the same potential as the gate wiring and a second terminal having the same potential as the source wiring.

A plurality of terminals, third terminals having the same potential as the capacitor wiring, and the like are arranged. Any number of terminals may be provided, and the practitioner may determine the number appropriately.

こうして6回のフォトリソグラフィ工程により、6枚のフォトマスクを使用して、ボトム

ゲート型のnチャネル型薄膜トランジスタである薄膜トランジスタ170を有する画素薄

膜トランジスタ部、保持容量を完成させることができる。そして、これらを個々の画素に

対応してマトリクス状に配置して画素部を構成することによりアクティブマトリクス型の

表示装置を作製するための一方の基板とすることができる。本明細書では、便宜上このよ

うな基板をアクティブマトリクス基板と呼ぶ。In this manner, the pixel thin film transistor portion including the

アクティブマトリクス型の液晶表示装置を作製する場合には、アクティブマトリクス基板

と、対向電極が設けられた対向基板との間に液晶層を設け、アクティブマトリクス基板と

対向基板とを固定する。なお、対向基板に設けられた対向電極と電気的に接続する共通電

極をアクティブマトリクス基板上に設け、共通電極と電気的に接続する第4端子を端子部

に設ける。この第4端子は、共通電極を固定電位、例えばGND、0Vなどに設定するた

めの端子である。In the case of manufacturing an active matrix liquid crystal display device, a liquid crystal layer is provided between an active matrix substrate and a counter substrate provided with a counter electrode, and the active matrix substrate and the counter substrate are fixed. Note that a common electrode electrically connected to the counter electrode provided on the counter substrate is provided over the active matrix substrate, and a fourth terminal electrically connected to the common electrode is provided in the terminal portion. The fourth terminal is a terminal for setting the common electrode to a fixed potential such as GND or 0V.

また、本実施の形態は、図10の画素構成に限定されず、図10とは異なる上面図の例を

図12に示す。図12では容量配線を設けず、画素電極110と隣り合う画素のゲート配

線とをゲート絶縁層を介して重ねて保持容量を形成する形態であり、この場合、容量配線

及び容量配線と接続する第3端子は省略することができる。また、表示領域に凹部を設け

なくとも、容量素子を形成することができるため、平坦性が高まり、液晶の配向ムラを低

減することができる。なお、図12において、図12と同じ部分には同じ符号を用いて説

明する。Further, this embodiment is not limited to the pixel configuration in FIG. 10, and FIG. 12 shows an example of a top view different from FIG. In FIG. 12, the capacitor wiring is not provided, and the storage capacitor is formed by overlapping the

アクティブマトリクス型の液晶表示装置においては、マトリクス状に配置された画素電極

を駆動することによって、液晶表示装置の画面上に表示パターンが形成される。詳しくは

選択された画素電極と該画素電極に対応する対向電極との間に電圧が印加されることによ

って、画素電極と対向電極との間に配置された液晶層の光学変調が行われ、この光学変調

による光の透過と非透過が表示パターンとして観察者に認識される。In an active matrix liquid crystal display device, a display pattern is formed on a screen of a liquid crystal display device by driving pixel electrodes arranged in a matrix. Specifically, by applying a voltage between the selected pixel electrode and the counter electrode corresponding to the pixel electrode, optical modulation of the liquid crystal layer disposed between the pixel electrode and the counter electrode is performed. The observer recognizes transmission and non-transmission of light by optical modulation as a display pattern.

液晶表示装置の動画表示において、液晶分子自体の応答が遅いため、残像が生じる、また

は動画のぼけが生じるという問題がある。液晶表示装置の動画特性を改善するため、全面

黒表示を1フレームおきに行う、所謂、黒挿入と呼ばれる駆動技術がある。In moving image display of a liquid crystal display device, there is a problem that an afterimage is generated or a moving image is blurred because the response of the liquid crystal molecules themselves is slow. In order to improve the moving image characteristics of a liquid crystal display device, there is a so-called black insertion driving technique in which black display is performed every other frame.

また、垂直同期周波数を通常の1.5倍、好ましくは2倍以上にすることで動画特性を改

善する、所謂、倍速駆動と呼ばれる駆動技術もある。There is also a so-called double speed drive technique that improves the moving image characteristics by setting the vertical synchronization frequency to 1.5 times the normal frequency, preferably 2 times or more.

また、液晶表示装置の動画特性を改善するため、バックライトとして複数のLED(発光

ダイオード)光源または複数のEL光源などを用いて面光源を構成し、面光源を構成して

いる各光源を独立して1フレーム期間内で間欠点灯駆動する駆動技術もある。面光源とし

て、3種類以上のLEDを用いてもよいし、白色発光のLEDを用いてもよい。独立して

複数のLEDを制御できるため、液晶層の光学変調の切り替えタイミングに合わせてLE

Dの発光タイミングを同期させることもできる。この駆動技術は、LEDを部分的に消灯

することができるため、特に一画面を占める黒い表示領域の割合が多い映像表示の場合に

は、消費電力の低減効果が図れる。In addition, in order to improve the moving image characteristics of the liquid crystal display device, a surface light source is configured using a plurality of LED (light emitting diode) light sources or a plurality of EL light sources as a backlight, and each light source constituting the surface light source is independent. There is also a driving technique that performs intermittent lighting driving within one frame period. As the surface light source, three or more kinds of LEDs may be used, or white light emitting LEDs may be used. Since a plurality of LEDs can be controlled independently, the LE is matched to the optical modulation switching timing of the liquid crystal layer.

The light emission timing of D can also be synchronized. Since this driving technique can partially turn off the LED, an effect of reducing power consumption can be achieved particularly in the case of video display in which the ratio of the black display area occupying one screen is large.

これらの駆動技術を組み合わせることによって、液晶表示装置の動画特性などの表示特性

を従来よりも改善することができる。By combining these driving techniques, the display characteristics such as the moving picture characteristics of the liquid crystal display device can be improved as compared with the related art.

本実施の形態で得られるnチャネル型のトランジスタは、酸化物半導体層、代表的にはI

n−Ga−Zn−O系非単結晶層をチャネル形成領域に用いており、更に酸化物半導体層

に接する有機樹脂層を有するため、良好な電気特性を有するため、これらの駆動技術を組

み合わせることができる。An n-channel transistor obtained in this embodiment includes an oxide semiconductor layer, typically I

Since an n-Ga-Zn-O-based non-single-crystal layer is used for a channel formation region and an organic resin layer in contact with the oxide semiconductor layer is included, the device has favorable electrical characteristics; Can do.

また、発光表示装置を作製する場合、有機発光素子の一方の電極(カソードとも呼ぶ)は

、低電源電位、例えばGND、0Vなどに設定するため、端子部に、カソードを低電源電

位、例えばGND、0Vなどに設定するための第4端子が設けられる。また、発光表示装

置を作製する場合には、ソース配線、及びゲート配線に加えて電源供給線を設ける。従っ

て、端子部には、電源供給線と電気的に接続する第5端子を設ける。In the case of manufacturing a light-emitting display device, one electrode (also referred to as a cathode) of an organic light-emitting element is set to a low power supply potential, for example, GND, 0 V, and the like. , A fourth terminal for setting to 0V or the like is provided. In the case of manufacturing a light-emitting display device, a power supply line is provided in addition to a source wiring and a gate wiring. Accordingly, the terminal portion is provided with a fifth terminal that is electrically connected to the power supply line.

ゲート線駆動回路またはソース線駆動回路で酸化物半導体を用いた薄膜トランジスタで形

成することにより、製造コストを低減する。そして駆動回路に用いる薄膜トランジスタの

ゲート電極とソース配線、或いはドレイン配線を直接接続させることでコンタクトホール

の数を少なくし、駆動回路の占有面積を縮小化できる表示装置を提供することができる。By forming the gate line driver circuit or the source line driver circuit with a thin film transistor using an oxide semiconductor, manufacturing cost is reduced. A display device can be provided in which the number of contact holes is reduced by directly connecting a gate electrode of a thin film transistor used for a driver circuit to a source wiring or a drain wiring, and the area occupied by the driver circuit can be reduced.

従って、本実施の形態により、画質が向上した表示装置を低コストで提供することができ

る。Therefore, according to this embodiment, a display device with improved image quality can be provided at low cost.

本実施の形態は実施の形態1乃至実施の形態3と自由に組み合わせることができる。This embodiment mode can be freely combined with any of

(実施の形態5)

本実施の形態では、実施の形態4より少ないフォトマスクで作製可能な、薄膜トランジス

タを含む表示装置の作製工程について、図31乃至図36を用いて説明する。(Embodiment 5)

In this embodiment, a manufacturing process of a display device including a thin film transistor which can be manufactured with fewer photomasks than in Embodiment 4 will be described with reference to FIGS.

図31(A)において、基板100全面に導電層を形成した後、第1フォトリソグラフィ

工程を行って形成したレジストマスクを用いた形成し、エッチングにより不要な部分を除

去して、配線及び電極(ゲート電極101を含むゲート配線、容量配線108、及び第1

端子121)を形成する。この後、レジストマスクを除去するなお、この段階での上面図

が図33に相当する。後に形成される酸化物半導体層、ソース電極層、ドレイン電極層、

画素電極、コンタクトホールは破線で示されている。In FIG. 31A, after a conductive layer is formed over the entire surface of the

Terminal 121) is formed. Thereafter, the resist mask is removed. A top view at this stage corresponds to FIG. Oxide semiconductor layer, source electrode layer, drain electrode layer formed later,

Pixel electrodes and contact holes are indicated by broken lines.

ゲート電極101を含むゲート配線と容量配線108、端子部の第1端子121は、実施

の形態1に示す第1ゲート電極401、第2ゲート電極402の材料を適宜用いて形成す

る。The gate wiring including the

次に、ゲート電極101上にゲート絶縁層102を全面に形成する。ゲート絶縁層102

はスパッタリング法などを用い、厚さを50〜250nmとする。Next, a

Uses a sputtering method or the like, and has a thickness of 50 to 250 nm.

なお、酸化物半導体層を形成する前に、アルゴンガスを導入してプラズマを発生させる逆

スパッタリングを行い、ゲート絶縁層の表面に付着しているゴミを除去することが好まし

い。なお、アルゴン雰囲気に代えて窒素、ヘリウムなどを用いてもよい。また、アルゴン

雰囲気に酸素、水素、N2Oなどを加えた雰囲気で行ってもよい。また、アルゴン雰囲気

にCl2、CF4などを加えた雰囲気で行ってもよい。Note that before the oxide semiconductor layer is formed, it is preferable to perform reverse sputtering in which an argon gas is introduced to generate plasma to remove dust attached to the surface of the gate insulating layer. Note that nitrogen, helium, or the like may be used instead of the argon atmosphere. Alternatively, an atmosphere in which oxygen, hydrogen, N2 O, or the like is added to an argon atmosphere may be used. Alternatively, an atmosphere in which Cl2 , CF4, or the like is added to an argon atmosphere may be used.

次に、ゲート絶縁層102上に、第1酸化物半導体層109(本実施の形態では第1In

−Ga−Zn−O系非単結晶層)を形成する。プラズマ処理後、大気に曝すことなく第1

In−Ga−Zn−O系非単結晶層を形成することは、ゲート絶縁層と第1酸化物半導体

層の界面にゴミや水分を付着させない点で有用である。ここでは、実施の形態4と同様に

、第1In−Ga−Zn−O系非単結晶層を形成する。Next, over the

-Ga-Zn-O-based non-single-crystal layer). After plasma treatment, the first without exposure to the atmosphere

The formation of the In—Ga—Zn—O-based non-single-crystal layer is useful in that dust and moisture are not attached to the interface between the gate insulating layer and the first oxide semiconductor layer. Here, as in Embodiment 4, the first In—Ga—Zn—O-based non-single-crystal layer is formed.

次いで、大気に曝すことなく、第2酸化物半導体層111(本実施の形態では第2In−

Ga−Zn−O系非単結晶層)をスパッタリング法で形成する。ここでは、In2O3:

Ga2O3:ZnO=1:1:1としたターゲットを用い、形成条件は、実施の形態4と

同様に第2In−Ga−Zn−O系非単結晶層を形成する。Next, the second oxide semiconductor layer 111 (in this embodiment, the second In− layer is not exposed to the atmosphere.

Ga—Zn—O-based non-single-crystal layer) is formed by a sputtering method. Here, In2 O3 :

A target with Ga2 O3 : ZnO = 1: 1: 1 is used, and the second In—Ga—Zn—O-based non-single-crystal layer is formed under the same formation conditions as in Embodiment Mode 4.

なお、第1In−Ga−Zn−O系非単結晶層は、第2In−Ga−Zn−O系非単結晶

層の形成条件と異ならせる。Note that the first In—Ga—Zn—O-based non-single-crystal layer is different from the formation conditions of the second In—Ga—Zn—O-based non-single-crystal layer.

次に、第1酸化物半導体層109及び第2酸化物半導体層111上に、金属材料からなる

導電層132をスパッタリング法や真空蒸着法で形成する。ここでは、実施の形態4と同

様に形成する。この段階での上面図を図31(B)に示す。Next, a

次に、第2フォトリソグラフィ工程を行い、レジストマスク133を形成する。本実施の

形態では、レジストマスク133を形成するために多階調(高階調)マスクを用いた露光

を行う例を示す。Next, a second photolithography process is performed to form a resist

ここで、多階調マスク59を用いた露光について、図37を用いて説明する。Here, exposure using the multi-tone mask 59 will be described with reference to FIG.

多階調マスクとは、露光部分、中間露光部分、及び未露光部分に3つの露光レベルを行う

ことが可能なマスクであり、透過した光が複数の強度となる露光マスクである。一度の露

光及び現像工程により、複数(代表的には二種類)の厚さの領域を有するレジストマスク

を形成することが可能である。このため、多階調マスクを用いることで、露光マスクの枚

数を削減することが可能である。A multi-tone mask is a mask capable of performing three exposure levels on an exposed portion, an intermediate exposed portion, and an unexposed portion, and is an exposure mask in which transmitted light has a plurality of intensities. By a single exposure and development process, a resist mask having a plurality of (typically two kinds) of thickness regions can be formed. For this reason, the number of exposure masks can be reduced by using a multi-tone mask.

多階調マスクの代表例としては、図37(A)に示すようなグレートーンマスク59a、

図37(C)に示すようなハーフトーンマスク59bがある。As a representative example of the multi-tone mask, a gray-

There is a

図37(A)に示すように、グレートーンマスク59aは、透光性基板63及びその上に

形成される遮光部64並びに回折格子65で構成される。遮光部64においては、光の透

過率が0%である。一方、回折格子65はスリット、ドット、メッシュ等の光透過部の間

隔を、露光に用いる光の解像度限界以下の間隔とすることにより、光の透過率を制御する

ことができる。なお、回折格子65は、周期的なスリット、ドット、メッシュ、または非

周期的なスリット、ドット、メッシュどちらも用いることができる。As shown in FIG. 37 (A), the

透光性基板63としては、石英等の透光性基板を用いることができる。遮光部64及び回

折格子65は、クロムや酸化クロム等の光を吸収する遮光材料を用いて形成することがで

きる。As the

グレートーンマスク59aに露光光を照射した場合、図30(B)に示すように、遮光部

64においては、光透過率66は0%であり、遮光部64及び回折格子65が設けられて

いない領域では光透過率66は100%である。また、回折格子65においては、10〜

70%の範囲で調整可能である。回折格子65における光の透過率の調整は、回折格子の

スリット、ドット、またはメッシュの間隔及びピッチの調整により可能である。When the gray-

Adjustment is possible within a range of 70%. The light transmittance of the

図37(C)に示すように、ハーフトーンマスク59bは、透光性基板63及びその上に

形成される半透過部67並びに遮光部68で構成される。半透過部167は、MoSiN

、MoSi、MoSiO、MoSiON、CrSiなどを用いることができる。遮光部1

68は、クロムや酸化クロム等の光を吸収する遮光材料を用いて形成することができる。As shown in FIG. 37C, the

MoSi, MoSiO, MoSiON, CrSi, or the like can be used. Shading

68 can be formed using a light-shielding material that absorbs light, such as chromium or chromium oxide.

ハーフトーンマスク59bに露光光を照射した場合、図37(D)に示すように、遮光部

68においては、光透過率69は0%であり、遮光部68及び半透過部167が設けられ

ていない領域では光透過率69は100%である。また、半透過部67においては、10

〜70%の範囲で調整可能である。半透過部67に於ける光の透過率の調整は、半透過部

67の材料により調整により可能である。When the

It can be adjusted within a range of ˜70%. The light transmittance in the

多階調マスクを用いて露光した後、現像することで、図31(C)に示すように厚さの異

なる領域を有するレジストマスク133を形成することができる。By developing after exposure using a multi-tone mask, a resist

次に、レジストマスク133を用いて第1エッチング工程を行い、第1酸化物半導体層1

09、第2酸化物半導体層111、導電層132をエッチングし、島状に加工する。この

結果、第1酸化物半導体層134、第2酸化物半導体層135、導電層136を形成する

ことができる(図31(C)参照。)。なお、この段階での上面図が、図34に相当する

。後に形成されるソース電極層、ドレイン電極層、画素電極、コンタクトホールは破線で

示されている。Next, a first etching step is performed using the resist

09, the second

次に、レジストマスク133をアッシングする。この結果、レジストマスクの面積が縮小

し、厚さが薄くなる。このとき、厚さの薄い領域のレジストマスク(ゲート電極101の

一部と重畳する領域)は除去され、分離されたレジストマスク131を形成することがで

きる(図32(A)参照。)。Next, the resist

レジストマスク131を用いて第1酸化物半導体層134、第2酸化物半導体層135、

導電層136を第2エッチング工程によりエッチングし、それぞれ酸化物半導体層103

、ソース領域及びドレイン領域であるn+層104a、104b、ソース電極又はドレイ

ン電極105a、105bを形成する。なお、酸化物半導体層103は一部のみがエッチ

ングされ、溝部(凹部)を有する酸化物半導体層となり、かつ端部においても、一部エッ

チングされ露出した形状となる。Using the resist

The

Then, n+ layers 104a and 104b which are a source region and a drain region, and source or

本実施の形態では、当該第1エッチング工程及び第2エッチング工程を、ウェットエッチ

ングを用いて行う。しかしながら、第1エッチング工程及び第2エッチング工程を行って

もよい。また、第1エッチング工程及び第2エッチング工程の一方をドライエッチングと

し、他方をウェットエッチングとしてもよい。In the present embodiment, the first etching step and the second etching step are performed using wet etching. However, the first etching step and the second etching step may be performed. One of the first etching step and the second etching step may be dry etching and the other may be wet etching.

第1酸化物半導体層109、第2酸化物半導体層111、導電層132を第1エッチング

工程でウェットエッチングすると、第1酸化物半導体層109、第2酸化物半導体層11

1、導電層132は等方的にエッチングされるため、レジストマスク133の端部と、第

1酸化物半導体層134、第2酸化物半導体層135、導電層136の端部は一致せずよ

り後退し、その端部は曲率を有する形状となる。これにより、上に形成される膜の段切れ

やカバレッジ不良が防止できる。また、ウェットエッチングでは第1の酸化物半導体膜1

09とゲート絶縁層102の選択比を高くとることが容易であり、ゲート絶縁層102の

意図しない薄膜化が防止できる。When the first

1. Since the

It is easy to increase the selection ratio between 09 and the

同様に、第1酸化物半導体層134、第2酸化物半導体層135、導電層136を第2エ

ッチング工程でウェットエッチングすると、第1酸化物半導体層134、第2酸化物半導

体層135、導電層136は等方的にエッチングされるため、レジストマスク131の端

部と、酸化物半導体層103の凹部、n+層104a、104b、ソース電極又はドレイ

ン電極105a、105bの端部は一致せずより後退し、その端部は曲率を有する形状と

なる。この後、レジストマスク131を除去する。これにより、上に形成される膜の段切

れやカバレッジ不良が防止できる。また、ウェットエッチングでは導電層136や第2の

酸化物半導体層135とゲート絶縁層102の選択比を高くとることが容易であり、ゲー

ト絶縁層102の意図しない薄膜化が防止できる。Similarly, when the first

また、ウェットエッチング後のエッチング液はエッチングされた材料とともに洗浄によっ

て除去される。その除去された材料を含むエッチング液の廃液を精製し、含まれる材料を

再利用してもよい。当該エッチング後の廃液から酸化物半導体層に含まれるインジウム等

の材料を回収して再利用することにより、資源を有効活用し低コスト化することができる

。In addition, the etchant after the wet etching is removed by cleaning together with the etched material. The waste solution of the etching solution containing the removed material may be purified and the contained material may be reused. By recovering and reusing materials such as indium contained in the oxide semiconductor layer from the waste liquid after the etching, resources can be effectively used and costs can be reduced.

さらに、露出している酸化物半導体層103のチャネル形成領域に、酸素ラジカル処理を

行ってもよい。酸素ラジカル処理を行うことにより薄膜トランジスタをノーマリーオフと

することができる。また、ラジカル処理を行うことにより、酸化物半導体層103のエッ

チングによるダメージを回復することができる。また、当該プラズマ処理により、ソース

電極105a、ドレイン電極105b、及び第2端子122の端部が湾曲する。Further, oxygen radical treatment may be performed on the exposed channel formation region of the

次に、200℃〜600℃、代表的には300℃〜500℃の熱処理を行うことが好まし

い。なお、熱処理を行うタイミングは、第2In−Ga−Zn−O系非単結晶層の形成後

であれば特に限定されず、例えば画素電極形成後に行ってもよい。Next, it is preferable to perform heat treatment at 200 ° C. to 600 ° C., typically 300 ° C. to 500 ° C. Note that the timing for performing the heat treatment is not particularly limited as long as it is after the formation of the second In—Ga—Zn—O-based non-single-crystal layer, and for example, the heat treatment may be performed after the pixel electrode is formed.

以上の工程により、酸化物半導体層103をチャネル形成領域とする薄膜トランジスタ1

70を作製することができる。この段階での断面図を図32(A)に示した。なお、この

段階での上面図が図35に相当する。後に形成される画素電極、コンタクトホールは破線

で示されている。Through the above process, the

70 can be made. A cross-sectional view at this stage is illustrated in FIG. Note that a top view at this stage corresponds to FIG. Pixel electrodes and contact holes to be formed later are indicated by broken lines.

また、第2エッチング工程において、酸化物半導体層103と同じ材料である端子層13

9、n+層104a、104bと同じ材料である端子層140、ソース電極又はドレイン

電極105a、105bと同じ材料である第2端子122を端子部に残す。なお、第2端

子122はソース配線(ソース電極又はドレイン電極105a、105bを含むソース配

線)と電気的に接続されている。In the second etching step, the terminal layer 13 which is the same material as the

9. The

多階調マスクにより形成した複数(代表的には二種類)の厚さの領域を有するレジストマ

スクを用いると、レジストマスクの数を減らすことができるため、工程簡略化、低コスト

化が図れる。When a resist mask having a plurality of (typically two kinds) of thickness regions formed using a multi-tone mask is used, the number of resist masks can be reduced, so that the process can be simplified and costs can be reduced.

次に、酸化物半導体層103を覆う有機絶縁層107を形成する。有機絶縁層107は、

実施の形態1に示す有機絶縁層452に列挙した材料を適宜用いて形成することができる

。Next, an organic insulating

The materials listed for the organic insulating

次に、第3フォトリソグラフィ工程を行ってレジストマスクを形成し、当該レジストマス

クを用いて有機絶縁層107をエッチングして、ドレイン電極105bに達するコンタク

トホール125を形成する。また、第2端子122に達するコンタクトホール127、第

2端子121に達するコンタクトホール126も形成する。また、ここでのエッチングに

より、容量部における誘電体をゲート絶縁層102とするための開口部124も形成する

。この後、レジストマスクを除去する。この段階での断面図を図32(B)に示す。Next, a third photolithography step is performed to form a resist mask, and the organic insulating

次に、有機絶縁層107上に、実施の形態4と同様に、透明導電層を形成する。Next, a transparent conductive layer is formed on the organic insulating

次に、第4フォトリソグラフィ工程を行ってレジストマスクを形成し、当該レジストマス