CN1722810A - A digital camera real-time acquisition system - Google Patents

A digital camera real-time acquisition systemDownload PDFInfo

- Publication number

- CN1722810A CN1722810ACN 200510082734CN200510082734ACN1722810ACN 1722810 ACN1722810 ACN 1722810ACN 200510082734CN200510082734CN 200510082734CN 200510082734 ACN200510082734 ACN 200510082734ACN 1722810 ACN1722810 ACN 1722810A

- Authority

- CN

- China

- Prior art keywords

- data

- digital camera

- pci

- computer

- real

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 230000005540biological transmissionEffects0.000claimsabstractdescription18

- 238000012545processingMethods0.000claimsabstractdescription16

- 238000006243chemical reactionMethods0.000claimsdescription10

- 238000003860storageMethods0.000claimsdescription6

- 230000001360synchronised effectEffects0.000claimsdescription6

- 239000000872bufferSubstances0.000claimsdescription4

- 230000001960triggered effectEffects0.000claimsdescription2

- 230000010354integrationEffects0.000claims2

- 238000012546transferMethods0.000abstractdescription3

- 230000000630rising effectEffects0.000description4

- 230000006870functionEffects0.000description3

- 238000000034methodMethods0.000description3

- 238000013461designMethods0.000description2

- 238000010586diagramMethods0.000description2

- 230000000694effectsEffects0.000description2

- 238000012986modificationMethods0.000description2

- 230000004048modificationEffects0.000description2

- 230000008569processEffects0.000description2

- 238000011160researchMethods0.000description2

- FGRBYDKOBBBPOI-UHFFFAOYSA-N10,10-dioxo-2-[4-(N-phenylanilino)phenyl]thioxanthen-9-oneChemical compoundO=C1c2ccccc2S(=O)(=O)c2ccc(cc12)-c1ccc(cc1)N(c1ccccc1)c1ccccc1FGRBYDKOBBBPOI-UHFFFAOYSA-N0.000description1

- 230000008859changeEffects0.000description1

- 239000000470constituentSubstances0.000description1

- 238000013500data storageMethods0.000description1

- 238000001514detection methodMethods0.000description1

- 238000009776industrial productionMethods0.000description1

- 230000007246mechanismEffects0.000description1

- 238000012544monitoring processMethods0.000description1

- 230000002093peripheral effectEffects0.000description1

- 230000004044responseEffects0.000description1

- 239000004065semiconductorSubstances0.000description1

- 238000004088simulationMethods0.000description1

- 230000000007visual effectEffects0.000description1

Images

Landscapes

- Studio Devices (AREA)

Abstract

Translated fromChineseDescription

Translated fromChinese技术领域technical field

本发明属于数据传输与处理技术领域,尤其涉及数字相机中图像数据的实时采集系统。The invention belongs to the technical field of data transmission and processing, in particular to a real-time collection system of image data in a digital camera.

背景技术Background technique

随着各种新型数字相机的不断出现,数字相机越来越多地成为实时数据采集、图形图像处理、遥感监测、自动检测等系统中的探测器,广泛应用于民用、商业、工业、医疗、科研等诸多领域。但与此同时,数字相机的海量数据输出也对数据采集系统的采集速度提出了更高的要求。With the continuous emergence of various new digital cameras, digital cameras have increasingly become detectors in systems such as real-time data acquisition, image processing, remote sensing monitoring, and automatic detection, and are widely used in civil, commercial, industrial, medical, scientific research and many other fields. But at the same time, the massive data output of the digital camera also puts forward higher requirements on the acquisition speed of the data acquisition system.

目前,市场上的图像采集卡大多只能用于一些低速场合,对低分辨率相机进行图像采集,而且实时性差,在图像帧率及分辨率要求比较高的场合下,无法获得令人满意的效果。因此急需设计一种高效的数字相机实时采集系统,实现对高精度相机数据的高速采集和传输,满足现代工业生产、生活以及科学研究中日益增长的高速、高精度的数据采集要求。At present, most of the image acquisition cards on the market can only be used in some low-speed occasions to collect images from low-resolution cameras, and the real-time performance is poor. In the occasions where the image frame rate and resolution requirements are relatively high, satisfactory results cannot be obtained. Effect. Therefore, it is urgent to design an efficient digital camera real-time acquisition system to realize high-speed acquisition and transmission of high-precision camera data, and to meet the increasing high-speed and high-precision data acquisition requirements in modern industrial production, life and scientific research.

发明内容Contents of the invention

为了克服现有的图像采集卡分辨率较低、传输速率较低的缺点,本发明提供了一种数字相机实时采集系统,它可以实现对高分辨率(1024×768)、高帧率(30fps)的数字图像的实时采集、显示和存储,速率可以达到480Mbps。In order to overcome the disadvantages of low resolution and low transmission rate of existing image acquisition cards, the invention provides a real-time acquisition system for digital cameras, which can realize high resolution (1024*768), high frame rate (30fps ) real-time collection, display and storage of digital images, the rate can reach 480Mbps.

本发明提供的数字相机实时采集系统,包括计算机、插在所述计算机PCI插槽上的PCI图像采集卡,以及通过数据总线与所述PCI图像采集卡连接的数字相机:The digital camera real-time acquisition system provided by the present invention includes a computer, a PCI image acquisition card inserted in the PCI slot of the computer, and a digital camera connected to the PCI image acquisition card by a data bus:

所述PCI图像采集卡实现了数字相机到计算机的高速数据采集和传输,具体包括CPLD逻辑控制芯片、高速缓存、PCI接口芯片及其配置E2PROM;The PCI image acquisition card realizes the high-speed data acquisition and transmission from the digital camera to the computer, and specifically includes a CPLD logic control chip, a cache memory, a PCI interface chip and configuration E2 PROM thereof;

所述数字相机通过数据总线和控制线与CPLD逻辑控制芯片相连;所述CPLD逻辑控制芯片分别与所述高速缓存和PCI接口芯片相连;所述配置E2PROM与PCI接口芯片相连;所述PCI接口芯片通过PCI总线与计算机相连接;Described digital camera links to each other with CPLD logic control chip by data bus and control line; Described CPLD logic control chip links to each other with described cache memory and PCI interface chip respectively; Described configuration E2 PROM links to each other with PCI interface chip; Described PCI The interface chip is connected to the computer through the PCI bus;

所述CPLD逻辑控制芯片通过控制线实现计算机对数字相机的同步控制,由CPLD逻辑控制芯片输出一个宽度由计算机给出的触发信号来触发数字相机开始积分、采集并输出图像数据;The CPLD logic control chip realizes the synchronous control of the computer to the digital camera through the control line, and the CPLD logic control chip outputs a trigger signal whose width is given by the computer to trigger the digital camera to start integrating, collecting and outputting image data;

所述CPLD逻辑控制芯片对数字相机采集到的图像数据首先进行整合处理,将数据变换成为32bit数据格式并实时存储在所述高速缓存中,然后等待高速缓存半满时,将存储在所述高速缓存中的数据实时读出到PCI接口芯片,经由PCI总线送入计算机;The CPLD logic control chip first integrates the image data collected by the digital camera, converts the data into a 32bit data format and stores it in the high-speed cache in real time, and then waits for the cache to be half full, then stores it in the high-speed cache. The data in the cache is read out to the PCI interface chip in real time, and sent to the computer via the PCI bus;

所述CPLD逻辑控制芯片控制高速缓存在每帧数据的开头置高速缓存复位,同时设置“可编程快满”偏移量和“可编程快空”偏移量,然后等待数字相机发来的行同步信号由低变高,开始保存一行有效数据,从而保证高速缓存中数据始终是从一帧图像的帧头开始,不会造成图像错位,并保证高速缓存不会因溢出而造成象素数据丢失;The CPLD logic control chip controls the cache to reset the cache at the beginning of each frame of data, set the "programmable almost full" offset and the "programmable fast empty" offset at the same time, and then wait for the row sent by the digital camera The synchronization signal changes from low to high, and starts to save a line of valid data, so as to ensure that the data in the cache always starts from the frame header of a frame of image, which will not cause image misalignment, and ensure that the cache will not cause pixel data loss due to overflow ;

所述CPLD逻辑控制芯片通过读取高速缓存的状态到计算机,来确定对所述高速缓存进行相应的读出或写入操作。The CPLD logic control chip determines to perform a corresponding read or write operation on the cache by reading the state of the cache to the computer.

在本发明中,所述数字相机输出的若是LVDS格式的数据,则所述PCI图像采集卡还设有驱动转换接口,将所述数字相机输出的LVDS格式的数据转换成TTL格式的数据后再输出给CPLD逻辑控制芯片进行处理。In the present invention, if the output of the digital camera is data in the LVDS format, the PCI image acquisition card is also provided with a drive conversion interface, and the data in the LVDS format output by the digital camera is converted into data in the TTL format. Output to the CPLD logic control chip for processing.

在本发明中,所述高速缓存采用高速同步先进先出缓存器(FIFO),以保证数据的高速存取。In the present invention, the high-speed cache adopts a high-speed synchronous first-in-first-out buffer (FIFO) to ensure high-speed access of data.

在本发明中,所述计算机用来控制CPLD逻辑控制芯片对数字相机进行单帧图像捕获、将单帧图像数据实时显示在计算机显示器上、将单帧图像数据实时保存到计算机硬盘中、对所述数字相机进行连续时间的图像采集、在计算机显示器上实时显示连续图像数据、将连续图像数据实时保存到计算机硬盘中、实时读取所述高速缓存的状态、实时置高速缓存复位。In the present invention, the computer is used to control the CPLD logic control chip to capture a single-frame image of the digital camera, display the single-frame image data on the computer monitor in real time, save the single-frame image data to the hard disk of the computer in real time, The digital camera performs continuous image acquisition, displays continuous image data on a computer monitor in real time, saves continuous image data to a computer hard disk in real time, reads the state of the cache in real time, and resets the cache in real time.

本发明解决了目前图像采集卡对于数字相机的海量数据输出无法实现实时采集与传输的难题,系统具有以下特点:采集速率高、实时性能好;操作简单、使用方便;工作稳定、可靠。而且,系统具有广泛的应用前景,只需稍作改动即可用于其它信号的采集处理。The invention solves the problem that the current image acquisition card cannot realize real-time acquisition and transmission for massive data output of digital cameras, and the system has the following characteristics: high acquisition rate, good real-time performance; simple operation, convenient use; stable and reliable work. Moreover, the system has wide application prospects, and can be used for acquisition and processing of other signals only with a slight modification.

附图说明Description of drawings

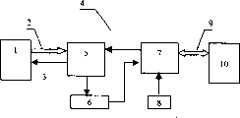

图1是数字相机实时采集系统的第一个实施例的系统结构图,其中各数字标识说明如下:

图2是数字相机实时采集系统的第二个实施例的系统结构图,其中各数字标识说明如下:Fig. 2 is the system structural diagram of the second embodiment of digital camera real-time acquisition system, wherein each digital identification is described as follows:

图3是计算机中的软件程序流程图。Figure 3 is a flow chart of the software program in the computer.

图4是数字相机实时采集系统的工作流程图。Fig. 4 is the working flowchart of the digital camera real-time acquisition system.

具体实施方式Detailed ways

下面结合附图和实施例来进一步说明本发明。The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

图1显示了本发明所述的数字相机实时采集系统的第一个实施例,此实施例是为一般的输出为TTL格式数据的数字相机而设计的,包括:数字相机1、数据总线2、控制线3、PCI图像采集卡4、PCI总线9、计算机10。其中,PCI图像采集卡4是一块集成了多种芯片和接口的印刷电路板卡,它由CPLD逻辑控制芯片(简称CPLD)5、高速缓存6、PCI接口芯片7和配置E2PROM8共同组成。Fig. 1 has shown the first embodiment of the digital camera real-time acquisition system of the present invention, and this embodiment is designed for the digital camera that general output is TTL format data, comprises:

PCI图像采集卡4直接插在计算机10的PCI插槽上;数字相机1与PCI图像采集卡4由数据总线2和控制线3连接:数字相机1通过数据总线2将拍摄到的图像数据送给PCI图像采集卡4,PCI图像采集卡4通过控制线3发送触发脉冲给数字相机1,控制数字相机1开始积分采集数据;PCI图像采集卡4在CPLD逻辑控制芯片5的控制下实时采集、整理相机数据并送给计算机10;计算机10通过设备驱动程序实现与PCI图像采集卡4的软件接口,通过应用程序实现实时显示、实时存盘等操作。The PCI

PCI图像采集卡4内部各芯片连接关系如下:数字相机1通过数据总线2与CPLD 5相连;CPLD5与高速缓存6相连,也与PCI接口芯片7相连;高速缓存6与PCI接口芯片7相连接;配置E2PROM8与PCI接口芯片7相连;最后,PCI接口芯片7通过PCI总线9与计算机10相连接。The connection relationship of each chip in the PCI

在第一个实施例中,数字相机1采用输出为TTL格式的普通数字相机,数字相机1输出的数据可以直接送入CPLD 5处理。In the first embodiment, the

图2显示了本发明所述的数字相机实时采集系统的第二个实施例,此实施例是为输出为LVDS(全称:Low Voltage Differential Signal)格式数据的数字相机而设计的,其组成部件与第一个实施例基本相同,只是在第一个实施例的基础上,PCI图像采集卡4中还增加了驱动转换接口11。Fig. 2 has shown the second embodiment of the digital camera real-time acquisition system of the present invention, and this embodiment is designed for the digital camera outputting as LVDS (full name: Low Voltage Differential Signal) format data, and its constituent parts and The first embodiment is basically the same, except that on the basis of the first embodiment, a

在第二个实施例中数字相机1输出的是LVDS格式的数据,因此PCI图像采集卡4中设有驱动转换接口11,如采用LVDS接口转换芯片DS90C32,将数字相机1输出的LVDS数据转换成适合CPLD 5处理的TTL信号后,再送到CPLD 5进行处理。In the second embodiment, what

PCI图像采集卡4是整个数字相机实时采集系统中的核心部分,它的功能是实现数字相机1与计算机10之间的数据的高速采集和传输。PCI图像采集卡4直接插在计算机10的PCI插槽上,由计算机10通过PCI总线9为其供电。其各部分的具体实施如下:The PCI

PCI接口芯片7与PCI总线9的信号一一对应,它们之间的接口只需将对应信号相连即PCI图像采集卡4直接插在计算机10的PCI插槽上即可,因此,设计时主要考虑PCI接口芯片局部总线的工作方式,在上述两个实施例中,PCI接口芯片均选用了通用的PCI接口芯片-PCI9054。在实施例中,PCI9054的工作时钟为33MHz,其局部总线采用数据和地址非复用的C模式,总线宽度为32位,从本地地址空间映射到PCI存储器空间的空间大小为4MB;PCI9054采用直接存储访问(DMA)工作方式,既是PCI总线的主控制器,又是局部总线的主控制器,利用其主控功能,通过DMA突发传输模式将数字相机数据传送到计算机中。PCI9054与局部总线通过地址线、数据线、控制信号线连接。这部分属于PCI图像采集卡内部电路,已经在印刷电路板上连接好。The

两个实施例均采用IDT公司生产的高速同步FIFO IDT72V251作为高速缓存(简称FIFO),由于IDT72V251输入/输出端口宽度只有9bit,而PCI总线宽度为32bit,为此,实施例中采用4个IDT72V251,每个IDT72V251使用其8个输入/输出端口,并行构成32bit的外部FIFO,与PCI9054的32位数据总线进行通信。该FIFO具有标准的“满”标志位(FF)、“空”标志位(EF),可禁止数据继续写入或读出;同时,还有“可编程的快满”标志(PAF)以及“可编程的快空”标志(PAE),系统根据这些标志位来控制对FIFO的读写操作。在WEN有效时,在WCLK的每一个上升沿,FIFO会把输入数据线上的数据存入内部存储器。同样,在REN有效,并且输出允许OE有效时,在RCLK的每一个上升沿,FIFO会把内部存储器中的数据输出到输出数据线上。Two embodiments all adopt the high-speed synchronous FIFO IDT72V251 that IDT Company produces as high-speed cache (referred to as FIFO), because IDT72V251 input/output port width has only 9bit, and PCI bus width is 32bit, for this reason, adopt 4 IDT72V251 in the embodiment, Each IDT72V251 uses its 8 input/output ports to form a 32-bit external FIFO in parallel to communicate with the 32-bit data bus of PCI9054. The FIFO has a standard "full" flag (FF) and an "empty" flag (EF), which can prohibit data from being written or read; at the same time, there are also "programmable almost full" flags (PAF) and " Programmable "fast empty" flag (PAE), the system controls the read and write operations to FIFO according to these flag bits. When WEN is valid, at each rising edge of WCLK, FIFO will store the data on the input data line into the internal memory. Similarly, when REN is valid and the output allows OE to be valid, at each rising edge of RCLK, the FIFO will output the data in the internal memory to the output data line.

CPLD 5是整个PCI图像采集卡的核心,它实现了对数字相机1的控制、对高速缓存6的控制、对PCI接口芯片7的应答以及这三者之间的逻辑协调工作。两个实施例均采用ALTERA公司的EPM7192作为逻辑控制芯片,其内部逻辑控制功能采用硬件编程语言Verilog来编程实现,利用ALTERA公司的MaxPlusII软件进行逻辑设计、调试和仿真。

配置E2PROM8是PCI接口芯片7的配置芯片,选用美国国家半导体公司的串行E2PROM 93C56,用于在系统加电时配置PCI9054,主要配置了厂家标识、设备标识以及本地总线的基地址空间、I/O空间、中断控制信号等等信息。配置信息预先烧入E2PROM中,上电后PCI9054将依次读取E2PROM的内容来初始化内部寄存器。Configuration E2 PROM8 is the configuration chip of

PCI总线9是计算机中央处理器与高速外围设备之间互连的纽带,它支持高数据传输率,可以在33M主频、32位数据总线的条件下达到峰值132MB/s的带宽,且可扩展为64位,是当今PC领域中的主流总线。

计算机10是数字相机图像数据的接收终端,它为整个采集系统提供终端显示设备、数据存储设备等硬件设备,同时也为数字相机的图像数据最终与用户见面提供了软件实现。软件部分主要包括底层的设备驱动程序和上层的应用程序。设备驱动程序提供了计算机连接到PCI板卡的软件接口,它主要完成以下了工作:对设备的初始化、对端口的读写操作、对中断的处理、对内存的访问、对DMA的处理等,可以根据Windows驱动程序模型(WDM)来设计。应用程序可以采用Visual C++6.0进行开发,它提供了良好的用户界面,用户可以方便地对数字相机图像进行单帧采集、连续采集、实时显示、实时存盘等操作。The

计算机中软件部分的工作流程如图3所示,计算机启动后,操作系统首先检测是否存在PCI设备,如果不存在,则不加载驱动程序。如果操作系统检测到存在PCI设备,则为PCI设备加载驱动程序,初始化PCI设备,配置PCI9054,为DMA分配内存缓冲区等,为数字相机数据的实时采集工作做好准备,DMA操作准备就绪。计算机开始实时采集数字相机图像数据时,先判断向计算机发来的数据是否是新一帧数据,如果不是,则不断循环等待,一直等到有新一帧数据到来,从一帧的开头将数据写入FIFO,这样保证了FIFO中数据始终都是从一帧图像的帧头开始的,不会造成图像错位。一直向FIFO中写数据,直到FIFO半满的时候,开始DMA传输,将FIFO中数据读出,直接送至计算机内存,这样,数字相机的图像数据连续不断地写入FIFO,而FIFO中的图像数据又以DMA方式高速实时地送入计算机,实现了数字相机数据的实时采集。而且可根据实际的需要,对相机图像数据进行实时显示或实时存储。对相机数据的实时采集工作将连续进行,直至用户选择退出。The workflow of the software part in the computer is shown in Figure 3. After the computer is started, the operating system first detects whether there is a PCI device, and if it does not exist, the driver is not loaded. If the operating system detects that there is a PCI device, it loads the driver for the PCI device, initializes the PCI device, configures the PCI9054, allocates memory buffers for the DMA, etc., and prepares for the real-time acquisition of digital camera data, and the DMA operation is ready. When the computer starts to collect digital camera image data in real time, it first judges whether the data sent to the computer is a new frame of data, if not, it waits in a loop until a new frame of data arrives, and writes the data from the beginning of a frame Into the FIFO, which ensures that the data in the FIFO always starts from the frame header of a frame of image, and will not cause image misalignment. Write data to the FIFO until the FIFO is half full, start DMA transmission, read the data in the FIFO, and send it directly to the computer memory, so that the image data of the digital camera is continuously written into the FIFO, and the image in the FIFO The data is sent to the computer in high-speed and real-time by DMA, which realizes the real-time collection of digital camera data. Moreover, the camera image data can be displayed or stored in real time according to actual needs. The real-time collection of camera data will continue until the user chooses to exit.

下面以第二个实施例为例详细说明本发明的工作过程,第一个实施例只是少了驱动转换接口11进行电平转换处理的部分,其工作机理与第二个实施例均相同,整个系统的工作流程图如图4所示。The following takes the second embodiment as an example to describe the working process of the present invention in detail. The first embodiment only lacks the part that drives the

整个系统可以实现以下操作:实时读相机数据、读FIFO状态以及写FIFO复位。The whole system can realize the following operations: read camera data in real time, read FIFO status and write FIFO reset.

1.实时读数字相机1的图像数据。1. Read the image data of the

计算机10在实时读取数字相机1的数据的同时,也实现了对数字相机1的同步控制。由计算机10给出脉冲宽度值,经过PCI总线9和PCI接口芯片7送到CPLD5,CPLD5根据这个脉冲宽度值输出相应宽度的触发脉冲,由控制线3发给数字相机1,触发数字相机1开始积分、采集图像,输出图像数据、行同步、帧同步以及时钟信号。While the

数字相机1将采集到的图像数据(包括同步信号)送到PCI图像采集卡4,PCI图像采集卡4收到数据后,首先经过驱动转换接口11进行电平转换处理,处理后的数据送到CPLD5处进行整合处理,将数据变换成为适合于PCI总线9传输的32bit的数据格式并实时存储在FIFO6中,等待FIFO达到半满状态后,将数据以DMA的方式实时地送入计算机,实现对数字相机数据的实时采集。具体操作如下:

CPLD5首先要对数字相机发来的数据进行判断“是否是新一帧图像的开头”,如果是,CPLD5就置FIFO6复位,同时设置“可编程快满”偏移量和“可编程快空”偏移量,这就保证了在接收一帧数据的过程中高速缓存不会溢出,从而不会有丢象素的现象发生。然后等待图像的行同步信号由低变高,这时开始传输一行有效数据,CPLD5将每两个象元的数据整合成一组32bit的数据,放到FIFO6的输入数据线上,同时设定FIFO6的写允许信号WEN有效,并给出WCLK信号,在WCLK信号的上升沿把FIFO6输入数据线上的数据写入FIFO6中。CPLD5 first needs to judge "whether it is the beginning of a new frame image" on the data sent by the digital camera, if so, CPLD5 resets FIFO6, and sets the "programmable fast full" offset and "programmable fast empty" at the same time Offset, which ensures that the cache will not overflow during the process of receiving a frame of data, so that no pixel loss will occur. Then wait for the line synchronization signal of the image to change from low to high, and then start to transmit one line of valid data. CPLD5 integrates the data of each two pixels into a group of 32bit data, puts it on the input data line of FIFO6, and sets the data of FIFO6 at the same time The write permission signal WEN is effective, and the WCLK signal is given, and the data on the FIFO6 input data line is written into FIFO6 at the rising edge of the WCLK signal.

向FIFO中写数据写到半满的时候,开始DMA传输,从FIFO6中读出数据,直接送至计算机内存。读FIFO6中数据到计算机10时,CPLD5置FIFO6的读允许信号REN有效,输出允许信号OE有效,同时给出RCLK,在RCLK的每一个上升沿,FIFO6会把内部存储器中的数据顺序输出到PCI接口芯7片的数据线上,经由PCI总线9,将数字相机的图像数据送入计算机10的内存缓冲区,最后可根据实际需要,对相机图像数据进行单帧采集、连续采集或实时显示在计算机屏幕上。When writing data to FIFO and writing to half full, start DMA transmission, read data from FIFO6, send directly to computer memory. When reading the data in FIFO6 to the

以上向FIFO中写数据和读FIFO数据是同时进行的,一旦DMA传输开始后,数字相机的图像数据就连续不断地写入FIFO,而FIFO中的图像数据又以DMA方式实时地送入计算机,实现数字相机数据的实时采集。这里置WEN信号有效与否要受FIFO6的满信号(FF)控制,只有在FIFO6不满的情况下才允许数据写入;RCLK信号的给出与否要受FIFO6空信号(EF)的控制,只有在FIFO6非空的情况下才能将其中数据读出。当本行的数据传输完毕时,行同步信号就变低,CPLD5将等待行同步信号再次变高,即下一行有效数据到来时再开始对下一行象元数据进行同样的操作。当帧同步信号和行同步信号都变低时,表示一帧图像数据已经传输完毕。The above writing data to FIFO and reading FIFO data are carried out at the same time. Once the DMA transfer starts, the image data of the digital camera is continuously written into FIFO, and the image data in FIFO is sent to the computer in real time by DMA. Realize the real-time collection of digital camera data. Whether the WEN signal is valid or not is controlled by the full signal (FF) of FIFO6, and data writing is allowed only when FIFO6 is not full; whether the RCLK signal is given or not is controlled by the empty signal (EF) of FIFO6, only Only when FIFO6 is not empty can the data be read out. When the data transmission of this line is completed, the line synchronization signal becomes low, and the CPLD5 will wait for the line synchronization signal to become high again, that is, when the next line of valid data arrives, the same operation will be performed on the next line of pixel data. When both the frame synchronization signal and the line synchronization signal become low, it means that a frame of image data has been transmitted.

计算机10通过CPLD5,可以不断向数字相机1发送宽度由计算机10指定的触发脉冲,来触发数字相机1不断积分、采集图像,数字相机不断地输出图像数据、行同步、帧同步以及时钟信号,速率可达以30fps,这样,由计算机10同步控制数字相机1,实现了数字相机图像连续采集并传输的效果。等到帧同步信号再次变高时,CPLD5就如上所述开始采集下一帧图像。The

2.计算机10除了进行读相机数据的操作外,还可以读FIFO6的状态到计算机10,来决定对所述FIFO进行正确的操作。这时,CPLD5直接将此时FIFO6的四个状态(FULL、Almost FULL、EMPTY、Almost EMPTY)发送给PCI接口芯片7,经由PCI总线9送入计算机10。2. In addition to the operation of reading camera data, the

3.若计算机10要写FIFO6复位,则计算机10发出一个FIFO复位指令,经过PCI总线9和PCI接口芯片7到CPLD5,由CPLD5发出一个复位脉冲到FIFO6,使高速缓存FIFO6回到复位状态。3. reset if

整个系统采用了高速PCI接口芯片,结合CPLD灵活的现场可更改性、可再配置能力,成功实现了数字相机到计算机的海量数据实时传输、显示和存储,采集速率可达480Mbps。系统具有采集速率高、实时性能好,操作简单、使用方便,工作稳定可靠等特点,用户可以方便地对数字相机进行单帧图像实时捕获、单帧图像数据实时显示、单帧图像数据实时保存、连续帧图像实时采集、连续帧图像实时显示、连续帧图像实时保存、实时读取图像采集卡中FIFO状态、实时置图像采集卡中FIFO复位。系统在数字图像采集及传输方面取得了积极的成果,而且,本系统具有广泛的应用前景,只需稍作改动即可用于其它信号的采集处理。The whole system uses a high-speed PCI interface chip, combined with the flexible on-site changeability and reconfigurability of CPLD, successfully realizes the real-time transmission, display and storage of massive data from the digital camera to the computer, and the acquisition rate can reach 480Mbps. The system has the characteristics of high acquisition rate, good real-time performance, simple operation, convenient use, stable and reliable work, etc. Users can conveniently capture single-frame images in real time, display single-frame image data in real time, save single-frame image data in real time, Real-time acquisition of continuous frame images, real-time display of continuous frame images, real-time storage of continuous frame images, real-time reading of FIFO status in the image acquisition card, real-time reset of FIFO in the image acquisition card. The system has achieved positive results in digital image acquisition and transmission. Moreover, this system has a wide application prospect and can be used for acquisition and processing of other signals with only a slight modification.

Claims (4)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CNB200510082734XACN100361523C (en) | 2005-07-11 | 2005-07-11 | A digital camera real-time acquisition system |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CNB200510082734XACN100361523C (en) | 2005-07-11 | 2005-07-11 | A digital camera real-time acquisition system |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1722810Atrue CN1722810A (en) | 2006-01-18 |

| CN100361523C CN100361523C (en) | 2008-01-09 |

Family

ID=35912720

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB200510082734XAExpired - Fee RelatedCN100361523C (en) | 2005-07-11 | 2005-07-11 | A digital camera real-time acquisition system |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN100361523C (en) |

Cited By (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102098441A (en)* | 2010-12-16 | 2011-06-15 | 深圳市经纬科技有限公司 | Image data transmission method and photographic equipment based on serial peripheral interface (SPI) |

| CN102307280A (en)* | 2011-09-14 | 2012-01-04 | 苏州百滨电子科技有限公司 | Method and apparatus of trigger detection for image acquisition applied for high speed digital camera device |

| CN103475871A (en)* | 2013-09-23 | 2013-12-25 | 合肥君达高科信息技术有限公司 | High-speed camera system with punctual data transmission function |

| CN104426851A (en)* | 2013-08-23 | 2015-03-18 | 北大方正集团有限公司 | Image signal transmission system and method |

| CN104902207A (en)* | 2015-06-17 | 2015-09-09 | 四川特伦特科技股份有限公司 | High speed signal collection method |

| CN105578042A (en)* | 2015-12-18 | 2016-05-11 | 深圳市金立通信设备有限公司 | Image data transmission method and terminal |

| CN107809635A (en)* | 2011-11-14 | 2018-03-16 | 深圳迈辽技术转移中心有限公司 | Information carrying means |

| CN108989605A (en)* | 2018-07-27 | 2018-12-11 | 湖南科技大学 | A kind of image capturing and transmitting system and method |

| CN111193873A (en)* | 2019-12-25 | 2020-05-22 | 新大陆数字技术股份有限公司 | Image rapid dimming system and method |

| CN111526317A (en)* | 2020-04-20 | 2020-08-11 | 武汉卓目科技有限公司 | Low-delay image acquisition method, device and system |

| WO2023124768A1 (en)* | 2021-12-29 | 2023-07-06 | 杭州海康机器人股份有限公司 | Image capture card, image capture method, and image capture system |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6025854A (en)* | 1997-12-31 | 2000-02-15 | Cognex Corporation | Method and apparatus for high speed image acquisition |

| US6720968B1 (en)* | 1998-12-11 | 2004-04-13 | National Instruments Corporation | Video acquisition system including a virtual dual ported memory with adaptive bandwidth allocation |

| JP2004221809A (en)* | 2003-01-14 | 2004-08-05 | Fuji Xerox Co Ltd | Image forming apparatus, connection device used for image forming apparatus, and program |

| CN2671031Y (en)* | 2003-12-24 | 2005-01-12 | 宝山钢铁股份有限公司 | Image collector of infrared thermal imaging system in high-temperature state |

- 2005

- 2005-07-11CNCNB200510082734XApatent/CN100361523C/ennot_activeExpired - Fee Related

Cited By (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102098441A (en)* | 2010-12-16 | 2011-06-15 | 深圳市经纬科技有限公司 | Image data transmission method and photographic equipment based on serial peripheral interface (SPI) |

| CN102098441B (en)* | 2010-12-16 | 2016-09-07 | 深圳市经纬科技有限公司 | Image data transfer method based on SPI interface and camera installation |

| CN102307280A (en)* | 2011-09-14 | 2012-01-04 | 苏州百滨电子科技有限公司 | Method and apparatus of trigger detection for image acquisition applied for high speed digital camera device |

| CN107809635A (en)* | 2011-11-14 | 2018-03-16 | 深圳迈辽技术转移中心有限公司 | Information carrying means |

| CN104426851A (en)* | 2013-08-23 | 2015-03-18 | 北大方正集团有限公司 | Image signal transmission system and method |

| CN103475871B (en)* | 2013-09-23 | 2017-02-01 | 合肥君达高科信息技术有限公司 | High-speed camera system with punctual data transmission function |

| CN103475871A (en)* | 2013-09-23 | 2013-12-25 | 合肥君达高科信息技术有限公司 | High-speed camera system with punctual data transmission function |

| CN104902207A (en)* | 2015-06-17 | 2015-09-09 | 四川特伦特科技股份有限公司 | High speed signal collection method |

| CN104902207B (en)* | 2015-06-17 | 2018-03-30 | 四川特伦特科技股份有限公司 | A kind of high-speed signal acquisition method |

| CN105578042A (en)* | 2015-12-18 | 2016-05-11 | 深圳市金立通信设备有限公司 | Image data transmission method and terminal |

| CN105578042B (en)* | 2015-12-18 | 2019-04-30 | 深圳市金立通信设备有限公司 | A kind of transmission method and terminal of image data |

| CN108989605A (en)* | 2018-07-27 | 2018-12-11 | 湖南科技大学 | A kind of image capturing and transmitting system and method |

| CN111193873A (en)* | 2019-12-25 | 2020-05-22 | 新大陆数字技术股份有限公司 | Image rapid dimming system and method |

| CN111526317A (en)* | 2020-04-20 | 2020-08-11 | 武汉卓目科技有限公司 | Low-delay image acquisition method, device and system |

| CN111526317B (en)* | 2020-04-20 | 2022-07-01 | 武汉卓目科技有限公司 | Low-delay image acquisition method, device and system |

| WO2023124768A1 (en)* | 2021-12-29 | 2023-07-06 | 杭州海康机器人股份有限公司 | Image capture card, image capture method, and image capture system |

Also Published As

| Publication number | Publication date |

|---|---|

| CN100361523C (en) | 2008-01-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN107527317B (en) | Data Transmission System Based on Image Processing | |

| CN110209607A (en) | A kind of channel IF data acquisition playback system | |

| CN101860657A (en) | Method and system for real-time image acquisition of large field of view visible infrared dual-channel camera | |

| CN1722810A (en) | A digital camera real-time acquisition system | |

| CN104394371B (en) | A kind of system for being adapted to a large amount of sequential image acquisitions and quick storage | |

| CN104378574B (en) | VGA IMAQs and compression storage device based on SoPC | |

| CN111314641B (en) | System and method for acquiring, storing and displaying high-frame-frequency image | |

| CN101567979A (en) | Data acquisition system between infrared vidicon and computer based on USB2.0 | |

| CN107908587A (en) | Real-time data acquisition transmitting device based on USB3.0 | |

| CN101793557B (en) | High-resolution imager data real-time acquisition system and method | |

| CN101901278B (en) | High-speed data acquisition card and data acquisition method | |

| CN110941583A (en) | USB3.0 data transmission system control method based on FPGA | |

| Yan et al. | Design of CMOS image acquisition system based on FPGA | |

| CN111639046B (en) | System and method for caching and transmitting data of far ultraviolet aurora imager in real time | |

| CN102253916B (en) | Double-end double-channel first in first out (FIFO) for synchronous-to-asynchronous conversion | |

| CN102012948B (en) | Data real-time acquisition and storage system and method based on USB | |

| CN207720271U (en) | Digital video image acquisition system based on USB3.0 | |

| CN2845007Y (en) | High speed data collecting card | |

| CN114302087A (en) | MIPI data transmission mode conversion method and device and electronic equipment | |

| CN1801313A (en) | Image data transmission and display circuit employing FPGA to control FED | |

| CN206136104U (en) | Image acquisition system based on CMOS image sensor | |

| CN101325712A (en) | A Portable Real-time Image Acquisition and Display Terminal Based on ARM | |

| CN118018665A (en) | A multi-channel image acquisition and processing system based on ZYNQ | |

| CN201449607U (en) | Data Collector Based on USB2.0 | |

| CN204100994U (en) | A kind of two-phase Linear Array CCD Data Acquisition and disposal system |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| EE01 | Entry into force of recordation of patent licensing contract | Application publication date:20060118 Assignee:Beijing IWHR Corporation (BIC) Assignor:China Institute of water resources and Hydropower Research Contract record no.:2014110000016 Denomination of invention:A real-time acquisition system for digital camera Granted publication date:20080109 License type:Exclusive License Record date:20140415 | |

| LICC | Enforcement, change and cancellation of record of contracts on the licence for exploitation of a patent or utility model | ||

| CF01 | Termination of patent right due to non-payment of annual fee | Granted publication date:20080109 Termination date:20140711 | |

| EXPY | Termination of patent right or utility model |