CN114510449A - Multi-core embedded system, communication method, equipment and storage medium - Google Patents

Multi-core embedded system, communication method, equipment and storage mediumDownload PDFInfo

- Publication number

- CN114510449A CN114510449ACN202210027739.6ACN202210027739ACN114510449ACN 114510449 ACN114510449 ACN 114510449ACN 202210027739 ACN202210027739 ACN 202210027739ACN 114510449 ACN114510449 ACN 114510449A

- Authority

- CN

- China

- Prior art keywords

- target

- core

- microprocessor

- space

- core chips

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F15/00—Digital computers in general; Data processing equipment in general

- G06F15/16—Combinations of two or more digital computers each having at least an arithmetic unit, a program unit and a register, e.g. for a simultaneous processing of several programs

- G06F15/163—Interprocessor communication

- G06F15/167—Interprocessor communication using a common memory, e.g. mailbox

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/40—Bus structure

- G06F13/4004—Coupling between buses

- G06F13/4022—Coupling between buses using switching circuits, e.g. switching matrix, connection or expansion network

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F15/00—Digital computers in general; Data processing equipment in general

- G06F15/76—Architectures of general purpose stored program computers

- G06F15/78—Architectures of general purpose stored program computers comprising a single central processing unit

- G06F15/7807—System on chip, i.e. computer system on a single chip; System in package, i.e. computer system on one or more chips in a single package

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2213/00—Indexing scheme relating to interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F2213/0026—PCI express

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Theoretical Computer Science (AREA)

- General Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Computing Systems (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Software Systems (AREA)

- Mathematical Physics (AREA)

- Hardware Redundancy (AREA)

Abstract

Description

Translated fromChinese技术领域technical field

本发明涉及通信领域,具体涉及一种多核嵌入式系统、通信方法、设备及存储介质。The invention relates to the field of communications, in particular to a multi-core embedded system, a communication method, a device and a storage medium.

背景技术Background technique

现有技术中,多核嵌入式系统作为从设备,基于高速串行计算机扩展总线标准(PCIE,peripheral component interconnect express)接口与主设备进行通信时,只能使用多核嵌入式系统的一个内核芯片与主设备通信连接,在此情况下,多核嵌入式系统的其他内核芯片无法与主设备通信连接,即,现有技术中只能实现两方通信,导致通信效率低。In the prior art, when a multi-core embedded system, as a slave device, communicates with the master device based on the high-speed serial computer expansion bus standard (PCIE, peripheral component interconnect express) interface, only one core chip of the multi-core embedded system can be used to communicate with the master device. Device communication connection. In this case, other core chips of the multi-core embedded system cannot be communicatively connected to the main device, that is, only two-party communication can be achieved in the prior art, resulting in low communication efficiency.

发明内容SUMMARY OF THE INVENTION

本申请提出了一种多核嵌入式系统、通信方法、设备及存储介质,至少可以解决现有技术中无法进行多方通信的技术问题。The present application proposes a multi-core embedded system, a communication method, a device and a storage medium, which can at least solve the technical problem that multi-party communication cannot be performed in the prior art.

根据本申请的一方面,提供了一种基于多核嵌入式系统的通信方法,所述多核嵌入式系统包括至少两个内核芯片,目标芯片的内存空间包括一个共享空间和至少两个目标空间,所述目标芯片是所述至少两个内核芯片中的一个芯片,所述至少两个内核芯片分别对应于所述至少两个目标空间,所述通信方法包括:According to an aspect of the present application, a communication method based on a multi-core embedded system is provided, the multi-core embedded system includes at least two core chips, the memory space of the target chip includes a shared space and at least two target spaces, so The target chip is one of the at least two core chips, the at least two core chips are respectively corresponding to the at least two target spaces, and the communication method includes:

所述至少两个内核芯片分别基于各自对应的目标空间,与各自对应的主设备进行通信;The at least two core chips communicate with their corresponding master devices respectively based on their corresponding target spaces;

所述至少两个内核芯片基于所述共享空间进行通信。The at least two core chips communicate based on the shared space.

在一种可能的实现方式中,所述至少两个内核芯片包括第一微处理器、第二微处理器和可编程器件,所述目标芯片为所述可编程器件,所述至少两个目标空间包括第一目标空间、第二目标空间和第三目标空间;In a possible implementation manner, the at least two core chips include a first microprocessor, a second microprocessor and a programmable device, the target chip is the programmable device, and the at least two target chips The space includes a first target space, a second target space and a third target space;

所述至少两个内核芯片分别基于各自对应的目标空间,与各自对应的主设备进行通信包括:The at least two core chips communicate with their corresponding master devices based on their corresponding target spaces, including:

所述第一微处理器基于所述第一目标空间,与所述第一微处理器对应的主设备进行通信;The first microprocessor communicates with the master device corresponding to the first microprocessor based on the first target space;

所述第二微处理器基于所述第二目标空间,与所述第二微处理器对应的主设备进行通信;The second microprocessor communicates with the master device corresponding to the second microprocessor based on the second target space;

所述可编程器件基于所述第三目标空间,与所述第三微处理器对应的主设备进行通信。The programmable device communicates with a host device corresponding to the third microprocessor based on the third target space.

在一种可能的实现方式中,所述通信方法还包括:In a possible implementation, the communication method further includes:

所述目标芯片对所述至少两个目标空间的读写状态进行监控。The target chip monitors the read and write states of the at least two target spaces.

在一种可能的实现方式中,所述目标芯片对所述至少两个目标空间的读写状态进行监控包括:In a possible implementation manner, the target chip monitoring the read and write status of the at least two target spaces includes:

在所述第二微处理器或所述可编程器件对所述第一目标空间进行读写时,所述可编程器件向所述第一微处理器发送第一中断信息,所述第一微处理器根据所述第一中断信息生成第一报错信息;When the second microprocessor or the programmable device reads and writes the first target space, the programmable device sends first interrupt information to the first microprocessor, and the first The processor generates first error reporting information according to the first interrupt information;

在所述第一微处理器或所述可编程器件对所述第二目标空间进行读写时,所述可编程器件向所述第二微处理器发送第二中断信息,所述第二微处理器根据所述第二中断信息生成第二报错信息;When the first microprocessor or the programmable device reads and writes the second target space, the programmable device sends second interrupt information to the second microprocessor, and the second The processor generates second error reporting information according to the second interrupt information;

在所述第一微处理器或所述第二微处理器对所述第三目标空间进行读写时,所述可编程器件生成第三中断信息,所述可编程器件根据所述第三中断信息生成第三报错信息。When the first microprocessor or the second microprocessor reads or writes the third target space, the programmable device generates third interrupt information, and the programmable device generates third interrupt information according to the third interrupt The message generates a third error message.

在一种可能的实现方式中,所述至少两个目标空间分别设有第一区域和第二区域;In a possible implementation manner, the at least two target spaces are respectively provided with a first area and a second area;

所述至少两个内核芯片分别基于各自对应的目标空间,与各自对应的主设备进行通信包括:The at least two core chips communicate with their corresponding master devices based on their corresponding target spaces, including:

所述至少两个内核芯片分别基于各自对应的第一区域进行写操作,基于各自对应的第二区域进行读操作;The at least two core chips respectively perform write operations based on their corresponding first regions, and perform read operations based on their respective corresponding second regions;

所述主设备基于所述主设备对应的第一区域进行读操作,基于所述主设备对应的第二区域进行写操作。The master device performs a read operation based on the first area corresponding to the master device, and performs a write operation based on the second area corresponding to the master device.

在一种可能的实现方式中,所述多核嵌入式系统设有一个目标接口,所述目标接口与所述至少两个内核芯片各自对应的目标空间相适配,所述目标接口通过高速串行计算机扩展总线与所述主设备连接。In a possible implementation manner, the multi-core embedded system is provided with a target interface, the target interface is adapted to the target spaces corresponding to the at least two core chips, and the target interface is connected through a high-speed serial A computer expansion bus is connected to the master device.

在一种可能的实现方式中,所述至少两个内核芯片分别基于各自对应的目标空间,与各自对应的主设备进行通信之前,所述通信方法还包括:In a possible implementation manner, before the at least two core chips communicate with their corresponding master devices based on their corresponding target spaces, the communication method further includes:

对所述可编程器件的内存空间进行划分处理,得到所述第一目标空间、所述第二目标空间、所述第三目标空间和所述共享空间。The memory space of the programmable device is divided to obtain the first target space, the second target space, the third target space and the shared space.

此外,根据本申请的一方面,提供了一种多核嵌入式系统,包括至少两个内核芯片,目标芯片的内存空间包括一个共享空间和至少两个目标空间,所述目标芯片是所述至少两个内核芯片中的一个芯片,所述至少两个内核芯片分别对应于所述至少两个目标空间;In addition, according to an aspect of the present application, a multi-core embedded system is provided, including at least two core chips, the memory space of the target chip includes a shared space and at least two target spaces, and the target chip is the at least two target chips. one of the core chips, the at least two core chips respectively correspond to the at least two target spaces;

所述至少两个内核芯片分别基于各自对应的目标空间,与各自对应的主设备通信连接;The at least two core chips are respectively connected to their corresponding master devices in communication based on their corresponding target spaces;

所述至少两个内核芯片基于所述共享空间通信连接。The at least two core chips are connected based on the shared space communication.

根据本申请的一方面,提供了一种基于多核嵌入式系统的通信设备,包括:According to an aspect of the present application, a communication device based on a multi-core embedded system is provided, including:

处理器;processor;

用于存储处理器可执行指令的存储器;memory for storing processor-executable instructions;

其中,所述处理器被配置为执行上述的方法。Wherein, the processor is configured to perform the above-mentioned method.

根据本申请的一方面,提供了一种非易失性计算机可读存储介质,其上存储有计算机程序指令,所述计算机程序指令被处理器执行时实现上述的方法。According to an aspect of the present application, there is provided a non-volatile computer-readable storage medium having computer program instructions stored thereon, the computer program instructions implementing the above method when executed by a processor.

本申请中,目标芯片是至少两个内核芯片中内存可编辑的一个芯片。可以通过对目标芯片的可编辑内存进行划分处理,得到一个共享空间和至少两个目标空间,至少两个目标空间一一对应于至少两个内核芯片,目标空间可以是基地址寄存器(Bar),共享空间可以是片上空间(on-chip space)。本申请中,内核芯片可以基于对应的目标空间与对应的主设备进行通信。内核芯片可以基于对应的目标空间进行读写操作,内核芯片对应的主设备也可以基于内核芯片对应的目标空间进行读写操作,从而实现内核芯片与主设备之间的通信。In this application, the target chip is one chip whose memory can be edited among at least two core chips. A shared space and at least two target spaces can be obtained by dividing the editable memory of the target chip. The at least two target spaces correspond to at least two kernel chips one-to-one. The target space can be a base address register (Bar), The shared space may be on-chip space. In this application, the core chip may communicate with the corresponding master device based on the corresponding target space. The kernel chip can perform read and write operations based on the corresponding target space, and the master device corresponding to the kernel chip can also perform read and write operations based on the target space corresponding to the kernel chip, thereby realizing communication between the kernel chip and the master device.

至少两个内核芯片可以分别基于各自对应的目标空间,与各自对应的主设备进行通信,从而实现多核嵌入式系统的多个内核芯片分别与对应的主设备之间通信,其中,多个内核芯片可以是至少两个内核芯片,主设备的数量可以是一个或多个。在一个示例中,任意主设备均可以与任意内核芯片通信。在另一个示例中,多个主设备和多个内核芯片之间可以具有对应关系,一个主设备可以与特定的一个或多个内核芯片通信,一个内核芯片可以与特定的一个或多个主设备通信。此外,多核嵌入式系统的多个内核芯片均可以基于共享空间进行读写操作,实现多个内核芯片之间的通信。由此,本申请中,一个多核嵌入式系统的多个内核芯片可以分别与对应的主设备通信,多个内核芯片之间也可以通信,由此实现至少两个内核芯片与对应的主设备之间的多方通信,其中,多方是指内核芯片与主设备的数量总和为三个及三个以上。At least two core chips can communicate with their corresponding master devices based on their corresponding target spaces, so as to realize communication between multiple core chips of the multi-core embedded system and the corresponding master devices, wherein the multiple core chips It can be at least two core chips, and the number of master devices can be one or more. In one example, any master device can communicate with any core chip. In another example, there may be a correspondence between multiple master devices and multiple core chips, one master device may communicate with a specific one or more core chips, and one core chip may communicate with a specific one or more master devices communication. In addition, multiple core chips of the multi-core embedded system can perform read and write operations based on the shared space to realize communication between multiple core chips. Therefore, in this application, multiple core chips of a multi-core embedded system can communicate with the corresponding master device respectively, and multiple core chips can also communicate with each other, thereby realizing the communication between at least two core chips and the corresponding master device. Multi-party communication between them, where multi-party means that the sum of the number of the core chip and the main device is three or more.

本申请中,可以通过一根总线连接多核嵌入式系统的多个内核芯片和至少一个主设备,本申请中的多核嵌入式系统与主设备之间无需使用总线桥;基于目标芯片的目标空间和共享空间,就可以实现至少两个内核芯片与至少一个主设备之间的多方通信,而且不会降低带宽,可以提高数据传输效率,提高通信质量。In this application, multiple core chips of a multi-core embedded system and at least one main device can be connected through a bus, and there is no need to use a bus bridge between the multi-core embedded system and the main device in this application; By sharing space, multi-party communication between at least two core chips and at least one master device can be realized without reducing bandwidth, which can improve data transmission efficiency and communication quality.

本申请提供的多核嵌入式系统可以应用于具有自动驾驶功能的车辆中,可以用于对车辆行驶过程中的相关数据进行分析、处理、计算等,通过本申请提供的多核嵌入式系统的多个内核芯片与主设备之间的多方通信,可以大幅度提高通信过程中数据交互的速度、准确性,提高通信效率,提高自动驾驶的安全性。The multi-core embedded system provided by this application can be applied to a vehicle with automatic driving function, and can be used to analyze, process, and calculate the relevant data during the driving process of the vehicle. The multi-party communication between the core chip and the main device can greatly improve the speed and accuracy of data interaction during the communication process, improve communication efficiency, and improve the safety of autonomous driving.

附图说明Description of drawings

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。In order to explain the embodiments of the present invention or the technical solutions in the prior art more clearly, the following briefly introduces the accompanying drawings that need to be used in the description of the embodiments or the prior art. Obviously, the accompanying drawings in the following description are only These are some embodiments of the present invention. For those of ordinary skill in the art, other drawings can also be obtained according to these drawings without creative efforts.

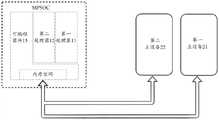

图1为根据一示例性实施例示出的一种多核嵌入式系统与主设备的框图;1 is a block diagram of a multi-core embedded system and a host device according to an exemplary embodiment;

图2为根据另一示例性实施例示出的一种多核嵌入式系统与主设备的框图;FIG. 2 is a block diagram of a multi-core embedded system and a master device according to another exemplary embodiment;

图3为根据又一示例性实施例示出的一种多核嵌入式系统与主设备的框图;3 is a block diagram of a multi-core embedded system and a host device according to yet another exemplary embodiment;

图4为根据一示例性实施例示出的一种基于多核嵌入式系统的通信方法的流程示意图;FIG. 4 is a schematic flowchart of a communication method based on a multi-core embedded system according to an exemplary embodiment;

图5为根据另一示例性实施例示出的一种基于多核嵌入式系统的通信方法的流程示意图。FIG. 5 is a schematic flowchart of a communication method based on a multi-core embedded system according to another exemplary embodiment.

具体实施方式Detailed ways

以下将参考附图详细说明本申请的各种示例性实施例、特征和方面。附图中相同的附图标记表示功能相同或相似的元件。尽管在附图中示出了实施例的各种方面,但是除非特别指出,不必按比例绘制附图。Various exemplary embodiments, features and aspects of the present application will be described in detail below with reference to the accompanying drawings. The same reference numbers in the figures denote elements that have the same or similar functions. While various aspects of the embodiments are shown in the drawings, the drawings are not necessarily drawn to scale unless otherwise indicated.

在这里专用的词“示例性”意为“用作例子、实施例或说明性”。这里作为“示例性”所说明的任何实施例不必解释为优于或好于其它实施例。The word "exemplary" is used exclusively herein to mean "serving as an example, embodiment, or illustration." Any embodiment described herein as "exemplary" is not necessarily to be construed as preferred or advantageous over other embodiments.

另外,为了更好的说明本申请,在下文的具体实施方式中给出了众多的具体细节。本领域技术人员应当理解,没有某些具体细节,本申请同样可以实施。在一些实例中,对于本领域技术人员熟知的方法、手段、元件和电路未作详细描述,以便于凸显本申请的主旨。In addition, in order to better illustrate the present application, numerous specific details are given in the following detailed description. It should be understood by those skilled in the art that the present application may be practiced without certain specific details. In some instances, methods, means, components and circuits well known to those skilled in the art have not been described in detail so as not to obscure the subject matter of the present application.

本申请提出了一种多核嵌入式系统、通信方法、设备及存储介质,至少可以解决现有技术中无法进行多方通信的技术问题,本申请具体是以如下技术方案实现的。The present application proposes a multi-core embedded system, a communication method, a device and a storage medium, which can at least solve the technical problem that multi-party communication cannot be performed in the prior art. The present application is specifically implemented by the following technical solutions.

结合图1至图3所示,本说明书实施例提供的一种多核嵌入式系统,包括至少两个内核芯片,目标芯片的内存空间包括一个共享空间和至少两个目标空间,目标芯片是至少两个内核芯片中的一个芯片,至少两个内核芯片分别对应于至少两个目标空间;1 to 3, a multi-core embedded system provided by the embodiments of this specification includes at least two core chips, the memory space of the target chip includes a shared space and at least two target spaces, and the target chip is at least two One of the core chips, at least two core chips respectively correspond to at least two target spaces;

至少两个内核芯片分别基于各自对应的目标空间,与各自对应的主设备通信连接;At least two core chips are respectively connected to their corresponding master devices in communication based on their corresponding target spaces;

至少两个内核芯片基于共享空间通信连接。At least two core chips are connected based on shared space communication.

嵌入式系统是一种完全嵌入受控器件内部,为特定应用而设计的专用计算机系统。本说明书实施例中的多核嵌入式系统(MPSOC)可以包括至少两个内核芯片,内核芯片可以用于完成计算、接收或存储命令、处理数据等操作。目标芯片是至少两个内核芯片中内存可编辑的一个芯片。可以通过对目标芯片的可编辑内存进行划分处理,得到一个共享空间和至少两个目标空间,至少两个目标空间一一对应于至少两个内核芯片,目标空间可以是基地址寄存器(Bar),共享空间可以是片上空间(on-chip space)。An embedded system is a special-purpose computer system that is completely embedded in the controlled device and designed for a specific application. The multi-core embedded system (MPSOC) in the embodiments of this specification may include at least two core chips, and the core chips may be used to perform operations such as computing, receiving or storing commands, and processing data. The target chip is one of at least two core chips whose memory is programmable. A shared space and at least two target spaces can be obtained by dividing the editable memory of the target chip. The at least two target spaces correspond to at least two kernel chips one-to-one. The target space can be a base address register (Bar), The shared space may be on-chip space.

本说明书实施例中,内核芯片可以基于对应的目标空间与对应的主设备进行通信。内核芯片可以基于对应的目标空间进行读写操作,内核芯片对应的主设备也可以基于内核芯片对应的目标空间进行读写操作,从而实现内核芯片与主设备之间的通信。In the embodiment of this specification, the core chip may communicate with the corresponding master device based on the corresponding target space. The kernel chip can perform read and write operations based on the corresponding target space, and the master device corresponding to the kernel chip can also perform read and write operations based on the target space corresponding to the kernel chip, thereby realizing communication between the kernel chip and the master device.

至少两个内核芯片可以分别基于各自对应的目标空间,与各自对应的主设备进行通信,从而实现多核嵌入式系统的多个内核芯片分别与对应的主设备之间通信,其中,多个内核芯片可以是至少两个内核芯片,主设备的数量可以是一个或多个。在一个示例中,任意主设备均可以与任意内核芯片通信。在另一个示例中,多个主设备和多个内核芯片之间可以具有对应关系,一个主设备可以与特定的一个或多个内核芯片通信,一个内核芯片可以与特定的一个或多个主设备通信。此外,多核嵌入式系统的多个内核芯片均可以基于共享空间进行读写操作,实现多个内核芯片之间的通信。由此,本说明书实施例中,一个多核嵌入式系统的多个内核芯片可以分别与对应的主设备通信,多个内核芯片之间也可以通信,由此实现至少两个内核芯片与对应的主设备之间的多方通信,其中,多方是指内核芯片与主设备的数量总和为三个及三个以上。At least two core chips can communicate with their corresponding master devices based on their corresponding target spaces, so as to realize communication between multiple core chips of the multi-core embedded system and the corresponding master devices, wherein the multiple core chips It can be at least two core chips, and the number of master devices can be one or more. In one example, any master device can communicate with any core chip. In another example, there may be a correspondence between multiple master devices and multiple core chips, one master device may communicate with a specific one or more core chips, and one core chip may communicate with a specific one or more master devices communication. In addition, multiple core chips of the multi-core embedded system can perform read and write operations based on the shared space to realize communication between multiple core chips. Therefore, in the embodiment of this specification, multiple core chips of a multi-core embedded system can communicate with the corresponding master device respectively, and multiple core chips can also communicate with each other, thereby realizing that at least two core chips communicate with the corresponding master device. Multi-party communication between devices, where multi-party means that the sum of the number of core chips and main devices is three or more.

相关技术中,在多核嵌入式系统的一个内核芯片与主设备通信连接的情况下,多核嵌入式系统的其他内核芯片无法与主设备通信连接,即只能实现一个内核芯片与一个主设备之间的两方通信。In the related art, when one core chip of the multi-core embedded system is communicatively connected to the main device, other core chips of the multi-core embedded system cannot be communicatively connected to the main device, that is, only one core chip and one main device can be connected. two-way communication.

本说明书实施例中,可以通过一根总线连接多核嵌入式系统的多个内核芯片和至少一个主设备,本说明书实施例中的多核嵌入式系统与主设备之间无需使用总线桥;基于目标芯片的目标空间和共享空间,就可以实现至少两个内核芯片与至少一个主设备之间的多方通信,而且不会降低带宽,可以提高数据传输效率,提高通信质量。In the embodiment of this specification, multiple core chips of the multi-core embedded system and at least one master device can be connected through a bus, and a bus bridge is not required between the multi-core embedded system and the master device in the embodiment of this specification; based on the target chip The target space and the shared space can realize multi-party communication between at least two core chips and at least one master device without reducing bandwidth, which can improve data transmission efficiency and communication quality.

本说明书实施例提供的多核嵌入式系统可以应用于具有自动驾驶功能的车辆中,可以用于对车辆行驶过程中的相关数据进行分析、处理、计算等,通过本说明书实施例提供的多核嵌入式系统的多个内核芯片与主设备之间的多方通信,可以大幅度提高通信过程中数据交互的速度、准确性,提高通信效率,提高自动驾驶的安全性。The multi-core embedded system provided by the embodiments of this specification can be applied to a vehicle with an automatic driving function, and can be used to analyze, process, calculate, etc. related data during the driving process of the vehicle. The multi-core embedded system provided by the embodiments of this specification The multi-party communication between the multiple core chips of the system and the main device can greatly improve the speed and accuracy of data interaction during the communication process, improve communication efficiency, and improve the safety of autonomous driving.

结合图2所示,在一种可能的实现方式中,至少两个内核芯片包括第一微处理器11、第二微处理器12和可编程器件13,目标芯片为可编程器件13,至少两个目标空间包括第一目标空间、第二目标空间和第三目标空间;2, in a possible implementation manner, at least two core chips include a first microprocessor 11, a second microprocessor 12 and a programmable device 13, the target chip is a programmable device 13, and at least two The target spaces include a first target space, a second target space and a third target space;

第一微处理器11基于第一目标空间,与第一微处理器11对应的主设备通信连接;The first microprocessor 11 is communicatively connected with the master device corresponding to the first microprocessor 11 based on the first target space;

第二微处理器12基于第二目标空间,与第二微处理器12对应的主设备通信连接;The second microprocessor 12 is connected in communication with the master device corresponding to the second microprocessor 12 based on the second target space;

可编程器件13基于第三目标空间,与可编程器件13对应的主设备通信连接。The programmable device 13 is communicatively connected to a host device corresponding to the programmable device 13 based on the third target space.

本说明书实施例可以基于多核嵌入式系统,对多核嵌入式系统进行改进,使多核嵌入式系统的多个内存芯片与主设备之间实现多方通信。在一个示例中,多核嵌入式系统(MPSOC)的第一微处理器11的型号可以为CoretexA53,第二微处理器12的型号可以为CoretexR5,可编程器件13可以为现场可编程门阵列(FPGA,FieldProgrammableGateArray)。The embodiments of this specification can improve the multi-core embedded system based on the multi-core embedded system, so that multi-party communication can be realized between multiple memory chips of the multi-core embedded system and the main device. In one example, the model of the first microprocessor 11 of the multi-core embedded system (MPSOC) may be CoretexA53, the model of the second microprocessor 12 may be CoretexR5, and the programmable device 13 may be a field programmable gate array (FPGA). , FieldProgrammableGateArray).

现场可编程门阵列具有可编程、灵活、多用的优点。FPGA可以包括逻辑单元、乘法器等硬件资源,通过将这些硬件资源合理组织,可实现乘法器、寄存器、地址发生器等硬件电路。FPGA可通过使用框图来设计;FPGA可无限地重新编程,加载一个新的设计方案只需几百毫秒,利用重配置可以减少硬件的开销。FPGA的工作频率由FPGA芯片以及设计决定,可以通过修改设计或者更换更快的芯片来达到某些苛刻的要求。Field programmable gate arrays have the advantages of being programmable, flexible and multi-purpose. FPGA can include hardware resources such as logic units and multipliers. By rationally organizing these hardware resources, hardware circuits such as multipliers, registers, and address generators can be realized. FPGAs can be designed using block diagrams; FPGAs can be reprogrammed indefinitely, loading a new design in just a few hundred milliseconds, and hardware overhead can be reduced using reconfiguration. The operating frequency of the FPGA is determined by the FPGA chip and design, and some harsh requirements can be met by modifying the design or replacing a faster chip.

本说明书实施例中,可以根据实际需求设置主设备的数量、主设备与内核芯片之间的对应关系。In the embodiments of this specification, the number of master devices and the corresponding relationship between the master devices and the core chips may be set according to actual requirements.

结合图2所示,在一个示例中设有一个主设备20,第一微处理器11、第二微处理器12和可编程器件13(FPGA)均对应于主设备20;第一微处理器11和主设备20均可以基于FPGA的第一目标空间进行读写操作,第二微处理器12和主设备20均可以基于FPGA的第二目标空间进行读写操作,FPGA和主设备20均可以基于FPGA的第三目标空间进行读写操作,第一微处理器11、第二微处理器12和FPGA还可以基于FPGA的共享空间进行读写操作。As shown in FIG. 2 , in an example, there is a master device 20 , and the first microprocessor 11 , the second microprocessor 12 and the programmable device 13 (FPGA) all correspond to the master device 20 ; the first microprocessor 12 corresponds to the master device 20 ; 11 and the main device 20 can both perform read and write operations based on the first target space of the FPGA, both the second microprocessor 12 and the main device 20 can perform read and write operations based on the second target space of the FPGA, and both the FPGA and the main device 20 can perform read and write operations. The read and write operations are performed based on the third target space of the FPGA, and the first microprocessor 11 , the second microprocessor 12 and the FPGA may also perform read and write operations based on the shared space of the FPGA.

结合图3所示,在另一个示例中设有第一主设备21和第二主设备22,第一微处理器11对应于第一主设备21和第二主设备22,第二微处理器12对应于第二主设备22,可编程器件13(FPGA)对应于第二主设备22;第一微处理器11、第一主设备21和第二主设备22均可以基于FPGA的第一目标空间进行读写操作,第二微处理器12和第二主设备22均可以基于FPGA的第二目标空间进行读写操作,FPGA和第二主设备22均可以基于FPGA的第三目标空间进行读写操作。第一微处理器11、第二微处理器12和FPGA还可以基于FPGA的共享空间进行读写操作。3, in another example, a first master device 21 and a second master device 22 are provided, the first microprocessor 11 corresponds to the first master device 21 and the second master device 22, and the second microprocessor 12 corresponds to the second master device 22, and the programmable device 13 (FPGA) corresponds to the second master device 22; the first microprocessor 11, the first master device 21 and the second master device 22 can all be based on the first target of the FPGA space for read and write operations, both the second microprocessor 12 and the second master device 22 can perform read and write operations based on the second target space of the FPGA, and both the FPGA and the second master device 22 can read and write based on the third target space of the FPGA write operation. The first microprocessor 11 , the second microprocessor 12 and the FPGA can also perform read and write operations based on the shared space of the FPGA.

本说明书实施例的目标芯片基于FPGA进行空间划分,通过对FPGA中的内存空间进行划分处理得到第一目标空间、第二目标空间、第三目标空间和共享空间,易于实现。The target chip in the embodiments of this specification performs space division based on the FPGA, and obtains the first target space, the second target space, the third target space and the shared space by dividing the memory space in the FPGA, which is easy to implement.

在一种可能的实现方式中,目标芯片用于对至少两个目标空间的读写状态进行监控。In a possible implementation manner, the target chip is used to monitor the read and write status of at least two target spaces.

本说明书实施例中,目标空间的读写状态可以反应当前对目标空间进行读写操作的内核芯片,目标芯片可以基于目标空间的读写状态监控各个内核芯片与目标空间之间的读写进程。在一个示例中,目标芯片可以根据目标空间的读写状态和预设映射信息,确定异常的访问进程;预设映射信息可以表征多个目标空间与多个内核芯片之间的对应关系;异常的访问进程可以是目标空间与访问该空间的内核芯片不对应。本说明书实施例中FPGA可以对第一目标空间、第二目标空间、第三目标空间和共享空间的读写状态进行监控,确保内核芯片对与其对应的目标空间进行读写操作,避免目标空间对应的内核芯片之外的芯片对目标空间进行读写操作,提高通信数据传输的准确性和安全性。In the embodiment of this specification, the read/write status of the target space may reflect the current kernel chip performing read/write operations on the target space, and the target chip may monitor the read/write process between each kernel chip and the target space based on the read/write status of the target space. In one example, the target chip can determine an abnormal access process according to the read and write status of the target space and preset mapping information; the preset mapping information can represent the correspondence between multiple target spaces and multiple core chips; abnormal The accessing process can be that the target space does not correspond to the kernel chip accessing the space. In the embodiment of this specification, the FPGA can monitor the read and write status of the first target space, the second target space, the third target space, and the shared space, so as to ensure that the core chip performs read and write operations on the corresponding target space and avoid the corresponding target space. Chips other than the core chip perform read and write operations on the target space to improve the accuracy and security of communication data transmission.

在一种可能的实现方式中,可编程器件13用于在第二微处理器12或可编程器件13对第一目标空间进行读写时,向第一微处理器11发送第一中断信息;第一微处理器11用于根据第一中断信息生成第一报错信息;In a possible implementation manner, the programmable device 13 is configured to send the first interrupt information to the first microprocessor 11 when the second microprocessor 12 or the programmable device 13 reads and writes the first target space; The first microprocessor 11 is configured to generate first error reporting information according to the first interrupt information;

可编程器件13用于在第一微处理器11或可编程器件13对第二目标空间进行读写时,向第二微处理器12发送第二中断信息;第二微处理器12用于根据第二中断信息生成第二报错信息;The programmable device 13 is used for sending the second interrupt information to the second microprocessor 12 when the first microprocessor 11 or the programmable device 13 reads and writes the second target space; the second microprocessor 12 is used for The second interrupt information generates second error reporting information;

可编程器件13用于在第一微处理器11或第二微处理器12对第三目标空间进行读写时,生成第三中断信息;可编程器件13用于根据第三中断信息生成第三报错信息。The programmable device 13 is used to generate third interrupt information when the first microprocessor 11 or the second microprocessor 12 reads and writes the third target space; the programmable device 13 is used to generate the third interrupt information according to the third interrupt information. Error message.

本说明书实施例中,第一目标空间对应于第一微处理器11,第一微处理器11可以基于第一目标空间进行读写操作;如果第二微处理器12或可编程器件13对第一目标空间进行读写操作,可编程器件13可以监测到该读写操作并向第一微处理器11发送第一中断信息,指示第一微处理器11当前有其他内核芯片读写第一目标空间,第一微处理器11可以根据第一中断信息生成第一报错信息,禁止其他内核芯片读写第一目标空间。本说明书实施例的中断信息是基于中断机制生成的信息。In the embodiment of this specification, the first target space corresponds to the first microprocessor 11, and the first microprocessor 11 can perform read and write operations based on the first target space; if the second microprocessor 12 or the programmable device 13 A target space performs a read/write operation, and the programmable device 13 can monitor the read/write operation and send the first interrupt information to the first microprocessor 11, indicating that the first microprocessor 11 currently has other core chips to read and write the first target. space, the first microprocessor 11 can generate the first error message according to the first interrupt information, and prohibit other core chips from reading and writing the first target space. The interrupt information in the embodiments of this specification is information generated based on an interrupt mechanism.

在一个示例中,可编程器件13可以监测第一目标空间的读写状态,第一目标空间的读写状态可以反应读写第一目标空间的内核芯片的芯片标识信息。可编程器件13可以根据预设映射信息,对第一目标空间的读写状态和第一目标空间的空间标识信息进行匹配处理;预设映射信息可以表征多个目标空间与多个内核芯片之间的对应关系。如果匹配结果为成功,则说明当前访问第一目标空间的内核芯片可以基于第一目标空间进行读写操作。如果匹配结果为失败,则说明当前访问第一目标空间的内核芯片不可以基于第一目标空间进行读写操作,则可编程器件13向第一微处理器11发送第一中断信息。In one example, the programmable device 13 may monitor the read/write status of the first target space, and the read/write status of the first target space may reflect the chip identification information of the core chip that reads and writes the first target space. The programmable device 13 can perform matching processing on the read-write state of the first target space and the space identification information of the first target space according to the preset mapping information; the preset mapping information can represent the relationship between multiple target spaces and multiple core chips. corresponding relationship. If the matching result is successful, it means that the core chip currently accessing the first target space can perform read and write operations based on the first target space. If the matching result is failure, it means that the core chip currently accessing the first target space cannot perform read and write operations based on the first target space, and the programmable device 13 sends the first interrupt information to the first microprocessor 11 .

第二目标空间对应于第二微处理器12,第二微处理器12可以基于第二目标空间进行读写操作;如果第一微处理器11或可编程器件13对第二目标空间进行读写操作,可编程器件13可以监测到该读写操作并向第二微处理器12发送第二中断信息,指示第二微处理器12当前有其他内核芯片读写第二目标空间,第二微处理器12可以根据第二中断信息生成第二报错信息,禁止其他内核芯片读写第二目标空间。The second target space corresponds to the second microprocessor 12, and the second microprocessor 12 can perform read and write operations based on the second target space; if the first microprocessor 11 or the programmable device 13 reads and writes the second target space operation, the programmable device 13 can monitor the read and write operation and send the second interrupt information to the second microprocessor 12, indicating that the second microprocessor 12 currently has other core chips to read and write the second target space, and the second microprocessor 12 The controller 12 may generate the second error message according to the second interrupt information, and prohibit other core chips from reading and writing the second target space.

第三目标空间对应于可编程器件13,可编程器件13可以基于第三目标空间进行读写操作;如果第一微处理器11或第二微处理器12对第三目标空间进行读写操作,可编程器件13可以监测到该读写操作并向生成第三中断信息,指示可编程器件13当前有其他内核芯片读写第三目标空间,可编程器件13可以根据第三中断信息生成第三报错信息,禁止其他内核芯片读写第三目标空间。The third target space corresponds to the programmable device 13, and the programmable device 13 can perform read and write operations based on the third target space; if the first microprocessor 11 or the second microprocessor 12 performs read and write operations on the third target space, The programmable device 13 can monitor the read and write operations and generate third interrupt information, indicating that the programmable device 13 currently has other core chips to read and write the third target space, and the programmable device 13 can generate a third error report according to the third interrupt information information, prohibiting other core chips from reading and writing the third target space.

本说明书实施例可以基于FPGA实现对目标空间的监控,易于实现,避免目标空间对应的内核芯片之外的芯片对目标空间进行读写操作,提高了通信数据传输的准确性和安全性。The embodiments of this specification can monitor the target space based on FPGA, which is easy to implement, avoids the read and write operations on the target space by chips other than the core chip corresponding to the target space, and improves the accuracy and security of communication data transmission.

在一种可能的实现方式中,至少两个目标空间分别设有第一区域和第二区域;In a possible implementation manner, at least two target spaces are respectively provided with a first area and a second area;

至少两个内核芯片分别基于各自对应的第一区域进行写操作,基于各自对应的第二区域进行读操作;at least two core chips respectively perform write operations based on their corresponding first regions, and perform read operations based on their respective corresponding second regions;

主设备基于主设备对应的第一区域进行读操作,基于主设备对应的第二区域进行写操作。The master device performs a read operation based on the first area corresponding to the master device, and performs a write operation based on the second area corresponding to the master device.

结合图2所示,在一个示例中,主设备20在与第一微处理器11进行通信的时候可以读写第一目标空间。第一目标空间可以包括对应的第一区域和第二区域,其中第一目标空间的第一区域用于供第一微处理器11写、主设备20读,第一目标空间中的第二区域用于供第一微处理器11读、主设备20写,这样整个数据的交互不会产生覆盖等错误,第一微处理器11和主设备20在各自的读写结束后还可以基于中断机制通知对方。With reference to FIG. 2 , in one example, the master device 20 can read and write the first target space when communicating with the first microprocessor 11 . The first target space may include a corresponding first area and a second area, wherein the first area of the first target space is used for writing by the first microprocessor 11 and reading by the host device 20, and the second area in the first target space It is used for reading by the first microprocessor 11 and writing by the main device 20, so that the interaction of the entire data will not generate errors such as overwriting. Notify the other party.

主设备20在与第二微处理器12进行通信的时候可以读写第二目标空间。第二目标空间可以包括对应的第一区域和第二区域,其中第二目标空间的第一区域用于供第二微处理器12写、主设备20读,第二目标空间中的第二区域用于供第二微处理器12读、主设备20写,第二微处理器12和主设备20在各自的读写结束后还可以基于中断机制通知对方。The master device 20 can read and write the second target space while communicating with the second microprocessor 12 . The second target space may include a corresponding first area and a second area, wherein the first area of the second target space is used for writing by the second microprocessor 12 and reading by the host device 20, and the second area in the second target space It is used for the second microprocessor 12 to read and the master device 20 to write. The second microprocessor 12 and the master device 20 can also notify each other based on an interrupt mechanism after their respective reading and writing are completed.

主设备20在与可编程器件13进行通信的时候可以读写第三目标空间。第三目标空间可以包括对应的第一区域和第二区域。其中第三目标空间的第一区域部分用于供可编程器件13写、主设备20读,第三目标空间中的第二区域用于供可编程器件13读、主设备20写,这样整个数据的交互不会产生覆盖等错误,可编程器件13和主设备20在各自的读写结束后还可以基于中断机制通知对方。The master device 20 can read and write the third target space when communicating with the programmable device 13 . The third target space may include corresponding first and second regions. The first area of the third target space is used for writing by the programmable device 13 and read by the master device 20, and the second area in the third target space is used for reading by the programmable device 13 and writing by the master device 20, so that the entire data The interaction will not generate errors such as overwriting, and the programmable device 13 and the master device 20 can also notify each other based on an interrupt mechanism after their respective reading and writing are completed.

本说明书实施例中,每个目标空间均可以包括第一区域和第二区域,第一区域用于供对应的内核芯片进行写操作,供对应的主设备进行读操作;第二区域用于供对应的内核芯片进行读操作,供对应的主设备进行写操作;由此,整个数据的交互不会产生覆盖等错误,可以提高通信过程中数据交互的准确性。In the embodiment of this specification, each target space may include a first area and a second area, the first area is used for the corresponding core chip to perform a write operation and the corresponding master device to perform a read operation; the second area is used for the corresponding core chip to perform a read operation; The corresponding core chip performs a read operation for the corresponding master device to perform a write operation; thus, errors such as overwriting will not occur in the interaction of the entire data, which can improve the accuracy of data interaction during the communication process.

在一种可能的实现方式中,多核嵌入式系统设有一个目标接口,目标接口与至少两个内核芯片各自对应的目标空间相适配,目标接口通过高速串行计算机扩展总线与主设备连接。In a possible implementation manner, the multi-core embedded system is provided with a target interface, the target interface is adapted to the corresponding target spaces of at least two core chips, and the target interface is connected to the master device through a high-speed serial computer expansion bus.

本说明书实施例中,高速串行计算机扩展总线可以为peripheral componentinterconnect express(PCIE)总线,目标接口可以为PCIE接口。本说明书实施例中,一根PCIE总线可以同时连接多核嵌入式系统的PCIE接口和至少一个主设备,本说明书实施例中的多核嵌入式系统与主设备之间无需使用总线桥,就可以实现至少两个内核芯片与主设备之间的多方通信,而且不会降低带宽,可以提高数据传输效率,提高通信质量。In the embodiment of this specification, the high-speed serial computer expansion bus may be a peripheral component interconnect express (PCIE) bus, and the target interface may be a PCIE interface. In the embodiment of this specification, a PCIE bus can connect the PCIE interface of the multi-core embedded system and at least one master device at the same time. The multi-party communication between the two core chips and the main device does not reduce the bandwidth, which can improve the data transmission efficiency and improve the communication quality.

现有技术中,高速串行计算机扩展总线标准(PCIE,peripheral componentinterconnect express)接口只能进行主设备(pcie host)和从设备(pcie device)之间的两方通信。现有技术中,多核嵌入式系统(MPSOC)中包含4个CoretexA53、2个coretexR5、1个fpga,fpga包含大量逻辑资源。In the prior art, a high-speed serial computer expansion bus standard (PCIE, peripheral component interconnect express) interface can only perform two-party communication between a master device (pcie host) and a slave device (pcie device). In the prior art, a multi-core embedded system (MPSOC) includes four CoretexA53s, two coretexR5s, and one fpga, and the fpga contains a large number of logic resources.

本说明书实施例提供的多核嵌入式系统,可以通过fpga逻辑资源构建pcie从设备,从而与其他外设进行连接;在某些场景下CoretexA53运行linux操作系统、CoretexR5系统裸跑、以及FPGA都可以通过pcie与pcie host进行通信,实现四方通信主体都通过PCIE接口进行数据交互。本说明书实施例中,4个CoretexA53可以基于相同的目标空间与对应的主设备通信,2个coretexR5可以基于相同的目标空间与对应的主设备通信。The multi-core embedded system provided by the embodiments of this specification can build pcie slave devices through fpga logic resources, so as to connect with other peripherals; in some scenarios, CoretexA53 running linux operating system, CoretexR5 system bare running, and FPGA can all be The pcie communicates with the pcie host, so that the four parties communicate with each other through the PCIE interface. In the embodiment of this specification, four CoretexA53s can communicate with corresponding master devices based on the same target space, and two coretexR5s can communicate with corresponding master devices based on the same target space.

本说明书实施例对FPGA进行改进,基于FPGA构建特殊pcie device逻辑,实现基于pcie接口的四方通信。本说明书实施例中基于FPGA的内存空间划分4片空间用于CoretexA53、CoretexR5、FPGA、Host四方通信交互,其中:The embodiments of this specification improve the FPGA, build a special pcie device logic based on the FPGA, and realize the four-way communication based on the pcie interface. In the embodiment of this specification, the FPGA-based memory space is divided into 4 pieces of space for communication and interaction among CoretexA53, CoretexR5, FPGA, and Host, wherein:

第一目标空间(bar1):用于pcie host与CoretexA53进行数据读写通信,如果其他读写该目标空间会产生对应的读写异常中断给CoretexA53。The first target space (bar1): used for data read and write communication between the pcie host and the CoretexA53. If other read and write the target space, a corresponding read and write exception will be generated to the CoretexA53.

第二目标空间(bar2):用于pcie host与CoretexR5进行数据读写通信,如果其他读写该目标空间会产生对应的读写异常中断给CoretexR5。The second target space (bar2): used for data read and write communication between the pcie host and the CoretexR5, if other read and write the target space will generate a corresponding read and write exception interrupt to the CoretexR5.

第三目标空间(bar3):用于pcie host与FPGA进行数据读写通信,如果其他读写该目标空间会产生对应的读写异常中断给FPGA。The third target space (bar3): used for data read and write communication between the pcie host and the FPGA, if other read and write the target space will generate a corresponding read and write exception interrupt to the FPGA.

共享空间(On-Chip Space):用于CoretexA53、CoretexR5和FPGA之间的数据读写通信,此空间为多核嵌入式系统内部之间的读写交互空间,该空间因为不通过基地址寄存器(bar)体现给PCIE host所以,pcie host无法访问到。Shared space (On-Chip Space): It is used for data read and write communication between CoretexA53, CoretexR5 and FPGA. This space is the read and write interaction space between multi-core embedded systems. This space does not pass through the base address register (bar ) is reflected to the PCIE host, so the pcie host cannot access it.

本说明书实施例中,当pcie host与CoretexA53进行通信的时候pcie host往第一目标空间的第一区域写入数据,然后基于中断机制通知CoretexA53,然后CoretexA53读取第一目标空间的第一区域中的数据;反之CoretexA53与pcie host进行通信的时候可以往第一目标空间的第二区域写入数据,然后基于中断机制通知pcie host,然后pcie host读取第一目标空间的第二区域中的数据。这样实现了双方的通信,其他几个的通信同样的方式进行,从而实现了四个通信主体的相互通信。In the embodiment of this specification, when the pcie host communicates with the CoretexA53, the pcie host writes data to the first area of the first target space, and then notifies the CoretexA53 based on the interrupt mechanism, and then the CoretexA53 reads the first area of the first target space. On the contrary, when CoretexA53 communicates with the pcie host, it can write data to the second area of the first target space, and then notify the pcie host based on the interrupt mechanism, and then the pcie host reads the data in the second area of the first target space . In this way, the communication between the two parties is realized, and the other several communications are carried out in the same way, thereby realizing the mutual communication of the four communication subjects.

结合图4至图5所示,本说明书实施例提供一种基于多核嵌入式系统的通信方法,应用于多核嵌入式系统,多核嵌入式系统包括至少两个内核芯片,目标芯片的内存空间包括一个共享空间和至少两个目标空间,目标芯片是至少两个内核芯片中的一个芯片,至少两个内核芯片分别对应于至少两个目标空间,通信方法包括:With reference to FIGS. 4 to 5 , the embodiments of this specification provide a communication method based on a multi-core embedded system, which is applied to a multi-core embedded system. The multi-core embedded system includes at least two core chips, and the memory space of the target chip includes one. The shared space and at least two target spaces, the target chip is one of the at least two core chips, the at least two core chips are respectively corresponding to the at least two target spaces, and the communication method includes:

步骤S101:至少两个内核芯片分别基于各自对应的目标空间,与各自对应的主设备进行通信;Step S101: at least two core chips communicate with their corresponding master devices respectively based on their corresponding target spaces;

步骤S102:至少两个内核芯片基于共享空间进行通信。Step S102: At least two core chips communicate based on the shared space.

嵌入式系统是一种完全嵌入受控器件内部,为特定应用而设计的专用计算机系统。本说明书实施例中的多核嵌入式系统(MPSOC)可以包括至少两个内核芯片,内核芯片可以用于完成计算、接收或存储命令、处理数据等操作。目标芯片是至少两个内核芯片中内存可编辑的一个芯片。可以通过对目标芯片的可编辑内存进行划分处理,得到一个共享空间和至少两个目标空间,至少两个目标空间一一对应于至少两个内核芯片,目标空间可以是基地址寄存器(Bar),共享空间可以是片上空间(on-chip space)。An embedded system is a special-purpose computer system that is completely embedded in the controlled device and designed for a specific application. The multi-core embedded system (MPSOC) in the embodiments of this specification may include at least two core chips, and the core chips may be used to perform operations such as computing, receiving or storing commands, and processing data. The target chip is one of at least two core chips whose memory is programmable. A shared space and at least two target spaces can be obtained by dividing the editable memory of the target chip. The at least two target spaces correspond to at least two kernel chips one-to-one. The target space can be a base address register (Bar), The shared space may be on-chip space.

本说明书实施例中,内核芯片可以基于对应的目标空间与对应的主设备进行通信。内核芯片可以基于对应的目标空间进行读写操作,内核芯片对应的主设备也可以基于内核芯片对应的目标空间进行读写操作,从而实现内核芯片与主设备之间的通信。In the embodiment of this specification, the core chip may communicate with the corresponding master device based on the corresponding target space. The kernel chip can perform read and write operations based on the corresponding target space, and the master device corresponding to the kernel chip can also perform read and write operations based on the target space corresponding to the kernel chip, thereby realizing communication between the kernel chip and the master device.

至少两个内核芯片可以分别基于各自对应的目标空间,与各自对应的主设备进行通信,从而实现多核嵌入式系统的多个内核芯片分别与对应的主设备之间通信,其中,多个内核芯片可以是至少两个内核芯片,主设备的数量可以是一个或多个。在一个示例中,任意主设备均可以与任意内核芯片通信。在另一个示例中,多个主设备和多个内核芯片之间可以具有对应关系,一个主设备可以与特定的一个或多个内核芯片通信,一个内核芯片可以与特定的一个或多个主设备通信。此外,多核嵌入式系统的多个内核芯片均可以基于共享空间进行读写操作,实现多个内核芯片之间的通信。由此,本说明书实施例中,一个多核嵌入式系统的多个内核芯片可以分别与对应的主设备通信,多个内核芯片之间也可以通信,由此实现至少两个内核芯片与对应的主设备之间的多方通信,其中,多方是指内核芯片与主设备的数量总和为三个及三个以上。At least two core chips can communicate with their corresponding master devices based on their corresponding target spaces, so as to realize communication between multiple core chips of the multi-core embedded system and the corresponding master devices, wherein the multiple core chips It can be at least two core chips, and the number of master devices can be one or more. In one example, any master device can communicate with any core chip. In another example, there may be a correspondence between multiple master devices and multiple core chips, one master device may communicate with a specific one or more core chips, and one core chip may communicate with a specific one or more master devices communication. In addition, multiple core chips of the multi-core embedded system can perform read and write operations based on the shared space to realize communication between multiple core chips. Therefore, in the embodiment of this specification, multiple core chips of a multi-core embedded system can communicate with the corresponding master device respectively, and multiple core chips can also communicate with each other, thereby realizing that at least two core chips communicate with the corresponding master device. Multi-party communication between devices, where multi-party means that the sum of the number of core chips and main devices is three or more.

相关技术中,在多核嵌入式系统的一个内核芯片与主设备通信连接的情况下,多核嵌入式系统的其他内核芯片无法与主设备通信连接,即只能实现一个内核芯片与一个主设备之间的两方通信。In the related art, when one core chip of the multi-core embedded system is communicatively connected to the main device, other core chips of the multi-core embedded system cannot be communicatively connected to the main device, that is, only one core chip and one main device can be connected. two-way communication.

本说明书实施例中,可以通过一根总线连接多核嵌入式系统的多个内核芯片和至少一个主设备,本说明书实施例中的多核嵌入式系统与主设备之间无需使用总线桥;基于目标芯片的目标空间和共享空间,就可以实现至少两个内核芯片与至少一个主设备之间的多方通信,而且不会降低带宽,可以提高数据传输效率,提高通信质量。In the embodiment of this specification, multiple core chips of the multi-core embedded system and at least one master device can be connected through a bus, and a bus bridge is not required between the multi-core embedded system and the master device in the embodiment of this specification; based on the target chip The target space and the shared space can realize multi-party communication between at least two core chips and at least one master device without reducing bandwidth, which can improve data transmission efficiency and communication quality.

本说明书实施例提供的多核嵌入式系统可以应用于具有自动驾驶功能的车辆中,可以用于对车辆行驶过程中的相关数据进行分析、处理、计算等,通过本说明书实施例提供的多核嵌入式系统的多个内核芯片与主设备之间的多方通信,可以大幅度提高通信过程中数据交互的速度、准确性,提高通信效率,提高自动驾驶的安全性。The multi-core embedded system provided by the embodiments of this specification can be applied to a vehicle with an automatic driving function, and can be used to analyze, process, calculate, etc. related data during the driving process of the vehicle. The multi-core embedded system provided by the embodiments of this specification The multi-party communication between the multiple core chips of the system and the main device can greatly improve the speed and accuracy of data interaction during the communication process, improve communication efficiency, and improve the safety of autonomous driving.

在一种可能的实现方式中,至少两个内核芯片包括第一微处理器11、第二微处理器12和可编程器件13,目标芯片为可编程器件13,至少两个目标空间包括第一目标空间、第二目标空间和第三目标空间;In a possible implementation manner, the at least two core chips include a first microprocessor 11, a second microprocessor 12, and a programmable device 13, the target chip is a programmable device 13, and the at least two target spaces include a first microprocessor 11, a second microprocessor 12, and a programmable device 13. target space, second target space and third target space;

步骤S101包括:Step S101 includes:

步骤S1011:第一微处理器11基于第一目标空间,与第一微处理器对应的主设备进行通信;Step S1011: the first microprocessor 11 communicates with the master device corresponding to the first microprocessor based on the first target space;

步骤S1012:第二微处理器12基于第二目标空间,与第二微处理器对应的主设备进行通信;Step S1012: the second microprocessor 12 communicates with the master device corresponding to the second microprocessor based on the second target space;

步骤S1013:可编程器件13基于第三目标空间,与第三微处理器对应的主设备进行通信。Step S1013: The programmable device 13 communicates with the master device corresponding to the third microprocessor based on the third target space.

在一种可能的实现方式中,通信方法还包括步骤S103:In a possible implementation, the communication method further includes step S103:

目标芯片对至少两个目标空间的读写状态进行监控。The target chip monitors the read and write status of at least two target spaces.

在一种可能的实现方式中,步骤S103包括:In a possible implementation manner, step S103 includes:

在第二微处理器12或可编程器件13对第一目标空间进行读写时,可编程器件13向第一微处理器11发送第一中断信息,第一微处理器11根据第一中断信息生成第一报错信息;When the second microprocessor 12 or the programmable device 13 reads and writes the first target space, the programmable device 13 sends the first interrupt information to the first microprocessor 11, and the first microprocessor 11 sends the first interrupt information according to the first interrupt information. Generate the first error message;

在第一微处理器11或可编程器件13对第二目标空间进行读写时,可编程器件13向第二微处理器12发送第二中断信息,第二微处理器12根据第二中断信息生成第二报错信息;When the first microprocessor 11 or the programmable device 13 reads and writes the second target space, the programmable device 13 sends the second interrupt information to the second microprocessor 12, and the second microprocessor 12 sends the second interrupt information according to the second interrupt information. Generate a second error message;

在第一微处理器11或第二微处理器12对第三目标空间进行读写时,可编程器件13生成第三中断信息,可编程器件13根据第三中断信息生成第三报错信息。When the first microprocessor 11 or the second microprocessor 12 reads and writes the third target space, the programmable device 13 generates third interrupt information, and the programmable device 13 generates third error information according to the third interrupt information.

在一种可能的实现方式中,至少两个目标空间分别设有第一区域和第二区域;In a possible implementation manner, at least two target spaces are respectively provided with a first area and a second area;

至少两个内核芯片分别基于各自对应的目标空间,与各自对应的主设备进行通信包括:The at least two core chips communicate with their corresponding master devices based on their corresponding target spaces, including:

至少两个内核芯片分别基于各自对应的第一区域进行写操作,基于各自对应的第二区域进行读操作;At least two core chips respectively perform write operations based on their corresponding first regions, and perform read operations based on their respective corresponding second regions;

主设备基于主设备对应的第一区域进行读操作,基于主设备对应的第二区域进行写操作。The master device performs a read operation based on the first area corresponding to the master device, and performs a write operation based on the second area corresponding to the master device.

在一种可能的实现方式中,多核嵌入式系统设有一个目标接口,目标接口与至少两个内核芯片各自对应的目标空间相适配,目标接口通过高速串行计算机扩展总线与主设备连接。In a possible implementation manner, the multi-core embedded system is provided with a target interface, the target interface is adapted to the corresponding target spaces of at least two core chips, and the target interface is connected to the master device through a high-speed serial computer expansion bus.

在一种可能的实现方式中,步骤S101之前,通信方法还包括:In a possible implementation manner, before step S101, the communication method further includes:

对可编程器件13的内存空间进行划分处理,得到第一目标空间、第二目标空间、第三目标空间和共享空间。The memory space of the programmable device 13 is divided to obtain a first target space, a second target space, a third target space and a shared space.

本说明书实施例还提供一种基于多核嵌入式系统的通信设备,包括:处理器;用于存储处理器可执行指令的存储器;其中,处理器被配置为执行上述方法。Embodiments of the present specification also provide a communication device based on a multi-core embedded system, including: a processor; a memory for storing instructions executable by the processor; wherein the processor is configured to execute the above method.

此外,本说明书实施例还提供一种非易失性计算机可读存储介质,其上存储有计算机程序指令,计算机程序指令被处理器执行时实现上述基于多核嵌入式系统的通信方法。In addition, the embodiments of this specification also provide a non-volatile computer-readable storage medium on which computer program instructions are stored, and when the computer program instructions are executed by a processor, the above communication method based on a multi-core embedded system is implemented.

计算机程序产品可以包括计算机可读存储介质,其上载有用于使处理器实现本申请的各个方面的计算机可读程序指令。The computer program product may include a computer-readable storage medium having computer-readable program instructions loaded thereon for causing a processor to implement various aspects of the present application.

计算机可读存储介质可以是可以保持和存储由指令执行设备使用的指令的有形设备。计算机可读存储介质例如可以是――但不限于――电存储设备、磁存储设备、光存储设备、电磁存储设备、半导体存储设备或者上述的任意合适的组合。计算机可读存储介质的更具体的例子(非穷举的列表)包括:便携式计算机盘、硬盘、随机存取存储器(RAM)、只读存储器(ROM)、可擦式可编程只读存储器(EPROM或闪存)、静态随机存取存储器(SRAM)、便携式压缩盘只读存储器(CD-ROM)、数字多功能盘(DVD)、记忆棒、软盘、机械编码设备、例如其上存储有指令的打孔卡或凹槽内凸起结构、以及上述的任意合适的组合。这里所使用的计算机可读存储介质不被解释为瞬时信号本身,诸如无线电波或者其他自由传播的电磁波、通过波导或其他传输媒介传播的电磁波(例如,通过光纤电缆的光脉冲)、或者通过电线传输的电信号。A computer-readable storage medium may be a tangible device that can hold and store instructions for use by the instruction execution device. The computer-readable storage medium may be, for example, but not limited to, an electrical storage device, a magnetic storage device, an optical storage device, an electromagnetic storage device, a semiconductor storage device, or any suitable combination of the foregoing. More specific examples (non-exhaustive list) of computer readable storage media include: portable computer disks, hard disks, random access memory (RAM), read only memory (ROM), erasable programmable read only memory (EPROM) or flash memory), static random access memory (SRAM), portable compact disk read only memory (CD-ROM), digital versatile disk (DVD), memory sticks, floppy disks, mechanically coded devices, such as printers with instructions stored thereon Hole cards or raised structures in grooves, and any suitable combination of the above. Computer-readable storage media, as used herein, are not to be construed as transient signals per se, such as radio waves or other freely propagating electromagnetic waves, electromagnetic waves propagating through waveguides or other transmission media (eg, light pulses through fiber optic cables), or through electrical wires transmitted electrical signals.

这里所描述的计算机可读程序指令可以从计算机可读存储介质下载到各个计算/处理设备,或者通过网络、例如因特网、局域网、广域网和/或无线网下载到外部计算机或外部存储设备。网络可以包括铜传输电缆、光纤传输、无线传输、路由器、防火墙、交换机、网关计算机和/或边缘服务器。每个计算/处理设备中的网络适配卡或者网络接口从网络接收计算机可读程序指令,并转发该计算机可读程序指令,以供存储在各个计算/处理设备中的计算机可读存储介质中。The computer readable program instructions described herein may be downloaded to various computing/processing devices from a computer readable storage medium, or to an external computer or external storage device over a network such as the Internet, a local area network, a wide area network, and/or a wireless network. The network may include copper transmission cables, fiber optic transmission, wireless transmission, routers, firewalls, switches, gateway computers, and/or edge servers. A network adapter card or network interface in each computing/processing device receives computer-readable program instructions from a network and forwards the computer-readable program instructions for storage in a computer-readable storage medium in each computing/processing device .

用于执行本申请操作的计算机程序指令可以是汇编指令、指令集架构(ISA)指令、机器指令、机器相关指令、微代码、固件指令、状态设置数据、或者以一种或多种编程语言的任意组合编写的源代码或目标代码,编程语言包括面向对象的编程语言—诸如Smalltalk、C++等,以及常规的过程式编程语言—诸如“C”语言或类似的编程语言。计算机可读程序指令可以完全地在用户计算机上执行、部分地在用户计算机上执行、作为一个独立的软件包执行、部分在用户计算机上部分在远程计算机上执行、或者完全在远程计算机或服务器上执行。在涉及远程计算机的情形中,远程计算机可以通过任意种类的网络—包括局域网(LAN)或广域网(WAN)—连接到用户计算机,或者,可以连接到外部计算机(例如利用因特网服务提供商来通过因特网连接)。在一些实施例中,通过利用计算机可读程序指令的状态信息来个性化定制电子电路,例如可编程逻辑电路、现场可编程门阵列(FPGA)或可编程逻辑阵列(PLA),该电子电路可以执行计算机可读程序指令,从而实现本申请的各个方面。Computer program instructions for carrying out the operations of the present application may be assembly instructions, instruction set architecture (ISA) instructions, machine instructions, machine-dependent instructions, microcode, firmware instructions, state setting data, or instructions in one or more programming languages. Source or object code written in any combination, programming languages including object-oriented programming languages - such as Smalltalk, C++, etc., and conventional procedural programming languages - such as the "C" language or similar programming languages. The computer readable program instructions may execute entirely on the user's computer, partly on the user's computer, as a stand-alone software package, partly on the user's computer and partly on a remote computer, or entirely on the remote computer or server implement. In the case of a remote computer, the remote computer may be connected to the user's computer through any kind of network, including a local area network (LAN) or a wide area network (WAN), or may be connected to an external computer (eg, using an Internet service provider through the Internet connect). In some embodiments, custom electronic circuits, such as programmable logic circuits, field programmable gate arrays (FPGAs), or programmable logic arrays (PLAs), can be personalized by utilizing state information of computer readable program instructions. Computer readable program instructions are executed to implement various aspects of the present application.

这里参照根据本申请实施例的方法、装置(系统)和计算机程序产品的流程图和/或框图描述了本申请的各个方面。应当理解,流程图和/或框图的每个方框以及流程图和/或框图中各方框的组合,都可以由计算机可读程序指令实现。Aspects of the present application are described herein with reference to flowchart illustrations and/or block diagrams of methods, apparatus (systems) and computer program products according to embodiments of the present application. It will be understood that each block of the flowchart illustrations and/or block diagrams, and combinations of blocks in the flowchart illustrations and/or block diagrams, can be implemented by computer readable program instructions.

这些计算机可读程序指令可以提供给通用计算机、专用计算机或其它可编程数据处理装置的处理器,从而生产出一种机器,使得这些指令在通过计算机或其它可编程数据处理装置的处理器执行时,产生了实现流程图和/或框图中的一个或多个方框中规定的功能/动作的装置。也可以把这些计算机可读程序指令存储在计算机可读存储介质中,这些指令使得计算机、可编程数据处理装置和/或其他设备以特定方式工作,从而,存储有指令的计算机可读介质则包括一个制造品,其包括实现流程图和/或框图中的一个或多个方框中规定的功能/动作的各个方面的指令。These computer readable program instructions may be provided to a processor of a general purpose computer, special purpose computer or other programmable data processing apparatus to produce a machine that causes the instructions when executed by the processor of the computer or other programmable data processing apparatus , resulting in means for implementing the functions/acts specified in one or more blocks of the flowchart and/or block diagrams. These computer readable program instructions can also be stored in a computer readable storage medium, these instructions cause a computer, programmable data processing apparatus and/or other equipment to operate in a specific manner, so that the computer readable medium storing the instructions includes An article of manufacture comprising instructions for implementing various aspects of the functions/acts specified in one or more blocks of the flowchart and/or block diagrams.

也可以把计算机可读程序指令加载到计算机、其它可编程数据处理装置、或其它设备上,使得在计算机、其它可编程数据处理装置或其它设备上执行一系列操作步骤,以产生计算机实现的过程,从而使得在计算机、其它可编程数据处理装置、或其它设备上执行的指令实现流程图和/或框图中的一个或多个方框中规定的功能/动作。Computer readable program instructions can also be loaded onto a computer, other programmable data processing apparatus, or other equipment to cause a series of operational steps to be performed on the computer, other programmable data processing apparatus, or other equipment to produce a computer-implemented process , thereby causing instructions executing on a computer, other programmable data processing apparatus, or other device to implement the functions/acts specified in one or more blocks of the flowcharts and/or block diagrams.

附图中的流程图和框图显示了根据本申请的多个实施例的系统、方法和计算机程序产品的可能实现的体系架构、功能和操作。在这点上,流程图或框图中的每个方框可以代表一个模块、程序段或指令的一部分,模块、程序段或指令的一部分包含一个或多个用于实现规定的逻辑功能的可执行指令。在有些作为替换的实现中,方框中所标注的功能也可以以不同于附图中所标注的顺序发生。例如,两个连续的方框实际上可以基本并行地执行,它们有时也可以按相反的顺序执行,这依所涉及的功能而定。也要注意的是,框图和/或流程图中的每个方框、以及框图和/或流程图中的方框的组合,可以用执行规定的功能或动作的专用的基于硬件的系统来实现,或者可以用专用硬件与计算机指令的组合来实现。The flowchart and block diagrams in the Figures illustrate the architecture, functionality, and operation of possible implementations of systems, methods and computer program products according to various embodiments of the present application. In this regard, each block in the flowchart or block diagrams may represent a module, segment, or portion of instructions, which comprises one or more executables for implementing the specified logical function(s) instruction. In some alternative implementations, the functions noted in the blocks may occur out of the order noted in the figures. For example, two blocks in succession may, in fact, be executed substantially concurrently, or the blocks may sometimes be executed in the reverse order, depending upon the functionality involved. It is also noted that each block of the block diagrams and/or flowchart illustrations, and combinations of blocks in the block diagrams and/or flowchart illustrations, can be implemented in dedicated hardware-based systems that perform the specified functions or actions , or can be implemented in a combination of dedicated hardware and computer instructions.

以上已经描述了本申请的各实施例,上述说明是示例性的,并非穷尽性的,并且也不限于所披露的各实施例。在不偏离所说明的各实施例的范围和精神的情况下,对于本技术领域的普通技术人员来说许多修改和变更都是显而易见的。本文中所用术语的选择,旨在最好地解释各实施例的原理、实际应用或对市场中的技术改进,或者使本技术领域的其它普通技术人员能理解本文披露的各实施例。Various embodiments of the present application have been described above, and the foregoing descriptions are exemplary, not exhaustive, and not limiting of the disclosed embodiments. Numerous modifications and variations will be apparent to those of ordinary skill in the art without departing from the scope and spirit of the described embodiments. The terminology used herein was chosen to best explain the principles of the embodiments, the practical application or technical improvement in the marketplace, or to enable others of ordinary skill in the art to understand the embodiments disclosed herein.

Claims (10)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202210027739.6ACN114510449A (en) | 2022-01-11 | 2022-01-11 | Multi-core embedded system, communication method, equipment and storage medium |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202210027739.6ACN114510449A (en) | 2022-01-11 | 2022-01-11 | Multi-core embedded system, communication method, equipment and storage medium |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN114510449Atrue CN114510449A (en) | 2022-05-17 |

Family

ID=81550162

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN202210027739.6APendingCN114510449A (en) | 2022-01-11 | 2022-01-11 | Multi-core embedded system, communication method, equipment and storage medium |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN114510449A (en) |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101398804A (en)* | 2007-09-29 | 2009-04-01 | 深圳迈瑞生物医疗电子股份有限公司 | Equipment with printing drive function and method for implementing printing drive |

| CN104820657A (en)* | 2015-05-14 | 2015-08-05 | 西安电子科技大学 | Inter-core communication method and parallel programming model based on embedded heterogeneous multi-core processor |

| CN106648896A (en)* | 2016-12-26 | 2017-05-10 | 北京四方继保自动化股份有限公司 | Method for outputting peripheral through dual core sharing of Zynq chip in asymmetric multi-processing mode |

| CN108073544A (en)* | 2016-11-10 | 2018-05-25 | 张颖 | Sharing Memory Realization method between processor |

| CN113434087A (en)* | 2021-06-28 | 2021-09-24 | 山东航天电子技术研究所 | Multi-core starting method based on shared space |

- 2022

- 2022-01-11CNCN202210027739.6Apatent/CN114510449A/enactivePending

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101398804A (en)* | 2007-09-29 | 2009-04-01 | 深圳迈瑞生物医疗电子股份有限公司 | Equipment with printing drive function and method for implementing printing drive |

| CN104820657A (en)* | 2015-05-14 | 2015-08-05 | 西安电子科技大学 | Inter-core communication method and parallel programming model based on embedded heterogeneous multi-core processor |

| CN108073544A (en)* | 2016-11-10 | 2018-05-25 | 张颖 | Sharing Memory Realization method between processor |

| CN106648896A (en)* | 2016-12-26 | 2017-05-10 | 北京四方继保自动化股份有限公司 | Method for outputting peripheral through dual core sharing of Zynq chip in asymmetric multi-processing mode |

| CN113434087A (en)* | 2021-06-28 | 2021-09-24 | 山东航天电子技术研究所 | Multi-core starting method based on shared space |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US20160092118A1 (en) | Memory write management in a computer system | |

| CN117112447B (en) | Data transmission method and device, electronic equipment and readable storage medium | |

| US20220342835A1 (en) | Method and apparatus for disaggregation of computing resources | |

| CN113223597B (en) | Flash memory test method, flash memory test device, storage medium and terminal equipment | |

| CN105094684A (en) | Reuse method and system for problematic disks in disk array system | |

| CN115061958B (en) | Hard disk identification method, identification system, storage medium and computer equipment | |

| US9697018B2 (en) | Synthesizing inputs to preserve functionality | |

| CN114510449A (en) | Multi-core embedded system, communication method, equipment and storage medium | |

| US10656991B2 (en) | Electronic component having redundant product data stored externally | |

| CN116483281A (en) | Data management method and device for memory chip | |

| US10360137B2 (en) | Adaptive testing using dynamically determined system resources of a computer system | |

| US9519746B1 (en) | Addressing early mode slack fails by book decomposition | |

| CN107870878A (en) | Storage system, terminal and computer device | |

| US10922249B2 (en) | Input/output control code filter | |

| US20200241760A1 (en) | Method, apparatus and computer program product for storing data | |

| US9715466B1 (en) | Processing input/output operations in a channel using a control block | |

| US9690680B1 (en) | Testing hybrid instruction architecture | |

| CN114356541B (en) | Configuration method, device and system of computing core and electronic equipment | |

| CN114121138B (en) | Memory voltage testing methods, devices, computing devices and systems | |

| US8645774B2 (en) | Expedited memory drive self test | |

| US20230176958A1 (en) | Monitoring code coverage | |

| US9524202B2 (en) | Communication software stack optimization using distributed error checking | |

| US8645652B2 (en) | Concurrently moving storage devices from one adapter pair to another | |

| CN120407470A (en) | Data transmission method, device, system and storage medium | |

| CN120407471A (en) | Data transmission method, device, system and storage medium |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PB01 | Publication | ||

| PB01 | Publication | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination |