CN114020344B - Bus resource reservation method, device, equipment and storage medium - Google Patents

Bus resource reservation method, device, equipment and storage mediumDownload PDFInfo

- Publication number

- CN114020344B CN114020344BCN202210007514.4ACN202210007514ACN114020344BCN 114020344 BCN114020344 BCN 114020344BCN 202210007514 ACN202210007514 ACN 202210007514ACN 114020344 BCN114020344 BCN 114020344B

- Authority

- CN

- China

- Prior art keywords

- bus

- configuration information

- vga

- root port

- shared memory

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/44—Arrangements for executing specific programs

- G06F9/4401—Bootstrapping

- G06F9/4403—Processor initialisation

Landscapes

- Engineering & Computer Science (AREA)

- Software Systems (AREA)

- Theoretical Computer Science (AREA)

- Computer Security & Cryptography (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Bus Control (AREA)

Abstract

Description

Translated fromChinese技术领域technical field

本发明涉及计算机技术领域,特别涉及一种总线资源预留方法、装置、设备及存储介质。The present invention relates to the field of computer technology, and in particular, to a bus resource reservation method, device, device and storage medium.

背景技术Background technique

在服务器BIOS启动过程中,Intel给CPU所有的根端口(Root Port)分配0-255总共256个总线(BUS)资源,而且按照默认平均分配的方式分给各Root Port,但实际应用中每个Root Port下面接的设备不同,需要的BUS资源也有很大差异,例如一个带宽X16的RootPort下面接了4个X4带宽的NVME盘,那么这个Root Port仅需要预留4个BUS就足够了,而另一个带宽X16的Root Port下面接了1张X16带宽的智能网卡,但是这张网卡可能会虚拟出近100个网口,那么这个Root Port需要预留100个BUS才能支持这样网卡正常工作。因此预留BUS是调整CPU Root PortBUS分配的一个非常重要的技术,但是当前的服务器领域,采用的预留BUS的方法一般是根据Root Port下面所接PCIE设备型号的不同再进行调整,由于判断设备型号拿到设备需要的BUS资源这个动作需要在PCIE设备枚举之后,已经过了CPU BUS资源初始化的阶段,因此这个方法需要重启一次,在第二次启动中生效,而且这个方法一旦有新的设备或者原先的设备接到了另外一个Root Port下面,需要BIOS发布新的版本来支持,维护十分不方便。During the server BIOS startup process, Intel allocates a total of 256 bus (BUS) resources from 0 to 255 to all the root ports (Root Ports) of the CPU, and distributes them to each Root Port according to the default average distribution method, but in practical applications each Different devices are connected to the Root Port, and the required BUS resources are also very different. For example, if a Root Port with a bandwidth of X16 is connected to 4 NVME disks with a bandwidth of X4, then this Root Port only needs to reserve 4 BUS. Another X16 bandwidth Root Port is connected to an X16 bandwidth smart network card, but this network card may have nearly 100 network ports, so this Root Port needs to reserve 100 BUS to support this network card to work normally. Therefore, reserving BUS is a very important technology to adjust the allocation of CPU Root PortBUS, but in the current server field, the method of reserving BUS is generally adjusted according to the different models of PCIE devices connected under the Root Port. The action of the model getting the BUS resources required by the device needs to pass the CPU BUS resource initialization stage after the PCIE device is enumerated, so this method needs to be restarted once, and it will take effect in the second startup, and once this method has a new The device or the original device is connected to another Root Port, and the BIOS needs to release a new version to support it, which is very inconvenient to maintain.

现有技术中,CPU预留资源常通过先获取服务器对应的各PCIE设备的资源信息,然后根据资源信息确定PCIE设备的最大资源需求量,将PCIE桥预留的资源需求量更改为最大资源需求量,最后根据32位可预取的资源类型及最大资源需求量进行资源分配。但是,获取CPU需要预留的资源是通过读取PCIE设备配置空间得到的,这个动作是在PCIE设备枚举之后进行的,已经过了CPU资源分配的阶段,因此必定需要一次重启来根据最大资源需求量进行资源分配,造成资源的浪费,并且降低了资源配置的效率;其次该方法不支持带外设置CPU需要的最大资源量,完全根据PCIE设备类型而变化,存在很大的局限性。因此,如何提高总线资源预留效率是当前亟需解决的问题。In the prior art, the CPU reserves resources usually by first obtaining the resource information of each PCIE device corresponding to the server, then determining the maximum resource requirement of the PCIE device according to the resource information, and changing the resource requirement reserved by the PCIE bridge to the maximum resource requirement. Finally, resource allocation is performed according to the 32-bit prefetchable resource type and the maximum resource demand. However, the resource that needs to be reserved by the CPU is obtained by reading the configuration space of the PCIE device. This action is performed after the enumeration of the PCIE device and has passed the stage of CPU resource allocation. Therefore, a restart must be required. Resource allocation based on demand results in waste of resources and reduces the efficiency of resource allocation; secondly, this method does not support out-of-band setting of the maximum amount of resources required by the CPU, which changes completely according to the type of PCIE device, and has great limitations. Therefore, how to improve the bus resource reservation efficiency is an urgent problem to be solved at present.

发明内容SUMMARY OF THE INVENTION

有鉴于此,本发明的目的在于提供一种总线资源预留方法、装置、设备及介质,能够提高总线资源分配的效率。其具体方案如下:In view of this, the purpose of the present invention is to provide a bus resource reservation method, apparatus, device and medium, which can improve the efficiency of bus resource allocation. Its specific plan is as follows:

第一方面,本申请公开了一种总线资源预留方法,包括:In a first aspect, the present application discloses a method for reserving bus resources, including:

向基板管理控制器关联的VGA共享内存中添加总线配置信息;所述总线配置信息包括CPU的每个根端口对应的总线数量;Adding bus configuration information to the VGA shared memory associated with the baseboard management controller; the bus configuration information includes the number of buses corresponding to each root port of the CPU;

在基本输入输出系统的第一阶段对所述VGA共享内存所在的VGA设备进行初始化;In the first stage of the basic input output system, initialize the VGA device where the VGA shared memory is located;

在所述基本输入输出系统的所述第一阶段之后的第二阶段,根据所述VGA共享内存中的所述总线配置信息为每个根端口进行总线资源配置。In the second stage after the first stage of the basic input output system, bus resource configuration is performed for each root port according to the bus configuration information in the VGA shared memory.

可选的,所述向基板管理控制器关联的VGA共享内存中添加总线配置信息之前,还包括:Optionally, before adding the bus configuration information to the VGA shared memory associated with the baseboard management controller, the method further includes:

获取所述CPU 对应的默认总线配置参数,以得到所述总线配置信息;所述默认总线配置参数包括每个CPU的每个根端口对应的默认总线数量。Acquire the default bus configuration parameters corresponding to the CPUs to obtain the bus configuration information; the default bus configuration parameters include the default bus number corresponding to each root port of each CPU.

可选的,所述在基本输入输出系统的第一阶段对所述VGA共享内存所在的VGA设备进行初始化之前,还包括:Optionally, before initializing the VGA device where the VGA shared memory is located in the first stage of the basic input output system, the method further includes:

通过所述基板管理控制器,获取用户按照目标协议通过带外方式发送的修改请求;Obtain, through the baseboard management controller, a modification request sent by the user in an out-of-band manner according to the target protocol;

根据所述修改请求对所述总线配置信息进行修改,以为所述CPU的目标根端口配置对应的当前目标总线数量。The bus configuration information is modified according to the modification request, so as to configure the corresponding current target bus number for the target root port of the CPU.

可选的,所述修改请求包括修改命令或目标格式的修改文件;所述目标格式为所述总线配置信息对应的文件存储格式;所述目标协议包括智能平台管理接口协议和redfish协议。Optionally, the modification request includes a modification command or a modification file in a target format; the target format is a file storage format corresponding to the bus configuration information; the target protocol includes an intelligent platform management interface protocol and a redfish protocol.

可选的,所述根据所述VGA共享内存中的所述总线配置信息为每个根端口进行总线资源配置,包括:Optionally, performing bus resource configuration for each root port according to the bus configuration information in the VGA shared memory, including:

判断所述总线配置信息中是否包含所述当前目标总线数量;Determine whether the bus configuration information includes the current number of target buses;

若所述总线配置信息中包含所述当前目标总线数量,则按照所述当前目标总线数量为对应的所述根端口进行总线资源配置。If the bus configuration information includes the current number of target buses, the bus resource configuration is performed according to the root port corresponding to the current number of target buses.

可选的,所述判断所述总线配置信息中是否包含所述当前目标总线数量之后,还包括:Optionally, after judging whether the bus configuration information includes the current number of target buses, the method further includes:

若所述总线配置信息中不包含所述当前目标总线数量,则按照所述默认总线数量为对应的所述根端口进行总线资源配置。If the bus configuration information does not include the current target bus quantity, the bus resource configuration is performed for the corresponding root port according to the default bus quantity.

可选的,所述在所述基本输入输出系统的所述第一阶段之后的第二阶段,根据所述VGA共享内存中的所述总线配置信息为每个根端口进行总线资源配置,包括:Optionally, in the second stage after the first stage of the BIOS, performing bus resource configuration for each root port according to the bus configuration information in the VGA shared memory, including:

在所述基本输入输出系统的所述第一阶段之后的第二阶段,通过内存映射I/O方式读取所述VGA共享内存中的所述总线配置信息;In the second stage after the first stage of the basic input output system, the bus configuration information in the VGA shared memory is read by means of memory mapped I/O;

根据所述总线配置信息为每个根端口进行总线资源配置。Perform bus resource configuration for each root port according to the bus configuration information.

第二方面,本申请公开了一种总线资源预留装置,包括:In a second aspect, the present application discloses a bus resource reservation device, comprising:

总线配置信息添加模块,用于向基板管理控制器关联的VGA共享内存中添加总线配置信息;所述总线配置信息包括CPU的每个根端口对应的总线数量;a bus configuration information adding module, used for adding bus configuration information to the VGA shared memory associated with the baseboard management controller; the bus configuration information includes the number of buses corresponding to each root port of the CPU;

初始化模块,用于在基本输入输出系统的第一阶段对所述VGA共享内存所在的VGA设备进行初始化;an initialization module for initializing the VGA device where the VGA shared memory is located in the first stage of the basic input output system;

总线资源配置模块,用于在所述基本输入输出系统的所述第一阶段之后的第二阶段,根据所述VGA共享内存中的所述总线配置信息为每个根端口进行总线资源配置。A bus resource configuration module, configured to perform bus resource configuration for each root port according to the bus configuration information in the VGA shared memory in the second stage after the first stage of the basic input output system.

第三方面,本申请公开了一种电子设备,包括:In a third aspect, the present application discloses an electronic device, comprising:

存储器,用于保存计算机程序;memory for storing computer programs;

处理器,用于执行所述计算机程序,以实现前述的总线资源预留方法。The processor is configured to execute the computer program to implement the aforementioned method for reserving bus resources.

第四方面,本申请公开了一种计算机可读存储介质,用于存储计算机程序;其中计算机程序被处理器执行时实现前述的总线资源预留方法。In a fourth aspect, the present application discloses a computer-readable storage medium for storing a computer program, wherein the aforementioned method for reserving bus resources is implemented when the computer program is executed by a processor.

本申请中,向基板管理控制器关联的VGA共享内存中添加总线配置信息;所述总线配置信息包括CPU的每个根端口对应的总线数量;在基本输入输出系统的第一阶段对所述VGA共享内存所在的VGA设备进行初始化;在所述基本输入输出系统的所述第一阶段之后的第二阶段,根据所述VGA共享内存中的所述总线配置信息为每个根端口进行总线资源配置。可见,通过在基板管理控制器关联的VGA共享内存中存储总线配置信息,基本输入输出系统可以在首次进行总线资源配置之前,通过访问VGA共享内存获得CPU 根端口对应的预留总线资源的配置信息,由此在进行首次总线资源配置时可以直接根据VGA共享内存中存储的总线配置信息为CPU中每个根端口进行总线数量配置,使得总线预留的方案一次启动生效不需要额外的重启动作,提高了总线资源分配的效率。In this application, bus configuration information is added to the VGA shared memory associated with the baseboard management controller; the bus configuration information includes the number of buses corresponding to each root port of the CPU; The VGA device where the shared memory is located is initialized; in the second stage after the first stage of the basic input output system, the bus resource configuration is performed for each root port according to the bus configuration information in the VGA shared memory . It can be seen that by storing the bus configuration information in the VGA shared memory associated with the baseboard management controller, the basic input output system can obtain the configuration information of the reserved bus resources corresponding to the CPU root port by accessing the VGA shared memory before the first bus resource configuration Therefore, when configuring the bus resources for the first time, you can directly configure the number of buses for each root port in the CPU according to the bus configuration information stored in the VGA shared memory, so that the bus reservation scheme takes effect at one time and does not require additional restart actions. The efficiency of bus resource allocation is improved.

附图说明Description of drawings

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图。In order to explain the embodiments of the present invention or the technical solutions in the prior art more clearly, the following briefly introduces the accompanying drawings that need to be used in the description of the embodiments or the prior art. Obviously, the accompanying drawings in the following description are only It is an embodiment of the present invention. For those of ordinary skill in the art, other drawings can also be obtained according to the provided drawings without creative work.

图1为本申请提供的一种总线资源预留方法流程图;1 is a flowchart of a method for reserving bus resources provided by the application;

图2为本申请提供的一种具体的总线资源预留方法流程图;2 is a flowchart of a specific method for reserving bus resources provided by the application;

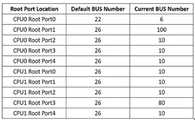

图3为本申请提供的一种具体的总线配置信息示意图;3 is a schematic diagram of a specific bus configuration information provided by the application;

图4为本申请提供的一种总线资源预留装置结构示意图;4 is a schematic structural diagram of a bus resource reservation device provided by the present application;

图5为本申请提供的一种电子设备结构图。FIG. 5 is a structural diagram of an electronic device provided by the present application.

具体实施方式Detailed ways

为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。In order to make the purposes, technical solutions and advantages of the embodiments of the present invention clearer, the technical solutions in the embodiments of the present invention will be clearly and completely described below with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments It is only a part of the embodiments of the present invention, but not all of the embodiments. Based on the embodiments of the present invention, all other embodiments obtained by those of ordinary skill in the art without creative efforts shall fall within the protection scope of the present invention.

现有技术中,CPU预留资源常通过先获取服务器对应的各PCIE设备的资源信息,然后根据资源信息确定PCIE设备的最大资源需求量,可预取的资源类型及最大资源需求量进行资源分配。但是,获取CPU需要预留的资源是通过读取PCIE设备配置空间得到的,是在PCIE设备枚举之后进行的,已经过了CPU资源分配的阶段,因此必定需要一次重启来根据最大资源需求量进行资源分配,造成资源的浪费,并且降低了资源配置的效率。为克服上述技术问题,本申请提出一种基于基板管理控制器关联的VGA共享内存的总线资源预留方法,能够提高总线资源分配的效率。In the prior art, the CPU reserves resources usually by first obtaining the resource information of each PCIE device corresponding to the server, and then determining the maximum resource demand of the PCIE device according to the resource information, the resource type that can be prefetched and the maximum resource demand for resource allocation. . However, the resources that need to be reserved by the CPU are obtained by reading the configuration space of the PCIE device, which is carried out after the enumeration of the PCIE device and has passed the stage of CPU resource allocation. Therefore, a restart must be required to meet the maximum resource demand. Allocating resources causes waste of resources and reduces the efficiency of resource allocation. In order to overcome the above technical problems, the present application proposes a method for reserving bus resources based on a VGA shared memory associated with a baseboard management controller, which can improve the efficiency of bus resource allocation.

本申请实施例公开了一种总线资源预留方法,参见图1所示,该方法可以包括以下步骤:An embodiment of the present application discloses a method for reserving bus resources. Referring to FIG. 1 , the method may include the following steps:

步骤S11:向基板管理控制器关联的VGA共享内存中添加总线配置信息;所述总线配置信息包括CPU的每个根端口对应的总线数量。Step S11: Add bus configuration information to the VGA shared memory associated with the baseboard management controller; the bus configuration information includes the number of buses corresponding to each root port of the CPU.

本实施例中,利用基板管理控制器(Baseboard Management Controller,BMC)关联的VGA(Video Graphics Array,视频图形阵列)共享内存进行总线配置信息的存储,其中,总线配置信息包括CPU的每个根端口对应的总线数量,也就是为CPU的每个根端口预留的总线数量,上述总线配置信息具体可以是以JSON格式存储在共享内存中的,即BMC在VGA共享内存中以JSON文件方式存储CPU每个Root Port预留BUS的数量。In this embodiment, a VGA (Video Graphics Array, video graphics array) shared memory associated with a baseboard management controller (Baseboard Management Controller, BMC) is used to store bus configuration information, where the bus configuration information includes each root port of the CPU The corresponding number of buses, that is, the number of buses reserved for each root port of the CPU. The above bus configuration information can be stored in the shared memory in JSON format, that is, the BMC stores the CPU in the VGA shared memory in the form of JSON files. The number of BUS reserved for each Root Port.

本实施例中,所述向基板管理控制器关联的VGA共享内存中添加总线配置信息之前,还可以包括:获取所述CPU 对应的默认总线配置参数,以得到所述总线配置信息;所述默认总线配置参数包括每个CPU的每个根端口对应的默认总线数量。即上述总线配置信息可以为当前CPU对应的默认总线配置参数,包括每个CPU的每个根端口对应的默认总线数量,其中当前CPU可以是一个或多个。In this embodiment, before adding the bus configuration information to the VGA shared memory associated with the baseboard management controller, the method may further include: acquiring default bus configuration parameters corresponding to the CPU to obtain the bus configuration information; The bus configuration parameters include the default number of buses for each root port of each CPU. That is, the above-mentioned bus configuration information may be the default bus configuration parameters corresponding to the current CPU, including the default number of buses corresponding to each root port of each CPU, where the current CPU may be one or more.

本实施例中,所述在基本输入输出系统的第一阶段对所述VGA共享内存所在的VGA设备进行初始化之前,还可以包括:通过所述基板管理控制器,获取用户按照目标协议通过带外方式发送的修改请求;根据所述修改请求对所述总线配置信息进行修改,以为所述CPU的目标根端口配置对应的当前目标总线数量。即例如图2所示,在获取到每个根端口对应的默认总线数量后,用户还可以通过基板管理控制器按照目标协议使用带外方式发送针对上述总线配置信息的修改请求,以便基板管理控制器根据修改请求对上述总线配置信息进行修改,使得总线配置信息中CPU的目标根端口配置总线数量为当前需要的目标总线数量,其中,上述目标根端口可以为CPU的全部根端口,也可以为部分根端口。例如图3所示为一种具体的BMC端VGA共享内存中总线配置信息存储格式示意图,以Intel最新whitley平台Icelake CPU为例,每个CPU有5个Root Port,在一台双路服务器上,第一列是Root Port的位置,具体为CPU0 Root Port0-Port4和CPU1 Root Port0-Port4,第二列为默认分配的BUS数量,第三列为提供给用户修改的当前预留的BUS数量。In this embodiment, before initializing the VGA device where the VGA shared memory is located in the first stage of the basic input output system, the method may further include: obtaining, through the baseboard management controller, that the user passes the out-of-band method according to the target protocol. modifying the bus configuration information according to the modification request, so as to configure the corresponding current target bus quantity for the target root port of the CPU. For example, as shown in Figure 2, after obtaining the default number of buses corresponding to each root port, the user can also send a modification request for the above bus configuration information in an out-of-band manner through the baseboard management controller according to the target protocol, so that the baseboard management control The controller modifies the above bus configuration information according to the modification request, so that the target root port configuration bus quantity of the CPU in the bus configuration information is the current required target bus quantity, wherein the above target root ports can be all the root ports of the CPU, or can be Partial root port. For example, Figure 3 shows a schematic diagram of a specific storage format of bus configuration information in the VGA shared memory on the BMC side. Taking the latest Intel whitley platform Icelake CPU as an example, each CPU has 5 Root Ports. On a dual-socket server, The first column is the location of the Root Port, specifically CPU0 Root Port0-Port4 and CPU1 Root Port0-Port4, the second column is the default allocated BUS number, and the third column is the currently reserved BUS number for user modification.

本实施例中,所述修改请求可以包括修改命令或目标格式的修改文件;所述目标格式可以为所述总线配置信息对应的文件存储格式;所述目标协议可以包括智能平台管理接口协议(Intelligent Platform Management Interface,IPMI)和redfish协议。即利用BMC提供给用户可通过带外方式设置总线配置信息文件内特定Root Port的预留BUS数量,此处可通过命令修改,也可通过导入JSON文件的方式修改。例如用户需要在CPU0 RootPort1上预留100个BUS,在CPU1 Root Port3上预留80个BUS,即可按照如图3所示带外修改预留的BUS数量,通过合理地调整BUS资源的分配,将BUS集中到有需求的Root Port下面,没有需求的Root Port分配少量BUS即可。即CPU的Root Port预留BUS的数量在BMC的VGA共享内存中以JSON文件方式存储,支持用户通过IPMI或者redfish等带外协议进行修改,不论需要预留BUS的设备接在了哪个Root Port下面,用户可以在开机前按照需求进行修改,提高了对总线资源预留参数修改的灵活性。In this embodiment, the modification request may include a modification command or a modification file in a target format; the target format may be a file storage format corresponding to the bus configuration information; the target protocol may include an intelligent platform management interface protocol (Intelligent Platform Management Interface Protocol). Platform Management Interface, IPMI) and redfish protocol. That is, BMC provides users with out-of-band settings to set the reserved BUS quantity for a specific Root Port in the bus configuration information file, which can be modified here by commands or by importing a JSON file. For example, if the user needs to reserve 100 BUS on CPU0 RootPort1 and 80 BUS on CPU1 Root Port3, the number of reserved BUS can be modified out-of-band as shown in Figure 3. By adjusting the allocation of BUS resources reasonably, Concentrate the BUS under the Root Port that needs it, and allocate a small amount of BUS to the Root Port that does not need it. That is, the number of BUS reserved by the Root Port of the CPU is stored as a JSON file in the VGA shared memory of the BMC, which supports users to modify it through out-of-band protocols such as IPMI or redfish, no matter which Root Port the device that needs to reserve the BUS is connected to. , the user can modify it according to the needs before starting the machine, which improves the flexibility of modifying the bus resource reservation parameters.

步骤S12:在基本输入输出系统的第一阶段对所述VGA共享内存所在的VGA设备进行初始化。Step S12: In the first stage of the basic input output system, initialize the VGA device where the VGA shared memory is located.

本实施例中,将总线配置信息存储至基板管理控制器的VGA共享内存后,基本输入输出系统(Basic Input Output System,BIOS)在运行的第一阶段对上述VGA共享内存所在的VGA设备进行初始化,可以理解的是,BIOS在开机的早期阶段,在CPU Root Port的BUS分配完成之前,进行BMC关联VGA设备的初始化,使其能够访问,初始化步骤要在开机后立即执行,这样才能保证BIOS在进行总线资源配置之前就读取到上述总线配置信息,由此保证总线资源配置中的BUS预留方案一次启动生效。In this embodiment, after the bus configuration information is stored in the VGA shared memory of the baseboard management controller, the Basic Input Output System (BIOS) initializes the VGA device where the VGA shared memory is located in the first stage of operation , It is understandable that in the early stage of booting, before the BUS allocation of the CPU Root Port is completed, the BIOS initializes the BMC-associated VGA device so that it can be accessed. The above-mentioned bus configuration information is read before the bus resource configuration is performed, thereby ensuring that the BUS reservation scheme in the bus resource configuration takes effect at one time.

步骤S13:在所述基本输入输出系统的所述第一阶段之后的第二阶段,根据所述VGA共享内存中的所述总线配置信息为每个根端口进行总线资源配置。Step S13: In the second stage after the first stage of the basic input output system, perform bus resource configuration for each root port according to the bus configuration information in the VGA shared memory.

本实施例中,在对BMC VGA设备进行初始化之后,基本输入输出系统根据VGA共享内存中的总线配置信息为每个根端口进行总线资源配置。可以理解的是,BIOS在CPU初始化之前,通过访问BMC VGA共享内存的方式获得CPU的Root Port预留BUS的数量, BIOS拿到预留BUS的数量再进行CPU内Root Port的BUS分配。In this embodiment, after initializing the BMC VGA device, the basic input output system configures the bus resources for each root port according to the bus configuration information in the VGA shared memory. It can be understood that before the CPU is initialized, the BIOS obtains the number of Root Port reserved BUS of the CPU by accessing the BMC VGA shared memory, and the BIOS obtains the reserved BUS number and then performs the BUS allocation of the Root Port in the CPU.

本实施例中,所述在所述基本输入输出系统的所述第一阶段之后的第二阶段,根据所述VGA共享内存中的所述总线配置信息为每个根端口进行总线资源配置,可以包括:在所述基本输入输出系统的所述第一阶段之后的第二阶段,通过内存映射I/O方式读取所述VGA共享内存中的所述总线配置信息;根据所述总线配置信息为每个根端口进行总线资源配置。即BIOS可以通过内存映射I/O(Memory-mapped I/O,MMIO)的方式读取VGA共享内存中JSON文件的内容。In this embodiment, in the second stage after the first stage of the basic input output system, the bus resource configuration is performed for each root port according to the bus configuration information in the VGA shared memory, which may be Including: in the second stage after the first stage of the basic input and output system, reading the bus configuration information in the VGA shared memory by means of memory mapped I/O; according to the bus configuration information: Each root port performs bus resource configuration. That is, the BIOS can read the content of the JSON file in the VGA shared memory by means of Memory-mapped I/O (MMIO).

本实施例中,所述根据所述VGA共享内存中的所述总线配置信息为每个根端口进行总线资源配置,可以包括:判断所述总线配置信息中是否包含所述当前目标总线数量;若所述总线配置信息中包含所述当前目标总线数量,则按照所述当前目标总线数量为对应的所述根端口进行总线资源配置。若所述总线配置信息中不包含所述当前目标总线数量,则按照所述默认总线数量为对应的所述根端口进行总线资源配置。以图3为例说明,BIOS读取VGA共享内存中总线配置信息后,判断第三列当前目标总线数量相对第二列默认总线数量是否有变化;如果有,则BIOS按照JSON文件中第三列当前目标总线数量的需求给CPU内RootPort分配BUS;否则,BIOS按照JSON文件中默认总线数量,即默认平均分配的方式给CPU的Root Port分配BUS。In this embodiment, the performing bus resource configuration for each root port according to the bus configuration information in the VGA shared memory may include: judging whether the bus configuration information includes the current number of target buses; if If the bus configuration information includes the current number of target buses, the bus resource configuration is performed according to the root port corresponding to the current number of target buses. If the bus configuration information does not include the current target bus quantity, the bus resource configuration is performed for the corresponding root port according to the default bus quantity. Taking Figure 3 as an example, after reading the bus configuration information in the VGA shared memory, the BIOS determines whether the current target bus number in the third column has changed from the default bus number in the second column; if so, the BIOS will follow the third column in the JSON file. The current number of target buses needs to allocate BUS to the RootPort in the CPU; otherwise, the BIOS allocates BUS to the Root Port of the CPU according to the default number of buses in the JSON file, that is, the default average allocation.

由此,通过充分利用了BMC关联的VGA的共享内存,BIOS在开机早期的阶段可以进行初始化并访问,BIOS先读取到用户需求的预留BUS数量,然后再进行针对CPU的BUS资源的初始化,从而让预留BUS这个需求可以一次启动立即生效,不需要BIOS在启动过程中再重启一次,此外BMC留给用户的带外设置预留BUS数量的接口非常灵活,可支持IPMI及Redfish等协议进行带外设置VGA共享内存中的内容,当用户想要调整预留BUS的数量时,不需要BIOS改动,只需要发一条带外命令即可实现。Therefore, by making full use of the shared memory of the VGA associated with the BMC, the BIOS can initialize and access it in the early stage of booting. The BIOS first reads the reserved BUS number required by the user, and then initializes the BUS resources for the CPU. , so that the requirement to reserve BUS can take effect immediately after one boot, without the need for the BIOS to restart again during the boot process. In addition, the interface for out-of-band settings reserved by the BMC for the user is very flexible, and can support protocols such as IPMI and Redfish. To set the content in the VGA shared memory out-of-band, when the user wants to adjust the number of reserved BUS, no need to change the BIOS, just send an out-of-band command.

由上可见,本实施例中通过向基板管理控制器关联的VGA共享内存中添加总线配置信息;所述总线配置信息包括CPU的每个根端口对应的总线数量;在基本输入输出系统的第一阶段对所述VGA共享内存所在的VGA设备进行初始化;在所述基本输入输出系统的所述第一阶段之后的第二阶段,根据所述VGA共享内存中的所述总线配置信息为每个根端口进行总线资源配置。可见,通过在基板管理控制器关联的VGA共享内存中存储总线配置信息,基本输入输出系统可以在首次进行总线资源配置之前,通过访问VGA共享内存获得CPU 根端口对应的预留总线资源的配置信息,由此在进行首次总线资源配置时可以直接根据VGA共享内存中存储的总线配置信息为CPU中每个根端口进行总线数量配置,使得总线预留的方案一次启动生效不需要额外的重启动作,提高了总线资源分配的效率。As can be seen from the above, in this embodiment, the bus configuration information is added to the VGA shared memory associated with the baseboard management controller; the bus configuration information includes the number of buses corresponding to each root port of the CPU; stage to initialize the VGA device where the VGA shared memory is located; in the second stage after the first stage of the basic input output system, according to the bus configuration information in the VGA shared memory for each root The port performs bus resource configuration. It can be seen that by storing the bus configuration information in the VGA shared memory associated with the baseboard management controller, the basic input output system can obtain the configuration information of the reserved bus resources corresponding to the CPU root port by accessing the VGA shared memory before the first bus resource configuration Therefore, when configuring the bus resources for the first time, you can directly configure the number of buses for each root port in the CPU according to the bus configuration information stored in the VGA shared memory, so that the bus reservation scheme takes effect at one time and does not require additional restart actions. The efficiency of bus resource allocation is improved.

相应的,本申请实施例还公开了一种总线资源预留装置,参见图4所示,该装置包括:Correspondingly, an embodiment of the present application also discloses a bus resource reservation device, as shown in FIG. 4 , the device includes:

总线配置信息添加模块11,用于向基板管理控制器关联的VGA共享内存中添加总线配置信息;所述总线配置信息包括CPU的每个根端口对应的总线数量;The bus configuration

初始化模块12,用于在基本输入输出系统的第一阶段对所述VGA共享内存所在的VGA设备进行初始化;The

总线资源配置模块13,用于在所述基本输入输出系统的所述第一阶段之后的第二阶段,根据所述VGA共享内存中的所述总线配置信息为每个根端口进行总线资源配置。The bus

由上可见,本实施例中向基板管理控制器关联的VGA共享内存中添加总线配置信息;所述总线配置信息包括CPU的每个根端口对应的总线数量;在基本输入输出系统的第一阶段对所述VGA共享内存所在的VGA设备进行初始化;在所述基本输入输出系统的所述第一阶段之后的第二阶段,根据所述VGA共享内存中的所述总线配置信息为每个根端口进行总线资源配置。可见,通过在基板管理控制器关联的VGA共享内存中存储总线配置信息,基本输入输出系统可以在首次进行总线资源配置之前,通过访问VGA共享内存获得CPU 根端口对应的预留总线资源的配置信息,由此在进行首次总线资源配置时可以直接根据VGA共享内存中存储的总线配置信息为CPU中每个根端口进行总线数量配置,使得总线预留的方案一次启动生效不需要额外的重启动作,提高了总线资源分配的效率。As can be seen from the above, in this embodiment, the bus configuration information is added to the VGA shared memory associated with the baseboard management controller; the bus configuration information includes the number of buses corresponding to each root port of the CPU; in the first stage of the basic input output system Initialize the VGA device where the VGA shared memory is located; in the second stage after the first stage of the basic input output system, according to the bus configuration information in the VGA shared memory for each root port Perform bus resource configuration. It can be seen that by storing the bus configuration information in the VGA shared memory associated with the baseboard management controller, the basic input output system can obtain the configuration information of the reserved bus resources corresponding to the CPU root port by accessing the VGA shared memory before the first bus resource configuration Therefore, when configuring the bus resources for the first time, you can directly configure the number of buses for each root port in the CPU according to the bus configuration information stored in the VGA shared memory, so that the bus reservation scheme takes effect at one time and does not require additional restart actions. The efficiency of bus resource allocation is improved.

在一些具体实施例中,所述总线资源预留装置具体可以包括:In some specific embodiments, the bus resource reservation apparatus may specifically include:

默认总线配置参数获取单元,用于获取所述CPU 对应的默认总线配置参数,以得到所述总线配置信息;所述默认总线配置参数包括每个CPU的每个根端口对应的默认总线数量。The default bus configuration parameter obtaining unit is configured to obtain the default bus configuration parameter corresponding to the CPU to obtain the bus configuration information; the default bus configuration parameter includes the default bus number corresponding to each root port of each CPU.

在一些具体实施例中,所述总线资源预留装置具体可以包括:In some specific embodiments, the bus resource reservation apparatus may specifically include:

修改请求获取单元,用于通过所述基板管理控制器,获取用户按照目标协议通过带外方式发送的修改请求;a modification request obtaining unit, configured to obtain, through the baseboard management controller, a modification request sent by a user in an out-of-band manner according to a target protocol;

修改单元,用于根据所述修改请求对所述总线配置信息进行修改,以为所述CPU的目标根端口配置对应的当前目标总线数量。A modification unit, configured to modify the bus configuration information according to the modification request, so as to configure the corresponding current target bus quantity for the target root port of the CPU.

在一些具体实施例中,所述修改请求具体可以包括修改命令或目标格式的修改文件;所述目标格式具体可以为所述总线配置信息对应的文件存储格式;所述目标协议具体可以包括智能平台管理接口协议和redfish协议。In some specific embodiments, the modification request may specifically include a modification command or a modification file in a target format; the target format may specifically be a file storage format corresponding to the bus configuration information; the target protocol may specifically include an intelligent platform Management interface protocol and redfish protocol.

在一些具体实施例中,所述总线资源配置模块13具体可以包括:In some specific embodiments, the bus

判断单元,用于判断所述总线配置信息中是否包含所述当前目标总线数量;a judging unit for judging whether the bus configuration information includes the current number of target buses;

第一总线资源配置单元,用于若所述总线配置信息中包含所述当前目标总线数量,则按照所述当前目标总线数量为对应的所述根端口进行总线资源配置。A first bus resource configuration unit, configured to configure bus resources according to the root port corresponding to the current target bus quantity if the bus configuration information includes the current target bus quantity.

在一些具体实施例中,所述总线资源配置模块13具体可以包括:In some specific embodiments, the bus

第二总线资源配置单元,用于若所述总线配置信息中不包含所述当前目标总线数量,则按照所述默认总线数量为对应的所述根端口进行总线资源配置。A second bus resource configuration unit, configured to perform bus resource configuration for the corresponding root port according to the default bus number if the current target bus number is not included in the bus configuration information.

在一些具体实施例中,所述总线资源配置模块13具体可以包括:In some specific embodiments, the bus

读取单元,用于在所述基本输入输出系统的所述第一阶段之后的第二阶段,通过内存映射I/O方式读取所述VGA共享内存中的所述总线配置信息;a reading unit, configured to read the bus configuration information in the VGA shared memory in the second stage after the first stage of the basic input output system through memory-mapped I/O;

配置单元,用于根据所述总线配置信息为每个根端口进行总线资源配置。A configuration unit, configured to configure bus resources for each root port according to the bus configuration information.

进一步的,本申请实施例还公开了一种电子设备,参见图5所示,图中的内容不能被认为是对本申请的使用范围的任何限制。Further, the embodiment of the present application also discloses an electronic device, as shown in FIG. 5 , the content in the figure should not be considered as any limitation on the scope of use of the present application.

图5为本申请实施例提供的一种电子设备20的结构示意图。该电子设备20,具体可以包括:至少一个处理器21、至少一个存储器22、电源23、通信接口24、输入输出接口25和通信总线26。其中,所述存储器22用于存储计算机程序,所述计算机程序由所述处理器21加载并执行,以实现前述任一实施例公开的总线资源预留方法中的相关步骤。FIG. 5 is a schematic structural diagram of an

本实施例中,电源23用于为电子设备20上的各硬件设备提供工作电压;通信接口24能够为电子设备20创建与外界设备之间的数据传输通道,其所遵循的通信协议是能够适用于本申请技术方案的任意通信协议,在此不对其进行具体限定;输入输出接口25,用于获取外界输入数据或向外界输出数据,其具体的接口类型可以根据具体应用需要进行选取,在此不进行具体限定。In this embodiment, the power supply 23 is used to provide working voltage for each hardware device on the

另外,存储器22作为资源存储的载体,可以是只读存储器、随机存储器、磁盘或者光盘等,其上所存储的资源包括操作系统221、计算机程序222及包括总线配置信息在内的数据223等,存储方式可以是短暂存储或者永久存储。In addition, the

其中,操作系统221用于管理与控制电子设备20上的各硬件设备以及计算机程序222,以实现处理器21对存储器22中海量数据223的运算与处理,其可以是Windows Server、Netware、Unix、Linux等。计算机程序222除了包括能够用于完成前述任一实施例公开的由电子设备20执行的总线资源预留方法的计算机程序之外,还可以进一步包括能够用于完成其他特定工作的计算机程序。The operating system 221 is used to manage and control each hardware device and computer program 222 on the

进一步的,本申请实施例还公开了一种计算机存储介质,所述计算机存储介质中存储有计算机可执行指令,所述计算机可执行指令被处理器加载并执行时,实现前述任一实施例公开的总线资源预留方法步骤。Further, an embodiment of the present application further discloses a computer storage medium, where computer-executable instructions are stored in the computer storage medium, and when the computer-executable instructions are loaded and executed by a processor, the disclosure of any of the foregoing embodiments is realized. The bus resource reservation method steps.

本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其它实施例的不同之处,各个实施例之间相同或相似部分互相参见即可。对于实施例公开的装置而言,由于其与实施例公开的方法相对应,所以描述的比较简单,相关之处参见方法部分说明即可。The various embodiments in this specification are described in a progressive manner, and each embodiment focuses on the differences from other embodiments, and the same or similar parts between the various embodiments may be referred to each other. As for the device disclosed in the embodiment, since it corresponds to the method disclosed in the embodiment, the description is relatively simple, and the relevant part can be referred to the description of the method.

结合本文中所公开的实施例描述的方法或算法的步骤可以直接用硬件、处理器执行的软件模块,或者二者的结合来实施。软件模块可以置于随机存储器(RAM)、内存、只读存储器(ROM)、电可编程ROM、电可擦除可编程ROM、寄存器、硬盘、可移动磁盘、CD-ROM、或技术领域内所公知的任意其它形式的存储介质中。The steps of a method or algorithm described in conjunction with the embodiments disclosed herein may be directly implemented in hardware, a software module executed by a processor, or a combination of the two. Software modules can be placed in random access memory (RAM), internal memory, read only memory (ROM), electrically programmable ROM, electrically erasable programmable ROM, registers, hard disk, removable disk, CD-ROM, or any other in the technical field. in any other known form of storage medium.

最后,还需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个……”限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。Finally, it should also be noted that in this document, relational terms such as first and second are used only to distinguish one entity or operation from another, and do not necessarily require or imply these entities or that there is any such actual relationship or sequence between operations. Moreover, the terms "comprising", "comprising" or any other variation thereof are intended to encompass a non-exclusive inclusion such that a process, method, article or device that includes a list of elements includes not only those elements, but also includes not explicitly listed or other elements inherent to such a process, method, article or apparatus. Without further limitation, an element qualified by the phrase "comprising a..." does not preclude the presence of additional identical elements in a process, method, article or apparatus that includes the element.

以上对本发明所提供的一种总线资源预留方法、装置、设备及介质进行了详细介绍,本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本发明的限制。A method, device, device and medium for reserving bus resources provided by the present invention have been described in detail above. The principles and implementations of the present invention are described with specific examples in this paper. The descriptions of the above embodiments are only used for Help to understand the method of the present invention and its core idea; at the same time, for those skilled in the art, according to the idea of the present invention, there will be changes in the specific implementation and application scope. In summary, the content of this specification It should not be construed as a limitation of the present invention.

Claims (8)

Translated fromChinesePriority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202210007514.4ACN114020344B (en) | 2022-01-06 | 2022-01-06 | Bus resource reservation method, device, equipment and storage medium |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202210007514.4ACN114020344B (en) | 2022-01-06 | 2022-01-06 | Bus resource reservation method, device, equipment and storage medium |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN114020344A CN114020344A (en) | 2022-02-08 |

| CN114020344Btrue CN114020344B (en) | 2022-04-22 |

Family

ID=80069963

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN202210007514.4AActiveCN114020344B (en) | 2022-01-06 | 2022-01-06 | Bus resource reservation method, device, equipment and storage medium |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN114020344B (en) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN115185874B (en)* | 2022-09-15 | 2022-12-13 | 珠海星云智联科技有限公司 | PCIE resource allocation method and related device |

| CN119201253B (en)* | 2024-11-26 | 2025-03-18 | 苏州元脑智能科技有限公司 | Bus resource configuration method and device |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104615572B (en)* | 2015-02-27 | 2018-05-01 | 苏州科达科技股份有限公司 | Hot plug processing system and method |

| CN108255527A (en)* | 2017-12-05 | 2018-07-06 | 华为技术有限公司 | The method and apparatus of activation system, computing device, readable storage medium storing program for executing |

| US10824471B2 (en)* | 2019-03-22 | 2020-11-03 | Dell Products L.P. | Bus allocation system |

- 2022

- 2022-01-06CNCN202210007514.4Apatent/CN114020344B/enactiveActive

Also Published As

| Publication number | Publication date |

|---|---|

| CN114020344A (en) | 2022-02-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10282192B1 (en) | Updating device code through a bus | |

| CN112099941B (en) | Method, device and system for implementing hardware accelerated processing | |

| CN110908753B (en) | Intelligent fusion cloud desktop server, client and system | |

| EP3457288A1 (en) | Computer system and storage access device | |

| CN114020344B (en) | Bus resource reservation method, device, equipment and storage medium | |

| CN109324991B (en) | Hot plug device, method, medium and system of PCIE (peripheral component interface express) equipment | |

| CN109828774B (en) | A server system and its startup method | |

| CN115562734A (en) | Data processor configuration method, device, equipment and medium | |

| CN111124508A (en) | Method and device for adjusting PXE (PCI extensions for instrumentation) starting sequence of network card | |

| CN115664953B (en) | Resource allocation method and related device for external equipment | |

| CN106569874B (en) | Operation method of storage device and physical server | |

| CN118672682A (en) | Server starting method and device, server and storage medium | |

| CN116339836A (en) | Resource access method, device, readable storage medium and BMC chip | |

| WO2025112645A1 (en) | Memory capacity adjustment method and apparatus, electronic device, and storage medium | |

| CN117687703A (en) | Server startup methods, devices, systems, storage media and electronic equipment | |

| CN113282342A (en) | Deployment method, device, system, electronic equipment and readable storage medium | |

| CN117827375A (en) | A method, device, equipment and medium for deploying a virtual machine Ceph cluster | |

| CN111163167B (en) | System installation method and device | |

| CN116881072A (en) | Network card monitoring method, device, system and equipment of baseboard management controller | |

| JP4692912B2 (en) | Resource allocation system and resource allocation method | |

| CN114048465B (en) | Stack state detection method, device, equipment and storage medium | |

| CN113064655B (en) | A BIOS network boot method, device and computer-readable storage medium | |

| CN118860507A (en) | Business interaction system, method, storage medium, and electronic device | |

| CN118689660A (en) | Method, device, medium and computer program product for dynamically displaying management information | |

| CN112580086B (en) | Configuration file access protection method, device, equipment and storage medium |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PB01 | Publication | ||

| PB01 | Publication | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| GR01 | Patent grant | ||

| GR01 | Patent grant | ||

| CP03 | Change of name, title or address | Address after:Building 9, No.1, guanpu Road, Guoxiang street, Wuzhong Economic Development Zone, Wuzhong District, Suzhou City, Jiangsu Province Patentee after:Suzhou Yuannao Intelligent Technology Co.,Ltd. Country or region after:China Address before:Building 9, No.1, guanpu Road, Guoxiang street, Wuzhong Economic Development Zone, Wuzhong District, Suzhou City, Jiangsu Province Patentee before:SUZHOU LANGCHAO INTELLIGENT TECHNOLOGY Co.,Ltd. Country or region before:China |