CN111353595A - Computing method, device and related products - Google Patents

Computing method, device and related productsDownload PDFInfo

- Publication number

- CN111353595A CN111353595ACN201910403429.8ACN201910403429ACN111353595ACN 111353595 ACN111353595 ACN 111353595ACN 201910403429 ACN201910403429 ACN 201910403429ACN 111353595 ACN111353595 ACN 111353595A

- Authority

- CN

- China

- Prior art keywords

- storage

- data

- interrupt

- instruction

- machine learning

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/06—Physical realisation, i.e. hardware implementation of neural networks, neurons or parts of neurons

- G06N3/063—Physical realisation, i.e. hardware implementation of neural networks, neurons or parts of neurons using electronic means

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Health & Medical Sciences (AREA)

- Life Sciences & Earth Sciences (AREA)

- Biomedical Technology (AREA)

- Biophysics (AREA)

- Theoretical Computer Science (AREA)

- Evolutionary Computation (AREA)

- Computational Linguistics (AREA)

- Data Mining & Analysis (AREA)

- Artificial Intelligence (AREA)

- General Health & Medical Sciences (AREA)

- Molecular Biology (AREA)

- Computing Systems (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Mathematical Physics (AREA)

- Software Systems (AREA)

- Neurology (AREA)

- Advance Control (AREA)

Abstract

Translated fromChineseDescription

Translated fromChinese技术领域technical field

本公开涉及计算机技术领域,尤其涉及一种中断存储指令处理方法、装置及相关产品。The present disclosure relates to the field of computer technologies, and in particular, to a method, device and related products for processing interrupt storage instructions.

背景技术Background technique

随着科技的不断发展,机器学习,尤其是神经网络算法的使用越来越广泛。其在图像识别、语音识别、自然语言处理等领域中都得到了良好的应用。但由于神经网络算法的复杂度越来越高,所涉及的数据运算种类和数量不断增大。相关技术中,在装置对数据的处理过程中发生中断退出时,对中断退出进行响应速度、效率不能满足用户的需求,以致影响装置对数据进行运算的效率和速度。With the continuous development of science and technology, the use of machine learning, especially neural network algorithms, is becoming more and more extensive. It has been well used in image recognition, speech recognition, natural language processing and other fields. However, due to the increasing complexity of neural network algorithms, the types and quantities of data operations involved continue to increase. In the related art, when an interrupted exit occurs during data processing by the device, the response speed and efficiency of the interrupted exit cannot meet the needs of the user, so that the efficiency and speed of the device's data operation are affected.

发明内容SUMMARY OF THE INVENTION

有鉴于此,本公开提出了一种中断存储指令处理方法、装置及相关产品,提高装置中断退出时进行响应的速度和效率,进而提高对数据进行运算的效率和速度。In view of this, the present disclosure proposes an interrupt storage instruction processing method, device, and related products, which improve the speed and efficiency of responding when the device is interrupted and exited, thereby improving the efficiency and speed of data operation.

根据本公开的第一方面,提供了一种中断存储指令处理装置,所述装置包括控制模块,所述控制模块包括:According to a first aspect of the present disclosure, an interrupt storage instruction processing apparatus is provided, the apparatus includes a control module, and the control module includes:

参数获取子模块,根据获取到的中断存储指令的操作域和操作码,确定进行响应中断退出的处理所需的存储参数;The parameter acquisition sub-module determines the storage parameters required for the processing of responding to the interrupt and exit according to the acquired operation domain and operation code of the interrupt storage instruction;

中断存储子模块,在执行到所述中断存储指令时,控制所述装置中断退出,并根据所述存储参数进行数据存储,The interrupt storage sub-module, when executing the interrupt storage instruction, controls the device to interrupt and exit, and performs data storage according to the storage parameter,

其中,所述操作码用于指示所述中断存储指令对装置中断退出时所进行的处理为中断存储处理,所述存储参数用于指示所述装置中断退出时需要存储的数据。Wherein, the operation code is used to indicate that the processing performed by the interrupt storage instruction when the device is interrupted and exited is an interrupted storage process, and the storage parameter is used to indicate the data to be stored when the device is interrupted and exited.

根据本公开的第二方面,提供了一种机器学习运算装置,所述装置包括:According to a second aspect of the present disclosure, there is provided a machine learning computing device, the device comprising:

一个或多个上述第一方面所述的中断存储指令处理装置,用于从其他处理装置中获取待运算数据和控制信息,并执行指定的机器学习运算,将执行结果通过I/O接口传递给其他处理装置;One or more interrupt storage instruction processing devices described in the first aspect above are used to obtain data to be calculated and control information from other processing devices, and perform specified machine learning operations, and pass the execution results to the I/O interface. other processing devices;

当所述机器学习运算装置包含多个所述中断存储指令处理装置时,所述多个所述中断存储指令处理装置间可以通过特定的结构进行连接并传输数据;When the machine learning computing device includes a plurality of the interrupt storage instruction processing devices, the multiple interrupt storage instruction processing devices can be connected through a specific structure and data can be transmitted;

其中,多个所述中断存储指令处理装置通过快速外部设备互连总线PCIE总线进行互联并传输数据,以支持更大规模的机器学习的运算;多个所述中断存储指令处理装置共享同一控制系统或拥有各自的控制系统;多个所述中断存储指令处理装置共享内存或者拥有各自的内存;多个所述中断存储指令处理装置的互联方式是任意互联拓扑。Wherein, a plurality of the interrupt storage instruction processing devices are interconnected and transmit data through the fast peripheral device interconnection bus PCIE bus to support larger-scale machine learning operations; a plurality of the interrupt storage instruction processing devices share the same control system Or have their own control systems; a plurality of the interrupt storage instruction processing devices share memory or have their own memory; the interconnection mode of the multiple interrupt storage instruction processing devices is any interconnection topology.

根据本公开的第三方面,提供了一种组合处理装置,所述装置包括:According to a third aspect of the present disclosure, there is provided a combined processing device, the device comprising:

上述第二方面所述的机器学习运算装置、通用互联接口和其他处理装置;The machine learning computing device, universal interconnection interface, and other processing devices described in the second aspect above;

所述机器学习运算装置与所述其他处理装置进行交互,共同完成用户指定的计算操作。The machine learning computing device interacts with the other processing devices to jointly complete the computing operation specified by the user.

根据本公开的第四方面,提供了一种机器学习芯片,所述机器学习芯片包括上述第二方面所述的机器学习络运算装置或上述第三方面所述的组合处理装置。According to a fourth aspect of the present disclosure, there is provided a machine learning chip, where the machine learning chip includes the machine learning network computing device described in the second aspect or the combined processing device described in the third aspect.

根据本公开的第五方面,提供了一种机器学习芯片封装结构,该机器学习芯片封装结构包括上述第四方面所述的机器学习芯片。According to a fifth aspect of the present disclosure, a machine learning chip packaging structure is provided, and the machine learning chip packaging structure includes the machine learning chip described in the fourth aspect.

根据本公开的第六方面,提供了一种板卡,该板卡包括上述第五方面所述的机器学习芯片封装结构。According to a sixth aspect of the present disclosure, there is provided a board card including the machine learning chip packaging structure described in the fifth aspect.

根据本公开的第七方面,提供了一种电子设备,所述电子设备包括上述第四方面所述的机器学习芯片或上述第六方面所述的板卡。According to a seventh aspect of the present disclosure, an electronic device is provided, and the electronic device includes the machine learning chip described in the fourth aspect or the board card described in the sixth aspect.

根据本公开的第八方面,提供了一种中断存储指令处理方法,所述方法应用于中断存储指令处理装置,所述方法包括:According to an eighth aspect of the present disclosure, a method for processing an interrupt storage instruction is provided. The method is applied to an interrupt storage instruction processing apparatus, and the method includes:

根据获取到的中断存储指令的操作域和操作码,确定进行响应中断退出的处理所需的存储参数;According to the obtained operation domain and operation code of the interrupt storage instruction, determine the storage parameters required for the processing of responding to the interrupt exit;

在执行到所述中断存储指令时,控制所述装置中断退出,并根据所述存储参数进行数据存储,When the interrupt storage instruction is executed, the device is controlled to interrupt and exit, and data storage is performed according to the storage parameter,

其中,所述操作码用于指示所述中断存储指令对装置中断退出时所进行的处理为中断存储处理,所述存储参数用于指示所述装置中断退出时需要存储的数据。Wherein, the operation code is used to indicate that the processing performed by the interrupt storage instruction when the device is interrupted and exited is an interrupted storage process, and the storage parameter is used to indicate the data to be stored when the device is interrupted and exited.

在一些实施例中,所述电子设备包括数据处理装置、机器人、电脑、打印机、扫描仪、平板电脑、智能终端、手机、行车记录仪、导航仪、传感器、摄像头、服务器、云端服务器、相机、摄像机、投影仪、手表、耳机、移动存储、可穿戴设备、交通工具、家用电器、和/或医疗设备。In some embodiments, the electronic device includes a data processing device, a robot, a computer, a printer, a scanner, a tablet computer, a smart terminal, a mobile phone, a driving recorder, a navigator, a sensor, a camera, a server, a cloud server, a camera, Cameras, projectors, watches, headphones, mobile storage, wearables, vehicles, home appliances, and/or medical equipment.

在一些实施例中,所述交通工具包括飞机、轮船和/或车辆;所述家用电器包括电视、空调、微波炉、冰箱、电饭煲、加湿器、洗衣机、电灯、燃气灶、油烟机;所述医疗设备包括核磁共振仪、B超仪和/或心电图仪。In some embodiments, the vehicles include airplanes, ships and/or vehicles; the household appliances include televisions, air conditioners, microwave ovens, refrigerators, rice cookers, humidifiers, washing machines, electric lights, gas stoves, and range hoods; the medical Equipment includes MRI machines, ultrasound machines and/or electrocardiographs.

本公开实施例所提供的中断存储指令处理方法、装置及相关产品,该装置包括控制模块,控制模块包括:参数获取子模块根据获取到的中断存储指令的操作域和操作码,确定进行响应中断退出的处理所需的存储参数;中断存储子模块在执行到中断存储指令时,控制装置中断退出,并根据存储参数进行数据存储。本公开实施例所提供的中断存储指令处理方法、装置及相关产品的适用范围广,对中断存储指令的处理效率高、处理速度快,能够高效、快速地对装置的中断退出做出响应,且提高了对数据进行运算的效率和速度。In the interrupt storage instruction processing method, device, and related products provided by the embodiments of the present disclosure, the device includes a control module, and the control module includes: a parameter acquisition sub-module determines to respond to the interrupt according to the acquired operation domain and operation code of the interrupt storage instruction The storage parameters required for the exit processing; when the interrupt storage sub-module executes the interrupt storage instruction, the control device interrupts the exit, and performs data storage according to the storage parameters. The interrupt storage instruction processing method, device, and related products provided by the embodiments of the present disclosure have a wide range of applications, have high processing efficiency and fast processing speed for interrupt storage instructions, and can efficiently and quickly respond to the interrupt exit of the device, and Improve the efficiency and speed of data operations.

根据下面参考附图对示例性实施例的详细说明,本公开的其它特征及方面将变得清楚。Other features and aspects of the present disclosure will become apparent from the following detailed description of exemplary embodiments with reference to the accompanying drawings.

附图说明Description of drawings

包含在说明书中并且构成说明书的一部分的附图与说明书一起示出了本公开的示例性实施例、特征和方面,并且用于解释本公开的原理。The accompanying drawings, which are incorporated in and constitute a part of the specification, illustrate exemplary embodiments, features, and aspects of the disclosure, and together with the description, serve to explain the principles of the disclosure.

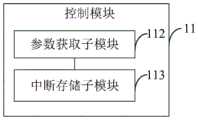

图1示出根据本公开一实施例的中断存储指令处理装置的框图。FIG. 1 shows a block diagram of an interrupt storage instruction processing apparatus according to an embodiment of the present disclosure.

图2a、图2b示出根据本公开一实施例的中断存储指令处理装置的框图。2a and 2b show block diagrams of an interrupt storage instruction processing apparatus according to an embodiment of the present disclosure.

图2c-图2f示出根据本公开一实施例的中断存储指令处理装置中运算模块的框图。2c-2f show block diagrams of operation modules in an interrupt storage instruction processing apparatus according to an embodiment of the present disclosure.

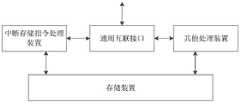

图3a、图3b示出根据本公开一实施例的中断存储指令处理装置的应用场景的示意图。3a and 3b are schematic diagrams illustrating application scenarios of an apparatus for processing interrupt storage instructions according to an embodiment of the present disclosure.

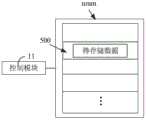

图4a、图4b示出根据本公开一实施例的组合处理装置的框图。4a and 4b illustrate block diagrams of a combined processing apparatus according to an embodiment of the present disclosure.

图5示出根据本公开一实施例的板卡的结构示意图。FIG. 5 shows a schematic structural diagram of a board according to an embodiment of the present disclosure.

图6示出根据本公开一实施例的中断存储指令处理方法的流程图。FIG. 6 shows a flowchart of a method for processing an interrupt storage instruction according to an embodiment of the present disclosure.

具体实施方式Detailed ways

以下将参考附图详细说明本公开的各种示例性实施例、特征和方面。附图中相同的附图标记表示功能相同或相似的元件。尽管在附图中示出了实施例的各种方面,但是除非特别指出,不必按比例绘制附图。Various exemplary embodiments, features and aspects of the present disclosure will be described in detail below with reference to the accompanying drawings. The same reference numbers in the figures denote elements that have the same or similar functions. While various aspects of the embodiments are shown in the drawings, the drawings are not necessarily drawn to scale unless otherwise indicated.

在这里专用的词“示例性”意为“用作例子、实施例或说明性”。这里作为“示例性”所说明的任何实施例不必解释为优于或好于其它实施例。The word "exemplary" is used exclusively herein to mean "serving as an example, embodiment, or illustration." Any embodiment described herein as "exemplary" is not necessarily to be construed as preferred or advantageous over other embodiments.

另外,为了更好的说明本公开,在下文的具体实施方式中给出了众多的具体细节。本领域技术人员应当理解,没有某些具体细节,本公开同样可以实施。在一些实例中,对于本领域技术人员熟知的方法、手段、元件和电路未作详细描述,以便于凸显本公开的主旨。In addition, in order to better illustrate the present disclosure, numerous specific details are given in the following detailed description. It will be understood by those skilled in the art that the present disclosure may be practiced without certain specific details. In some instances, methods, means, components and circuits well known to those skilled in the art have not been described in detail so as not to obscure the subject matter of the present disclosure.

图1示出根据本公开一实施例的中断存储指令处理装置的框图。如图1所示,该装置包括控制模块11,控制模块11包括参数获取子模块112和中断存储子模块113。FIG. 1 shows a block diagram of an interrupt storage instruction processing apparatus according to an embodiment of the present disclosure. As shown in FIG. 1 , the apparatus includes a

参数获取子模块112,根据获取到的中断存储指令的操作域和操作码,确定进行响应中断退出的处理所需的存储参数。其中,操作码用于指示中断存储指令对装置中断退出时所进行的处理为中断存储处理。存储参数用于指示装置中断退出时需要存储的数据。中断存储处理包括装置中断退出以及根据存储参数进行数据存储。The

中断存储子模块113,在执行到中断存储指令时,控制装置中断退出,并根据存储参数进行数据存储。In the

在本实施例中,在对装置进行调试、测试等处理的过程中,根据中断存储指令,能够实时将装置中断退出时,能够对可以表明装置的运行状态的数据进行存储,也即根据存储参数进行数据存储。以便于相关人员可以基于根据存储参数所存储的数据,确定调试和测试的结果,以及根据存储的数据对装置的运行状况进行分析。In this embodiment, in the process of debugging and testing the device, according to the interrupt storage instruction, when the device can be interrupted and exited in real time, the data that can indicate the operating state of the device can be stored, that is, according to the storage parameter for data storage. So that the relevant personnel can determine the results of debugging and testing based on the data stored according to the storage parameters, and analyze the operating status of the device according to the stored data.

在本实施例中,可以根据存储参数确定需要存储的数据,并将确定的需要存储的数据存储到装置的内存中,或者存储到其他位置,本公开对此不作限制。In this embodiment, the data to be stored may be determined according to the storage parameter, and the determined data to be stored may be stored in the memory of the device, or stored in another location, which is not limited in the present disclosure.

在本实施例中,控制模块可以通过数据输入输出单元获得指令和数据,该数据输入输出单元可以为一个或多个数据I/O接口或I/O引脚。In this embodiment, the control module may obtain instructions and data through a data input and output unit, and the data input and output unit may be one or more data I/O interfaces or I/O pins.

在本实施例中,操作码可以是计算机程序中所规定的要执行操作的那一部分指令或字段(通常用代码表示),是指令序列号,用来告知执行指令的装置具体需要执行哪一条指令。操作域可以是执行对应的指令所需的所有数据的来源,执行对应的指令所需的所有数据包括待运算数据、存储参数以及对应的运算方法等等。对于一个中断存储指令其必须包括操作码和操作域。In this embodiment, the operation code may be the part of the instruction or field (usually represented by code) specified in the computer program to perform the operation, and the instruction sequence number, which is used to inform the device that executes the instruction which instruction needs to be executed. . The operation domain may be the source of all data required to execute the corresponding instruction, and all the data required to execute the corresponding instruction includes data to be operated, storage parameters, and corresponding operation methods, and so on. For an interrupt store instruction it must include the opcode and operation field.

应当理解的是,本领域技术人员可以根据需要对中断存储指令的指令格式以及所包含的操作码和操作域进行设置,本公开对此不作限制。It should be understood that those skilled in the art can set the instruction format of the interrupt storage instruction and the included operation codes and operation fields as required, which is not limited in the present disclosure.

在本实施例中,该装置可以包括一个或多个控制模块,可以根据实际需要对控制模块的数量进行设置,本公开对此不作限制。In this embodiment, the apparatus may include one or more control modules, and the number of control modules may be set according to actual needs, which is not limited in the present disclosure.

本公开实施例所提供的中断存储指令处理装置,该装置包括控制模块,控制模块包括:参数获取子模块根据获取到的中断存储指令的操作域和操作码,确定进行响应中断退出的处理所需的存储参数;中断存储子模块在执行到中断存储指令时,控制装置中断退出,并根据所述存储参数进行数据存储。本公开实施例所提供的中断存储指令处理方法、装置及相关产品的适用范围广,对中断存储指令的处理效率高、处理速度快,能够高效、快速地对装置的中断退出做出响应,且提高了对数据进行运算的效率和速度。The interrupt storage instruction processing device provided by the embodiment of the present disclosure includes a control module, and the control module includes: a parameter acquisition sub-module determines, according to the acquired operation domain and operation code of the interrupt storage instruction, the processing required to perform the processing of responding to the interrupt and exit. When the interrupt storage sub-module executes the interrupt storage instruction, the control device interrupts and exits, and performs data storage according to the storage parameter. The interrupt storage instruction processing method, device, and related products provided by the embodiments of the present disclosure have a wide range of applications, have high processing efficiency and fast processing speed for interrupt storage instructions, and can efficiently and quickly respond to the interrupt exit of the device, and Improve the efficiency and speed of data operations.

图2a示出根据本公开一实施例的中断存储指令处理装置的框图。在一种可能的实现方式中,如图2a所示,该装置还可以包括运算模块12。Fig. 2a shows a block diagram of an interrupt storage instruction processing apparatus according to an embodiment of the present disclosure. In a possible implementation manner, as shown in FIG. 2 a , the apparatus may further include an

控制模块11,还用于获取计算指令以及执行计算指令所需的待运算数据。The

运算模块12,用于根据计算指令对待运算数据进行运算,得到运算结果。The

其中,在执行到中断存储指令时,控制装置中断退出,可以包括:在执行到中断存储指令时,控制运算模块中断当前计算指令的执行。Wherein, when the interrupt storage instruction is executed, the control device interrupts and exits, which may include: when the interrupt storage instruction is executed, controlling the arithmetic module to interrupt the execution of the current calculation instruction.

其中,运算模块12可以包括多个运算器120。多个运算器120用于执行与计算指令的运算类型相对应的运算。Wherein, the

在该实现方式中,在执行计算指令的过程中,若控制模块执行到中断存储指令时,中断当前正在执行的计算指令的计算过程,并根据存储参数进行数据存储。In this implementation manner, in the process of executing the calculation instruction, if the control module executes the interrupt storage instruction, the calculation process of the currently executing calculation instruction is interrupted, and data storage is performed according to the storage parameter.

在该实现方式中,计算指令可以是与中断存储指令不同的、对标量、向量、矩阵、张量等数据进行算术运算、逻辑运算等运算的指令,例如,标量计算指令、卷积计算指令等,本领域技术人员可以根据实际需要对计算指令进行设置,本公开对此不作限制。在该实现方式中,控制模块还用于对计算指令进行解析,得到计算指令的操作码和操作域,并根据操作码和操作域获取待运算数据。In this implementation, the calculation instruction may be an instruction that is different from the interrupt storage instruction and performs arithmetic operations, logical operations and other operations on data such as scalars, vectors, matrices, and tensors, for example, scalar calculation instructions, convolution calculation instructions, etc. , those skilled in the art can set the calculation instruction according to actual needs, which is not limited in the present disclosure. In this implementation manner, the control module is further configured to parse the calculation instruction, obtain the operation code and operation field of the calculation instruction, and obtain the data to be calculated according to the operation code and the operation field.

在该实现方式中,运算器可以包括加法器、除法器、乘法器、比较器等能够对数据进行算术运算、逻辑运算等运算的运算器。可以根据所需进行的运算的数据量的大小、运算类型、对数据进行运算的处理速度、效率等要求对运算器的种类及数量进行设置,本公开对此不作限制。In this implementation manner, the operator may include an adder, a divider, a multiplier, a comparator, and other operators capable of performing arithmetic operations, logical operations, and other operations on data. The type and quantity of arithmetic units can be set according to the size of the data volume of the operation to be performed, the type of operation, the processing speed and efficiency of the operation on the data, etc., which are not limited in the present disclosure.

图2b示出根据本公开一实施例的中断存储指令处理装置的框图。在一种可能的实现方式中,如图2b所示,运算模块12可以包括主运算子模块121和多个从运算子模块122。主运算子模块121可以包括多个运算器,和/或从运算子模块122中可以包括多个运算器(图中未示出)。FIG. 2b shows a block diagram of an interrupt storage instruction processing apparatus according to an embodiment of the present disclosure. In a possible implementation manner, as shown in FIG. 2 b , the

控制模块11,还用于解析计算指令得到多个运算指令,并将待运算数据和多个运算指令发送至主运算子模块121。The

主运算子模块121,用于对待运算数据执行前序处理,以及与多个从运算子模块122进行数据和运算指令的传输。The

从运算子模块122,用于根据从主运算子模块121传输的数据和运算指令并行执行中间运算得到多个中间结果,并将多个中间结果传输给主运算子模块122。The

主运算子模块121,还用于对多个中间结果执行后续处理,得到运算结果。The

在该实现方式中,在计算指令为针对标量、向量数据所进行的运算时,装置可以控制主运算子模块利用其中的运算器进行与计算指令相对应的运算。在计算指令为针对矩阵、张量等维度大于或等于2的数据进行运算时,装置可以控制从运算子模块利用其中的运算器进行与计算指令相对应的运算。In this implementation manner, when the calculation instruction is an operation performed on scalar or vector data, the apparatus can control the main operation sub-module to use the operator therein to perform an operation corresponding to the calculation instruction. When the calculation instruction is to perform operations on data whose dimensions are greater than or equal to 2, such as matrices and tensors, the apparatus may control the operation sub-module to perform operations corresponding to the calculation instructions using the operators therein.

需要说明的是,本领域技术人员可以根据实际需要对主运算子模块和多个从运算子模块之间的连接方式进行设置,以实现对运算模块的架构设置,例如,运算模块的架构可以是“H”型架构、阵列型架构、树型架构等,本公开对此不作限制。It should be noted that those skilled in the art can set the connection mode between the main operation sub-module and multiple slave operation sub-modules according to actual needs, so as to realize the architecture setting of the operation module. For example, the architecture of the operation module can be "H"-type architecture, array-type architecture, tree-type architecture, etc., are not limited in the present disclosure.

图2c示出根据本公开一实施例的中断存储指令处理装置中运算模块的框图。在一种可能的实现方式中,如图2c所示,运算模块12还可以包括一个或多个分支运算子模块123,该分支运算子模块123用于转发主运算子模块121和从运算子模块122之间的数据和/或运算指令。其中,主运算子模块121与一个或多个分支运算子模块123连接。这样,运算模块中的主运算子模块、分支运算子模块和从运算子模块之间采用“H”型架构连接,通过分支运算子模块转发数据和/或运算指令,节省了对主运算子模块的资源占用,进而提高指令的处理速度。FIG. 2c shows a block diagram of an operation module in an interrupt storage instruction processing apparatus according to an embodiment of the present disclosure. In a possible implementation manner, as shown in FIG. 2c, the

图2d示出根据本公开一实施例的中断存储指令处理装置中运算模块的框图。在一种可能的实现方式中,如图2d所示,多个从运算子模块122呈阵列分布。FIG. 2d shows a block diagram of an operation module in an interrupt storage instruction processing apparatus according to an embodiment of the present disclosure. In a possible implementation manner, as shown in FIG. 2d , a plurality of

每个从运算子模块122与相邻的其他从运算子模块122连接,主运算子模块121连接多个从运算子模块122中的k个从运算子模块122,k个从运算子模块122为:第1行的n个从运算子模块122、第m行的n个从运算子模块122以及第1列的m个从运算子模块122。Each

其中,如图2d所示,k个从运算子模块仅包括第1行的n个从运算子模块、第m行的n个从运算子模块以及第1列的m个从运算子模块,即该k个从运算子模块为多个从运算子模块中直接与主运算子模块连接的从运算子模块。其中,k个从运算子模块,用于在主运算子模块以及多个从运算子模块之间的数据以及指令的转发。这样,多个从运算子模块呈阵列分布,可以提高主运算子模块向从运算子模块发送数据和/或运算指令速度,进而提高指令的处理速度。Among them, as shown in Figure 2d, the k slave operation submodules only include n slave operation submodules in the first row, n slave operation submodules in the mth row, and m slave operation submodules in the first column, that is, The k slave operation submodules are slave operation submodules that are directly connected to the master operation submodule among the plurality of slave operation submodules. The k slave operation submodules are used for data and instruction forwarding between the master operation submodule and a plurality of slave operation submodules. In this way, the plurality of slave operation sub-modules are distributed in an array, which can improve the speed at which the master operation sub-module sends data and/or operation instructions to the slave operation sub-modules, thereby increasing the instruction processing speed.

图2e示出根据本公开一实施例的中断存储指令处理装置中运算模块的框图。在一种可能的实现方式中,如图2e所示,运算模块还可以包括树型子模块124。该树型子模块124包括一个根端口401和多个支端口402。根端口401与主运算子模块121连接,多个支端口402与多个从运算子模块122分别连接。其中,树型子模块124具有收发功能,用于转发主运算子模块121和从运算子模块122之间的数据和/或运算指令。这样,通过树型子模块的作用使得运算模块呈树型架构连接,并利用树型子模块的转发功能,可以提高主运算子模块向从运算子模块发送数据和/或运算指令速度,进而提高指令的处理速度。FIG. 2e shows a block diagram of an operation module in an interrupt storage instruction processing apparatus according to an embodiment of the present disclosure. In a possible implementation manner, as shown in FIG. 2e , the operation module may further include a tree-

在一种可能的实现方式中,树型子模块124可以为该装置的可选结果,其可以包括至少一层节点。节点为具有转发功能的线结构,节点本身不具备运算功能。最下层的节点与从运算子模块连接,以转发主运算子模块121和从运算子模块122之间的数据和/或运算指令。特殊地,如树型子模块具有零层节点,该装置则无需树型子模块。In a possible implementation manner, the tree-

在一种可能的实现方式中,树型子模块124可以包括n叉树结构的多个节点,n叉树结构的多个节点可以具有多个层。In a possible implementation manner, the

举例来说,图2f示出根据本公开一实施例的中断存储指令处理装置中运算模块的框图。如图2f所示,n叉树结构可以是二叉树结构,树型子模块包括2层节点01。最下层节点01与从运算子模块122连接,以转发主运算子模块121和从运算子模块122之间的数据和/或运算指令。For example, FIG. 2f shows a block diagram of an operation module in an interrupt storage instruction processing apparatus according to an embodiment of the present disclosure. As shown in FIG. 2f , the n-ary tree structure may be a binary tree structure, and the tree-type sub-module includes 2-layer nodes 01 . The lowermost node 01 is connected to the slave operation sub-module 122 to forward data and/or operation instructions between the

在该实现方式中,n叉树结构还可以是三叉树结构等,n为大于或等于2的正整数。本领域技术人员可以根据需要对n叉树结构中的n以及n叉树结构中节点的层数进行设置,本公开对此不作限制。In this implementation manner, the n-ary tree structure may also be a ternary tree structure, etc., and n is a positive integer greater than or equal to 2. Those skilled in the art can set n in the n-ary tree structure and the number of layers of nodes in the n-ary tree structure as required, which is not limited in the present disclosure.

在一种可能的实现方式中,存储参数可以包括存储空间类型和存储空间标识。其中,操作码还可以用于指示存储空间类型,操作域可以包括存储空间标识。其中,根据存储参数进行数据存储,可以包括:In a possible implementation manner, the storage parameter may include a storage space type and a storage space identifier. Wherein, the operation code may also be used to indicate the storage space type, and the operation field may include the storage space identifier. Among them, data storage according to storage parameters may include:

确定与存储空间类型、存储空间标识相匹配的至少一个目标存储空间,并存储目标存储空间中的数据。Determine at least one target storage space matching the storage space type and storage space identifier, and store the data in the target storage space.

在该实现方式中,目标存储空间可以是装置的内存,如缓存、寄存器等位于装置中、或与装置的运行相关的内部存储空间。存储空间类型可以表明存储空间的位置、存储速度等信息。可以为不同类型的存储空间设置在中断存储指令中的代码,例如,可以将寄存器的代码设置为“gpr”,可以将NRAM的代码设置为“nram”。其中,缓存可以包括NRAM(NeuronRandom Access Memory)神经元随机存取存储器,其为专门用于存储神经元的存储器。装置的内存可以用于存储执行计算指令所需的待运算数据等,本公开对此不作限制。In this implementation manner, the target storage space may be the memory of the device, such as caches, registers, etc. located in the device, or an internal storage space related to the operation of the device. The storage space type can indicate information such as the location and storage speed of the storage space. The code in the interrupt store instruction can be set for different types of memory space, for example, the code of the register can be set to "gpr", and the code of the NRAM can be set to "nram". The cache may include NRAM (Neuron Random Access Memory) neuron random access memory, which is a memory specially used for storing neurons. The memory of the device may be used to store the data to be calculated and the like required to execute the calculation instruction, which is not limited in the present disclosure.

在该实现方式中,储空间标识可以存储空间在装置中的编号、名称以及存储空间的类型等能够表征该存储空间的信息。In this implementation manner, the storage space identifier can be information that can characterize the storage space, such as the number, name, and type of the storage space in the device.

在一种可能的实现方式中,在目标存储空间为多个时,每个目标存储空间中的数据为一组待存储数据,多组待存储数据对应至少一种数据格式。In a possible implementation manner, when there are multiple target storage spaces, the data in each target storage space is a group of data to be stored, and the multiple groups of data to be stored correspond to at least one data format.

在该实现方式中,对目标存储空间中所存储的数据的数据格式不作限制,同一组待存储数据的数据格式相同,多组待存储数据之间的数据格式可以相同,也可以不同。数据格式可以包括数据类型和数据长度中的至少一种。例如,目标存储空间中所存储的数据可以为16位整数型数据,32位无符号整数型数据等。举例来说,假定装置中断退出后,根据存储参数确定需存储寄存器1、寄存器2和寄存器3中的数据,其中,寄存器1中的数据以16位整数型数据格式存储、寄存器2中的数据以32位无符号整数型数据格式存储和寄存器3中的数据以8位整数型数据格式存储。中断存储模块可以对寄存器1中16位整数型的数据、寄存器2中32位无符号整数型的数据和寄存器3中8位整数型的数据进行存储。In this implementation, the data format of the data stored in the target storage space is not limited. The data format of the same group of data to be stored is the same, and the data formats of multiple groups of data to be stored may be the same or different. The data format may include at least one of a data type and a data length. For example, the data stored in the target storage space may be 16-bit integer data, 32-bit unsigned integer data, and the like. For example, it is assumed that after the device is interrupted and exited, the data in register 1, register 2 and register 3 are determined according to the storage parameters, wherein the data in register 1 is stored in a 16-bit integer data format, and the data in register 2 is stored in the format of 16-bit integer data. The 32-bit unsigned integer data format is stored and the data in register 3 is stored in the 8-bit integer data format. The interrupt storage module can store the data of 16-bit integer type in register 1, the data of 32-bit unsigned integer type in register 2 and the data of 8-bit integer type in register 3.

在该实现方式中,中断存储模块在进行数据存储的过程中,可以直接按照数据在目标存储空间中的数据格式进行数据存储,也可以将目标存储空间中数据统一转化为指定数据格式后进行存储。In this implementation, in the process of data storage, the interrupt storage module can directly store the data according to the data format of the data in the target storage space, or can store the data in the target storage space after uniformly converting it into a specified data format. .

在该实现方式中,中断存储模块可以存储目标存储空间中的全部数据,也可以存储目标存储空间中的部分数据,本公开对此不作限制。In this implementation manner, the interrupt storage module may store all the data in the target storage space, or may store part of the data in the target storage space, which is not limited in the present disclosure.

在一种可能的实现方式中,存储参数可以包括存储空间标识和待存储数据地址。其中,操作码还可以用于指示存储空间标识,操作域可以包括待存储数据地址。其中,根据存储参数进行数据存储,可以包括:In a possible implementation manner, the storage parameter may include a storage space identifier and an address of data to be stored. Wherein, the operation code may also be used to indicate the storage space identifier, and the operation field may include the address of the data to be stored. Among them, data storage according to storage parameters may include:

确定与存储空间标识相对应的目标存储空间,并从目标存储空间的待存储数据地址中获取待存储数据,存储待存储数据。The target storage space corresponding to the storage space identifier is determined, and the data to be stored is acquired from the address of the data to be stored in the target storage space, and the data to be stored is stored.

在一种可能的实现方式中,在与装置相关的存储空间中仅有一个与存储空间标识对应的存储空间、且该存储空间的类型也仅为一个时,存储参数也可以包括存储空间类型和待存储数据地址。其中,操作码还可以用于指示存储空间类型,操作域可以包括待存储数据地址。其中,根据存储参数进行数据存储,可以包括:确定与存储空间类型相对应的目标存储空间,并从目标存储空间的待存储数据地址中获取待存储数据,存储待存储数据。In a possible implementation manner, when there is only one storage space corresponding to the storage space identifier in the storage space related to the device, and the type of the storage space is also only one, the storage parameter may also include the storage space type and The address of the data to be stored. Wherein, the operation code may also be used to indicate the storage space type, and the operation field may include the address of the data to be stored. Wherein, performing data storage according to the storage parameters may include: determining a target storage space corresponding to the storage space type, acquiring the data to be stored from the address of the data to be stored in the target storage space, and storing the data to be stored.

在该实现方式中,当根据待存储数据地址和存储空间类型可以确定唯一的待存储数据时,存储参数也可以包括存储空间类型和待存储数据地址。In this implementation manner, when the unique data to be stored can be determined according to the address of the data to be stored and the type of the storage space, the storage parameter may also include the type of the storage space and the address of the data to be stored.

在一种可能的实现方式中,存储参数还可以包括目标存储量。其中,操作域还可以包括目标存储量。其中,从目标存储空间的待存储数据地址中获取待存储数据,存储待存储数据,可以包括:In a possible implementation manner, the storage parameter may also include a target storage amount. Wherein, the operation domain may also include the target storage amount. Wherein, obtaining the data to be stored from the address of the data to be stored in the target storage space, and storing the data to be stored, may include:

从目标存储空间的待存储数据地址中获取数据量为目标存储量的待存储数据,存储待存储数据。The to-be-stored data whose data amount is the target storage amount is obtained from the to-be-stored data address of the target storage space, and the to-be-stored data is stored.

在一种可能的实现方式中,可以设置默认目标存储量。在根据中断存储指令的操作域无法确定目标存储量时,可以将默认目标存储量确定为对应当前中断存储指令的目标存储量,进而从目标存储空间的待存储数据地址中获取数据量为目标存储量(也即默认目标存储量)的待存储数据。In one possible implementation, a default target storage amount can be set. When the target storage amount cannot be determined according to the operation domain of the interrupt storage instruction, the default target storage amount can be determined as the target storage amount corresponding to the current interrupt storage instruction, and then the data amount obtained from the data address to be stored in the target storage space is the target storage amount The amount of data to be stored (that is, the default target storage amount).

应当理解的是,本领域技术人员可以根据实际需要对接收中断存储指令的运算模块进行设置,本公开对此不作限制。It should be understood that those skilled in the art can set the operation module for receiving the interrupt storage instruction according to actual needs, which is not limited in the present disclosure.

在一种可能的实现方式中,操作域中可以包括用于指示中断存储空间的标识。其中,中断存储子模块113可以将根据存储参数获取的所需存储的数据存入与中断存储空间的标识相对应的中断存储空间中。In a possible implementation manner, the operation domain may include an identifier for indicating the interruption of the storage space. The interrupt

在一种可能的实现方式中,中断存储空间可以包括装置的片外存储和/或片上存储。片外存储可以包括至少一个DDR(也即DDR SDRAM,英文:Double Data Rate SDRAM,双倍速率同步动态随机存储器),DDR可以包括至少一个LDRAM(Local DRAM,本地动态随机存储器)。片上存储可以包括寄存器、NRAM中的至少一种,片上存储中每一种存储空间(寄存器和/或NRAM)可以包括至少一个。片外存储的可用存储空间小于或等于指定存储容量。In one possible implementation, the interrupt storage space may include off-chip storage and/or on-chip storage of the device. The off-chip storage may include at least one DDR (ie, DDR SDRAM, English: Double Data Rate SDRAM, double-rate synchronous dynamic random access memory), and the DDR may include at least one LDRAM (Local DRAM, local dynamic random access memory). The on-chip storage may include at least one of registers and NRAM, and each storage space (register and/or NRAM) in the on-chip storage may include at least one. The available storage space of off-chip storage is less than or equal to the specified storage capacity.

在该实现方式中,片外存储的可用存储空间可以是片外存储中、可以供装置在执行中断存储指令的过程中进行中断退出后的数据存储的存储空间。其中,向量数据可以存储于NRAM、LDRAM中。可以预先根据装置所执行的数据运算过程对指定存储容量进行设置,例如,1024KB等,本公开对此不作限制。In this implementation manner, the available storage space of the off-chip storage may be a storage space in the off-chip storage that can be used for data storage after the device is interrupted and exited in the process of executing the interrupt storage instruction. Among them, the vector data can be stored in NRAM, LDRAM. The specified storage capacity may be set in advance according to the data operation process performed by the device, for example, 1024KB, etc., which is not limited in the present disclosure.

在该实现方式中,可以通过在操作域中中断存储空间的标识可以包括中断存储空间的编号、名称、首地址等能够表征中断存储空间的参数,本公开对此不作限制。In this implementation manner, the identifier of the interrupt storage space in the operation domain may include parameters that can characterize the interrupt storage space, such as the number, name, and first address of the interrupt storage space, which is not limited in the present disclosure.

在一种可能的实现方式中,若操作域中不包含中断存储空间,可以根据预先设置的默认存储方式,对不同种类的数据进行存储,例如,可以默认设置将标量数据存储到寄存器中,将向量数据存储到NRAM中。本领域技术人员可以根据实际需要对默认存储方式进行设置,本公开对此不作限制。In a possible implementation, if the operation domain does not contain interrupt storage space, different types of data can be stored according to the preset default storage mode. For example, the scalar data can be stored in the register by default, and the Vector data is stored in NRAM. Those skilled in the art can set the default storage mode according to actual needs, which is not limited in the present disclosure.

在一种可能的实现方式中,如图2a所示,该装置还可以包括存储模块13。存储模块13可以包括片外存储和/或片上存储,片上存储可以用于存储待运算数据。其中,片上存储可以包括寄存器和缓存中的至少一种。缓存用于存储待运算数据,缓存包括至少一个NRAM。寄存器用于存储待运算数据中的标量数据。其中,待运算数据包括标量数据、向量数据、张量数据等类型的数据。待运算数据可以是机器学习中进行运算所使用的数据。机器学习运算可以包括神经网络运算。In a possible implementation manner, as shown in FIG. 2a , the apparatus may further include a

在一种可能的实现方式中,缓存可以包括神经元缓存。神经元缓存可以用于存储待运算数据中的神经元数据。神经元数据可以是进行神经网络运算所使用的数据,如向量数据等。In one possible implementation, the cache may include a neuron cache. The neuron cache can be used to store neuron data in the data to be calculated. Neuron data can be data used for neural network operations, such as vector data.

在一种可能的实现方式中,该装置还可以包括直接内存访问模块,用于从存储模块中读取或者存储数据。In a possible implementation manner, the apparatus may further include a direct memory access module for reading or storing data from the storage module.

在一种可能的实现方式中,如图2a所示,控制模块11可以包括指令存储子模块114、指令处理子模块115和队列存储子模块116。In a possible implementation manner, as shown in FIG. 2 a , the

指令存储子模块114用于存储中断存储指令和计算指令。The

指令处理子模块115用于对中断存储指令和计算指令分别进行解析,得到对应的操作码和操作域。也即对中断存储指令进行解析得到中断存储指令的操作码和操作域,以及对计算指令进行解析得到计算指令的操作码和操作域。The

队列存储子模块116用于存储指令队列,指令队列包括按照执行顺序依次排列的多个待执行指令,多个待执行指令可以包括中断存储指令和计算指令。The

在该实现方式中,可以根据待执行指令的接收时间、优先级别等对多个待执行指令的执行顺序进行排列获得指令队列,以便于根据指令队列依次执行多个待执行指令。In this implementation manner, the execution order of the plurality of to-be-executed commands can be arranged according to the receiving time and priority level of the to-be-executed commands to obtain the command queue, so as to execute the plurality of to-be-executed commands in sequence according to the command queue.

在一种可能的实现方式中,如图2a所示,控制模块11还可以包括依赖关系处理子模块117。依赖关系处理子模块117,用于在确定多个待执行命令中的第一待执行指令与第一待执行指令之前的第零待执行指令存在关联关系时,将第一待执行指令缓存在指令存储子模块114中,在第零待执行指令执行完毕后,从指令存储子模块114中提取第一待执行指令发送至运算模块12。In a possible implementation manner, as shown in FIG. 2 a , the

其中,第一待执行指令与第一待执行指令之前的第零待执行指令存在关联关系包括:存储第一待执行指令所需数据的第一存储地址区间与存储第零待执行指令所需数据的第零存储地址区间具有重叠的区域。反之,第一待执行指令与第一待执行指令之前的第零待执行指令之间没有关联关系可以是第一存储地址区间与第零存储地址区间没有重叠区域。Wherein, the relationship between the first instruction to be executed and the zeroth instruction to be executed before the first instruction to be executed includes: a first storage address range for storing data required by the first instruction to be executed and data required for storing the zeroth instruction to be executed The zeroth memory address range of has overlapping regions. Conversely, if there is no association between the first instruction to be executed and the zeroth instruction to be executed before the first instruction to be executed, it may be that the first storage address interval and the zeroth storage address interval have no overlapping area.

通过这种方式,可以根据第一待执行指令与第一待执行指令之前的第零待执行指令之间的依赖关系,使得在先的第零待执行指令执行完毕之后,再执行在后的第一待执行指令,保证运算结果的准确性。In this way, according to the dependency between the first to-be-executed instruction and the zeroth to-be-executed instruction before the first to-be-executed instruction, after the previous zeroth to-be-executed instruction is executed, the subsequent zeroth to-be-executed instruction is executed. Once the instruction to be executed, the accuracy of the operation result is guaranteed.

在一种可能的实现方式中,中断存储指令的指令格式可以是:In a possible implementation, the instruction format of the interrupt store instruction may be:

breakdump.type addrSpace sign0breakdump.type addrSpace sign0

其中,breakdump.type为中断存储指令的操作码。sign0、addrSpace为中断存储指令的操作域。breakdump.type中的type表示存储空间类型。sign0表示存储空间标识,其中,在存储空间为多个时,存储空间标识可以为多个。addrSpace为中断存储空间的标识。其表示:在装置中断退出时,将存储空间类型type相对应的、标识为存储空间标识sign0的存储空间确定为目标存储空间,并将目标存储空间中的全部数据存储至与中断存储空间的标识addrSpace相对应的中断存储空间中。type可以是gpr。Among them, breakdump.type is the opcode of the interrupt storage instruction. sign0 and addrSpace are the operation fields of the interrupt storage instruction. The type in breakdump.type represents the storage space type. sign0 represents a storage space identifier, wherein when there are multiple storage spaces, there may be multiple storage space identifiers. addrSpace is the identifier of the interrupt storage space. It means: when the device is interrupted and exited, the storage space corresponding to the storage space type type and identified as the storage space identifier sign0 is determined as the target storage space, and all the data in the target storage space is stored to the identifier of the interrupted storage space. In the interrupt storage space corresponding to addrSpace. type can be gpr.

举例来说,当需要存储寄存器中的数据时,假定需要存储数据的寄存器为6个,其6个寄存器的存储空间标识分别为sign0、sign1、sign2、sign3、sign4、sign5,其对应的中断存储指令的指令格式可以为:breakdump.gpr nram0sign0sign1sign2sign3sign4sign5。其表示:在装置中断退出时,将存储空间标识为sign0、sign1、sign2、sign3、sign4、sign5的6个寄存器中的全部数据存储在与中断存储空间的标识nram0对应的中断存储空间中。For example, when the data in the register needs to be stored, it is assumed that there are 6 registers that need to store the data, and the storage space identifiers of the 6 registers are sign0, sign1, sign2, sign3, sign4, sign5, and the corresponding interrupt storage The command format of the command can be: breakdump.gpr nram0sign0sign1sign2sign3sign4sign5. It means that when the device is interrupted and exits, all data in the six registers whose storage spaces are identified as sign0, sign1, sign2, sign3, sign4, and sign5 are stored in the interrupt storage space corresponding to the identifier nram0 of the interrupt storage space.

在一种可能的实现方式中,中断存储指令的指令格式还可以是:In a possible implementation manner, the instruction format of the interrupt storage instruction may also be:

breakdump.sign addrSpace src sizebreakdump.sign addrSpace src size

其中,breakdump.sign为中断存储指令的操作码。addrSpace、src、size为中断存储指令的操作域。src表示待存储数据地址。size表示目标存储量。addrSpace为中断存储空间的标识。其表示:在装置中断退出时,确定存储空间标识sign相对应目标存储空间,并从目标存储空间的待存储数据地址src中获取数据量为目标存储量size的待存储数据,将待存储数据存储至与中断存储空间的标识addrSpace对应的中断存储空间中。Among them, breakdump.sign is the opcode of the interrupt storage instruction. addrSpace, src, and size are the operation fields of the interrupt storage instruction. src represents the address of the data to be stored. size indicates the target storage amount. addrSpace is the identifier of the interrupt storage space. It means: when the device is interrupted and exits, determine the storage space identifier sign corresponding to the target storage space, and obtain the to-be-stored data whose data volume is the target storage volume size from the to-be-stored data address src of the target storage space, and store the to-be-stored data. into the interrupt storage space corresponding to the identifier addrSpace of the interrupt storage space.

在一种可能的实现方式中,在需要存储内存如NRAM中的数据时,存储参数可以包括存储空间类型、待存储数据地址和目标存储量。中断存储指令的指令格式可以是:breakdump.nram ldram0src size。其表示:在装置中断退出时,从NRAM的待存储数据地址src中获取数据量为目标存储量size的待存储数据,并将待存储数据存储至与中断存储空间的标识ldram0对应的中断存储空间中。In a possible implementation manner, when data in a memory such as NRAM needs to be stored, the storage parameters may include a storage space type, an address of data to be stored, and a target storage amount. The instruction format of the interrupt storage instruction can be: breakdump.nram ldram0src size. It means: when the device is interrupted and exits, the data to be stored whose data amount is the target storage size size is obtained from the address src of the data to be stored in the NRAM, and the data to be stored is stored in the interrupt storage space corresponding to the identifier ldram0 of the interrupt storage space. middle.

在一种可能的实现方式中,该装置可以设置于图形处理器(Graphics ProcessingUnit,简称GPU)、中央处理器(Central Processing Unit,简称CPU)和嵌入式神经网络处理器(Neural-network Processing Unit,简称NPU)的一种或多种之中。In a possible implementation manner, the apparatus may be provided in a graphics processing unit (Graphics Processing Unit, GPU for short), a central processing unit (Central Processing Unit, CPU for short), and an embedded neural-network processing unit (Neural-network Processing Unit, abbreviated as NPU) among one or more of them.

需要说明的是,尽管以上述实施例作为示例介绍了中断存储指令处理装置如上,但本领域技术人员能够理解,本公开应不限于此。事实上,用户完全可根据个人喜好和/或实际应用场景灵活设定各模块,只要符合本公开的技术方案即可。It should be noted that although the above embodiments are used as examples to introduce the interrupt storage instruction processing apparatus as above, those skilled in the art can understand that the present disclosure should not be limited thereto. In fact, the user can flexibly set each module according to personal preferences and/or actual application scenarios, as long as it conforms to the technical solutions of the present disclosure.

应用示例Application example

以下结合“利用中断存储指令处理装置执行中断存储指令”作为一个示例性应用场景,给出根据本公开实施例的应用示例,以便于理解中断存储指令处理装置的流程。本领域技术人员应理解,以下应用示例仅仅是出于便于理解本公开实施例的目的,不应视为对本公开实施例的限制In the following, an application example according to an embodiment of the present disclosure is given in conjunction with "using an interrupt storage instruction processing apparatus to execute an interrupt storage instruction" as an exemplary application scenario, so as to facilitate understanding of the flow of the interrupt storage instruction processing apparatus. Those skilled in the art should understand that the following application examples are only for the purpose of facilitating the understanding of the embodiments of the present disclosure, and should not be regarded as limitations on the embodiments of the present disclosure

图3a、图3b示出根据本公开一实施例的中断存储指令处理装置的应用场景的示意图。如图3a、图3b所示,中断存储指令处理装置对中断存储指令进行处理的过程如下:3a and 3b are schematic diagrams illustrating application scenarios of an apparatus for processing interrupt storage instructions according to an embodiment of the present disclosure. As shown in Figure 3a and Figure 3b, the process of processing the interrupt storage instruction by the interrupt storage instruction processing device is as follows:

示例一Example 1

如图3a所示,控制模块11对获取到的中断存储指令1(如中断存储指令1为breakdump.gpr nram0r0r1r2r3r4r5)进行解析,得到中断存储指令1的操作码和操作域。其中,中断存储指令1的操作码为breakdump.gpr,gpr为存储空间类型,表示寄存器。r0、r1、r2、r3、r4、r5表示存储空间标识。nram0表示中断存储空间的标识。在执行到中断存储指令1时,控制装置中断退出,并对存储空间标识为r0、r1、r2、r3、r4、r5的6个寄存器中的数据存储至与中断存储空间的标识nram0对应的中断存储空间中。As shown in FIG. 3 a , the

其中,控制装置中断退出,可以包括:在执行到中断存储指令1时,中断当前计算指令的执行。The interrupting and exiting by the control device may include: interrupting the execution of the current calculation instruction when the interrupt storage instruction 1 is executed.

示例二Example 2

如图3b所示,控制模块11对获取到的中断存储指令2(如中断存储指令2为breakdump.nram ldram0 500 1024)进行解析,得到中断存储指令2的操作码和操作域。其中,中断存储指令2的操作码为breakdump.nram,nram为存储空间类型,表示NRAM。500表示待存储数据地址。1024为目标存储量。ldram0表示中断存储空间的标识。在执行到中断存储指令2时,控制装置中断退出,并从NRAM中待存储数据地址500中获取目标存储量1024的待存储数据,将待存储数据存入与中断存储空间的标识ldram0对应的中断存储空间中。As shown in FIG. 3b , the

其中,控制装置中断退出,可以包括:在执行到中断存储指令2时,中断当前计算指令的执行。The interrupting and exiting by the control device may include: interrupting the execution of the current calculation instruction when the interrupt storage instruction 2 is executed.

这样,中断存储指令处理装置可以高效、快速地对中断存储指令进行处理,能够高效、快速地对装置的中断退出做出响应,且提高了对数据进行运算的效率和速度。以上各模块的工作过程可参考上文的相关描述。In this way, the interrupt storage instruction processing device can efficiently and quickly process the interrupt storage instruction, can efficiently and quickly respond to the interrupt exit of the device, and improve the efficiency and speed of data operation. For the working process of the above modules, reference may be made to the above related descriptions.

本公开提供一种机器学习运算装置,该机器学习运算装置可以包括一个或多个上述中断存储指令处理装置,用于从其他处理装置中获取待运算数据和控制信息,执行指定的机器学习运算。该机器学习运算装置可以从其他机器学习运算装置或非机器学习运算装置中获得中断存储指令,并将执行结果通过I/O接口传递给外围设备(也可称其他处理装置)。外围设备譬如摄像头,显示器,鼠标,键盘,网卡,wifi接口,服务器。当包含一个以上中断存储指令处理装置时,中断存储指令处理装置间可以通过特定的结构进行链接并传输数据,譬如,通过PCIE总线进行互联并传输数据,以支持更大规模的神经网络的运算。此时,可以共享同一控制系统,也可以有各自独立的控制系统;可以共享内存,也可以每个加速器有各自的内存。此外,其互联方式可以是任意互联拓扑。The present disclosure provides a machine learning computing device, the machine learning computing device may include one or more of the above interrupt storage instruction processing devices, which are used to obtain data to be operated and control information from other processing devices, and perform specified machine learning operations. The machine learning computing device can obtain interrupt storage instructions from other machine learning computing devices or non-machine learning computing devices, and transmit the execution results to peripheral devices (also called other processing devices) through the I/O interface. Peripherals such as camera, monitor, mouse, keyboard, network card, wifi interface, server. When more than one interrupt storage instruction processing device is included, the interrupt storage instruction processing devices can be linked and transmitted through a specific structure, for example, interconnected and transmitted through the PCIE bus to support larger-scale neural network operations. At this time, the same control system can be shared, or there can be independent control systems; memory can be shared, or each accelerator can have its own memory. In addition, the interconnection method can be any interconnection topology.

该机器学习运算装置具有较高的兼容性,可通过PCIE接口与各种类型的服务器相连接。The machine learning computing device has high compatibility and can be connected with various types of servers through the PCIE interface.

图4a示出根据本公开一实施例的组合处理装置的框图。如图4a所示,该组合处理装置包括上述机器学习运算装置、通用互联接口和其他处理装置。机器学习运算装置与其他处理装置进行交互,共同完成用户指定的操作。FIG. 4a shows a block diagram of a combined processing apparatus according to an embodiment of the present disclosure. As shown in Fig. 4a, the combined processing device includes the above-mentioned machine learning computing device, a general interconnection interface and other processing devices. The machine learning computing device interacts with other processing devices to jointly complete the operation specified by the user.

其他处理装置,包括中央处理器CPU、图形处理器GPU、神经网络处理器等通用/专用处理器中的一种或以上的处理器类型。其他处理装置所包括的处理器数量不做限制。其他处理装置作为机器学习运算装置与外部数据和控制的接口,包括数据搬运,完成对本机器学习运算装置的开启、停止等基本控制;其他处理装置也可以和机器学习运算装置协作共同完成运算任务。Other processing devices include one or more processor types among general-purpose/special-purpose processors such as a central processing unit (CPU), a graphics processing unit (GPU), and a neural network processor. The number of processors included in other processing devices is not limited. Other processing devices serve as the interface between the machine learning computing device and external data and control, including data transfer, to complete the basic control of starting and stopping the machine learning computing device; other processing devices can also cooperate with the machine learning computing device to complete computing tasks.

通用互联接口,用于在机器学习运算装置与其他处理装置间传输数据和控制指令。该机器学习运算装置从其他处理装置中获取所需的输入数据,写入机器学习运算装置片上的存储装置;可以从其他处理装置中获取控制指令,写入机器学习运算装置片上的控制缓存;也可以读取机器学习运算装置的存储模块中的数据并传输给其他处理装置。A universal interconnect interface for transferring data and control instructions between machine learning computing devices and other processing devices. The machine learning computing device obtains required input data from other processing devices, and writes it into a storage device on-chip of the machine learning computing device; it can obtain control instructions from other processing devices and write it into the control cache on the machine learning computing device chip; The data in the storage module of the machine learning computing device can be read and transmitted to other processing devices.

图4b示出根据本公开一实施例的组合处理装置的框图。在一种可能的实现方式中,如图4b所示,该组合处理装置还可以包括存储装置,存储装置分别与机器学习运算装置和所述其他处理装置连接。存储装置用于保存在机器学习运算装置和所述其他处理装置的数据,尤其适用于所需要运算的数据在本机器学习运算装置或其他处理装置的内部存储中无法全部保存的数据。该存储装置也可以作为上述中断存储指令处理装置的片外存储。FIG. 4b shows a block diagram of a combined processing apparatus according to an embodiment of the present disclosure. In a possible implementation manner, as shown in FIG. 4b, the combined processing device may further include a storage device, and the storage device is respectively connected to the machine learning computing device and the other processing devices. The storage device is used to save data in the machine learning computing device and the other processing devices, and is especially suitable for data that cannot be fully stored in the internal storage of the machine learning computing device or other processing devices. The storage device can also be used as off-chip storage of the above-mentioned interrupt storage instruction processing device.

该组合处理装置可以作为手机、机器人、无人机、视频监控设备等设备的SOC片上系统,有效降低控制部分的核心面积,提高处理速度,降低整体功耗。此情况时,该组合处理装置的通用互联接口与设备的某些部件相连接。某些部件譬如摄像头,显示器,鼠标,键盘,网卡,wifi接口。The combined processing device can be used as an SOC system for mobile phones, robots, drones, video surveillance equipment and other equipment, effectively reducing the core area of the control part, improving the processing speed and reducing the overall power consumption. In this case, the general interconnection interface of the combined processing device is connected to certain components of the apparatus. Some components such as camera, monitor, mouse, keyboard, network card, wifi interface.

本公开提供一种机器学习芯片,该芯片包括上述机器学习运算装置或组合处理装置。The present disclosure provides a machine learning chip, which includes the above-mentioned machine learning computing device or combined processing device.

本公开提供一种机器学习芯片封装结构,该机器学习芯片封装结构包括上述机器学习芯片。The present disclosure provides a machine learning chip packaging structure, and the machine learning chip packaging structure includes the above-mentioned machine learning chip.

本公开提供一种板卡,图5示出根据本公开一实施例的板卡的结构示意图。如图5所示,该板卡包括上述机器学习芯片封装结构或者上述机器学习芯片。板卡除了包括机器学习芯片389以外,还可以包括其他的配套部件,该配套部件包括但不限于:存储器件390、接口装置391和控制器件392。The present disclosure provides a board, and FIG. 5 shows a schematic structural diagram of the board according to an embodiment of the present disclosure. As shown in FIG. 5 , the board includes the above-mentioned machine learning chip packaging structure or the above-mentioned machine learning chip. In addition to the machine learning chip 389 , the board may also include other supporting components, including but not limited to: a storage device 390 , an

存储器件390与机器学习芯片389(或者机器学习芯片封装结构内的机器学习芯片)通过总线连接,用于存储数据。存储器件390可以包括多组存储单元393。每一组存储单元393与机器学习芯片389通过总线连接。可以理解,每一组存储单元393可以是DDR SDRAM(英文:Double Data Rate SDRAM,双倍速率同步动态随机存储器)。其中,存储单元393可以是LDRAM,在存储单元393为LDRAM时,每个存储单元393分别对应于一个芯片389。The storage device 390 is connected to the machine learning chip 389 (or the machine learning chip in the machine learning chip package structure) through a bus for storing data. The memory device 390 may include groups of memory cells 393 . Each group of storage units 393 is connected to the machine learning chip 389 through a bus. It can be understood that each group of storage units 393 may be DDR SDRAM (English: Double Data Rate SDRAM, double-rate synchronous dynamic random access memory). The storage unit 393 may be an LDRAM, and when the storage unit 393 is an LDRAM, each storage unit 393 corresponds to one chip 389 respectively.

DDR不需要提高时钟频率就能加倍提高SDRAM的速度。DDR允许在时钟脉冲的上升沿和下降沿读出数据。DDR的速度是标准SDRAM的两倍。DDR does not need to increase the clock frequency to double the speed of SDRAM. DDR allows data to be read out on both the rising and falling edges of the clock pulse. DDR is twice as fast as standard SDRAM.

在一个实施例中,存储器件390可以包括4组存储单元393。每一组存储单元393可以包括多个DDR4颗粒(芯片)。在一个实施例中,机器学习芯片389内部可以包括4个72位DDR4控制器,上述72位DDR4控制器中64bit用于传输数据,8bit用于ECC校验。可以理解,当每一组存储单元393中采用DDR4-3200颗粒时,数据传输的理论带宽可达到25600MB/s。In one embodiment, the memory device 390 may include four sets of memory cells 393 . Each set of memory cells 393 may include a plurality of DDR4 particles (chips). In one embodiment, the machine learning chip 389 may include four 72-bit DDR4 controllers inside, where 64 bits of the 72-bit DDR4 controllers are used for data transmission and 8 bits are used for ECC verification. It can be understood that when DDR4-3200 particles are used in each group of storage units 393, the theoretical bandwidth of data transmission can reach 25600MB/s.

在一个实施例中,每一组存储单元393包括多个并联设置的双倍速率同步动态随机存储器。DDR在一个时钟周期内可以传输两次数据。在机器学习芯片389中设置控制DDR的控制器,用于对每个存储单元393的数据传输与数据存储的控制。In one embodiment, each set of memory cells 393 includes a plurality of double-rate synchronous dynamic random access memories arranged in parallel. DDR can transfer data twice in one clock cycle. A controller for controlling the DDR is provided in the machine learning chip 389 for controlling data transmission and data storage of each storage unit 393 .

接口装置391与机器学习芯片389(或者机器学习芯片封装结构内的机器学习芯片)电连接。接口装置391用于实现机器学习芯片389与外部设备(例如服务器或计算机)之间的数据传输。例如在一个实施例中,接口装置391可以为标准PCIE接口。比如,待处理的数据由服务器通过标准PCIE接口传递至机器学习芯片289,实现数据转移。优选的,当采用PCIE 3.0X 16接口传输时,理论带宽可达到16000MB/s。在另一个实施例中,接口装置391还可以是其他的接口,本公开并不限制上述其他的接口的具体表现形式,接口装置能够实现转接功能即可。另外,机器学习芯片的计算结果仍由接口装置传送回外部设备(例如服务器)。The

控制器件392与机器学习芯片389电连接。控制器件392用于对机器学习芯片389的状态进行监控。具体的,机器学习芯片389与控制器件392可以通过SPI接口电连接。控制器件392可以包括单片机(Micro Controller Unit,MCU)。如机器学习芯片389可以包括多个处理芯片、多个处理核或多个处理电路,可以带动多个负载。因此,机器学习芯片389可以处于多负载和轻负载等不同的工作状态。通过控制器件可以实现对机器学习芯片中多个处理芯片、多个处理和/或多个处理电路的工作状态的调控。The control device 392 is electrically connected to the machine learning chip 389 . The control device 392 is used to monitor the state of the machine learning chip 389 . Specifically, the machine learning chip 389 and the control device 392 may be electrically connected through an SPI interface. The control device 392 may include a Micro Controller Unit (MCU). For example, the machine learning chip 389 may include multiple processing chips, multiple processing cores or multiple processing circuits, and may drive multiple loads. Therefore, the machine learning chip 389 can be in different working states such as multi-load and light-load. The control device can realize the regulation of the working states of multiple processing chips, multiple processing and/or multiple processing circuits in the machine learning chip.

本公开提供一种电子设备,该电子设备包括上述机器学习芯片或板卡。The present disclosure provides an electronic device including the above-mentioned machine learning chip or board.

电子设备可以包括数据处理装置、机器人、电脑、打印机、扫描仪、平板电脑、智能终端、手机、行车记录仪、导航仪、传感器、摄像头、服务器、云端服务器、相机、摄像机、投影仪、手表、耳机、移动存储、可穿戴设备、交通工具、家用电器、和/或医疗设备。Electronic devices may include data processing devices, robots, computers, printers, scanners, tablet computers, smart terminals, mobile phones, driving recorders, navigators, sensors, cameras, servers, cloud servers, cameras, video cameras, projectors, watches, Headphones, mobile storage, wearables, vehicles, home appliances, and/or medical equipment.

交通工具可以包括飞机、轮船和/或车辆。家用电器可以包括电视、空调、微波炉、冰箱、电饭煲、加湿器、洗衣机、电灯、燃气灶、油烟机。医疗设备可以包括核磁共振仪、B超仪和/或心电图仪。Vehicles may include aircraft, ships and/or vehicles. Household appliances may include televisions, air conditioners, microwave ovens, refrigerators, rice cookers, humidifiers, washing machines, electric lights, gas stoves, and range hoods. Medical equipment may include MRI machines, ultrasound machines and/or electrocardiographs.

图6示出根据本公开一实施例的中断存储指令处理方法的流程图。如图6所示,该方法应用于上述中断存储指令处理装置,该方法包括步骤S51和步骤S52。FIG. 6 shows a flowchart of a method for processing an interrupt storage instruction according to an embodiment of the present disclosure. As shown in FIG. 6, the method is applied to the above-mentioned interrupt storage instruction processing apparatus, and the method includes step S51 and step S52.

在步骤S51中,根据获取到的中断存储指令的操作域和操作码,确定进行响应中断退出的处理所需的存储参数。其中,操作码用于指示中断存储指令对装置中断退出时所进行的处理为中断存储处理,存储参数用于指示装置中断退出时需要存储的数据。In step S51, according to the obtained operation domain and operation code of the interrupt storage instruction, the storage parameters required to perform the processing of responding to the interrupt and exit are determined. The operation code is used to indicate that the processing performed by the interrupt storage instruction when the device is interrupted and exited is interrupt storage processing, and the storage parameter is used to indicate the data to be stored when the device is interrupted and exited.

在步骤S53中,在执行到中断存储指令时,控制装置中断退出,并根据存储参数进行数据存储。In step S53, when the interrupt storage instruction is executed, the control device interrupts and exits, and performs data storage according to the storage parameter.

在一种可能的实现方式中,操作域可以包括用于指示中断存储空间的标识.其中,根据存储参数进行数据存储,可以包括:In a possible implementation manner, the operation domain may include an identifier for indicating the interruption of the storage space. Wherein, performing data storage according to storage parameters may include:

将根据存储参数获取的所需存储的数据存入与中断存储空间的标识相对应的中断存储空间中。The data to be stored obtained according to the storage parameter is stored in the interrupt storage space corresponding to the identifier of the interrupt storage space.

在一种可能的实现方式中,中断存储空间可以包括装置的片外存储和/或片上存储。其中,片外存储可以包括至少一个DDR,DDR可以包括至少一个LDRAM,片上存储可以包括寄存器、NRAM中的至少一种,片外存储的可用存储空间小于或等于指定存储容量。In one possible implementation, the interrupt storage space may include off-chip storage and/or on-chip storage of the device. The off-chip storage may include at least one DDR, the DDR may include at least one LDRAM, the on-chip storage may include at least one of registers and NRAM, and the available storage space of the off-chip storage is less than or equal to the specified storage capacity.

在一种可能的实现方式中,存储参数包括存储空间类型和存储空间标识。其中,操作码还用于指示存储空间类型,操作域包括存储空间标识。其中,根据存储参数进行数据存储,可以包括:In a possible implementation manner, the storage parameter includes a storage space type and a storage space identifier. The operation code is also used to indicate the storage space type, and the operation field includes the storage space identifier. Among them, data storage according to storage parameters may include:

确定与存储空间类型、存储空间标识相匹配的至少一个目标存储空间,并存储目标存储空间中的数据。Determine at least one target storage space matching the storage space type and storage space identifier, and store the data in the target storage space.

在一种可能的实现方式中,在目标存储空间为多个时,每个目标存储空间中的数据为一组待存储数据,多组待存储数据对应至少一种数据格式。In a possible implementation manner, when there are multiple target storage spaces, the data in each target storage space is a group of data to be stored, and the multiple groups of data to be stored correspond to at least one data format.

在一种可能的实现方式中,存储参数可以包括存储空间标识和待存储数据地址。其中,操作码还可以用于指示存储空间标识,操作域可以包括待存储数据地址。其中,根据存储参数进行数据存储,可以包括:In a possible implementation manner, the storage parameter may include a storage space identifier and an address of data to be stored. Wherein, the operation code may also be used to indicate the storage space identifier, and the operation field may include the address of the data to be stored. Among them, data storage according to storage parameters may include:

确定与存储空间标识相对应的目标存储空间,并从目标存储空间的待存储数据地址中获取待存储数据,存储待存储数据。The target storage space corresponding to the storage space identifier is determined, and the data to be stored is acquired from the address of the data to be stored in the target storage space, and the data to be stored is stored.

在一种可能的实现方式中,存储参数还可以包括目标存储量。其中,操作域还可以包括目标存储量。其中,从目标存储空间的待存储数据地址中获取待存储数据,存储待存储数据,可以包括:In a possible implementation manner, the storage parameter may also include a target storage amount. Wherein, the operation domain may also include the target storage amount. Wherein, obtaining the data to be stored from the address of the data to be stored in the target storage space, and storing the data to be stored, may include:

从目标存储空间的待存储数据地址中获取数据量为目标存储量的待存储数据,存储待存储数据。The to-be-stored data whose data amount is the target storage amount is obtained from the to-be-stored data address of the target storage space, and the to-be-stored data is stored.

在一种可能的实现方式中,该方法还可以包括:In a possible implementation, the method may further include:

获取计算指令,并获取执行计算指令所需的待运算数据;Obtain the calculation instruction, and obtain the data to be operated required to execute the calculation instruction;

根据待运算数据,执行计算指令,得到运算结果,According to the data to be operated, execute the calculation instruction to obtain the operation result,

其中,在执行到中断存储指令时,控制装置中断退出,包括:Wherein, when the interrupt storage instruction is executed, the control device interrupts and exits, including:

在执行到中断存储指令时,控制运算模块中断当前计算指令的执行。When the interrupt storage instruction is executed, the control operation module interrupts the execution of the current calculation instruction.

在一种可能的实现方式中,该方法还可以包括:In a possible implementation, the method may further include:

解析计算指令得到多个运算指令;Parse the calculation instruction to obtain multiple operation instructions;

其中,根据待运算数据,执行计算指令,得到运算结果,可以包括:Wherein, according to the data to be calculated, the calculation instruction is executed to obtain the calculation result, which may include:

对待运算数据执行前序处理,以及与进行数据和运算指令的传输;Perform pre-order processing on the data to be operated, and transmit data and operation instructions;

根据传输的数据和运算指令并行执行中间运算得到多个中间结果;Perform intermediate operations in parallel according to the transmitted data and operation instructions to obtain multiple intermediate results;

对多个中间结果执行后续处理,得到运算结果。Perform subsequent processing on multiple intermediate results to obtain operation results.

在一种可能的实现方式中,该方法还可以包括:In a possible implementation, the method may further include:

利用存储模块中的片上存储来存储待运算数据,Use the on-chip storage in the memory module to store the data to be calculated,

其中,存储模块可以包括片外存储和/或片上存储,片上存储可以包括寄存器和缓存中的至少一种,Wherein, the storage module may include off-chip storage and/or on-chip storage, and the on-chip storage may include at least one of registers and caches,

缓存,用于存储待运算数据,缓存可以包括至少一个NRAM;a cache, which is used to store data to be operated, and the cache may include at least one NRAM;

寄存器,用于存储待运算数据中的标量数据。The register is used to store the scalar data in the data to be operated.

在一种可能的实现方式中,缓存可以包括神经元缓存,神经元缓存用于存储待运算数据中的神经元数据。In a possible implementation manner, the cache may include a neuron cache, and the neuron cache is used to store neuron data in the data to be operated.

在一种可能的实现方式中,该方法还可以包括:In a possible implementation, the method may further include:

存储中断存储指令和计算指令;Store interrupt storage instructions and calculation instructions;

对中断存储指令和计算指令分别进行解析,得到对应的操作码和操作域;Analyze the interrupt storage instruction and the calculation instruction respectively to obtain the corresponding opcode and operation domain;

存储指令队列,指令队列包括按照执行顺序依次排列的多个待执行指令,多个待执行指令包括中断存储指令和计算指令。A storage instruction queue, the instruction queue includes a plurality of to-be-executed instructions sequentially arranged in an execution order, and the multiple to-be-executed instructions include interrupt storage instructions and calculation instructions.

在一种可能的实现方式中,该方法还可以包括:在确定多个待执行指令中的第一待执行指令与第一待执行指令之前的第零待执行指令存在关联关系时,缓存第一待执行指令,并在确定第零执行指令执行完毕后,控制进行第一待执行指令的执行,In a possible implementation manner, the method may further include: when it is determined that the first to-be-executed instruction in the plurality of to-be-executed instructions has an associated relationship with the zeroth to-be-executed instruction before the first to-be-executed instruction, caching the first to-be-executed instruction The instruction to be executed, and after it is determined that the execution of the zeroth execution instruction is completed, the execution of the first instruction to be executed is controlled,

其中,第一待执行指令与第一待执行指令之前的第零待执行指令存在关联关系可以包括:存储第一待执行指令所需数据的第一存储地址区间与存储第零待执行指令所需数据的第零存储地址区间具有重叠的区域。Wherein, the relationship between the first instruction to be executed and the zeroth instruction to be executed before the first instruction to be executed may include: a first storage address interval for storing data required by the first instruction to be executed and a first storage address range required for storing the zeroth instruction to be executed The zeroth storage address range of data has overlapping areas.

需要说明的是,尽管以上述实施例作为示例介绍了中断存储指令处理方法如上,但本领域技术人员能够理解,本公开应不限于此。事实上,用户完全可根据个人喜好和/或实际应用场景灵活设定各步骤,只要符合本公开的技术方案即可。It should be noted that although the above-mentioned embodiment is used as an example to introduce the method for processing the interrupt storage instruction as above, those skilled in the art can understand that the present disclosure should not be limited thereto. In fact, the user can flexibly set each step according to personal preference and/or actual application scenarios, as long as it conforms to the technical solutions of the present disclosure.

本公开实施例所提供的中断存储指令处理方法的适用范围广,对中断存储指令的处理效率高、处理速度快,能够高效、快速地对装置的中断退出做出响应,且提高了对数据进行运算的效率和速度。The interrupt storage instruction processing method provided by the embodiment of the present disclosure has a wide application range, has high processing efficiency and fast processing speed for the interrupt storage instruction, can efficiently and quickly respond to the interruption and exit of the device, and improves the data processing efficiency. Efficiency and speed of operations.

A1、一种中断存储指令处理装置,所述装置包括控制模块,所述控制模块包括:A1. An interrupt storage instruction processing device, the device includes a control module, and the control module includes:

参数获取子模块,根据获取到的中断存储指令的操作域和操作码,确定进行响应中断退出的处理所需的存储参数;The parameter acquisition sub-module determines the storage parameters required for the processing of responding to the interrupt and exit according to the acquired operation domain and operation code of the interrupt storage instruction;

中断存储子模块,在执行到所述中断存储指令时,控制所述装置中断退出,并根据所述存储参数进行数据存储,The interrupt storage sub-module, when executing the interrupt storage instruction, controls the device to interrupt and exit, and performs data storage according to the storage parameter,

其中,所述操作码用于指示所述中断存储指令对装置中断退出时所进行的处理为中断存储处理,所述存储参数用于指示所述装置中断退出时需要存储的数据。Wherein, the operation code is used to indicate that the processing performed by the interrupt storage instruction when the device is interrupted and exited is an interrupted storage process, and the storage parameter is used to indicate the data to be stored when the device is interrupted and exited.

A2、根据权利要求A1所述的装置,所述操作域包括用于指示中断存储空间的标识,A2. The apparatus according to claim A1, wherein the operation field includes an identifier for indicating the interruption of the storage space,

其中,所述中断存储子模块,还用于将根据所述存储参数获取的所需存储的数据存入与所述中断存储空间的标识相对应的中断存储空间中。The interrupt storage sub-module is further configured to store the data to be stored obtained according to the storage parameter into the interrupt storage space corresponding to the identifier of the interrupt storage space.

A3、根据权利要求A2所述的装置,所述中断存储空间包括所述装置的片外存储和/或片上存储,A3. The device according to claim A2, wherein the interrupt storage space comprises off-chip storage and/or on-chip storage of the device,

其中,所述片外存储包括至少一个DDR,所述DDR包括至少一个LDRAM,所述片上存储包括寄存器、NRAM中的至少一种,所述片外存储的可用存储空间小于或等于指定存储容量。The off-chip storage includes at least one DDR, the DDR includes at least one LDRAM, the on-chip storage includes at least one of registers and NRAM, and the available storage space of the off-chip storage is less than or equal to a specified storage capacity.

A4、根据权利要求A1所述的装置,所述存储参数包括存储空间类型和存储空间标识,A4. The device according to claim A1, wherein the storage parameter includes a storage space type and a storage space identifier,

其中,所述操作码还用于指示所述存储空间类型,所述操作域包括存储空间标识,Wherein, the operation code is also used to indicate the storage space type, and the operation field includes a storage space identifier,

其中,根据所述存储参数进行数据存储,包括:Wherein, data storage is performed according to the storage parameters, including:

确定与所述存储空间类型、存储空间标识相匹配的至少一个目标存储空间,并存储目标存储空间中的数据。At least one target storage space matching the storage space type and storage space identifier is determined, and data in the target storage space is stored.

A5、根据权利要求A4所述的装置,在所述目标存储空间为多个时,每个目标存储空间中的数据为一组待存储数据,多组待存储数据对应至少一种数据格式。A5. The device according to claim A4, when there are multiple target storage spaces, the data in each target storage space is a group of data to be stored, and the multiple groups of data to be stored correspond to at least one data format.

A6、根据权利要求A1所述的装置,所述存储参数包括存储空间标识和待存储数据地址,A6. The device according to claim A1, wherein the storage parameter comprises a storage space identifier and an address of the data to be stored,

其中,所述操作码还用于指示所述存储空间标识,所述操作域包括所述待存储数据地址,Wherein, the operation code is also used to indicate the storage space identifier, and the operation field includes the address of the data to be stored,

其中,根据所述存储参数进行数据存储,包括:Wherein, data storage is performed according to the storage parameters, including:

确定与所述存储空间标识相对应的目标存储空间,并从所述目标存储空间的待存储数据地址中获取待存储数据,存储所述待存储数据。A target storage space corresponding to the storage space identifier is determined, and data to be stored is acquired from an address of data to be stored in the target storage space, and the data to be stored is stored.

A7、根据权利要求A6所述的装置,所述存储参数还包括目标存储量,其中,所述操作域还包括目标存储量,A7. The apparatus according to claim A6, wherein the storage parameter further includes a target storage amount, wherein the operation field further includes a target storage amount,

其中,从所述目标存储空间的待存储数据地址中获取待存储数据,存储所述待存储数据,包括:Wherein, obtaining the data to be stored from the address of the data to be stored in the target storage space, and storing the data to be stored, includes:

从所述目标存储空间的待存储数据地址中获取数据量为所述目标存储量的待存储数据,存储所述待存储数据。The to-be-stored data whose data volume is the target storage volume is acquired from the to-be-stored data address of the target storage space, and the to-be-stored data is stored.

A8、根据权利要求A1所述的装置,所述装置还包括运算模块,A8. The device according to claim A1, further comprising an arithmetic module,

所述控制模块,还用于获取计算指令,获取执行所述计算指令所需的待运算数据,并将所述待运算数据和所述计算指令发送至所述运算模块;The control module is further configured to obtain a calculation instruction, obtain the data to be calculated required to execute the calculation instruction, and send the data to be calculated and the calculation instruction to the calculation module;

所述运算模块,用于根据所述待运算数据,执行所述计算指令,得到运算结果,The operation module is configured to execute the calculation instruction according to the data to be calculated to obtain an operation result,

其中,在执行到所述中断存储指令时,控制所述装置中断退出,包括:Wherein, when the interrupt storage instruction is executed, controlling the device to interrupt and exit includes:

在执行到中断存储指令时,控制所述运算模块中断当前所述计算指令的执行。When the interrupt storage instruction is executed, the operation module is controlled to interrupt the current execution of the calculation instruction.

A9、根据权利要求A8所述的装置,所述运算模块包括主运算子模块和多个从运算子模块,A9. The device according to claim A8, wherein the operation module comprises a master operation sub-module and a plurality of slave operation sub-modules,

所述控制模块,还用于解析所述计算指令得到多个运算指令,并将所述待运算数据和所述多个运算指令发送至所述主运算子模块;The control module is further configured to parse the calculation instruction to obtain multiple operation instructions, and send the data to be calculated and the multiple operation instructions to the main operation sub-module;

所述主运算子模块,用于对所述待运算数据执行前序处理,以及与所述多个从运算子模块进行数据和运算指令的传输;The main operation submodule is used to perform pre-order processing on the data to be operated, and transmit data and operation instructions with the plurality of slave operation submodules;

所述从运算子模块,用于根据从所述主运算子模块传输的数据和运算指令并行执行中间运算得到多个中间结果,并将所述多个中间结果传输给所述主运算子模块;The slave operation submodule is configured to perform intermediate operations in parallel according to the data and operation instructions transmitted from the master operation submodule to obtain multiple intermediate results, and transmit the multiple intermediate results to the master operation submodule;

所述主运算子模块,还用于对所述多个中间结果执行后续处理,得到运算结果。The main operation sub-module is further configured to perform subsequent processing on the plurality of intermediate results to obtain operation results.

A10、根据权利要求A8所述的装置,所述装置还包括存储模块,所述存储模块包括片外存储和/或片上存储,A10. The apparatus according to claim A8, further comprising a storage module, the storage module comprising off-chip storage and/or on-chip storage,

所述片上存储,用于存储所述待运算数据,The on-chip storage is used to store the data to be calculated,

其中,所述片上存储包括寄存器和缓存中的至少一种,Wherein, the on-chip storage includes at least one of a register and a cache,

所述缓存,用于存储所述待运算数据,所述缓存包括至少一个NRAM;The cache is used to store the data to be calculated, and the cache includes at least one NRAM;

所述寄存器,用于存储所述待运算数据中的标量数据。The register is used to store the scalar data in the data to be operated.

A11、根据权利要求A10所述的装置,所述缓存包括神经元缓存,A11. The apparatus of claim A10, wherein the buffer comprises a neuron buffer,

所述神经元缓存,用于存储所述待运算数据中的神经元数据。The neuron cache is used to store neuron data in the data to be operated.

A12、根据权利要求A8所述的装置,所述控制模块,包括:A12. The apparatus according to claim A8, the control module comprising:

指令存储子模块,用于存储所述中断存储指令和所述计算指令;an instruction storage submodule for storing the interrupt storage instruction and the calculation instruction;

指令处理子模块,用于对所述中断存储指令和所述计算指令分别进行解析,得到对应的操作码和操作域;an instruction processing submodule, configured to parse the interrupt storage instruction and the calculation instruction respectively to obtain the corresponding operation code and operation domain;

队列存储子模块,用于存储指令队列,所述指令队列包括按照执行顺序依次排列的多个待执行指令,所述多个待执行指令包括所述中断存储指令和所述计算指令。The queue storage sub-module is used to store an instruction queue, the instruction queue includes a plurality of instructions to be executed sequentially arranged in an execution order, and the multiple instructions to be executed include the interrupt storage instruction and the calculation instruction.

A13、根据权利要求A12所述的装置,所述控制模块,还包括:A13. The apparatus according to claim A12, the control module, further comprising: