CN110828379A - 一种薄膜晶体管的制造方法、薄膜晶体管及显示面板 - Google Patents

一种薄膜晶体管的制造方法、薄膜晶体管及显示面板Download PDFInfo

- Publication number

- CN110828379A CN110828379ACN201910980595.4ACN201910980595ACN110828379ACN 110828379 ACN110828379 ACN 110828379ACN 201910980595 ACN201910980595 ACN 201910980595ACN 110828379 ACN110828379 ACN 110828379A

- Authority

- CN

- China

- Prior art keywords

- layer

- silicon wafer

- low

- gate

- low temperature

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0165—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs the components including complementary IGFETs, e.g. CMOS devices

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/1368—Active matrix addressed cells in which the switching element is a three-electrode device

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/02—Manufacture or treatment characterised by using material-based technologies

- H10D84/03—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology

- H10D84/038—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology using silicon technology, e.g. SiGe

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/80—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs

- H10D84/82—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs of only field-effect components

- H10D84/83—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs of only field-effect components of only insulated-gate FETs [IGFET]

- H10D84/85—Complementary IGFETs, e.g. CMOS

- H10D84/859—Complementary IGFETs, e.g. CMOS comprising both N-type and P-type wells, e.g. twin-tub

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Nonlinear Science (AREA)

- Mathematical Physics (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- General Physics & Mathematics (AREA)

- Optics & Photonics (AREA)

- Thin Film Transistor (AREA)

Abstract

Description

技术领域

本发明涉及一种薄膜晶体管的制造方法、薄膜晶体管及显示面板。

背景技术

目前,高分辨率平板显示器(FPDs)在现代信息交换和通信过程中发挥着重要作用。智能手机、电视和笔记本电脑的两种主流技术分别是有源矩阵液晶显示器(AMLCDs)和有源矩阵有机发光二极管(AMOLED)显示器。AMOLED和AMOLED显示器都需要一个含有源开关阵列的背板来控制像素的开关状态。这种矩阵通常由在大片玻璃基底上制作的薄膜晶体管构成。

FPD的像素由每英寸的像素点(ppi)决定。对于高端智能手机来说,ppi通常大于300,例如,Apple iPhone的ppi为326,SONY Xperia Z5 Premium的ppi为806;对近眼领域而言,例如AR和VR,ppi大于500是必要的。为了防止木纹效应,OLED显示器的ppi要采用3000以上,例如,奈德光学公司的GOOVIS G1,3147ppi,像素大小=8.1μm×8.1μm,面板大小为0.6英寸。由于TFTs的电气特性差、不均匀性,所以要在一个像素点里使用更大的宽长比或更多的TFT去满足当前的要求或用于不均匀性的补偿。

因此,以TFT背板制作ppi>800的屏幕极具挑战性。在近眼应用方面,这种面板是基于成熟的现代IC制造工艺-单晶硅晶圆加工制造的。其中涉及了一些高温过程,包括热氧化、掺杂扩散、激活掺杂剂的后退火等。这些工艺温度大多在9001000℃。而小尺寸和高温工艺使得硅片加工费用远比FDRTFT背板的制备昂贵。针对于现有技术,如何设计开发一种使用较低成本制作ppi>1000的FPD的制作工艺,是本领域技术人员亟待解决的技术问题。

发明内容

本发明所要解决的技术问题是克服上述现有技术的不足,提供一种薄膜晶体管的制造方法、薄膜晶体管及显示面板。

本发明解决上述技术问题采用的一个技术方案是:一种薄膜晶体管的制造方法,其中,所述制造方法包括:

准备硅片;

在所述硅片上设置低温隔离层;

在所述硅片上依次设置低温栅极介质层和栅极层;

在所述硅片中设置源漏极层;

在所述低温栅极介质层和所述栅极层上设置低温钝化层;

在所述低温钝化层、所述栅极层和所述源漏极层上设置金属层,所述金属层连接所述栅极层和所述源漏极层。

本发明解决上述技术问题采用的另一个技术方案是:提供一种薄膜晶体管,其中,所述薄膜晶体管包括:

硅片和形成于所述硅片一侧的低温隔离层;

低温栅极介质层,形成于所述硅片靠近所述低温隔离层的一侧;

栅极层,形成于所述低温栅极介质层背离所述硅片的一侧;

源漏极层,形成于所述硅片中;

低温钝化层,形成于所述低温栅极介质层和所述栅极层上;

金属层,形成于所述低温钝化层、所述栅极层和所述源漏极层上,连接所述栅极层和所述源漏极层。

本发明解决上述技术问题采用的又一个技术方案是:提供一种显示面板,其中,所述显示面板包括如上述的薄膜晶体管。

与现有技术相比,本发明的有益效果是:本申请提供一种薄膜晶体管的制造方法、薄膜晶体管及显示面板,该制造方法包括准备硅片;在硅片上设置低温隔离层;在硅片上依次设置低温栅极介质层和栅极层;在硅片中设置源漏极层;在低温栅极介质层和栅极层上设置低温钝化层;在低温钝化层、栅极层和源漏极层上设置金属层,金属层连接栅极层和源漏极层。通过在低温状态下,在硅片上设置低温隔离层、低温栅极介质层、栅极层、源漏极层、低温钝化层和金属层,解决了现有技术中制造高分辨率的薄膜晶体管的成功率低、成本高的问题。

附图说明

为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,其中:

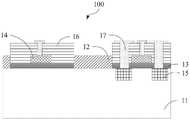

图1是本申请一种薄膜晶体管一实施例的结构示意图;

图2是本申请一种薄膜晶体管的制造方法一实施例的流程示意图;

图3是本申请一种薄膜晶体管的制造方法另一实施例的流程示意图;

图4是本申请一种薄膜晶体管另一实施例的结构示意图;

图5是本申请一种薄膜晶体管的制造方法又一实施例的流程示意图;

图6是本申请一种薄膜晶体管又一实施例的结构示意图;

图7是本申请一种薄膜晶体管的制造方法再一实施例的流程示意图;

图8是本申请一种薄膜晶体管再一实施例的结构示意图;

图9是本申请一种显示面板一实施例的结构示意图。

具体实施方式

下面将结合附图以及具体实施方式,对本发明做进一步描述。较佳实施例中所引用的如“上”、“下”、“左”、“右”、“中间”及“一”等用语,仅为便于叙述的明了,而非用以限定本发明可实施的范围,其相对关系的改变或调整,在无实质变更技术内容下,当亦视为本发明可实施的范畴。

请参阅图1和图2,图1是本申请一种薄膜晶体管一实施例的结构示意图,图2是本申请一种薄膜晶体管的制造方法一实施例的流程示意图。

该薄膜晶体管100包括硅片11、低温隔离层12、低温栅极介质层13、栅极层14、源漏极层15、低温钝化层16和金属层17。其中,低温隔离层12形成于硅片11的一侧;低温栅极介质层13,形成于硅片11靠近低温隔离层12的一侧;栅极层14,形成于低温栅极介质层13背离硅片11的一侧;源漏极层15,形成于硅片11中;低温钝化层16,形成于低温栅极介质层13和栅极层14上;金属层17,形成于低温钝化层16、栅极层14和源漏极层15上,连接栅极层14和源漏极层15。

为制得图1所示的薄膜晶体管100,本实施例所揭示的方法具体可以包括以下步骤:

S11:准备硅片。

本实施例中采用低温金属氧化物半导体(MOS,Metal-Oxide-Semiconductor)工艺,互补式金属氧化物半导体(CMOS,Complementary Metal Oxide Semiconductor)是成熟的现代集成电路工艺。

CMOS工艺包括了NMOS(N-Metal-Oxide-Semiconductor,N型金属氧化物半导体)工艺和PMOS(positive channel Metal Oxide Semiconductor,P沟道MOS晶体管)工艺,一般来说电路设计可以用单独的NMOS工艺实现,或者是单独的PMOS工艺实现,也可以同时用NMOS和PMOS组合的工艺来实现,即CMOS工艺。

CMOS工艺制程最高温度约9001000℃,而平板显示器(FPD,Flat-panel displays)薄膜晶体管(TFT,Thin-Film Transistor)工艺通常在大面积玻璃基板上制造,制程温度通常在600℃以下。TFT的电学特性虽然逊于单晶硅器件,但可应用于大面积低成本制造,高性能TFT基板可满足电视和手机应用需要,像素密度(pixel per inch,简称ppi)可高达800-2500。新型的增强现实(AR)/虚拟现实(VR)等近眼应用需要更高的像素密度以避免颗粒效应,高端近眼应用显示屏ppi超过3000,只能用硅工艺制作。

在本实施例中将硅片11作为基板,硅片11可以为硅晶圆,例如,IC级硅晶圆,PV级硅晶圆等等。本实施例中所揭示的制造方法可以在低温状态下进行,实现低温CMOS工艺、低温NMOS工艺和低温PMOS工艺,制造成本低,能够大面积制造。

S12:在硅片上设置低温隔离层。

在硅片11的一侧沉积低温隔离层材料,采用低温工艺对低温隔离层材料进行图形化等处理以形成低温隔离层12,低温隔离层12在硅片11上作为场氧化物以使器件彼此隔离。其中,低温隔离层12的材料可以为低介电常数材料,例如,SiO2(二氧化硅)、SiNx(氮化硅)等等。

S13:在硅片上依次设置低温栅极介质层和栅极层。

在硅片11上沉积低温栅极介质层材料,采用低温工艺得到低温栅极介质层13,其中,低温栅极介质层材料可以为栅氧材料,例如二氧化硅、氮化硅,高介电常数材料等等。

在低温栅极介质层13背离硅片11的一侧上沉积栅极材料,将栅极材料图形化得到栅极层14,其中,栅极材料为金属,例如Mo(钼)、Al(铝)、Cu(铜)、W(钨)等等。

S14:在硅片中设置源漏极层。

在硅片11上形成源漏极层15时,根据低温CMOS工艺、低温NMOS工艺和低温PMOS工艺的不同,选择需要的离子并注入到硅片11中,形成源漏极层15,例如,可以选择P型离子、N型离子,或者是P型离子和N型离子的混合型离子。通过注入一种或者两种离子的离子掺杂工艺,在硅片11靠近低温栅极介质层13的一侧上形成源漏极层15,源漏极层15连接低温栅极介质层13。

S15:在低温栅极介质层和栅极层上设置低温钝化层。

在低温栅极介质层13和栅极层14上沉积低温钝化层材料,并采用低温工艺进行固化处理得到低温钝化层16,低温钝化层材料可以为氮化硅和/或者二氧化硅,低温钝化层16能够对栅极层14进行保护,防止栅极层14被氧化,同时可以保护器件免受外界湿度等因素的影响。

S16:在低温钝化层、栅极层和源漏极层上设置金属层,金属层连接栅极层和源漏极层。

在得到低温钝化层16后,在低温钝化层16、栅极层14和源漏极层15上沉积金属材料,并将金属材料图形化为金属层17,作为薄膜晶体管100的连接线和测试焊盘。

本申请提供一种薄膜晶体管的制造方法,该制造方法包括准备硅片;在硅片上设置低温隔离层;在硅片上依次设置低温栅极介质层和栅极层;在硅片中设置源漏极层;在低温栅极介质层和栅极层上设置低温钝化层;在低温钝化层、栅极层和源漏极层上设置金属层,金属层连接栅极层和源漏极层。通过在低温状态下,在硅片上设置低温隔离层、低温栅极介质层、栅极层、源漏极层、低温钝化层和金属层,能够降低制造成本,提高制造高分辨率显示中的薄膜晶体管的成功率。

在上述实施方式的基础上,本申请提出一种薄膜晶体管的另外三个实施例,本实施例所揭示的方法按照低温CMOS工艺、低温PMOS工艺和低温NMOS工艺三种工艺分别进行说明,本实施例中与上述相同的部分此处不做赘述。

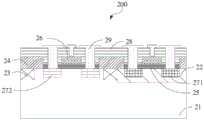

请一并参阅图3和图4,图3是本申请一种薄膜晶体管的制造方法另一实施例的流程示意图,图4是本申请一种薄膜晶体管另一实施例的结构示意图。在低温CMOS工艺中,薄膜晶体管200的制造方法具体可以包括以下步骤:

S21:准备P型硅片。

本实施例中为使用的硅片为P型硅片21,将P型硅片21作为基板。

S22:在P型硅片上设置第一二氧化硅层。

在P型硅片21上生长一层二氧化硅薄膜作为第一二氧化硅层,第一二氧化硅层作为牺牲氧化层保护表面。此处的第一二氧化硅层可以通过LPCVD(Low pressure chemicalvapor deposition,低压化学气相沉积),PECVD(Plasma Enhanced Chemical VaporDeposition,等离子体增强化学的气相沉积法)等方式生成,例如在本实施例中采用425℃的LPCVD的方法,第一二氧化硅层的厚度为50nm。

S23:在第一二氧化硅层上设置光刻胶并进行图形化处理,注入第一N型离子以在P型硅片和第一二氧化硅层之间形成N阱,除去光刻胶。

在第一二氧化硅层背离P型硅片21的一侧上涂抹一层光刻胶(PR),用掩模版进行图形化处理,将N型离子注入以在P型硅片21靠近第一二氧化硅层的一侧形成N阱22(N-well)。其中,N阱22注入的N型离子可以为磷离子或砷离子,在本实施例中使用磷离子进行掺杂。由于基板使用的是P型硅片21,P型硅片21就是天然的P阱,除去光刻胶后,得到了具有N阱22和P阱的P型硅片21。

S24:在第一二氧化硅层上设置光刻胶并进行图形化处理,注入第一P型离子以在P型硅片和第一二氧化硅层之间形成P场,除去光刻胶和第一二氧化硅层。

在第一二氧化硅层上设置光刻胶并进行图形化处理,注入第一P型离子以在P型硅片21和第一二氧化硅层之间形成P场23,即使用光刻工艺定义P型离子注入范围,从而能够防止不同器件之间发生漏电。其中,至少一个P场23与N阱22相邻设置。得到P场23后,剥离光刻胶和作为牺牲氧化层的第一二氧化硅层。

S25:在P型硅片上沉积二氧化硅,对二氧化硅层进行图形化处理,得到第二二氧化硅层,对第二二氧化硅层图形化处理得到低温隔离层。

在P型硅片21靠近N阱22的一侧沉积二氧化硅,其中,沉积方式可以是低压化学气相沉积(LPCVD)、等离子体增强化学气相沉积(PECVD)或者溅射等工艺。在本实施例中,第二二氧化硅层的厚度大于或者等于500nm。

对第二二氧化硅层进行图形化处理形成低温隔离层24,以暴露器件区域,低温隔离层24在P型硅片21上作为场氧化物以使器件彼此隔离。在本实施例中,低温隔离层24与P场23相邻设置。

S26:在P型硅片上依次设置低温栅极介质层和栅极层。

S261:在P型硅片上沉积栅极介质,对栅极介质图形化以形成低温栅极介质层。

S262:在低温栅极介质层上沉积栅极金属以形成栅极层。

在本实施例中,步骤S26可以包括步骤S261~S262,下面一并进行说明:

在P型硅片21上采用低温工艺沉积二氧化硅,得到低温栅极介质层25,其中,沉积的方式可以是低压化学气相沉积(LPCVD)、等离子体增强化学气相沉积(PECVD),或者原子层沉积(ALD,Atomic Layer Deposition)或溅射等等。在本实施例中,低温栅极介质层25的厚度为70nm,采用LPCVD方法,加热温度为425℃。

在低温栅极介质层25背离P型硅片21的一侧上沉积栅极材料金属钼,沉积的方式可以是溅射或者蒸镀,将金属钼图形化得到栅极层26。在本实施例中,栅极层26的厚度为200nm。栅极层26可以设置于相邻两低温隔离层24之间。

S27:在P型硅片中设置源漏极层。

S271:对N阱注入第二P型离子以进行掺杂处理,得到第一源漏极层。

S272:对P型硅片注入N型离子以进行掺杂处理,得到第二源漏极层。

在本实施例中,步骤S27可以包括步骤S271~S272,下面一并进行说明:

在P型硅片21上形成源漏极层27时,需要分别对N阱22和P阱设置源漏极层27,即通过两次离子掺杂工艺,分别形成N阱22和P阱的源漏极层27。其中,离子掺杂可以是通过离子注入机或离子轰击的方式来实现的。

具体来说,对N阱22注入第二P型离子以进行掺杂处理,先通过设置光刻胶,将光刻胶图形化后暴露出PMOS器件的源漏(S/D)区域和NMOS器件的体接触区域,然后光刻胶作为掩模阻挡P型离子掺杂,掺杂。P型离子掺杂结束后,除去光刻胶,得到第一源漏极层271,其中第一源漏极层271设置于N阱22中,且设置于N阱22和低温栅极介质层25之间,第一源漏极层271还分布于栅极层26的两侧。

再一次设置光刻胶,对P型硅片21注入N型离子以进行掺杂处理,定义出NMOS器件的源漏(S/D)区域和PMOS器件的体接触区域,得到第二源漏极层272,其中第二源漏极层272形成于P型硅片21中,且设置于P型硅片21和低温栅极介质层25之间,第二源漏极层272还分布于栅极层26的两侧。

S28:在低温栅极介质层和栅极层上设置低温钝化层。

S281:在低温隔离层、栅极层和低温栅极介质层上依次沉积氮化硅和氧化硅,对氮化硅和氧化硅进行快速热退火处理得到低温钝化层,其中加热温度小于或者等于600℃。

S282:对低温钝化层图形化处理得到接触孔,以裸露出栅极层、第一源漏极层和第二源漏极层。

在本实施例中,步骤S28可以包括步骤S281~S282,下面一并进行说明:

在低温隔离层24、低温栅极介质层25和栅极层26上依次沉积氮化硅和氧化硅作为低温钝化层材料,氮化硅层的目的是防止栅极层26的金属在随后的过程中被氧化,以及保护器件免受外界水汽等影响。

低温钝化层材料沉积后,对P型硅片21进行加热以激活低温钝化层材料,激活过程可以是在不超过600℃的温度下进行快速热退火,或者通过加热台退火。

在得到低温钝化层28后,在低温钝化层28上进行图形化处理形成接触孔和接触孔两侧的岛体,并且在接触孔裸露出栅极层26、第一源漏极层271和第二源漏极层272。

S29:在低温钝化层、栅极层和源漏极层上设置金属层,金属层连接栅极层和源漏极层。

S291:在低温钝化层和接触孔上沉积金属,对金属图形化处理。

S292:对金属层进行合成气体退火处理。

在本实施例中,步骤S29可以包括步骤S291~S292,下面一并进行说明:

在低温钝化层28和接触孔中沉积金属层材料,将金属材料图形化形成金属层29,金属层29设置于低温钝化层28、栅极层26和源漏极层27上,且与两岛体中的低温栅极介质层25连接,并将金属层材料图形化为连接线和测试焊盘。其中,金属层材料可以为硅和铝的混合物,例如,金属层材料为铝和硅的混合物,硅(Si)在金属层材料中占有1%,金属层29的厚度为700nm。对金属层29采用合成气体(Forming gas)退火的方式进行图形化,能够改善铝与硅之间的接触。

在上述实施方式的基础上,请一并参阅图5和图6,图5是本申请一种薄膜晶体管的制造方法又一实施例的流程示意图,图6是本申请一种薄膜晶体管又一实施例的结构示意图。在低温PMOS工艺中,薄膜晶体管300的制造方法具体可以包括以下步骤:

S31:准备N型硅片。

在低温PMOS工艺中,硅片31为N型硅片31,因此不需要形成N阱和P场。

S32:在硅片上设置低温隔离层。

在N型硅片31上设置低温隔离层32,以定义有源器件。

S33:在硅片上设置体掺杂区,其中体掺杂区设置于硅片朝向低温隔离层的一侧。

在低温PMOS工艺中,对体接触区进行N型掺杂,该步骤类似于上述实施例中低温CMOS工艺中NMOS的源漏(S/D)掺杂。在本实施例中,对N型硅片31进行图形化处理得到第一体掺杂区33,其中第一体掺杂区33设置于N型硅片31朝向低温隔离层32的一侧。

S34:对体掺杂区进行热退火处理,其中加热温度为600℃。

在形成体掺杂区33后,对N型硅片31进行热退火处理,其中热退火处理时的温度大于600℃。

S35:在硅片上依次设置低温栅极介质层和栅极层。

S351:在硅片和低温隔离层上设置低温栅极介质层。

S352:在低温栅极介质层上沉积栅极金属,对栅极金属进行干法刻蚀处理以图形化形成栅极层。

在本实施例中,步骤S35可以包括步骤S351~S352,下面一并进行说明:

在N型硅片31和低温隔离层32上设置低温栅极介质层34,与上述低温CMOS工艺中类似,在低温栅极介质层34上沉积栅极金属,对栅极金属图形化是将光刻胶图形转移到金属层38上,再进行干法刻蚀处理以图形化形成栅极层35。

S36:在硅片中设置源漏极层。

对N型硅片31注入第三P型离子以进行掺杂处理,与上述低温CMOS工艺中的PMOS器件的源漏(S/D)掺杂过程类似,将源漏(S/D)区暴露于P型离子注入机或离子轰击,得到第三源漏极层36,其中第三源漏极层36形成于N型硅片31中,且设置于低温栅极介质层34和N型硅片31之间。

S37:在低温栅极介质层和栅极层上设置低温钝化层。

在栅极层35和低温栅极介质层34上依次沉积氮化硅和氧化硅,得到低温钝化层37。

S38:在低温钝化层、栅极层和源漏极层上设置金属层,金属层连接栅极层和源漏极层。

与上述低温CMOS工艺中类似,在低温钝化层37、栅极层35和源漏极层36上设置金属层材料,固化后得到金属层38。

在上述实施方式的基础上,请一并参阅图7和图8,图7是本申请一种薄膜晶体管的制造方法再一实施例的流程示意图,图8是本申请一种薄膜晶体管再一实施例的结构示意图。在低温NMOS工艺中,薄膜晶体管400的制造方法具体可以包括以下步骤:

S41:准备P型硅片。

在低温NMOS工艺中,硅片41为P型硅片41。

S42:在硅片上设置低温隔离层。

S43:在硅片上设置体掺杂区,其中体掺杂区设置于硅片朝向低温隔离层的一侧。

与低温PMOS工艺不同,低温NMOS的体区域采用P型掺杂剂掺杂,即在P型硅片41上注入第四P型离子以进行体掺杂处理得到第二体掺杂区43,其中第二体掺杂区43设置于P型硅片41朝向低温隔离层42的一侧。

S44:对体掺杂区进行热退火处理,其中加热温度大于600℃。

S45:在硅片上依次设置低温栅极介质层和栅极层。

S451:在硅片和低温隔离层上设置低温栅极介质层。

S452:在低温栅极介质层上沉积栅极金属,对栅极金属进行干法刻蚀处理以图形化形成栅极层。

S46:在硅片中设置源漏极层。

与低温PMOS工艺不同,源漏极层46采用N型掺杂,即对P型硅片41进行图形化处理,得到第四源漏极层46,其中第四源漏极层46形成于P型硅片41中,且设置于低温栅极介质层44和P型硅片41之间。

S47:在低温栅极介质层和栅极层上设置低温钝化层。

在栅极层45和低温栅极介质层44上依次沉积氮化硅和氧化硅,对氮化硅和氧化硅进行热退火处理,以激活N型掺杂剂,得到低温钝化层47。

S48:在低温钝化层、栅极层和源漏极层上设置金属层,金属层连接栅极层和源漏极层。

与上述低温CMOS工艺中类似,在低温钝化层47、栅极层45和源漏极层46上设置金属材料,固化后得到金属层48。

本申请提供一种用于高分辨率显示器的低温金属氧化物半导体工艺,商业化的TFT背板能够处理PPI<1000的FPD,昂贵的硅芯片工艺能够处理具有PPI>1000的小尺寸FPDS,没有制造超高PPI显示器的成本效益高的FPD工业兼容工艺。本申请降低了硅基显示面板的制造成本,缩短了生产成本、加工时间,填补IC工艺与TFT面板技术之间的空白。

本申请中所揭示的技术方案能够实现低温、低成本、工业兼容的硅MOSFET制作工艺,即低温CMOS工艺、低温PMOS工艺和低温NMOS工艺。通过这三种低温工艺,均能够低成本、大面积制造薄膜晶体管,继而制作高分辨率虚拟现实/增强现实设备包括微型OLED投影仪,使得基于硅的液晶显示器成为可能。

本申请提供一种薄膜晶体管的制造方法,该制造方法包括准备硅片;在硅片上设置低温隔离层;在硅片上依次设置低温栅极介质层和栅极层;在硅片中设置源漏极层;在低温栅极介质层和栅极层上设置低温钝化层;在低温钝化层、栅极层和源漏极层上设置金属层,金属层连接栅极层和源漏极层。通过在低温状态下,在硅片上设置低温隔离层、低温栅极介质层、栅极层、源漏极层、低温钝化层和金属层,能够降低制造成本,提高制造高分辨率显示中的薄膜晶体管的成功率。

对应上述的方法,本申请提出一种薄膜晶体管,请参阅图1,图1是本申请一种薄膜晶体管一实施例的结构示意图。本申请所揭示的薄膜晶体管100包括硅片11、低温隔离层12、低温栅极介质层13、栅极层14、源漏极层15、低温钝化层16和金属层17。

具体来说,低温隔离层12形成于硅片11的一侧;低温栅极介质层13,形成于硅片11靠近低温隔离层12的一侧;栅极层14,形成于低温栅极介质层13背离硅片11的一侧;源漏极层15,形成于硅片11中;低温钝化层16,形成于低温栅极介质层13和栅极层14上;金属层17,形成于低温钝化层16、栅极层14和源漏极层15上,连接栅极层14和源漏极层15。

本申请提供一种薄膜晶体管100,能够降低制造成本,提高制造高分辨率显示中的薄膜晶体管的成功率。

对应上述的薄膜晶体管100,本申请提出一种显示面板500,请参阅图9,图9是本申请一种显示面板一实施例的结构示意图。本申请所揭示的显示面板500包括薄膜晶体管51,薄膜晶体管51的具体实施方式由于上述类似,此处不做赘述。

本申请提供一种显示面板500,能够降低制造成本,提高制造高分辨率显示中的薄膜晶体管的成功率。

以上所述,仅是本发明的较佳实施例而已,并非对本发明作任何形式上的限制,任何本领域技术人员,在不脱离本发明技术方案范围内,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化与修饰,均仍属于本发明技术方案的范围内。

Claims (10)

1.一种薄膜晶体管的制造方法,其特征在于,所述制造方法包括:

准备硅片;

在所述硅片上设置低温隔离层;

在所述硅片上依次设置低温栅极介质层和栅极层;

在所述硅片中设置源漏极层;

在所述低温栅极介质层和所述栅极层上设置低温钝化层;

在所述低温钝化层、所述栅极层和所述源漏极层上设置金属层,所述金属层连接所述栅极层和所述源漏极层。

2.根据权利要求1所述的方法,其特征在于,所述硅片为P型硅片,在所述硅片上设置低温隔离层的步骤之前包括:

在所述P型硅片上设置第一二氧化硅层;

在所述第一二氧化硅层上设置光刻胶并进行图形化处理,注入第一N型离子以在所述P型硅片和所述第一二氧化硅层之间形成N阱,除去所述光刻胶;

在所述第一二氧化硅层上设置所述光刻胶并进行图形化处理,注入第一P型离子以在所述P型硅片和所述第一二氧化硅层之间形成P场,除去所述光刻胶和所述第一二氧化硅层;

在所述硅片上设置低温隔离层的步骤包括:

在所述P型硅片上沉积二氧化硅,对所述二氧化硅层进行图形化处理,得到第二二氧化硅层,对所述第二二氧化硅层图形化处理得到所述低温隔离层。

3.根据权利要求2所述的方法,其特征在于,在所述硅片上依次设置低温栅极介质层和栅极层的步骤包括:

在所述P型硅片上沉积栅极介质,对所述栅极介质图形化以形成所述低温栅极介质层;

在所述低温栅极介质层上沉积栅极金属以形成所述栅极层;

在所述硅片中设置源漏极层的步骤包括:

对所述N阱注入第二P型离子以进行掺杂处理,得到第一源漏极层;

对所述P型硅片注入N型离子以进行掺杂处理,得到第二源漏极层。

4.根据权利要求3所述的方法,其特征在于,在所述低温栅极介质层和所述栅极层上设置低温钝化层的步骤包括:

在所述低温隔离层、所述栅极层和所述低温栅极介质层上依次沉积氮化硅和氧化硅,对所述氮化硅和所述氧化硅进行快速热退火处理得到所述低温钝化层,其中加热温度小于或者等于600℃;

对所述低温钝化层图形化处理得到接触孔,以裸露出所述栅极层、所述第一源漏极层和所述第二源漏极层;

在所述低温钝化层、所述栅极层和所述源漏极层上设置金属层,所述金属层连接所述栅极层和所述源漏极层的步骤包括:

在所述低温钝化层和所述接触孔上沉积金属,对所述金属图形化处理;

对所述金属层进行合成气体退火处理。

5.根据权利要求1所述的方法,其特征在于,在所述硅片上依次设置低温栅极介质层和栅极层的步骤之前包括:

在所述硅片上设置体掺杂区,其中所述体掺杂区设置于所述硅片朝向所述低温隔离层的一侧;

对所述体掺杂区进行热退火处理,其中加热温度大于600℃;

在所述硅片上依次设置低温栅极介质层和栅极层的步骤包括:

在所述硅片和所述低温隔离层上设置所述低温栅极介质层;

在所述低温栅极介质层上沉积栅极金属,对所述栅极金属进行干法刻蚀处理以图形化形成所述栅极层;

在所述低温栅极介质层和所述栅极层上设置低温钝化层的步骤包括:

在所述栅极层和所述低温栅极介质层上依次沉积氮化硅和氧化硅,得到所述低温钝化层。

6.根据权利要求5所述的方法,其特征在于,所述硅片为N型硅片,在所述硅片上设置体掺杂区,其中所述体掺杂区设置于所述硅片朝向所述低温隔离层的一侧的步骤包括:

对所述N型硅片进行图形化处理得到第一体掺杂区,其中所述第一体掺杂区设置于所述N型硅片朝向所述低温隔离层的一侧;

在所述硅片和所述低温隔离层上设置所述低温栅极介质层的步骤包括:

在所述N型硅片和所述低温隔离层上设置所述低温栅极介质层;

在所述硅片中设置源漏极层的步骤包括:

对所述N型硅片注入第三P型离子以进行掺杂处理,得到第三源漏极层,其中所述第三源漏极层形成于所述N型硅片中。

7.根据权利要求5所述的方法,其特征在于,所述硅片为P型硅片,在所述硅片上设置体掺杂区,其中所述体掺杂区设置于所述硅片朝向所述低温隔离层的一侧的步骤包括:

在所述P型硅片上注入第四P型离子以进行体掺杂处理得到第二体掺杂区,其中所述第二体掺杂区设置于所述P型硅片朝向所述低温隔离层的一侧;

在所述硅片中设置源漏极层的步骤包括:

对所述P型硅片注入N型离子以进行掺杂处理得到第四源漏极层,其中所述第四源漏极层形成于所述硅片中。

8.根据权利要求7所述的方法,其特征在于,在所述低温栅极介质层和所述栅极层上设置低温钝化层的步骤包括:

在所述栅极层和所述低温栅极介质层上依次沉积氮化硅和氧化硅,对所述氮化硅和所述氧化硅进行热退火处理,得到所述低温钝化层。

9.一种薄膜晶体管,其特征在于,所述薄膜晶体管包括:

硅片和形成于所述硅片一侧的低温隔离层;

低温栅极介质层,形成于所述硅片靠近所述低温隔离层的一侧;

栅极层,形成于所述低温栅极介质层背离所述硅片的一侧;

源漏极层,形成于所述硅片中;

低温钝化层,形成于所述低温栅极介质层和所述栅极层上;

金属层,形成于所述低温钝化层、所述栅极层和所述源漏极层上,连接所述栅极层和所述源漏极层。

10.一种显示面板,其特征在于,所述显示面板包括如上述权利要求9所述的薄膜晶体管。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201910980595.4ACN110828379A (zh) | 2019-10-15 | 2019-10-15 | 一种薄膜晶体管的制造方法、薄膜晶体管及显示面板 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201910980595.4ACN110828379A (zh) | 2019-10-15 | 2019-10-15 | 一种薄膜晶体管的制造方法、薄膜晶体管及显示面板 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN110828379Atrue CN110828379A (zh) | 2020-02-21 |

Family

ID=69549522

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201910980595.4APendingCN110828379A (zh) | 2019-10-15 | 2019-10-15 | 一种薄膜晶体管的制造方法、薄膜晶体管及显示面板 |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN110828379A (zh) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN116295962A (zh)* | 2023-02-23 | 2023-06-23 | 深圳大学 | 具有微结构梯度化的复合柔性压力传感器及其制备方法 |

Citations (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0932117A2 (en)* | 1998-01-22 | 1999-07-28 | STMicroelectronics, Inc. | Touchpad providing screen cursor/pointer movement control |

| CN1877851A (zh)* | 1999-09-30 | 2006-12-13 | 株式会社半导体能源研究所 | 有机电致发光显示器件 |

| US8298875B1 (en)* | 2011-03-06 | 2012-10-30 | Monolithic 3D Inc. | Method for fabrication of a semiconductor device and structure |

| CN103794630A (zh)* | 2012-10-31 | 2014-05-14 | 乐金显示有限公司 | 用于制造有机电致发光显示器的方法 |

| CN104064583A (zh)* | 2014-05-29 | 2014-09-24 | 何东阳 | 一种超高分辨率amoled显示器件 |

| US20150287813A1 (en)* | 2010-04-23 | 2015-10-08 | Semiconductor Energy Laboratory Co., Ltd. | Method For Manufacturing Semiconductor Device |

| US20160027967A1 (en)* | 2014-07-25 | 2016-01-28 | Semiconductor Energy Laboratory Co., Ltd. | Stacked Structure, Input/output Device, Information Processing Device, and Manufacturing Method of Stacked Structure |

| CN105893985A (zh)* | 2016-05-05 | 2016-08-24 | 京东方科技集团股份有限公司 | 显示装置及其制造方法 |

| CN106654071A (zh)* | 2017-03-09 | 2017-05-10 | 南京迈智芯微光电科技有限公司 | 一种有机电致发光器件的制作与封装方法 |

| US20170263651A1 (en)* | 2016-03-11 | 2017-09-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, semiconductor wafer, module, electronic device, and manufacturing method the same |

| US20180277445A1 (en)* | 2017-03-22 | 2018-09-27 | International Business Machines Corporation | Vertical transistor top epitaxy source/drain and contact structure |

| CN108962967A (zh)* | 2018-08-03 | 2018-12-07 | 京东方科技集团股份有限公司 | 显示面板及其制造方法、显示装置及显示控制方法 |

| CN111133499A (zh)* | 2017-04-13 | 2020-05-08 | 香港北大青鸟显示有限公司 | Led-oled混合自发射显示器 |

- 2019

- 2019-10-15CNCN201910980595.4Apatent/CN110828379A/zhactivePending

Patent Citations (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0932117A2 (en)* | 1998-01-22 | 1999-07-28 | STMicroelectronics, Inc. | Touchpad providing screen cursor/pointer movement control |

| CN1877851A (zh)* | 1999-09-30 | 2006-12-13 | 株式会社半导体能源研究所 | 有机电致发光显示器件 |

| US20150287813A1 (en)* | 2010-04-23 | 2015-10-08 | Semiconductor Energy Laboratory Co., Ltd. | Method For Manufacturing Semiconductor Device |

| US8298875B1 (en)* | 2011-03-06 | 2012-10-30 | Monolithic 3D Inc. | Method for fabrication of a semiconductor device and structure |

| CN103794630A (zh)* | 2012-10-31 | 2014-05-14 | 乐金显示有限公司 | 用于制造有机电致发光显示器的方法 |

| CN104064583A (zh)* | 2014-05-29 | 2014-09-24 | 何东阳 | 一种超高分辨率amoled显示器件 |

| US20160027967A1 (en)* | 2014-07-25 | 2016-01-28 | Semiconductor Energy Laboratory Co., Ltd. | Stacked Structure, Input/output Device, Information Processing Device, and Manufacturing Method of Stacked Structure |

| US20170263651A1 (en)* | 2016-03-11 | 2017-09-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, semiconductor wafer, module, electronic device, and manufacturing method the same |

| CN105893985A (zh)* | 2016-05-05 | 2016-08-24 | 京东方科技集团股份有限公司 | 显示装置及其制造方法 |

| CN106654071A (zh)* | 2017-03-09 | 2017-05-10 | 南京迈智芯微光电科技有限公司 | 一种有机电致发光器件的制作与封装方法 |

| US20180277445A1 (en)* | 2017-03-22 | 2018-09-27 | International Business Machines Corporation | Vertical transistor top epitaxy source/drain and contact structure |

| CN111133499A (zh)* | 2017-04-13 | 2020-05-08 | 香港北大青鸟显示有限公司 | Led-oled混合自发射显示器 |

| CN108962967A (zh)* | 2018-08-03 | 2018-12-07 | 京东方科技集团股份有限公司 | 显示面板及其制造方法、显示装置及显示控制方法 |

Non-Patent Citations (1)

| Title |

|---|

| 严国荣: "硅基液晶显示屏及其应用", 《电声技术》* |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN116295962A (zh)* | 2023-02-23 | 2023-06-23 | 深圳大学 | 具有微结构梯度化的复合柔性压力传感器及其制备方法 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8183135B2 (en) | Method for manufacturing thin film transistor having hydrogen feeding layer formed between a metal gate and a gate insulating film | |

| KR101491567B1 (ko) | 픽셀 및 구동영역에서 상이한 전기적 특성들을 갖는 박막트랜지스터 장치를 가지는 디스플레이 및 이를 제조하는방법 | |

| CN107482066B (zh) | 薄膜晶体管及其制备方法、阵列基板和显示装置 | |

| US9716119B2 (en) | Manufacturing method of dual gate TFT substrate and structure thereof | |

| US6562671B2 (en) | Semiconductor display device and manufacturing method thereof | |

| WO2014134925A1 (zh) | 多晶硅薄膜晶体管及其制备方法、阵列基板 | |

| US10290663B2 (en) | Manufacturing method of thin film transistor and manufacturing method of array substrate | |

| WO2015096355A1 (zh) | 阵列基板及其制作方法、显示装置 | |

| CN103579115A (zh) | 互补式薄膜晶体管及其制备方法、阵列基板、显示装置 | |

| US9159773B2 (en) | Thin film transistor and active matrix organic light emitting diode assembly | |

| US10957606B2 (en) | Manufacturing method of complementary metal oxide semiconductor transistor and manufacturing method of array substrate | |

| CN110828379A (zh) | 一种薄膜晶体管的制造方法、薄膜晶体管及显示面板 | |

| US7704890B2 (en) | Method for fabricating thin film transistor and pixel structure | |

| CN101150092A (zh) | 互补式金属氧化物半导体薄膜晶体管的制造方法 | |

| JP5188106B2 (ja) | 薄膜トランジスタデバイスを含む画像表示システムおよびその製造方法 | |

| JP4006993B2 (ja) | 薄膜トランジスタの製造方法,液晶表示装置の製造方法,エレクトロルミネッセンス表示装置の製造方法 | |

| US6887745B2 (en) | Polysilicon thin film transistor and method of forming the same | |

| CN103123902A (zh) | 半导体层结构、多晶硅薄膜晶体管、制作方法、显示装置 | |

| KR102872571B1 (ko) | 다층 층간 유전체 구조들을 갖는 트랜지스터 디바이스들 | |

| TWI785545B (zh) | 工序簡化的透明薄膜電晶體的製法 | |

| US8030143B2 (en) | Method of forming a display device by using separate masks in forming source and drain regions of MOS transistors | |

| TWI325612B (en) | Method for manufacturing complementary metal-oxide-semiconductor thin film transistor | |

| US7064017B2 (en) | Method of forming a CMOS transistor | |

| CN101593732B (zh) | 显示装置及其形成方法,以及包含显示装置的电子装置 | |

| KR20240157087A (ko) | 다층 층간 유전체 구조들을 갖는 트랜지스터 디바이스들 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PB01 | Publication | ||

| PB01 | Publication | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| RJ01 | Rejection of invention patent application after publication | ||

| RJ01 | Rejection of invention patent application after publication | Application publication date:20200221 |