CN110163354B - Computing device and method - Google Patents

Computing device and methodDownload PDFInfo

- Publication number

- CN110163354B CN110163354BCN201910195598.7ACN201910195598ACN110163354BCN 110163354 BCN110163354 BCN 110163354BCN 201910195598 ACN201910195598 ACN 201910195598ACN 110163354 BCN110163354 BCN 110163354B

- Authority

- CN

- China

- Prior art keywords

- data

- processing circuit

- input data

- result

- slave

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F7/00—Methods or arrangements for processing data by operating upon the order or content of the data handled

- G06F7/38—Methods or arrangements for performing computations using exclusively denominational number representation, e.g. using binary, ternary, decimal representation

- G06F7/48—Methods or arrangements for performing computations using exclusively denominational number representation, e.g. using binary, ternary, decimal representation using non-contact-making devices, e.g. tube, solid state device; using unspecified devices

- G06F7/57—Arithmetic logic units [ALU], i.e. arrangements or devices for performing two or more of the operations covered by groups G06F7/483 – G06F7/556 or for performing logical operations

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/06—Physical realisation, i.e. hardware implementation of neural networks, neurons or parts of neurons

- G06N3/063—Physical realisation, i.e. hardware implementation of neural networks, neurons or parts of neurons using electronic means

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Computing Systems (AREA)

- Health & Medical Sciences (AREA)

- Life Sciences & Earth Sciences (AREA)

- Biomedical Technology (AREA)

- Biophysics (AREA)

- General Engineering & Computer Science (AREA)

- Neurology (AREA)

- Computational Mathematics (AREA)

- Molecular Biology (AREA)

- Evolutionary Computation (AREA)

- Data Mining & Analysis (AREA)

- Computational Linguistics (AREA)

- Mathematical Physics (AREA)

- Software Systems (AREA)

- Artificial Intelligence (AREA)

- General Health & Medical Sciences (AREA)

- Mathematical Analysis (AREA)

- Mathematical Optimization (AREA)

- Pure & Applied Mathematics (AREA)

- Advance Control (AREA)

- Feedback Control In General (AREA)

- Management, Administration, Business Operations System, And Electronic Commerce (AREA)

- Image Processing (AREA)

Abstract

Translated fromChineseDescription

Translated fromChinese技术领域technical field

本申请涉及信息处理技术领域,具体涉及一种计算装置及方法。The present application relates to the technical field of information processing, and in particular, to a computing device and method.

背景技术Background technique

随着信息技术的不断发展和人们日益增长的需求,人们对信息及时性的要求越来越高了。目前,终端对信息的获取以及处理均是基于通用处理器获得的。With the continuous development of information technology and people's increasing demands, people's requirements for information timeliness are getting higher and higher. At present, the terminal acquires and processes information based on a general-purpose processor.

在实践中发现,这种基于通用处理器运行软件程序来处理信息的方式,受限于通用处理器的运行速率,特别是在通用处理器负荷较大的情况下,信息处理效率较低、时延较大,对于信息处理的计算模型例如训练模型来说,训练运算的计算量更大,通用的处理器完成训练运算的时间长,效率低。In practice, it is found that this method of processing information based on general-purpose processors running software programs is limited by the operating speed of the general-purpose processors, especially when the general-purpose processors are heavily loaded, the information processing efficiency is low, and the time is limited. If the delay is large, for a computing model of information processing, such as a training model, the computing amount of the training operation is larger, and the general-purpose processor takes a long time to complete the training operation, and the efficiency is low.

发明内容SUMMARY OF THE INVENTION

本申请实施例提供了一种计算装置及方法,可提升运算的处理速度,提高效率。The embodiments of the present application provide a computing device and method, which can improve the processing speed of the operation and improve the efficiency.

第一方面,本申请实施例提供一种计算装置包括:存储单元、转换单元、运算单元以及控制器单元;所述存储单元包括缓存和寄存器,In a first aspect, an embodiment of the present application provides a computing device including: a storage unit, a conversion unit, an arithmetic unit, and a controller unit; the storage unit includes a cache and a register,

所述控制器单元,用于确定第一输入数据的小数点位置和定点数据的位宽;所述定点数据的位宽为所述第一输入数据转换为定点数据的位宽;The controller unit is configured to determine the decimal point position of the first input data and the bit width of the fixed-point data; the bit width of the fixed-point data is the bit width of the first input data converted into the fixed-point data;

所述运算单元,用于初始化所述第一输入数据的小数点位置和调整所述第一输入数据的小数点位置;并将所述调整后的第一输入数据的小数点位置存储至所述存储单元的缓存中,The arithmetic unit is used to initialize the decimal point position of the first input data and adjust the decimal point position of the first input data; and store the adjusted decimal point position of the first input data in the storage unit. in cache,

所述控制器单元,用于从所述寄存器中获取第一输入数据和多个运算指令,并从所述缓存中获取所述调整后的第一输入数据的小数点位置;将所述调整后的第一输入数据的小数点位置及所述第一输入数据传输至所述转换单元;The controller unit is configured to obtain the first input data and a plurality of operation instructions from the register, and obtain the decimal point position of the adjusted first input data from the cache; The decimal point position of the first input data and the first input data are transmitted to the conversion unit;

所述转换单元,用于根据所述调整后的第一输入数据的小数点位置将所述第一输入数据转换为第二输入数据;the conversion unit, configured to convert the first input data into the second input data according to the position of the decimal point of the adjusted first input data;

其中,所述运算单元初始化所述第一输入数据的小数点位置,包括:Wherein, the operation unit initializes the decimal point position of the first input data, including:

根据经验值常量初始化所述第一输入数据的小数点位置。The decimal point position of the first input data is initialized according to an empirical value constant.

在一种可能的实施例中,所述运算单元调整所述第一输入数据的小数点位置,包括:In a possible embodiment, the operation unit adjusts the decimal point position of the first input data, including:

根据所述第一输入数据中数据绝对值的最大值单步向上调整所述第一输入数据的小数点位置,或者;根据所述第一输入数据中数据绝对值的最大值逐步向上调整所述第一输入数据的小数点位置,或者;根据所述第一输入数据分布单步向上调整所述第一输入数据的小数点位置,或者;根据所述第一输入数据分布逐步向上调整所述第一输入数据的小数点位置,或者;根据所述第一输入数据绝对值最大值向下调整所述第一输入数据的小数点位置。Adjust the decimal point position of the first input data upward in a single step according to the maximum value of the absolute value of the data in the first input data, or; gradually adjust the first input data upward according to the maximum value of the absolute value of the data in the first input data. The decimal point position of the input data, or; adjust the decimal point position of the first input data upward in a single step according to the distribution of the first input data, or; adjust the first input data gradually upward according to the distribution of the first input data The decimal point position of the first input data, or: adjust the decimal point position of the first input data downward according to the maximum absolute value of the first input data.

在一种可能的实施例中,所述计算装置用于执行机器学习计算,In a possible embodiment, the computing device is configured to perform machine learning computations,

所述控制器单元,还用于将所述多个运算指令传输至所述运算单元;the controller unit, further configured to transmit the plurality of operation instructions to the operation unit;

所述转换单元,还用于将所述第二输入数据传输至所述运算单元;the conversion unit, further configured to transmit the second input data to the operation unit;

所述运算单元,还用于根据所述多个运算指令对所述第二输入数据进行运算,以得到运算结果。The operation unit is further configured to perform an operation on the second input data according to the plurality of operation instructions to obtain an operation result.

在一种可能的实施例中,所述机器学习计算包括:人工神经网络运算,所述第一输入数据包括:输入神经元数据和权值数据;所述计算结果为输出神经元数据。In a possible embodiment, the machine learning calculation includes: artificial neural network operation, the first input data includes: input neuron data and weight data; and the calculation result is output neuron data.

在一种可能的实施例中,所述运算单元包括一个主处理电路和多个从处理电路;In a possible embodiment, the operation unit includes a master processing circuit and a plurality of slave processing circuits;

所述主处理电路,用于对所述第二输入数据进行执行前序处理以及与所述多个从处理电路之间传输数据和所述多个运算指令;the master processing circuit, configured to perform pre-processing on the second input data and transmit data and the multiple operation instructions with the multiple slave processing circuits;

所述多个从处理电路,用于依据从所述主处理电路传输第二输入数据以及所述多个运算指令并执行中间运算得到多个中间结果,并将多个中间结果传输给所述主处理电路;The plurality of slave processing circuits are configured to obtain a plurality of intermediate results according to transmitting the second input data and the plurality of operation instructions from the main processing circuit and performing intermediate operations, and transmit the plurality of intermediate results to the master processing circuit;

所述主处理电路,用于对所述多个中间结果执行后续处理得到所述运算结果。The main processing circuit is configured to perform subsequent processing on the plurality of intermediate results to obtain the operation result.

在一种可能的实施例中,所述计算装置还包括:直接内存访问DMA单元;In a possible embodiment, the computing device further includes: a direct memory access DMA unit;

所述缓存,还用于存储所述第一输入数据;其中,所述缓存包括高速暂存缓存;The cache is also used to store the first input data; wherein, the cache includes a high-speed temporary cache;

所述寄存器,还用于存储所述第一输入数据中标量数据;The register is also used to store scalar data in the first input data;

所述DMA单元,用于从所述存储单元中读取数据或者向所述存储单元存储数据。The DMA unit is configured to read data from the storage unit or store data to the storage unit.

在一种可能的实施例中,当所述第一输入数据为定点数据时,所述运算单元还包括:In a possible embodiment, when the first input data is fixed-point data, the operation unit further includes:

推导单元,用于根据所述第一输入数据的小数点位置,推导得到一个或者多个中间结果的小数点位置,其中所述一个或多个中间结果为根据所述第一输入数据运算得到的。A deriving unit, configured to derive the decimal point position of one or more intermediate results according to the decimal point position of the first input data, wherein the one or more intermediate results are obtained by operation according to the first input data.

在一种可能的实施例中,所述运算单元还包括:数据缓存单元,用于缓存所述一个或多个中间结果。In a possible embodiment, the operation unit further includes: a data cache unit, configured to cache the one or more intermediate results.

在一种可能的实施例中,所述运算单元包括:树型模块,所述树型模块包括:一个根端口和多个支端口,所述树型模块的根端口连接所述主处理电路,所述树型模块的多个支端口分别连接多个从处理电路中的一个从处理电路;In a possible embodiment, the operation unit includes: a tree module, the tree module includes: a root port and a plurality of branch ports, the root port of the tree module is connected to the main processing circuit, The multiple branch ports of the tree module are respectively connected to one slave processing circuit in the multiple slave processing circuits;

所述树型模块,用于转发所述主处理电路与所述多个从处理电路之间的数据以及运算指令;其中,所述树型模型为n叉树结构,所述n为大于或等于2的整数。The tree-type module is used to forward data and operation instructions between the master processing circuit and the plurality of slave processing circuits; wherein, the tree-type model is an n-ary tree structure, and n is greater than or equal to An integer of 2.

在一种可能的实施例中,所述运算单元还包括分支处理电路,In a possible embodiment, the operation unit further includes a branch processing circuit,

所述主处理电路,具体用于确定所述输入神经元为广播数据,权值为分发数据,将一个分发数据分配成多个数据块,将所述多个数据块中的至少一个数据块、广播数据以及多个运算指令中的至少一个运算指令发送给所述分支处理电路;The main processing circuit is specifically configured to determine that the input neuron is broadcast data, the weight is distribution data, allocate one distribution data into multiple data blocks, and divide at least one data block, sending broadcast data and at least one operation instruction among the plurality of operation instructions to the branch processing circuit;

所述分支处理电路,用于转发所述主处理电路与所述多个从处理电路之间的数据块、广播数据以及运算指令;The branch processing circuit is configured to forward data blocks, broadcast data and operation instructions between the master processing circuit and the plurality of slave processing circuits;

所述多个从处理电路,用于依据该运算指令对接收到的数据块以及广播数据执行运算得到中间结果,并将中间结果传输给所述分支处理电路;The plurality of slave processing circuits are configured to perform operations on the received data blocks and broadcast data according to the operation instructions to obtain intermediate results, and transmit the intermediate results to the branch processing circuits;

所述主处理电路,还用于将所述分支处理电路发送的中间结果进行后续处理得到所述运算指令的结果,将所述计算指令的结果发送至所述控制器单元。The main processing circuit is further configured to perform subsequent processing on the intermediate result sent by the branch processing circuit to obtain the result of the operation instruction, and send the result of the calculation instruction to the controller unit.

在一种可能的实施例中,所述多个从处理电路呈阵列分布;每个从处理电路与相邻的其他从处理电路连接,所述主处理电路连接所述多个从处理电路中的K个从处理电路,所述K个从处理电路为:第1行的n个从处理电路、第m行的n个从处理电路以及第1列的m个从处理电路;In a possible embodiment, the plurality of slave processing circuits are distributed in an array; each slave processing circuit is connected to other adjacent slave processing circuits, and the master processing circuit is connected to one of the plurality of slave processing circuits. K slave processing circuits, the K slave processing circuits are: n slave processing circuits in the first row, n slave processing circuits in the mth row, and m slave processing circuits in the first column;

所述K个从处理电路,用于在所述主处理电路以及多个从处理电路之间的数据以及指令的转发;The K slave processing circuits are used for data and instruction forwarding between the master processing circuit and a plurality of slave processing circuits;

所述主处理电路,还用于确定所述输入神经元为广播数据,权值为分发数据,将一个分发数据分配成多个数据块,将所述多个数据块中的至少一个数据块以及多个运算指令中的至少一个运算指令发送给所述K个从处理电路;The main processing circuit is further configured to determine that the input neuron is broadcast data, the weight is distribution data, distribute one distribution data into a plurality of data blocks, and assign at least one data block of the plurality of data blocks and at least one operation instruction in the plurality of operation instructions is sent to the K slave processing circuits;

所述K个从处理电路,用于转换所述主处理电路与所述多个从处理电路之间的数据;the K slave processing circuits for converting data between the master processing circuit and the plurality of slave processing circuits;

所述多个从处理电路,用于依据所述运算指令对接收到的数据块执行运算得到中间结果,并将运算结果传输给所述K个从处理电路;The multiple slave processing circuits are configured to perform operations on the received data blocks according to the operation instructions to obtain intermediate results, and transmit the operation results to the K slave processing circuits;

所述主处理电路,用于将所述K个从处理电路发送的中间结果进行处理得到该计算指令的结果,将该计算指令的结果发送给所述控制器单元。The main processing circuit is configured to process the K intermediate results sent from the processing circuit to obtain the result of the calculation instruction, and send the result of the calculation instruction to the controller unit.

在一种可能的实施例中,所述主处理电路,具体用于将多个处理电路发送的中间结果进行组合排序得到该计算指令的结果;In a possible embodiment, the main processing circuit is specifically configured to combine and sort the intermediate results sent by the multiple processing circuits to obtain the result of the calculation instruction;

或所述主处理电路,具体用于将多个处理电路的发送的中间结果进行组合排序以及激活处理后得到该计算指令的结果。Or the main processing circuit is specifically configured to combine, sort and activate the intermediate results sent by the multiple processing circuits to obtain the result of the calculation instruction.

在一种可能的实施例中,所述主处理电路包括:激活处理电路和加法处理电路中的一种或任意组合;In a possible embodiment, the main processing circuit includes: one or any combination of an activation processing circuit and an addition processing circuit;

所述激活处理电路,用于执行主处理电路内数据的激活运算;The activation processing circuit is used to execute the activation operation of the data in the main processing circuit;

所述加法处理电路,用于执行加法运算或累加运算。The addition processing circuit is used for performing addition operation or accumulation operation.

所述从处理电路包括:The slave processing circuit includes:

乘法处理电路,用于对接收到的数据块执行乘积运算得到乘积结果;a multiplication processing circuit, which is used to perform a multiplication operation on the received data block to obtain a multiplication result;

累加处理电路,用于对该乘积结果执行累加运算得到该中间结果。The accumulation processing circuit is used for performing accumulation operation on the product result to obtain the intermediate result.

第二方面,本申请实施例提供一种计算方法,包括:In a second aspect, an embodiment of the present application provides a computing method, including:

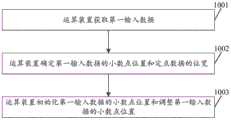

控制器单元确定第一输入数据的小数点位置和定点数据的位宽,所述定点数据的位宽为所述第一输入数据的为定点数据的位宽;运算单元初始化所述第一输入数据的小数点位置和调整所述第一输入数据的小数点位置;转换单元获取调整后的第一输入数据的小数点位置,并根据所述调整后的小数点位置将所述第一输入数据转换为第二输入数据;其中,所述运算单元初始化所述第一输入数据的小数点位置,包括:根据经验值常量初始化所述第一输入数据的小数点位置。The controller unit determines the decimal point position of the first input data and the bit width of the fixed-point data, and the bit width of the fixed-point data is the bit width of the fixed-point data of the first input data; the operation unit initializes the first input data. Decimal point position and adjusting the decimal point position of the first input data; the conversion unit obtains the adjusted decimal point position of the first input data, and converts the first input data into the second input data according to the adjusted decimal point position ; wherein, the operation unit initializing the decimal point position of the first input data includes: initializing the decimal point position of the first input data according to an empirical value constant.

在一种可能的实施例中,所述运算单元调整所述第一输入数据的小数点位置,包括:In a possible embodiment, the operation unit adjusts the decimal point position of the first input data, including:

根据所述第一输入数据中数据绝对值的最大值单步向上调整所述第一输入数据的小数点位置,或者;根据所述第一输入数据中数据绝对值的最大值逐步向上调整所述第一输入数据的小数点位置,或者;根据所述第一输入数据分布单步向上调整所述第一输入数据的小数点位置,或者;根据所述第一输入数据分布逐步向上调整所述第一输入数据的小数点位置,或者;根据所述第一输入数据绝对值最大值向下调整所述第一输入数据的小数点位置。Adjust the decimal point position of the first input data upward in a single step according to the maximum value of the absolute value of the data in the first input data, or; gradually adjust the first input data upward according to the maximum value of the absolute value of the data in the first input data. The decimal point position of the input data, or; adjust the decimal point position of the first input data upward in a single step according to the distribution of the first input data, or; adjust the first input data gradually upward according to the distribution of the first input data The decimal point position of the first input data, or: adjust the decimal point position of the first input data downward according to the maximum absolute value of the first input data.

在一种可能的实施例中,所述计算方法为用于执行机器学习计算的方法,所述方法还包括:所述运算单元根据所述多个运算指令对所述第二输入数据进行运算,以得到运算结果。In a possible embodiment, the calculation method is a method for performing machine learning calculation, and the method further includes: the operation unit performs an operation on the second input data according to the plurality of operation instructions, to get the result of the operation.

在一种可能的实施例中,所述机器学习计算包括:人工神经网络运算,所述第一输入数据包括:输入神经元和权值;所述计算结果为输出神经元。In a possible embodiment, the machine learning calculation includes: an artificial neural network operation, the first input data includes: an input neuron and a weight; the calculation result is an output neuron.

在一种可能的实施例中,当所述第一输入数据为定点数据时,所述方法还包括:In a possible embodiment, when the first input data is fixed-point data, the method further includes:

所述运算单元根据所述第一输入数据的小数点位置,推导得到一个或者多个中间结果的小数点位置,其中所述一个或多个中间结果为根据所述第一输入数据运算得到的。The operation unit derives the decimal point position of one or more intermediate results according to the decimal point position of the first input data, wherein the one or more intermediate results are obtained by operation according to the first input data.

第三方面,本发明实施例提供了一种机器学习运算装置,该机器学习运算装置包括一个或者多个第一方面所述的计算装置。该机器学习运算装置用于从其他处理装置中获取待运算数据和控制信息,并执行指定的机器学习运算,将执行结果通过I/O接口传递给其他处理装置;In a third aspect, an embodiment of the present invention provides a machine learning computing device, where the machine learning computing device includes one or more computing devices described in the first aspect. The machine learning computing device is used to obtain the data to be computed and control information from other processing devices, execute the specified machine learning operation, and transmit the execution result to other processing devices through the I/O interface;

当所述机器学习运算装置包含多个所述计算装置时,所述多个所述计算装置间可以通过特定的结构进行链接并传输数据;When the machine learning computing device includes a plurality of the computing devices, the plurality of the computing devices can be linked through a specific structure and data can be transmitted;

其中,多个所述计算装置通过PCIE总线进行互联并传输数据,以支持更大规模的机器学习的运算;多个所述计算装置共享同一控制系统或拥有各自的控制系统;多个所述计算装置共享内存或者拥有各自的内存;多个所述计算装置的互联方式是任意互联拓扑。Wherein, a plurality of the computing devices are interconnected and transmit data through the PCIE bus to support larger-scale machine learning operations; a plurality of the computing devices share the same control system or have their own control systems; a plurality of the computing devices The devices share memory or have their own memory; the interconnection of a plurality of the computing devices is any interconnection topology.

第四方面,本发明实施例提供了一种组合处理装置,该组合处理装置包括如第三方面所述的机器学习处理装置、通用互联接口,和其他处理装置。该机器学习运算装置与上述其他处理装置进行交互,共同完成用户指定的操作。该组合处理装置还可以包括存储装置,该存储装置分别与所述机器学习运算装置和所述其他处理装置连接,用于保存所述机器学习运算装置和所述其他处理装置的数据。In a fourth aspect, an embodiment of the present invention provides a combined processing device, where the combined processing device includes the machine learning processing device described in the third aspect, a universal interconnection interface, and other processing devices. The machine learning computing device interacts with the above-mentioned other processing devices to jointly complete the operation specified by the user. The combined processing device may further include a storage device, which is respectively connected to the machine learning computing device and the other processing device, and is used for saving the data of the machine learning computing device and the other processing device.

第五方面,本发明实施例提供了一种神经网络芯片,该神经网络芯片包括上述第一方面所述的计算装置、上述第三方面所述的机器学习运算装置或者上述第四方面所述的组合处理装置。In a fifth aspect, an embodiment of the present invention provides a neural network chip, where the neural network chip includes the computing device described in the first aspect, the machine learning computing device described in the third aspect, or the fourth aspect described above. Combined processing unit.

第六方面,本发明实施例提供了一种神经网络芯片封装结构,该神经网络芯片封装结构包括上述第五方面所述的神经网络芯片;In a sixth aspect, an embodiment of the present invention provides a neural network chip packaging structure, and the neural network chip packaging structure includes the neural network chip described in the fifth aspect;

第七方面,本发明实施例提供了一种板卡,该板卡包括存储器件、接口装置和控制器件以及上述第五方面所述的神经网络芯片;In a seventh aspect, an embodiment of the present invention provides a board card, the board card includes a storage device, an interface device, a control device, and the neural network chip described in the fifth aspect;

其中,所述神经网络芯片与所述存储器件、所述控制器件以及所述接口装置分别连接;Wherein, the neural network chip is respectively connected with the storage device, the control device and the interface device;

所述存储器件,用于存储数据;the storage device for storing data;

所述接口装置,用于实现所述芯片与外部设备之间的数据传输;the interface device for realizing data transmission between the chip and an external device;

所述控制器件,用于对所述芯片的状态进行监控。The control device is used for monitoring the state of the chip.

进一步地,所述存储器件包括:多组存储单元,每一组所述存储单元与所述芯片通过总线连接,所述存储单元为:DDR SDRAM;Further, the storage device includes: multiple groups of storage units, each group of the storage units is connected to the chip through a bus, and the storage units are: DDR SDRAM;

所述芯片包括:DDR控制器,用于对每个所述存储单元的数据传输与数据存储的控制;The chip includes: a DDR controller for controlling data transmission and data storage of each of the storage units;

所述接口装置为:标准PCIE接口。The interface device is: a standard PCIE interface.

第八方面,本发明实施例提供了一种电子装置,该电子装置包括上述第五方面所述的神经网络芯片、第六方面所述的神经网络芯片封装结构或者上述第七方面所述的板卡。In an eighth aspect, an embodiment of the present invention provides an electronic device, the electronic device includes the neural network chip described in the fifth aspect, the neural network chip packaging structure described in the sixth aspect, or the board described in the seventh aspect. Card.

在一些实施例中,所述电子设备包括数据处理装置、机器人、电脑、打印机、扫描仪、平板电脑、智能终端、手机、行车记录仪、导航仪、传感器、摄像头、服务器、云端服务器、相机、摄像机、投影仪、手表、耳机、移动存储、可穿戴设备、交通工具、家用电器、和/或医疗设备。In some embodiments, the electronic device includes a data processing device, a robot, a computer, a printer, a scanner, a tablet computer, a smart terminal, a mobile phone, a driving recorder, a navigator, a sensor, a camera, a server, a cloud server, a camera, Cameras, projectors, watches, headphones, mobile storage, wearables, vehicles, home appliances, and/or medical equipment.

在一些实施例中,所述交通工具包括飞机、轮船和/或车辆;所述家用电器包括电视、空调、微波炉、冰箱、电饭煲、加湿器、洗衣机、电灯、燃气灶、油烟机;所述医疗设备包括核磁共振仪、B超仪和/或心电图仪。In some embodiments, the vehicles include airplanes, ships and/or vehicles; the household appliances include televisions, air conditioners, microwave ovens, refrigerators, rice cookers, humidifiers, washing machines, electric lights, gas stoves, and range hoods; the medical Equipment includes MRI machines, ultrasound machines and/or electrocardiographs.

本发明的这些方面或其他方面在以下实施例的描述中会更加简明易懂。These and other aspects of the invention will be more clearly understood from the description of the following embodiments.

附图说明Description of drawings

为了更清楚地说明本申请实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。In order to illustrate the technical solutions in the embodiments of the present application more clearly, the following briefly introduces the drawings that are used in the description of the embodiments. Obviously, the drawings in the following description are some embodiments of the present application. For those of ordinary skill in the art, other drawings can also be obtained from these drawings without any creative effort.

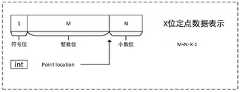

图1为本申请实施例提供一种定点数据的数据结构示意图;1 provides a schematic diagram of a data structure of fixed-point data according to an embodiment of the present application;

图2为本申请实施例提供另一种定点数据的数据结构示意图;FIG. 2 provides a schematic diagram of a data structure of another fixed-point data according to an embodiment of the present application;

图2A为本申请实施例提供另一种定点数据的数据结构示意图;FIG. 2A provides a schematic diagram of a data structure of another fixed-point data according to an embodiment of the present application;

图2B为本申请实施例提供另一种定点数据的数据结构示意图;FIG. 2B provides a schematic diagram of a data structure of another fixed-point data according to an embodiment of the present application;

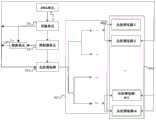

图3本申请实施例提供一种计算装置的结构示意图;3 is a schematic structural diagram of a computing device provided by an embodiment of the present application;

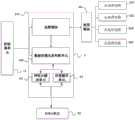

图3A是本申请一个实施例提供的计算装置的结构示意图;3A is a schematic structural diagram of a computing device provided by an embodiment of the present application;

图3B是本申请另一个实施例提供的计算装置的结构示意图;3B is a schematic structural diagram of a computing device provided by another embodiment of the present application;

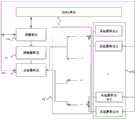

图3C是本申请另一个实施例提供的计算装置的结构示意图;3C is a schematic structural diagram of a computing device provided by another embodiment of the present application;

图3D是本申请实施例提供的主处理电路的结构示意图;3D is a schematic structural diagram of a main processing circuit provided by an embodiment of the present application;

图3E是本申请另一个实施例提供的计算装置的结构示意图;3E is a schematic structural diagram of a computing device provided by another embodiment of the present application;

图3F是本申请实施例提供的树型模块的结构示意图;3F is a schematic structural diagram of a tree module provided by an embodiment of the present application;

图3G是本申请另一个实施例提供的计算装置的结构示意图;3G is a schematic structural diagram of a computing device provided by another embodiment of the present application;

图3H是本申请另一个实施例提供的计算装置的结构示意图;3H is a schematic structural diagram of a computing device provided by another embodiment of the present application;

图4为本申请实施例提供的一种单层人工神经网络正向运算流程图;4 is a flow chart of forward operation of a single-layer artificial neural network provided by an embodiment of the present application;

图5为本申请实施例提供的一种神经网络正向运算和反向训练流程图;Fig. 5 is a kind of neural network forward operation and reverse training flow chart provided by the embodiment of the application;

图6是本申请实施例提供的一种组合处理装置的结构图;6 is a structural diagram of a combined processing device provided by an embodiment of the present application;

图6A是本申请另一个实施例提供的计算装置的结构示意图;6A is a schematic structural diagram of a computing device provided by another embodiment of the present application;

图7是本申请实施例提供的另一种组合处理装置的结构图;7 is a structural diagram of another combined processing device provided by an embodiment of the present application;

图8为本申请实施例提供的一种板卡的结构示意图;FIG. 8 is a schematic structural diagram of a board provided by an embodiment of the present application;

图9为本申请实施例提供的一种计算方法的流程示意图;9 is a schematic flowchart of a calculation method provided by an embodiment of the present application;

图10为本申请实施例提供的一种数据的小数点位置确定和调整流程示意图;10 is a schematic flowchart of the determination and adjustment of the decimal point position of a kind of data provided by the embodiment of the present application;

图11为本申请实施例提供的一种分布式系统的结构示意图;FIG. 11 is a schematic structural diagram of a distributed system provided by an embodiment of the application;

图12为本申请实施例提供的另一种分布式系统的结构示意图。FIG. 12 is a schematic structural diagram of another distributed system provided by an embodiment of the present application.

具体实施方式Detailed ways

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。The technical solutions in the embodiments of the present application will be clearly and completely described below with reference to the accompanying drawings in the embodiments of the present application. Obviously, the described embodiments are part of the embodiments of the present application, not all of the embodiments. Based on the embodiments in the present application, all other embodiments obtained by those of ordinary skill in the art without creative work fall within the protection scope of the present application.

本申请的说明书和权利要求书及所述附图中的术语“第一”、“第二”、“第三”和“第四”等是用于区别不同对象,而不是用于描述特定顺序。此外,术语“包括”和“具有”以及它们任何变形,意图在于覆盖不排他的包含。例如包含了一系列步骤或单元的过程、方法、系统、产品或设备没有限定于已列出的步骤或单元,而是可选地还包括没有列出的步骤或单元,或可选地还包括对于这些过程、方法、产品或设备固有的其它步骤或单元。The terms "first", "second", "third" and "fourth" in the description and claims of the present application and the drawings are used to distinguish different objects, rather than to describe a specific order . Furthermore, the terms "comprising" and "having" and any variations thereof are intended to cover non-exclusive inclusion. For example, a process, method, system, product or device comprising a series of steps or units is not limited to the listed steps or units, but optionally also includes unlisted steps or units, or optionally also includes For other steps or units inherent to these processes, methods, products or devices.

在本文中提及“实施例”意味着,结合实施例描述的特定特征、结构或特性可以包含在本申请的至少一个实施例中。在说明书中的各个位置出现该短语并不一定均是指相同的实施例,也不是与其它实施例互斥的独立的或备选的实施例。本领域技术人员显式地和隐式地理解的是,本文所描述的实施例可以与其它实施例相结合Reference herein to an "embodiment" means that a particular feature, structure, or characteristic described in connection with the embodiment can be included in at least one embodiment of the present application. The appearances of the phrase in various places in the specification are not necessarily all referring to the same embodiment, nor a separate or alternative embodiment that is mutually exclusive of other embodiments. It is explicitly and implicitly understood by those skilled in the art that the embodiments described herein may be combined with other embodiments

本申请实施例提供一种数据类型,该数据类型包括调整因子,该调整因子用于指示该数据类型的取值范围及精度。An embodiment of the present application provides a data type, where the data type includes an adjustment factor, and the adjustment factor is used to indicate a value range and precision of the data type.

其中,上述调整因子包括第一缩放因子和第二缩放因子(可选地),该第一缩放因子用于指示上述数据类型的精度;上述第二缩放因子用于调整上述数据类型的取值范围。Wherein, the above-mentioned adjustment factor includes a first scale factor and a second scale factor (optional), the first scale factor is used to indicate the precision of the above-mentioned data type; the above-mentioned second scale factor is used to adjust the value range of the above-mentioned data type .

可选地,上述第一缩放因子可为2-m、8-m、10-m、2、3、6、9、10、2m、8m、10m或者其他值。Optionally, the above-mentioned first scaling factor may be 2-m , 8-m , 10-m , 2, 3, 6, 9, 10, 2m , 8m , 10m or other values.

具体地,上述第一缩放因子可为小数点位置。比如以二进制表示的输入数据INA1的小数点位置向右移动m位后得到的输入数据INB1=INA1*2m,即输入数据INB1相对于输入数据INA1放大了2m倍;再比如,以十进制表示的输入数据INA2的小数点位置左移动n位后得到的输入数据INB2=INA2/10n,即输入数据INA2相对于输入数据INB2缩小了10n倍,m和n均为整数。Specifically, the above-mentioned first scaling factor may be a decimal point position. For example, the input data INB1=INA1*2m obtained after the decimal point position of the input data INA1 expressed in binary is shifted to the right by m bits, that is, the input data INB1 is enlarged by 2m times relative to the input data INA1; for another example, the decimal expressed The input data INB2=INA2/10n obtained after the decimal point position of the input data INA2 is shifted to the left by n bits, that is, the input data INA2 is reduced by 10n times relative to the input data INB2, and both m and n are integers.

可选地,上述第二缩放因子可为2、8、10、16或其他值。Optionally, the above-mentioned second scaling factor may be 2, 8, 10, 16 or other values.

举例说明,上述输入数据对应的数据类型的取值范围为8-15-816,在进行运算过程中,得到的运算结果大于输入数据对应的数据类型的取值范围对应的最大值时,将该数据类型的取值范围乘以该数据类型的第二缩放因子(即8),得到新的取值范围8-14-817;当上述运算结果小于上述输入数据对应的数据类型的取值范围对应的最小值时,将该数据类型的取值范围除以该数据类型的第二缩放因子(8),得到新的取值范围8-16-815。For example, the value range of the data type corresponding to the above input data is 8-15 -816 . During the operation process, when the obtained operation result is greater than the maximum value corresponding to the value range of the data type corresponding to the input data, the The value range of the data type is multiplied by the second scaling factor (ie 8) of the data type to obtain a new value range 8-14 -817 ; when the above operation result is less than the value of the data type corresponding to the above input data When the minimum value corresponding to the range is reached, the value range of the data type is divided by the second scaling factor (8) of the data type to obtain a new value range of 8-16 -815 .

对于任何格式的数据(比如浮点数、离散数据)都可以加上缩放因子,以调整该数据的大小和精度。For data in any format (such as floating point numbers, discrete data), scaling factors can be added to adjust the size and precision of the data.

需要说明的是,本申请说明书下文提到的小数点位置都可以是上述第一缩放因子,在此不再叙述。It should be noted that, the position of the decimal point mentioned below in the specification of this application may all be the above-mentioned first scaling factor, which will not be described here.

下面介绍定点数据的结构,参加图1,图1为本申请实施例提供一种定点数据的数据结构示意图。如图1所示有符号的定点数据,该定点数据占X比特位,该定点数据又可称为X位定点数据。其中,该X位定点数据包括占1比特的符号位、M比特的整数位和N比特的小数位,X-1=M+N。对于无符号的定点数据,只包括M比特的整数位和N比特的小数位,即X=M+N。The structure of fixed-point data is described below, referring to FIG. 1 , which provides a schematic diagram of a data structure of fixed-point data according to an embodiment of the present application. As shown in FIG. 1, the signed fixed-point data occupies X bits, and the fixed-point data may also be called X-bit fixed-point data. Wherein, the X-bit fixed-point data includes a sign bit occupying 1 bit, an integer bit of M bits, and a decimal bit of N bits, X−1=M+N. For unsigned fixed-point data, only M bits of integer bits and N bits of fractional bits are included, that is, X=M+N.

相比于32位浮点数据表示形式,本发明采用的短位定点数据表示形式除了占用比特位数更少外,对于网路模型中同一层、同一类型的数据,如第一个卷积层的所有卷积核、输入神经元或者偏置数据,还另外设置了一个标志位记录定点数据的小数点位置,该标志位即为Point Location。这样可以根据输入数据的分布来调整上述标志位的大小,从而达到调整定点数据的精度与定点数据可表示范围。Compared with the 32-bit floating point data representation, the short-bit fixed-point data representation adopted by the present invention not only occupies fewer bits, but also for the same layer and the same type of data in the network model, such as the first convolutional layer. All the convolution kernels, input neurons or bias data of , also set a flag bit to record the decimal point position of the fixed-point data, the flag bit is Point Location. In this way, the size of the flag bit can be adjusted according to the distribution of the input data, so as to adjust the precision of the fixed-point data and the representable range of the fixed-point data.

举例说明,将浮点数68.6875转换为小数点位置为5的有符号16位定点数据。其中,对于小数点位置为5的有符号16位定点数据,其整数部分占10比特,小数部分占5比特,符号位占1比特。上述转换单元将上述浮点数68.6875转换成有符号16位定点数据为0000010010010110,如图2所示。As an example, converts the floating-point number 68.6875 to signed 16-bit fixed-point data with a decimal point of 5. Among them, for the signed 16-bit fixed-point data whose decimal point position is 5, the integer part occupies 10 bits, the fractional part occupies 5 bits, and the sign bit occupies 1 bit. The above conversion unit converts the above floating point number 68.6875 into signed 16-bit fixed point data as 0000010010010110, as shown in FIG. 2 .

在一种可能的实施例中,上述定点数据还可用图2A所示方式进行表示。如图2A所示,该定点数据所占的比特位数为bitnum,小数点位置为s,该定点数据的精度为2s。第一位为符号位,用于指示该定数据是正数还是负数。比如当符号位为0时,表示该定点数据为正数;当符号位为1时,表示该定点数据为负数。该定点数据表示的范围为[neg,pos],其中,pos=(2bitnum-1-1)*2s,neg=-(2bitnum-1-1)*2s。In a possible embodiment, the above-mentioned fixed-point data can also be represented in the manner shown in FIG. 2A . As shown in FIG. 2A , the number of bits occupied by the fixed-point data is bitnum, the position of the decimal point is s, and the precision of the fixed-point data is 2s . The first bit is the sign bit, which is used to indicate whether the fixed data is positive or negative. For example, when the sign bit is 0, it means that the fixed-point data is a positive number; when the sign bit is 1, it means that the fixed-point data is a negative number. The range represented by the fixed-point data is [neg, pos], where pos=(2bitnum-1 -1)*2s and neg=-(2bitnum-1 -1)*2s .

其中,上述bitnum可以去任意正整数。上述s可为任意不小于s_min的整数Among them, the above bitnum can be any positive integer. The above s can be any integer not less than s_min

可选地,上述bitnum可为8、16、24、32、64或者其他值。进一步地,上述s_min为-64。Optionally, the above bitnum may be 8, 16, 24, 32, 64 or other values. Further, the above-mentioned s_min is -64.

可选地,上述bitnum为8,16,24,32或者其他值。s可以取任意不小于s_min的整数,进一步地,s_min取-64。Optionally, the above bitnum is 8, 16, 24, 32 or other values. s can take any integer not less than s_min, and further, s_min takes -64.

在一种实施例中,对于数值较大的数据可采用多种定点表示方法,具体参见图2B:如图2B所示,对上述数值较大的数据采用3种定点数据组合表示,即该数据由定点数据1、定点数据2和定点数据3组成。其中,定点数据1的位宽为bitnum1,小数点位置为s1,定点数据2的位宽为bitnum2,小数点位置为s2;定点数据3的位宽为bitnum3,小数点位置为s3,且bitnum2-2=s1-1,bitnum3-2=s2-1。采用3种定点数据表示的范围为[neg,pos],其中,pos=(2bitnum-1-1)*2s,neg=-(2bitnum-1-1)*2s。In one embodiment, a variety of fixed-point representation methods can be used for data with larger numerical values, as shown in FIG. 2B : as shown in FIG. 2B , three fixed-point data combinations are used to represent the above-mentioned data with larger numerical values, that is, the data It consists of fixed-

首先介绍本申请使用的计算装置。参阅图3,提供了一种计算装置,该计算装置包括:控制器单元11、运算单元12和转换单元13,其中,控制器单元11与运算单元12连接,转换单元13与上述控制器单元11和运算单元12均相连接;First, the computing device used in this application is introduced. Referring to FIG. 3, a computing device is provided, the computing device includes: a

在一个可能的实施例中,控制器单元11,用于获取第一输入数据以及计算指令。In a possible embodiment, the

在一个实施例里,第一输入数据是机器学习数据。进一步地,机器学习数据包括输入神经元数据,权值数据。输出神经元数据是最终输出结果或者中间数据。In one embodiment, the first input data is machine learning data. Further, the machine learning data includes input neuron data and weight data. The output neuron data is the final output result or intermediate data.

在一种可选方案中,获取第一输入数据以及计算指令方式具体可以通过数据输入输出单元得到,该数据输入输出单元具体可以为一个或多个数据I/O接口或I/O引脚。In an optional solution, the method of acquiring the first input data and the calculation instruction may be obtained through a data input and output unit, and the data input and output unit may be one or more data I/O interfaces or I/O pins.

上述计算指令包括但不限于:正向运算指令或反向训练指令,或其他神经网络运算指令等等,例如卷积运算指令,本申请具体实施方式并不限制上述计算指令的具体表现形式。The above calculation instructions include but are not limited to: forward operation instructions or reverse training instructions, or other neural network operation instructions, etc., such as convolution operation instructions. The specific embodiment of the present application does not limit the specific expression form of the above calculation instructions.

上述控制器单元11,还用于解析所述计算指令得到数据转换指令和/或一个或多个运算指令,其中,所述数据转换指令包括操作域和操作码,该操作码用于指示所述数据类型转换指令的功能,所述数据类型转换指令的操作域包括小数点位置、用于指示第一输入数据的数据类型的标志位和数据类型的转换方式标识。The above-mentioned

当上述数据转换指令的操作域为存储空间的地址时,上述控制器单元11根据该地址对应的存储空间中获取上述小数点位置、用于指示第一输入数据的数据类型的标志位和数据类型的转换方式标识。When the operation domain of the above-mentioned data conversion instruction is the address of the storage space, the above-mentioned

上述控制器单元11将所述数据转换指令的操作码和操作域及所述第一输入数据传输至所述转换单元13;将所述多个运算指令传输至所述运算单元12;The above-mentioned

上述转换单元13,用于根据所述数据转换指令的操作码和操作域将所述第一输入数据转换为第二输入数据,该第二输入数据为定点数据;并将所述第二输入数据传输至运算单元12;The

上述运算单元12,用于根据所述多个运算指令对所述第二输入数据进行运算,以得到所述计算指令的计算结果。The above-mentioned

在一中可能的实施例中,本申请提供的技术方案将运算单元12设置成一主多从结构,对于正向运算的计算指令,其可以将依据正向运算的计算指令将数据进行拆分,这样通过多个从处理电路102即能够对计算量较大的部分进行并行运算,从而提高运算速度,节省运算时间,进而降低功耗。如图3A所示,上述运算单元12包括一个主处理电路101和多个从处理电路102;In one possible embodiment, the technical solution provided by the present application sets the

上述主处理电路101,用于对上述第二输入数据进行执行前序处理以及与上述多个从处理电路102之间传输数据和上述多个运算指令;The above-mentioned

上述多个从处理电路102,用于依据从上述主处理电路101传输第二输入数据以及上述多个运算指令并执行中间运算得到多个中间结果,并将多个中间结果传输给上述主处理电路101;The plurality of

上述主处理电路101,用于对上述多个中间结果执行后续处理得到上述计算指令的计算结果。The above-mentioned

在一个实施例里,机器学习运算包括深度学习运算(即人工神经网络运算),机器学习数据(即第一输入数据)包括输入神经元和权值(即神经网络模型数据)。输出神经元为上述计算指令的计算结果或中间结果。下面以深度学习运算为例,但应理解的是,不局限在深度学习运算。In one embodiment, the machine learning operations include deep learning operations (ie, artificial neural network operations), and the machine learning data (ie, first input data) include input neurons and weights (ie, neural network model data). The output neuron is the calculation result or the intermediate result of the above calculation instruction. The following uses deep learning operations as an example, but it should be understood that it is not limited to deep learning operations.

可选的,上述计算装置还可以包括:该存储单元10和直接内存访问(directmemory access,DMA)单元50,存储单元10可以包括:寄存器、缓存中的一个或任意组合,具体的,所述缓存,用于存储所述计算指令;所述寄存器201,用于存储所述第一输入数据和标量。其中第一输入数据包括输入神经元、权值和输出神经元。Optionally, the above-mentioned computing device may further include: the

所述缓存202为高速暂存缓存。The

DMA单元50用于从存储单元10读取或存储数据。The

在一种可能的实施例中,上述寄存器201中存储有上述运算指令、第一输入数据、小数点位置、用于指示第一输入数据的数据类型的标志位和数据类型的转换方式标识;上述控制器单元11直接从上述寄存器201中获取上述运算指令、第一输入数据、小数点位置、用于指示第一输入数据的数据类型的标志位和数据类型的转换方式标识;将第一输入数据、小数点位置、用于指示第一输入数据的数据类型的标志位和数据类型的转换方式标识出传输至上述转换单元13;将上述运算指令传输至上述运算单元12;In a possible embodiment, the above-mentioned

上述转换单元13根据上述小数点位置、用于指示第一输入数据的数据类型的标志位和数据类型的转换方式标识将上述第一输入数据转换为第二输入数据;然后将该第二输入数据传输至上述运算单元12;The above-mentioned

上述运算单元12根据上述运算指令对上述第二输入数据进行运算,以得到运算结果。The above-mentioned

可选的,该控制器单元11包括:指令缓存单元110、指令处理单元111和存储队列单元113;Optionally, the

所述指令缓存单元110,用于存储所述人工神经网络运算关联的计算指令;The

所述指令处理单元111,用于对所述计算指令解析得到所述数据转换指令和所述多个运算指令,并解析所述数据转换指令以得到所述数据转换指令的操作码和操作域;The

所述存储队列单元113,用于存储指令队列,该指令队列包括:按该队列的前后顺序待执行的多个运算指令或计算指令。The

举例说明,在一个可选的技术方案中,主处理电路101也可以包括一个控制单元,该控制单元可以包括主指令处理单元,具体用于将指令译码成微指令。当然在另一种可选方案中,从处理电路102也可以包括另一个控制单元,该另一个控制单元包括从指令处理单元,具体用于接收并处理微指令。上述微指令可以为指令的下一级指令,该微指令可以通过对指令的拆分或解码后获得,能被进一步解码为各部件、各单元或各处理电路的控制信号。For example, in an optional technical solution, the

在一种可选方案中,该计算指令的结构可以如下表1所示。In an optional solution, the structure of the calculation instruction may be as shown in Table 1 below.

表1Table 1

上表中的省略号表示可以包括多个寄存器或立即数。The ellipsis in the above table indicates that multiple registers or immediate values can be included.

在另一种可选方案中,该计算指令可以包括:一个或多个操作域以及一个操作码。该计算指令可以包括神经网络运算指令。以神经网络运算指令为例,如表1所示,其中,寄存器号0、寄存器号1、寄存器号2、寄存器号3、寄存器号4可以为操作域。其中,每个寄存器号0、寄存器号1、寄存器号2、寄存器号3、寄存器号4可以是一个或者多个寄存器的号码。In another optional solution, the computing instruction may include: one or more operation domains and an operation code. The calculation instructions may include neural network operation instructions. Taking the neural network operation instruction as an example, as shown in Table 1, register number 0,

表2Table 2

上述寄存器可以为片外存储器,当然在实际应用中,也可以为片内存储器,用于存储数据,该数据具体可以为n维数据,n为大于等于1的整数,例如,n=1时,为1维数据,即向量,如n=2时,为2维数据,即矩阵,如n=3或3以上时,为多维张量。The above register can be an off-chip memory. Of course, in practical applications, it can also be an on-chip memory for storing data. Specifically, the data can be n-dimensional data, where n is an integer greater than or equal to 1. For example, when n=1, It is 1-dimensional data, that is, a vector. For example, when n=2, it is 2-dimensional data, that is, a matrix. For example, when n=3 or more, it is a multi-dimensional tensor.

可选的,该控制器单元11还可以包括:Optionally, the

依赖关系处理单元112,用于在具有多个运算指令时,确定第一运算指令与所述第一运算指令之前的第零运算指令是否存在关联关系,如所述第一运算指令与所述第零运算指令存在关联关系,则将所述第一运算指令缓存在所述指令缓存单元110内,在所述第零运算指令执行完毕后,从所述指令缓存单元110提取所述第一运算指令传输至所述运算单元;The dependency

所述确定该第一运算指令与第一运算指令之前的第零运算指令是否存在关联关系包括:依据所述第一运算指令提取所述第一运算指令中所需数据(例如矩阵)的第一存储地址区间,依据所述第零运算指令提取所述第零运算指令中所需矩阵的第零存储地址区间,如所述第一存储地址区间与所述第零存储地址区间具有重叠的区域,则确定所述第一运算指令与所述第零运算指令具有关联关系,如所述第一存储地址区间与所述第零存储地址区间不具有重叠的区域,则确定所述第一运算指令与所述第零运算指令不具有关联关系。The determining whether there is an association relationship between the first operation instruction and the zeroth operation instruction before the first operation instruction includes: extracting the first data (for example, a matrix) required in the first operation instruction according to the first operation instruction. storage address interval, extracting the zeroth storage address interval of the matrix required in the zeroth operation instruction according to the zeroth operation instruction, if the first storage address interval and the zeroth storage address interval have an overlapping area, Then it is determined that the first operation instruction and the zeroth operation instruction have an associated relationship. If the first storage address interval and the zeroth storage address interval do not have overlapping areas, then it is determined that the first operation instruction and the zeroth storage address interval do not overlap. The zeroth operation instruction has no association relationship.

在另一种可选实施例中,如图3B所示,上述运算单元12包括一个主处理电路101、多个从处理电路102和多个分支处理电路103。In another optional embodiment, as shown in FIG. 3B , the above-mentioned

上述主处理电路101,具体用于确定所述输入神经元为广播数据,权值为分发数据,将一个分发数据分配成多个数据块,将所述多个数据块中的至少一个数据块、广播数据以及多个运算指令中的至少一个运算指令发送给所述分支处理电路103;The above-mentioned

所述分支处理电路103,用于转发所述主处理电路101与所述多个从处理电路102之间的数据块、广播数据以及运算指令;The

所述多个从处理电路102,用于依据该运算指令对接收到的数据块以及广播数据执行运算得到中间结果,并将中间结果传输给所述分支处理电路103;The plurality of

上述主处理电路101,还用于将上述分支处理电路103发送的中间结果进行后续处理得到上述运算指令的结果,将上述计算指令的结果发送至上述控制器单元11。The

在另一种可选实施例中,运算单元12如图3C所示,可以包括一个主处理电路101和多个从处理电路102。如图3C所示,多个从处理电路102呈阵列分布;每个从处理电路102与相邻的其他从处理电路102连接,主处理电路101连接所述多个从处理电路102中的K个从处理电路102,所述K个从处理电路102为:第1行的n个从处理电路102、第m行的n个从处理电路102以及第1列的m个从处理电路102,需要说明的是,如图3C所示的K个从处理电路102仅包括第1行的n个从处理电路102、第m行的n个从处理电路102以及第1列的m个从处理电路102,即该K个从处理电路102为多个从处理电路102中直接与主处理电路101连接的从处理电路102。In another optional embodiment, as shown in FIG. 3C , the

K个从处理电路102,用于在上述主处理电路101以及多个从处理电路102之间的数据以及指令的转发;K

所述主处理电路101,还用于确定上述输入神经元为广播数据,权值为分发数据,将一个分发数据分配成多个数据块,将所述多个数据块中的至少一个数据块以及多个运算指令中的至少一个运算指令发送给所述K个从处理电路102;The

所述K个从处理电路102,用于转换所述主处理电路101与所述多个从处理电路102之间的数据;The K

所述多个从处理电路102,用于依据所述运算指令对接收到的数据块执行运算得到中间结果,并将运算结果传输给所述K个从处理电路102;The multiple

所述主处理电路101,用于将所述K个从处理电路102发送的中间结果进行处理得到该计算指令的结果,将该计算指令的结果发送给所述控制器单元11。The

可选的,如图3D所示,上述图3A-图3C中的主处理电路101还可以包括:激活处理电路1011、加法处理电路1012中的一种或任意组合;Optionally, as shown in FIG. 3D, the

激活处理电路1011,用于执行主处理电路101内数据的激活运算;The activation processing circuit 1011 is used to execute the activation operation of the data in the

加法处理电路1012,用于执行加法运算或累加运算。The addition processing circuit 1012 is used for performing addition operation or accumulation operation.

上述从处理电路102包括:乘法处理电路,用于对接收到的数据块执行乘积运算得到乘积结果;转发处理电路(可选的),用于将接收到的数据块或乘积结果转发。累加处理电路,用于对该乘积结果执行累加运算得到该中间结果。The above-mentioned

在一种可行的实施例中,上述第一输入数据为数据类型与参与运算的运算指令所指示的运算类型不一致的数据,第二输入数据为数据类型与参与运算的运算指令所指示的运算类型一致的数据,上述转换单元13获取上述数据转换指令的操作码和操作域,该操作码用于指示该数据转换指令的功能,操作域包括小数点位置和数据类型的转换方式标识。上述转换单元13根据上述小数点位置和数据类型的转换方式标识将上述第一输入数据转换为第二输入数据。In a feasible embodiment, the above-mentioned first input data is data whose data type is inconsistent with the operation type indicated by the operation instruction participating in the operation, and the second input data is the data type and the operation type indicated by the operation instruction participating in the operation. The

具体地,上述数据类型的转换方式标识与上述数据类型的转换方式一一对应。参见下表3,表3为一种可行的数据类型的转换方式标识与数据类型的转换方式的对应关系表。Specifically, the conversion mode identifiers of the above data types are in one-to-one correspondence with the conversion modes of the above data types. See Table 3 below. Table 3 is a corresponding relationship table between a feasible data type conversion mode identifier and a data type conversion mode.

表3table 3

如表3所示,当上述数据类型的转换方式标识为00时,上述数据类型的转换方式为定点数据转换为定点数据;当上述数据类型的转换方式标识为01时,上述数据类型的转换方式为浮点数据转换为浮点数据;当上述数据类型的转换方式标识为10时,上述数据类型的转换方式为定点数据转换为浮点数据;当上述数据类型的转换方式标识为11时,上述数据类型的转换方式为浮点数据转换为定点数据。As shown in Table 3, when the conversion method of the above-mentioned data type is marked as 00, the conversion method of the above-mentioned data type is that fixed-point data is converted into fixed-point data; when the conversion method of the above-mentioned data type is marked as 01, the conversion method of the above-mentioned data type is Convert floating point data to floating point data; when the conversion method of the above data type is marked as 10, the conversion method of the above data type is to convert fixed-point data to floating point data; when the conversion method of the above data type is marked as 11, the above The conversion method of the data type is to convert floating-point data to fixed-point data.

可选地,上述数据类型的转换方式标识与数据类型的转换方式的对应关系还可如下表4所示。Optionally, the corresponding relationship between the data type conversion mode identifier and the data type conversion mode may also be as shown in Table 4 below.

表4Table 4

如表4所示,当上述数据类型的转换方式标识为0000时,上述数据类型的转换方式为64位定点数据转换为64位浮点数据;当上述数据类型的转换方式标识为0001时,上述数据类型的转换方式为32位定点数据转换为64位浮点数据;当上述数据类型的转换方式标识为0010时,上述数据类型的转换方式为16位定点数据转换为64位浮点数据;当上述数据类型的转换方式标识为0011时,上述数据类型的转换方式为32位定点数据转换为32位浮点数据;当上述数据类型的转换方式标识为0100时,上述数据类型的转换方式为16位定点数据转换为32位浮点数据;当上述数据类型的转换方式标识为0101时,上述数据类型的转换方式为16位定点数据转换为16位浮点数据;当上述数据类型的转换方式标识为0110时,上述数据类型的转换方式为64位浮点数据转换为64位定点数据;当上述数据类型的转换方式标识为0111时,上述数据类型的转换方式为32位浮点数据转换为64位定点数据;当上述数据类型的转换方式标识为1000时,上述数据类型的转换方式为16位浮点数据转换为64位定点数据;当上述数据类型的转换方式标识为1001时,上述数据类型的转换方式为32位浮点数据转换为32位定点数据;当上述数据类型的转换方式标识为1010时,上述数据类型的转换方式为16位浮点数据转换为32位定点数据;当上述数据类型的转换方式标识为1011时,上述数据类型的转换方式为16位浮点数据转换为16位定点数据。As shown in Table 4, when the conversion method of the above data type is marked as 0000, the conversion method of the above data type is that 64-bit fixed-point data is converted into 64-bit floating-point data; when the conversion method of the above data type is marked as 0001, the above The conversion method of the data type is to convert 32-bit fixed-point data to 64-bit floating-point data; when the conversion method of the above data type is identified as 0010, the conversion method of the above data type is to convert 16-bit fixed-point data to 64-bit floating-point data; when When the conversion method of the above data type is marked as 0011, the conversion method of the above data type is that 32-bit fixed-point data is converted into 32-bit floating-point data; when the conversion method of the above data type is marked as 0100, the conversion method of the above data type is 16 The fixed-point data is converted into 32-bit floating-point data; when the conversion method of the above data type is marked as 0101, the conversion method of the above data type is 16-bit fixed-point data is converted into 16-bit floating-point data; when the conversion method of the above data type is marked When it is 0110, the conversion method of the above data type is to convert 64-bit floating point data to 64-bit fixed-point data; when the conversion method of the above data type is marked as 0111, the conversion method of the above data type is 32-bit floating point data to 64 When the conversion method of the above data type is marked as 1000, the conversion method of the above data type is that 16-bit floating point data is converted into 64-bit fixed-point data; when the conversion method of the above data type is marked as 1001, the above data type The conversion method of 32-bit floating point data is converted to 32-bit fixed-point data; when the conversion method of the above data type is marked as 1010, the conversion method of the above data type is 16-bit floating-point data to 32-bit fixed-point data; when the above data type is converted to 32-bit fixed-point data; When the type conversion mode identifier is 1011, the conversion mode of the above data type is 16-bit floating point data to 16-bit fixed-point data.

在一种可行的实施例中,上述控制器单元11从上述存储单元10中获取计算指令,解析该计算指令以得到一个或者多个运算指令,其中该运算指令可为可变格式运算指令或者定点格式运算指令。In a feasible embodiment, the

其中,上述可变格式运算指令包括操作码和操作域,该操作码用于指示该可变格式运算指令的功能,上述操作域包括第一输入数据的首地址、第一输入数据的长度(可选地)、输出数据的首地址、小数点位置、第一输入数据的数据类型标志位(可选地)和操作类型标识。Wherein, the above-mentioned variable format operation instruction includes an operation code and an operation field, the operation code is used to indicate the function of the variable format operation instruction, and the above-mentioned operation field includes the first address of the first input data, the length of the first input data (optional Optionally), the first address of the output data, the decimal point position, the data type flag bit (optionally) of the first input data, and the operation type identifier.

当上述运算指令为可变格式运算指令时,上述控制器单元11解析上述可变格式运算指令,以得到上述第一输入数据的首地址、第一输入数据的长度、输出数据的首地址、小数点位置、第一输入数据的数据类型标志位和操作类型标识,然后根据第一输入数据的首地址和上述第一输入数据的长度从上述存储单元10中获取第一输入数据,然后将第一输入数据、小数点位置、第一输入数据的数据类型标志位和操作类型标识传输至上述转换单元13,然后将上述输出数据的首地址上述运算单元12;When the operation instruction is a variable format operation instruction, the

上述转换单元13根据上述数据类型标志位、上述小数点位置和上述操作类型标识指示的操作类型将上述第一输入数据转换为第二输入数据;然后将该第二输入数据传输至上述运算单元12。The

上述运算单元12的主处理电路101和从处理电路102对上述第二输入数据进行运算,以得到上述计算指令的结果;将该计算指令的结果存储至上述存储单元10中上述输出数据的首地址对应的位置。The

其中,上述操作类型标识用于指示上述运算单元12进行运算时参与运算的数据的类型。该类型包括定点数据,浮点数据、整型数据和离散数据等。The above-mentioned operation type identifier is used to indicate the type of data involved in the operation when the

在一种可能的实施例中,上述存储单元10中存储有上述第一输入数据的首地址、第一输入数据的长度、输出数据的首地址、小数点位置、第一输入数据的数据类型标志位和操作类型标识,上述控制器单元11直接从上述存储单元10中获取上述上述第一输入数据的首地址、第一输入数据的长度、输出数据的首地址、小数点位置、第一输入数据的数据类型标志位和操作类型标识,然后按照上述过程进行后续操作。In a possible embodiment, the

举例说明,上述操作类型标识为0或1。当该标志位为1时,上述运算单元12的主处理电路101和从处理电路102进行浮点运算,即参与运算的数据类型为浮点数据;当操作类型标识为0时,上述运算单元12的主处理电路101和从处理电路102进行定点运算,即参与运算的数据类型为定点数据。For example, the above operation type identifier is 0 or 1. When the flag bit is 1, the

上述运算单元12可根据上述数据标志位和操作类型标识确定输入数据的类型和进行运算的类型。The above-mentioned

具体地,参见表5,表5为数据类型标志位与操作类型标识的映射关系表。Specifically, see Table 5, which is a mapping relationship table between data type flag bits and operation type identifiers.

表5table 5

如表5所示,当上述操作类型标识为0且上述数据类型标志位为0时,上述第一输入数据为定点数据,上述运算单元12的主处理电路101和从处理电路102进行定点运算,不进行数据转换;当上述操作类型标识为0且上述数据类型标志位为1时,上述第一输入数据为浮点数据,上述运算单元12的主处理电路101和从处理电路102进行浮点运算,不进行数据转换;当上述操作类型标识为1且上述数据类型标志位为0时,上述第一输入数据为定点数据,上述转换单元13先根据上述小数点位置将上述第一输入数据转换为第二输入数据,第二输入数据为浮点数据,上述运算单元12的主处理电路101和从处理电路102对第二输入数据进行运算;当上述操作类型标识为1且上述数据类型标志位为1时,上述第一输入数据为浮点数据,上述转换单元13先根据上述小数点位置将上述第一输入数据转换为第二输入数据,第二输入数据为定点数据,上述运算单元12的主处理电路101和从处理电路102对该第二输入数据进行运算。As shown in Table 5, when the above-mentioned operation type flag is 0 and the above-mentioned data type flag bit is 0, the above-mentioned first input data is fixed-point data, and the

其中,上述定点数据包括64位定点数据、32位定点数据、16位定点数据。上述浮点数据64位浮点数据、32位浮点数据和16位浮点数据。上述标志位与操作类型标识的映射关系具体还可参见下表6。The above-mentioned fixed-point data includes 64-bit fixed-point data, 32-bit fixed-point data, and 16-bit fixed-point data. The above floating point data are 64-bit floating-point data, 32-bit floating-point data, and 16-bit floating-point data. For details on the mapping relationship between the flag bits and the operation type identifier, please refer to Table 6 below.

表6Table 6

如表6所示,当上述操作类型标识为0000且上述数据类型标志位为0时,上述第一输入数据为64为定点数据,上述运算单元12的主处理电路101和从处理电路102进行64位定点运算,不进行数据类型转换;当上述操作类型标识为0000且上述数据类型标志位为1时,上述第一输入数据为64为浮点数据,上述运算单元12的主处理电路101和从处理电路102进行64位浮点运算,不进行数据类型转换;当上述操作类型标识为0001且上述数据类型标志位为0时,上述第一输入数据为32为定点数据,上述运算单元12的主处理电路101和从处理电路102进行32位定点运算,不进行数据类型转换;当上述操作类型标识为0001且上述数据类型标志位为1时,上述第一输入数据为32为浮点数据,上述运算单元12的主处理电路101和从处理电路102进行32位浮点运算,不进行数据类型转换;当上述操作类型标识为0010且上述数据类型标志位为0时,上述第一输入数据为16为定点数据,上述运算单元12的主处理电路101和从处理电路102进行16位定点运算,不进行数据类型转换;当上述操作类型标识为0010且上述数据类型标志位为1时,上述第一输入数据为16为浮点数据,上述运算单元12的主处理电路101和从处理电路102进行16位浮点运算,不进行数据类型转换。As shown in Table 6, when the above-mentioned operation type identifier is 0000 and the above-mentioned data type flag bit is 0, the above-mentioned first input data is 64 fixed-point data, and the

当上述操作类型标识为0011且上述数据类型标志位为0时,上述第一输入数据为64为定点数据,上述转换单元13先根据上述小数点位置将上述第一输入数据转换为第二输入数据,第二输入数据为64为浮点数据,然后上述运算单元12的主处理电路101和从处理电路102对该第二输入数据进行64位浮点运算;当上述操作类型标识为0011且上述数据类型标志位为1时,上述第一输入数据为64为浮点数据,上述转换单元13先根据上述小数点位置将上述第一输入数据转换为第二输入数据,第二输入数据为64为定点数据,然后上述运算单元12的主处理电路101和从处理电路102对该第二输入数据进行64位定点运算。When the above-mentioned operation type identifier is 0011 and the above-mentioned data type flag bit is 0, the above-mentioned first input data is 64 fixed-point data, and the above-mentioned

当上述操作类型标识为0100且上述数据类型标志位为0时,上述第一输入数据为32为定点数据,上述转换单元13根据上述小数点位置将上述第一输入数据转换为第二输入数据,第二输入数据为64为浮点数据,然后上述运算单元12的主处理电路101和从处理电路102对该第二输入数据进行64位浮点运算;当上述操作类型标识为0100且上述数据类型标志位为1时,上述第一输入数据为32为浮点数据,上述转换单元13先根据上述小数点位置将上述第一输入数据转换为第二输入数据,第二输入数据为64为定点数据,然后上述运算单元12的主处理电路101和从处理电路102对该第二输入数据进行64位定点运算。When the above-mentioned operation type identifier is 0100 and the above-mentioned data type flag bit is 0, the above-mentioned first input data is 32 is fixed-point data, and the above-mentioned

当上述操作类型标识为0101且上述数据类型标志位为0时,上述第一输入数据为16为定点数据,上述转换单元13先根据上述小数点位置将上述第一输入数据转换为第二输入数据,第二输入数据为64为浮点数据,然后上述运算单元12的主处理电路101和从处理电路102对该第二输入数据进行64位浮点运算;当上述操作类型标识为0101且上述数据类型标志位为1时,上述第一输入数据为16为浮点数据,上述转换单元13先根据上述小数点位置将上述第一输入数据转换为第二输入数据,第二输入数据为64为定点数据,然后上述运算单元12的主处理电路101和从处理电路102对该第二输入数据进行64位定点运算。When the above-mentioned operation type identifier is 0101 and the above-mentioned data type flag bit is 0, the above-mentioned first input data is 16 is fixed-point data, and the above-mentioned

当上述操作类型标识为0110且上述数据类型标志位为0时,上述第一输入数据为32为定点数据,上述转换单元13先根据上述小数点位置将上述第一输入数据转换为第二输入数据,第二输入数据为32为浮点数据,然后上述运算单元12的主处理电路101和从处理电路102对该第二输入数据进行32位浮点运算;当上述操作类型标识为0110且上述数据类型标志位为1时,上述第一输入数据为32为浮点数据,上述转换单元13先根据上述小数点位置将上述第一输入数据转换为第二输入数据,第二输入数据为32为定点数据,然后上述运算单元12的主处理电路101和从处理电路102对该第二输入数据进行32位定点运算。When the above-mentioned operation type identifier is 0110 and the above-mentioned data type flag bit is 0, the above-mentioned first input data is 32 is fixed-point data, and the above-mentioned

当上述操作类型标识为0111且上述数据类型标志位为0时,上述第一输入数据为16为定点数据,上述转换单元13先根据上述小数点位置将上述第一输入数据转换为第二输入数据,第二输入数据为32为浮点数据,然后上述运算单元12的主处理电路101和从处理电路102对该第二输入数据进行32位浮点运算;当上述操作类型标识为0111且上述数据类型标志位为1时,上述第一输入数据为16为浮点数据,上述转换单元13先根据上述小数点位置将上述第一输入数据转换为第二输入数据,第二输入数据为32为定点数据,然后上述运算单元12的主处理电路101和从处理电路102对该第二输入数据进行32位定点运算。When the above-mentioned operation type identifier is 0111 and the above-mentioned data type flag bit is 0, the above-mentioned first input data is 16 is fixed-point data, and the above-mentioned

当上述操作类型标识为1000且上述数据类型标志位为0时,上述第一输入数据为16为定点数据,上述转换单元13先根据上述小数点位置将上述第一输入数据转换为第二输入数据,第二输入数据为16为浮点数据,然后上述运算单元12的主处理电路101和从处理电路102对该第二输入数据进行16位浮点运算;当上述操作类型标识为1000且上述数据类型标志位为1时,上述第一输入数据为16为浮点数据,上述转换单元13先根据上述小数点位置将上述第一输入数据转换为第二输入数据,第二输入数据为16为定点数据,然后上述运算单元12的主处理电路101和从处理电路102对该第二输入数据进行16位定点运算。When the above-mentioned operation type identifier is 1000 and the above-mentioned data type flag bit is 0, the above-mentioned first input data is 16 is fixed-point data, and the above-mentioned

当上述操作类型标识为1001且上述数据类型标志位为0时,上述第一输入数据为64为定点数据,上述转换单元13先根据上述小数点位置将上述第一输入数据转换为第二输入数据,第二输入数据为32为浮点数据,然后上述运算单元12的主处理电路101和从处理电路102对该第二输入数据进行32位浮点运算;当上述操作类型标识为1001且上述数据类型标志位为1时,上述第一输入数据为64为浮点数据,上述转换单元13先根据上述小数点位置将上述第一输入数据转换为第二输入数据,第二输入数据为32为定点数据,然后上述运算单元12的主处理电路101和从处理电路102对该第二输入数据进行32位定点运算。When the above-mentioned operation type identifier is 1001 and the above-mentioned data type flag bit is 0, the above-mentioned first input data is 64 is fixed-point data, and the above-mentioned

当上述操作类型标识为1010且上述数据类型标志位为0时,上述第一输入数据为64为定点数据,上述转换单元13先根据上述小数点位置将上述第一输入数据转换为第二输入数据,第二输入数据为16为浮点数据,然后上述运算单元12的主处理电路101和从处理电路102对该第二输入数据进行16位浮点运算;当上述操作类型标识为1010且上述数据类型标志位为1时,上述第一输入数据为64为浮点数据,上述转换单元13先根据上述小数点位置将上述第一输入数据转换为第二输入数据,第二输入数据为16为定点数据,然后上述运算单元12的主处理电路101和从处理电路102对该第二输入数据进行16位定点运算。When the above-mentioned operation type identifier is 1010 and the above-mentioned data type flag bit is 0, the above-mentioned first input data is 64 is fixed-point data, and the above-mentioned

当上述操作类型标识为1011且上述数据类型标志位为0时,上述第一输入数据为32为定点数据,上述转换单元13先根据上述小数点位置将上述第一输入数据转换为第二输入数据,第二输入数据为16为浮点数据,然后上述运算单元12的主处理电路101和从处理电路102对该第二输入数据进行16位浮点运算;当上述操作类型标识为1011且上述数据类型标志位为1时,上述第一输入数据为32为浮点数据,上述转换单元13先根据上述小数点位置将上述第一输入数据转换为第二输入数据,第二输入数据为16为定点数据,然后上述运算单元12的主处理电路101和从处理电路102对该第二输入数据进行16位定点运算。When the above-mentioned operation type identifier is 1011 and the above-mentioned data type flag bit is 0, the above-mentioned first input data is 32 is fixed-point data, and the above-mentioned

在一种可行的实施例中,上述运算指令为定点格式运算指令,该定点格式运算指令包括操作域和操作码,该操作码用于指示该定点格式运算指令的功能,定点格式运算指令的操作码包括第一输入数据的首地址,第一输入数据的长度(可选地)、输出数据的首地址和小数点位置。In a feasible embodiment, the above-mentioned operation instruction is a fixed-point format operation instruction, and the fixed-point format operation instruction includes an operation field and an operation code. The operation code is used to indicate the function of the fixed-point format operation instruction, and the operation of the fixed-point format operation instruction. The code includes the first address of the first input data, the length of the first input data (optionally), the first address of the output data and the decimal point position.

上述控制器单元11获取上述定点格式运算指令后,解析该定点格式运算指令,以得到上述第一输入数据的首地址、第一输入数据的长度、输出数据的首地址和小数点位置;然后上述控制器单元11根据上述第一输入数据的首地址和第一输入数据的长度从上述存储单元10中获取第一输入数据,接着将该第一输入数据和小数点位置传输至上述转换单元13;将上述输出数据的首地址传输至上述运算单元12。上述转换单元根据上述小数点位置将上述第一输入数据转换为第二输入数据,然后将该第二输入数据传输至上述运算单元13,该运算单元12的主处理电路101和从处理电路102按照对上述第二输入数据进行运算,以得到计算指令的结果,并将该计算指令的结果存储至上述存储单元10中上述输出数据的首地址对应的位置。After the above-mentioned

在一种可行的实施例中,上述计算装置的运算单元13在进行上述多层神经网络模型的第i层的运算之前,该计算装置的控制器单元11获取配置指令,该配置指令包括小数点位置和参与运算的数据类型。该控制器单元11解析该配置指令,以得到小数点位置和参与运算的数据类型,或者从上述存储单元10中直接获取上述小数点位置和参与运算的数据类型,然后上述控制器单元11获取输入数据后,判断输入数据的数据类型与参与运算的数据类型是否一致;当确定输入数据的数据类型与参与运算的数据类型不一致时,上述控制器单元11将上述输入数据、小数点位置和参与运算的数据类型传输至上述转换单元13;该转换单元根据上述小数点位置和参与运算的数据类型对上述输入数据进行数据类型转换,使得输入数据的数据类型与参与运算的数据类型一致;然后将转换后的数据传输至上述运算单元12,该运算单元12的主处理电路101和从处理电路102对转换后的输入数据进行运算;当确定输入数据的数据类型与参与运算的数据类型一致时,上述控制器单元11将上述输入数据传输至上述运算单元12,该运算单元12的主处理电路101和从处理电路102直接对输入数据进行运算,不用进行数据类型转换。In a feasible embodiment, before the

进一步地,当上述输入数据为定点数据且参与运算的数据类型为定点数据时,上述控制器单元11判断输入数据的小数点位置与参与运算的小数点位置是否一致,若不一致,上述控制器单元11将上述输入数据、输入数据的小数点位置和参与运算的小数点位置传输至上述转换单元13,该转换单元13将输入数据转换为与小数点位置与参与运算的数据的小数点位置一致的定点数据,然后将转换后的数据传输至上述运算单元,该运算单元12的主处理电路101和从处理电路102对转换后的数据进行运算。Further, when the above-mentioned input data is fixed-point data and the data type participating in the operation is fixed-point data, the above-mentioned

换句话说,上述运算指令可以替换为上述配置指令。In other words, the above-mentioned operation instructions can be replaced with the above-mentioned configuration instructions.

另一个实施例里,该运算指令为矩阵乘以矩阵的指令、累加指令、激活指令等等计算指令。In another embodiment, the operation instruction is a matrix-by-matrix instruction, an accumulation instruction, an activation instruction, and other calculation instructions.

在一种可选的实施方案中,如图3E所示,所述运算单元包括:树型模块40,所述树型模块包括:一个根端口401和多个支端口404,所述树型模块的根端口连接所述主处理电路101,所述树型模块的多个支端口分别连接多个从处理电路102中的一个从处理电路102;In an optional implementation, as shown in FIG. 3E, the operation unit includes: a

上述树型模块具有收发功能,如图3E所示,该树型模块即为发送功能,如图6A所示,该树型模块即为接收功能。The above-mentioned tree-type module has a transceiver function. As shown in FIG. 3E , the tree-type module is a sending function. As shown in FIG. 6A , the tree-type module is a receiving function.

所述树型模块,用于转发所述主处理电路101与所述多个从处理电路102之间的数据块、权值以及运算指令。The tree module is configured to forward data blocks, weights and operation instructions between the

可选的,该树型模块为计算装置的可选择结果,其可以包括至少1层节点,该节点为具有转发功能的线结构,该节点本身可以不具有计算功能。如树型模块具有零层节点,即无需该树型模块。Optionally, the tree-type module is a selectable result of the computing device, which may include at least one layer of nodes, the node is a line structure with a forwarding function, and the node itself may not have a computing function. If a tree-type module has zero-level nodes, the tree-type module is not required.

可选的,该树型模块可以为n叉树结构,例如,如图3F所示的二叉树结构,当然也可以为三叉树结构,该n可以为大于等于2的整数。本申请具体实施方式并不限制上述n的具体取值,上述层数也可以为2,从处理电路102可以连接除倒数第二层节点以外的其他层的节点,例如可以连接如图3F所示的倒数第一层的节点。Optionally, the tree module may be an n-ary tree structure, for example, a binary tree structure as shown in FIG. 3F , or a ternary tree structure, of course, and n may be an integer greater than or equal to 2. The specific implementation manner of the present application does not limit the specific value of the above n, and the above-mentioned number of layers can also be 2, and the

可选的,上述运算单元可以携带单独的缓存,如图3G所示,可以包括:神经元缓存单元,该神经元缓存单元63缓存该从处理电路102的输入神经元向量数据和输出神经元值数据。Optionally, the above-mentioned operation unit may carry a separate buffer, as shown in FIG. 3G , may include: a neuron buffer unit, the

如图3H所示,该运算单元还可以包括:权值缓存单元64,用于缓存该从处理电路102在计算过程中需要的权值数据。As shown in FIG. 3H , the operation unit may further include: a weight

在一种可选实施例中,以神经网络运算中的全连接运算为例,过程可以为:y=f(wx+b),其中,x为输入神经元矩阵,w为权值矩阵,b为偏置标量,f为激活函数,具体可以为:sigmoid函数,tanh、relu、softmax函数中的任意一个。这里假设为二叉树结构,具有8个从处理电路102,其实现的方法可以为:In an optional embodiment, taking the fully connected operation in the neural network operation as an example, the process may be: y=f(wx+b), where x is the input neuron matrix, w is the weight matrix, b is a bias scalar, and f is an activation function, which can be: sigmoid function, any one of tanh, relu, and softmax functions. Here, it is assumed to be a binary tree structure with 8

控制器单元11从存储单元10内获取输入神经元矩阵x,权值矩阵w以及全连接运算指令,将输入神经元矩阵x,权值矩阵w以及全连接运算指令传输给主处理电路101;The

主处理电路101将输入神经元矩阵x拆分成8个子矩阵,然后将8个子矩阵通过树型模块分发给8个从处理电路102,将权值矩阵w广播给8个从处理电路102,The

从处理电路102并行执行8个子矩阵与权值矩阵w的乘法运算和累加运算得到8个中间结果,将8个中间结果发送给主处理电路101;The

上述主处理电路101,用于将8个中间结果排序得到wx的运算结果,将该运算结果执行偏置b的运算后执行激活操作得到最终结果y,将最终结果y发送至控制器单元11,控制器单元11将该最终结果y输出或存储至存储单元10内。The above-mentioned

在一个实施例里,运算单元12包括但不仅限于:第一部分的第一个或多个乘法器;第二部分的一个或者多个加法器(更具体的,第二个部分的加法器也可以组成加法树);第三部分的激活函数单元;和/或第四部分的向量处理单元。更具体的,向量处理单元可以处理向量运算和/或池化运算。第一部分将输入数据1(in1)和输入数据2(in2)相乘得到相乘之后的输出(out),过程为:out=in1*in2;第二部分将输入数据in1通过加法器相加得到输出数据(out)。更具体的,第二部分为加法树时,将输入数据in1通过加法树逐级相加得到输出数据(out),其中in1是一个长度为N的向量,N大于1,过程为:out=in1[1]+in1[2]+...+in1[N],和/或将输入数据(in1)通过加法数累加之后和输入数据(in2)相加得到输出数据(out),过程为:out=in1[1]+in1[2]+...+in1[N]+in2,或者将输入数据(in1)和输入数据(in2)相加得到输出数据(out),过程为:out=in1+in2;第三部分将输入数据(in)通过激活函数(active)运算得到激活输出数据(out),过程为:out=active(in),激活函数active可以是sigmoid、tanh、relu、softmax等,除了做激活操作,第三部分可以实现其他的非线性函数,可将输入数据(in)通过运算(f)得到输出数据(out),过程为:out=f(in)。向量处理单元将输入数据(in)通过池化运算得到池化操作之后的输出数据(out),过程为out=pool(in),其中pool为池化操作,池化操作包括但不限于:平均值池化,最大值池化,中值池化,输入数据in是和输出out相关的一个池化核中的数据。In one embodiment, the

所述运算单元执行运算包括第一部分是将所述输入数据1和输入数据2相乘,得到相乘之后的数据;和/或第二部分执行加法运算(更具体的,为加法树运算,用于将输入数据1通过加法树逐级相加),或者将所述输入数据1通过和输入数据2相加得到输出数据;和/或第三部分执行激活函数运算,对输入数据通过激活函数(active)运算得到输出数据;和/或第四部分执行池化运算,out=pool(in),其中pool为池化操作,池化操作包括但不限于:平均值池化,最大值池化,中值池化,输入数据in是和输出out相关的一个池化核中的数据。以上几个部分的运算可以自由选择一个多个部分进行不同顺序的组合,从而实现各种不同功能的运算。计算单元相应的即组成了二级,三级,或者四级流水级架构。The operation performed by the operation unit includes that the first part is to multiply the

需要说明的是,上述第一输入数据为长位数非定点数据,例如32位浮点数据,也可以是针对标准的64位或者16位浮点数等,这里只是以32位为具体实施例进行说明;上述第二输入数据为短位数定点数据,又称为较少位数定点数据,表示相对于长位数非定点数据的第一输入数据来说,采用更少的位数来表示的定点数据。It should be noted that the above-mentioned first input data is long-digit non-fixed-point data, such as 32-bit floating-point data, or can also be for standard 64-bit or 16-bit floating-point numbers, etc. Here, only 32-bit is used as a specific example. Explanation; the above-mentioned second input data is short-digit fixed-point data, also known as less-digit fixed-point data, which means that compared with the first input data of long-digit non-fixed-point data, it is represented by fewer digits. Fixed-point data.

在一种可行的实施例中,上述第一输入数据为非定点数据,上述第二输入数据为定点数据,该第一输入数据占的比特位数大于或者等于上述第二输入数据占的比特位数。比如上述第一输入输入数据为32位浮点数,上述第二输入数据为32位定点数据;再比如上述第一输入输入数据为32位浮点数,上述第二输入数据为16位定点数据。In a feasible embodiment, the first input data is non-fixed-point data, the second input data is fixed-point data, and the number of bits occupied by the first input data is greater than or equal to the number of bits occupied by the second input data number. For example, the first input data is a 32-bit floating point number, and the second input data is 32-bit fixed-point data; for example, the first input data is a 32-bit floating point number, and the second input data is 16-bit fixed-point data.

具体地,对于不同的网络模型的不同的层,上述第一输入数据包括不同类型的数据。该不同类型的数据的小数点位置不相同,即对应的定点数据的精度不同。对于全连接层,上述第一输入数据包括输入神经元、权值和偏置数据等数据;对于卷积层时,上述第一输入数据包括卷积核、输入神经元和偏置数据等数据。Specifically, for different layers of different network models, the above-mentioned first input data includes different types of data. The decimal point positions of the different types of data are different, that is, the precision of the corresponding fixed-point data is different. For a fully connected layer, the first input data includes data such as input neurons, weights, and bias data; for a convolutional layer, the first input data includes data such as convolution kernels, input neurons, and bias data.

比如对于全连接层,上述小数点位置包括输入神经元的小数点位置、权值的小数点位置和偏置数据的小数点位置。其中,上述输入神经元的小数点位置、权值的小数点位置和偏置数据的小数点位置可以全部相同或者部分相同或者互不相同。For example, for a fully connected layer, the above-mentioned decimal point position includes the decimal point position of the input neuron, the decimal point position of the weight, and the decimal point position of the bias data. Wherein, the position of the decimal point of the input neuron, the position of the decimal point of the weight, and the position of the decimal point of the bias data may be all the same or partially the same or different from each other.

在一种可行的实施例中,所述控制器单元11还用于:在获取第一输入数据以及计算指令之前,确定所述第一输入数据的小数点位置和定点数据的位宽;所述定点数据的位宽为所述第一输入数据转换为定点数据的位宽;In a feasible embodiment, the

运算单元12,还用于初始化所述第一输入数据的小数点位置和调整所述第一输入数据的小数点位置。The

其中,上述第一输入数据的定点数据的位宽为以定点数据表示的第一输入数据所占的比特位,上述小数点位置为以定点数据表示的第一数据数据的小数部分所占的比特位。该小数点位置用于表征定点数据的精度。具体参见图2A的相关描述。Wherein, the bit width of the fixed-point data of the first input data is the bits occupied by the first input data represented by the fixed-point data, and the position of the decimal point is the bits occupied by the fractional part of the first data data represented by the fixed-point data . The decimal point position is used to characterize the precision of fixed-point data. Please refer to the related description of FIG. 2A for details.

具体地,第一输入数据可以为任意类型的数据,该第一输入数据a根据上述小数点位置和定点数据的位宽转换为第二输入数据具体如下:Specifically, the first input data may be any type of data, and the first input data a is converted into the second input data according to the position of the decimal point and the bit width of the fixed-point data details as follows:

其中,当上述第一输入数据a满足条件neg≤a≤pos时,上述第二输入数据为|a/2s|*2s;当上述第一输入数据a大于pos时,上述第二输入数据为pos;当上述第一输入数据a小于neg时,上述第二输入数据为neg。Wherein, when the first input data a satisfies the condition neg≤a≤pos, the second input data is |a/2s |*2s ; when the above-mentioned first input data a is greater than pos, the above-mentioned second input data is pos; when the above-mentioned first input data a is less than neg, the above-mentioned second input data for neg.

在一种实施例中,对于卷积层和全连接层的输入神经元、权值、输出神经元、输入神经元导数、输出神经元导数和权值导数均采用定点数据进行表示。In one embodiment, the input neurons, weights, output neurons, input neuron derivatives, output neuron derivatives, and weight derivatives of the convolutional layer and the fully connected layer are all represented by fixed-point data.

可选地,上述输入神经元采用的定点数据的位宽可为8、16、32、64或者其他值。进一步地,上述输入神经元采用的定点数据的位宽为8。Optionally, the bit width of the fixed-point data used by the above-mentioned input neurons may be 8, 16, 32, 64 or other values. Further, the bit width of the fixed-point data used by the above input neuron is 8.

可选地,上述权值采用的定点数据的位宽可为8、16、32、64或者其他值。进一步地,上述权值采用的定点数据的位宽为8。Optionally, the bit width of the fixed-point data used by the above weights may be 8, 16, 32, 64 or other values. Further, the bit width of the fixed-point data used for the above weights is 8.

可选地,上述输入神经元导数采用的定点数据的位宽可为8、16、32、64或者其他值。进一步地,上述输入神经元导数采用的定点数据的位宽为16。Optionally, the bit width of the fixed-point data used for the input neuron derivative may be 8, 16, 32, 64 or other values. Further, the bit width of the fixed-point data used for the above input neuron derivative is 16.

可选地,上述输出神经元导数采用的定点数据的位宽可为8、16、32、64或者其他值。进一步地,上述输出神经元导数采用的定点数据的位宽为24。Optionally, the bit width of the fixed-point data used for the above-mentioned output neuron derivative may be 8, 16, 32, 64 or other values. Further, the bit width of the fixed-point data used for the above-mentioned output neuron derivative is 24.

可选地,上述权值导数采用的定点数据的位宽可为8、16、32、64或者其他值。进一步地,上述权值导数采用的定点数据的位宽为24。Optionally, the bit width of the fixed-point data used for the weight derivative may be 8, 16, 32, 64 or other values. Further, the bit width of the fixed-point data used in the weight derivative is 24.

在一种实施例中,对于参与上述多层网络模型运算的数据中数值较大的数据a可采用多种定点表示方法,具体参见图2B的相关描述。In an embodiment, multiple fixed-point representation methods may be used for the data a with a larger value in the data participating in the above-mentioned multi-layer network model operation. For details, please refer to the relevant description of FIG. 2B .

具体地,第一输入数据可以为任意类型的数据,该第一输入数据a根据上述小数点位置和定点数据的位宽转换为第二输入数据具体如下:Specifically, the first input data may be any type of data, and the first input data a is converted into the second input data according to the position of the decimal point and the bit width of the fixed-point data details as follows:

其中,当上述第一输入数据a满足条件neg≤a≤pos时,上述第二输入数据为且当上述第一输入数据a大于pos时,上述第二输入数据为pos;当上述第一输入数据a小于neg时,上述第二输入数据为neg。Wherein, when the first input data a satisfies the condition neg≤a≤pos, the second input data for and When the first input data a is greater than pos, the second input data is pos; when the above-mentioned first input data a is less than neg, the above-mentioned second input data for neg.

进一步地,所述运算单元12初始化所述第一输入数据的小数点位置,包括:Further, the

根据所述第一输入数据绝对值的最大值初始化所述第一输入数据的小数点位置,或者;Initialize the decimal point position of the first input data according to the maximum value of the absolute value of the first input data, or;

根据所述第一输入数据的绝对值最小值初始化所述第一输入数据的小数点位置,或者;Initialize the decimal point position of the first input data according to the minimum absolute value of the first input data, or;

根据所述第一输入数据中不同数据类型间关系初始化所述第一输入数据的小数点位置,或者;Initialize the decimal point position of the first input data according to the relationship between different data types in the first input data, or;

根据经验值常量初始化所述第一输入数据的小数点位置。The decimal point position of the first input data is initialized according to an empirical value constant.

具体地,其中,上述小数点位置s需要根据不同类别的数据、不同神经网络层的数据,处于不同迭代轮次的数据进行初始化和动态调整。Specifically, the above-mentioned decimal point position s needs to be initialized and dynamically adjusted according to data of different categories, data of different neural network layers, and data in different iteration rounds.

下面具体介绍第一输入数据的小数点位置s的初始化过程,即确定进行第一次将第一输入数据转换时定点数据所采用的小数点位置s。The following specifically describes the initialization process of the decimal point position s of the first input data, that is, determining the decimal point position s used by the fixed-point data when converting the first input data for the first time.

其中,上述运算单元1211对上述第一输入数据的小数点位置s进行初始化包括:根据第一输入数据绝对值最大值初始化第一输入数据的小数点位置s;根据第一输入数据绝对值的最小值初始化第一输入数据的小数点位置s;根据第一输入数据中不同数据类型间关系初始化第一输入数据的小数点位置s;根据经验值常量初始化第一输入数据的小数点位置s。The operation unit 1211 initializing the decimal point position s of the first input data includes: initializing the decimal point position s of the first input data according to the maximum absolute value of the first input data; initializing according to the minimum value of the absolute value of the first input data. The decimal point position s of the first input data; the decimal point position s of the first input data is initialized according to the relationship between different data types in the first input data; the decimal point position s of the first input data is initialized according to the empirical value constant.

具体地,下面分别具体介绍上述初始化过程。Specifically, the above initialization processes are described in detail below.

a)、上述计算单元12根据第一输入数据绝对值的最大值初始化第一输入数据的小数点位置s:a), the above-mentioned

上述运算单元12具体通过进行以下公式所示的运算,以初始化上述第一输入数据的小数点位置s:。The above-mentioned

其中,上述amax为上述第一输入数据绝对值的最大值,上述bitnum为上述第一输入数据转换为定点数据的位宽,上述sa为上述第一输入数据的小数点位置。The amax is the maximum absolute value of the first input data, the bitnum is the bit width of the first input data converted to fixed-point data, and the sa is the decimal point position of the first input data.

其中,参与运算的数据按类别与网络层次可分为:第l层的输入神经元X(l)、输出神经元Y(l)、权值W(l)、输入神经元导数输出神经元导数和权值导数寻找绝对值最大值时,可以按数据类别寻找;可以分层、分类别寻找;可以分层、分类别、分组寻找。第一输入数据绝对值的最大值的确定方法包括:Among them, the data involved in the operation can be divided into: the input neuron X(l) of the lth layer, the output neuron Y(l) , the weight W(l) , the input neuron derivative output neuron derivative and weight derivatives When looking for the maximum absolute value, you can search by data category; you can search by layers and categories; you can search by layers, categories, and groups. The method for determining the maximum value of the absolute value of the first input data includes:

a.1)、上述计算单元12按数据类别寻找绝对值最大值a.1), the