CN107342216B - Plasma Activated Conformal Dielectric Film Deposition - Google Patents

Plasma Activated Conformal Dielectric Film DepositionDownload PDFInfo

- Publication number

- CN107342216B CN107342216BCN201710347032.2ACN201710347032ACN107342216BCN 107342216 BCN107342216 BCN 107342216BCN 201710347032 ACN201710347032 ACN 201710347032ACN 107342216 BCN107342216 BCN 107342216B

- Authority

- CN

- China

- Prior art keywords

- reactant

- film

- plasma

- cfd

- dopant

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/04—Coating on selected surface areas, e.g. using masks

- C23C16/045—Coating cavities or hollow spaces, e.g. interior of tubes; Infiltration of porous substrates

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/44—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating

- C23C16/4401—Means for minimising impurities, e.g. dust, moisture or residual gas, in the reaction chamber

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/44—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating

- C23C16/455—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating characterised by the method used for introducing gases into reaction chamber or for modifying gas flows in reaction chamber

- C23C16/45523—Pulsed gas flow or change of composition over time

- C23C16/45525—Atomic layer deposition [ALD]

- C23C16/45527—Atomic layer deposition [ALD] characterized by the ALD cycle, e.g. different flows or temperatures during half-reactions, unusual pulsing sequence, use of precursor mixtures or auxiliary reactants or activations

- C23C16/45536—Use of plasma, radiation or electromagnetic fields

- C23C16/4554—Plasma being used non-continuously in between ALD reactions

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/56—After-treatment

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/02126—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material containing Si, O, and at least one of H, N, C, F, or other non-metal elements, e.g. SiOC, SiOC:H or SiONC

- H01L21/02129—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material containing Si, O, and at least one of H, N, C, F, or other non-metal elements, e.g. SiOC, SiOC:H or SiONC the material being boron or phosphorus doped silicon oxides, e.g. BPSG, BSG or PSG

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/02164—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material being a silicon oxide, e.g. SiO2

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02205—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition

- H01L21/02208—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition the precursor containing a compound comprising Si

- H01L21/02211—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition the precursor containing a compound comprising Si the compound being a silane, e.g. disilane, methylsilane or chlorosilane

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/0226—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process

- H01L21/02263—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase

- H01L21/02271—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition

- H01L21/02274—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition in the presence of a plasma [PECVD]

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/0226—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process

- H01L21/02263—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase

- H01L21/02271—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition

- H01L21/0228—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition deposition by cyclic CVD, e.g. ALD, ALE, pulsed CVD

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02296—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer

- H01L21/02299—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer pre-treatment

- H01L21/02312—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer pre-treatment treatment by exposure to a gas or vapour

- H01L21/02315—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer pre-treatment treatment by exposure to a gas or vapour treatment by exposure to a plasma

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02296—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer

- H01L21/02318—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment

- H01L21/02337—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment treatment by exposure to a gas or vapour

- H01L21/0234—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment treatment by exposure to a gas or vapour treatment by exposure to a plasma

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02296—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer

- H01L21/02318—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment

- H01L21/02345—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment treatment by exposure to radiation, e.g. visible light

- H01L21/02348—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment treatment by exposure to radiation, e.g. visible light treatment by exposure to UV light

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02612—Formation types

- H01L21/02617—Deposition types

- H01L21/0262—Reduction or decomposition of gaseous compounds, e.g. CVD

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31105—Etching inorganic layers

- H01L21/31111—Etching inorganic layers by chemical means

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/76224—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using trench refilling with dielectric materials

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76822—Modification of the material of dielectric layers, e.g. grading, after-treatment to improve the stability of the layers, to increase their density etc.

- H01L21/76825—Modification of the material of dielectric layers, e.g. grading, after-treatment to improve the stability of the layers, to increase their density etc. by exposing the layer to particle radiation, e.g. ion implantation, irradiation with UV light or electrons etc.

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76822—Modification of the material of dielectric layers, e.g. grading, after-treatment to improve the stability of the layers, to increase their density etc.

- H01L21/76826—Modification of the material of dielectric layers, e.g. grading, after-treatment to improve the stability of the layers, to increase their density etc. by contacting the layer with gases, liquids or plasmas

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76829—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing characterised by the formation of thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers

- H01L21/76831—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing characterised by the formation of thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers in via holes or trenches, e.g. non-conductive sidewall liners

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76837—Filling up the space between adjacent conductive structures; Gap-filling properties of dielectrics

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76898—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics formed through a semiconductor substrate

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/024—Manufacture or treatment of FETs having insulated gates [IGFET] of fin field-effect transistors [FinFET]

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Chemical & Material Sciences (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Plasma & Fusion (AREA)

- General Chemical & Material Sciences (AREA)

- Materials Engineering (AREA)

- Mechanical Engineering (AREA)

- Metallurgy (AREA)

- Organic Chemistry (AREA)

- Inorganic Chemistry (AREA)

- Electromagnetism (AREA)

- Chemical Vapour Deposition (AREA)

- Formation Of Insulating Films (AREA)

Abstract

Translated fromChineseDescription

Translated fromChinese本申请是申请日为2012年8月29日,申请号为201280046487.6,申请人为诺发系统公司,名称为“等离子体活化保形电介质膜沉积”的专利申请的分案申请。This application is a divisional application of a patent application entitled "Plasma-Activated Conformal Dielectric Film Deposition" with the application date of August 29, 2012, the application number is 201280046487.6, and the applicant is Nova Systems Corporation.

相关申请的交叉引用CROSS-REFERENCE TO RELATED APPLICATIONS

根据35U.S.C.§120,本申请作为2011年4月11日提交的美国专利申请No.13/084,399的部分继续申请要求优先权,美国专利申请 No.13/084,399主张于2010年4月15日提交的美国临时专利申请号61/324710、于2010年8月10日提交的美国临时专利申请号61/372,367、于 2010年9月1日提交的美国临时专利申请号61/379,081、以及于2010年11 月29日提交的美国临时专利申请号61/417,807的利益。上述专利申请中的每一个其全部内容通过引用并入本申请,并用于所有目的。本申请也是于2011 年4月11日提交的美国专利申请No.13/084,305申请的部分继续申请,其全部内容通过引用并入本申请,并用于所有目的。This application claims priority under 35 U.S.C. §120 as a continuation-in-part of US Patent Application No. 13/084,399, filed April 11, 2011, claimed April 15, 2010 US Provisional Patent Application No. 61/324710 filed, US Provisional Patent Application No. 61/372,367 filed August 10, 2010, US Provisional Patent Application No. 61/379,081 filed September 1, 2010, and of the interest of US Provisional Patent Application No. 61/417,807, filed November 29, 2007. The entire contents of each of the aforementioned patent applications are hereby incorporated by reference into this application and are used for all purposes. This application is also a continuation-in-part of US Patent Application No. 13/084,305, filed April 11, 2011, the entire contents of which are incorporated herein by reference and are used for all purposes.

技术领域technical field

本发明涉及半导体制造工艺,尤其是涉及等离子体活化保形电介质膜沉积。The present invention relates to semiconductor fabrication processes, and more particularly to plasma-activated conformal dielectric film deposition.

背景技术Background technique

用于半导体器件的各种薄膜层可利用原子层沉积(ALD)工艺沉积。但是,现有的ALD工艺可能不适合用于沉积高度保形的电介质膜。Various thin film layers for semiconductor devices can be deposited using atomic layer deposition (ALD) processes. However, existing ALD processes may not be suitable for depositing highly conformal dielectric films.

发明内容SUMMARY OF THE INVENTION

本文所公开的各个方面涉及用于在衬底表面上沉积膜的方法和装置。在某些实施方案中,所述方法包括通过表面介导反应沉积膜,在所述反应中经过反应物的吸附和反应的一个或多个循环使膜生长。在一个方面,该方法的特征在于,在吸附和反应的循环之间间歇输送掺杂物质到膜。在某些时候,该掺杂剂物质可被驱动跨越衬底表面到所述衬底的掺杂区域。Various aspects disclosed herein relate to methods and apparatus for depositing films on substrate surfaces. In certain embodiments, the method includes depositing a film by a surface-mediated reaction in which the film is grown through one or more cycles of adsorption and reaction of reactants. In one aspect, the method is characterized by intermittently delivering the dopant species to the membrane between cycles of adsorption and reaction. At some point, the dopant species may be driven across the surface of the substrate to a doped region of the substrate.

在一个方面,公开的方法在反应室中在衬底表面上沉积膜。所述方法的特征在于以下操作:(a)在允许第一反应物吸附到所述衬底表面的条件下将所述第一反应物引入所述反应室;(b)在所述第一反应物被吸附在所述衬底表面上的同时,将第二反应物引入所述反应室;(c)将所述衬底表面暴露于等离子体以驱动所述衬底表面上的所述第一和所述第二反应物之间的反应以形成所述膜的一部分;(d)重复(a)-(c)至少一次;(e)在允许包含掺杂剂的材料接触所述膜的暴露表面的条件下,将所述包含掺杂剂的材料引入所述反应室,而在(a)-(d)中不引入;以及(f)将掺杂剂从所述包含掺杂剂的材料引入所述膜。将所述掺杂剂引入所述膜可涉及将所述包含掺杂剂的材料暴露于等离子体。In one aspect, the disclosed method deposits a film on a substrate surface in a reaction chamber. The method is characterized by the following operations: (a) introducing the first reactant into the reaction chamber under conditions that allow adsorption of the first reactant to the substrate surface; (b) during the first reaction introducing a second reactant into the reaction chamber while the species is adsorbed on the substrate surface; (c) exposing the substrate surface to a plasma to drive the first reactant on the substrate surface and the second reactant to form a portion of the film; (d) repeating (a)-(c) at least once; (e) during exposure allowing dopant-containing material to contact the film introducing the dopant-containing material into the reaction chamber under surface conditions but not in (a)-(d); and (f) introducing the dopant from the dopant-containing material Introduce the membrane. Introducing the dopant into the film may involve exposing the dopant-containing material to a plasma.

在各种实施方式中,所述方法另外包括从所述膜驱动所述掺杂剂到所述膜驻留的所述衬底表面的特征中。从所述膜驱动所述掺杂剂可通过对所述膜进行退火处理来实现。在一些应用中,所述膜驻留在所述衬底表面的三维特征上,并且驱动来自所述膜的掺杂剂使所述掺杂剂保形扩散到所述特征中。在特定应用中,所述特征具有不大于约40纳米的宽度。In various embodiments, the method additionally includes driving the dopant from the film into features of the substrate surface where the film resides. Driving the dopant from the film may be accomplished by annealing the film. In some applications, the film resides on a three-dimensional feature of the substrate surface, and driving a dopant from the film causes conformal diffusion of the dopant into the feature. In certain applications, the features have a width of no greater than about 40 nanometers.

在某些实施方式中,膜是电介质膜。在一些情况下,总的膜厚度介于约10-100埃之间。在各种实施方式中,在膜中的掺杂剂浓度为介于按重量计约0.01%至10%之间。In certain embodiments, the film is a dielectric film. In some cases, the total film thickness is between about 10-100 angstroms. In various embodiments, the dopant concentration in the film is between about 0.01% to 10% by weight.

在某些实施方式中,方法的该方面另外包括在(e)或(f)之后重复(a)-(c)。在某些实施方式中,本方法的该方面另外包括重复(a)- (e)。在一些实施方式中,在(a)-(c)中沉积的膜的量为介于约0.5至1 埃之间。In certain embodiments, this aspect of the method further comprises repeating (a)-(c) after (e) or (f). In certain embodiments, this aspect of the method additionally comprises repeating (a)-(e). In some embodiments, the amount of film deposited in (a)-(c) is between about 0.5 to 1 Angstrom.

在某些实施方式中,所述方法另外包括在将所述衬底表面暴露于等离子体之前从所述反应室清除所述第二反应物。所述清除可以通过使含有氧化剂的气体流入所述反应室来实现。在一些实施方式中,所述第一和第二反应物以气相共存于所述反应室中,并且在所述反应室中所述第一和第二反应物直至在(c)中暴露于等离子体中才会明显相互反应。In certain embodiments, the method additionally includes purging the second reactant from the reaction chamber prior to exposing the substrate surface to the plasma. The purging can be accomplished by flowing an oxidant-containing gas into the reaction chamber. In some embodiments, the first and second reactants coexist in the reaction chamber in a gas phase, and the first and second reactants remain in the reaction chamber until exposed to the plasma in (c) The body reacts significantly with each other.

在某些实施方式中,第一反应物是氧化剂,例如,一氧化二氮。在某些实施方式中,第二反应物是电介质前体,例如(i)烷氨基硅烷(SiHx (NR2)4-x)中,其中x=1-3,并且R包括烷基,或(ii)卤代硅烷(SiHxY4-x),其中X=1-3,以及Y包括Cl、Br和I。在一个具体实施方式中,第二反应物是BTBAS。在某些实施方式中,所述包含掺杂剂的材料选自膦、砷化氢、烷基硼、烷基镓烷、烷基膦、卤化磷、卤化砷、卤化镓、卤化硼、烷基硼,和乙硼烷。In certain embodiments, the first reactant is an oxidizing agent, eg, nitrous oxide. In certain embodiments, the second reactant is a dielectric precursor, such as in (i) an alkylaminosilane (SiHx (NR2 )4-x ), where x = 1-3, and R includes an alkyl group, or (ii) Halosilanes (SiHx Y4-x ), where X=1-3, and Y includes Cl, Br and I. In a specific embodiment, the second reactant is BTBAS. In certain embodiments, the dopant-containing material is selected from the group consisting of phosphine, arsine, alkyl boron, alkyl gallium, alkyl phosphine, phosphorus halide, arsenic halide, gallium halide, boron halide, alkyl halide Boron, and Diborane.

在另一个方面,一种公开的方法在反应室中在衬底表面上沉积膜。所述方法的特征在于以下操作:(a)在允许第一反应物吸附到所述衬底表面上的条件下使氧化剂流入所述反应室;(b)在所述氧化剂继续流入所述反应室的同时,将电介质前体引入所述反应室;(c)将所述衬底表面暴露于等离子体以驱动在所述衬底表面上的所述电介质前体和氧化剂反应,以形成所述电介质膜的一部分;(d)在允许包含掺杂剂的材料接触所述膜的暴露表面的条件下,将所述包含掺杂剂的材料引入所述反应室,而在(a)-(c)中不引入;和(e)造成来自所述包含掺杂剂的材料的掺杂剂结合入所述电介质膜。在一个实施方式中,所述电介质前体是BTBAS或在先前方面中确定的其他的前体。In another aspect, a disclosed method deposits a film on a substrate surface in a reaction chamber. The method is characterized by the following operations: (a) flowing an oxidant into the reaction chamber under conditions that allow adsorption of a first reactant onto the substrate surface; (b) flowing the oxidant into the reaction chamber while the oxidant continues to flow into the reaction chamber At the same time, a dielectric precursor is introduced into the reaction chamber; (c) the substrate surface is exposed to a plasma to drive the reaction of the dielectric precursor and oxidant on the substrate surface to form the dielectric a portion of a membrane; (d) introducing the dopant-containing material into the reaction chamber under conditions that allow the dopant-containing material to contact the exposed surface of the membrane, while in (a)-(c) and (e) cause dopants from the dopant-containing material to incorporate into the dielectric film. In one embodiment, the dielectric precursor is BTBAS or other precursors identified in the previous aspects.

此外,该方法可以要求重复操作(a)-(c)一次或多次。在一个具体的例子中,当最初执行(a)时,所述氧化剂包含第一比率的氧比氮,而当随后执行(a)时,所述氧化剂包含第二比率的氧比氮。所述第二比率小于所述第一比率。例如,当最初执行(a)时,所述氧化剂可包括元素氧,而当重复(a)时,所述氧化剂包括一氧化二氮。在一些实施方式中,当最初执行(c)时,所述衬底在第一温度,而当重复(c)时,所述衬底在第二温度,所述第二温度高于所述第一温度。Furthermore, the method may require repeating operations (a)-(c) one or more times. In a specific example, when (a) is initially performed, the oxidant comprises a first ratio of oxygen to nitrogen, and when (a) is subsequently performed, the oxidant comprises a second ratio of oxygen to nitrogen. The second ratio is less than the first ratio. For example, when (a) is initially performed, the oxidant may comprise elemental oxygen, and when (a) is repeated, the oxidant comprises nitrous oxide. In some embodiments, when (c) is initially performed, the substrate is at a first temperature, and when (c) is repeated, the substrate is at a second temperature, the second temperature being higher than the first temperature a temperature.

在某些情况下,该方法还包括将掺杂剂从电介质膜驱动进入所述衬底。在一些实施方式中,所述方法还包括在(a)之前将所述衬底表面与所述包含掺杂剂的材料接触。In some cases, the method further includes driving dopants from the dielectric film into the substrate. In some embodiments, the method further includes contacting the substrate surface with the dopant-containing material prior to (a).

在另一方面,本发明所公开的方法根据以下操作在反应室中在衬底表面上沉积电介质膜:(a)在允许电介质前体吸附到所述衬底表面的条件下将所述前体引入所述反应室;(b)此后在所述前体保持吸附在所述衬底表面上的同时,将所述电介质前体从所述反应室清除;(c)将所述衬底表面暴露于等离子体以驱动所述衬底表面上的所述电介质前体的反应以形成所述电介质膜的一部分;以及(d)在允许掺杂剂前体接触所述电介质膜的条件下,将所述掺杂剂前体引入所述反应室,而在(a)-(c)中不引入。在一些实施方式中,所述方法另外包括在(a)-(c)之前和期间使氧化剂流入所述反应室。在一些情况下,所述方法还包括使所述掺杂剂前体反应以将掺杂剂引入到膜中。In another aspect, the disclosed methods deposit a dielectric film on a substrate surface in a reaction chamber according to: (a) depositing a dielectric precursor under conditions that allow adsorption of the precursor to the substrate surface introducing the reaction chamber; (b) thereafter purging the dielectric precursor from the reaction chamber while the precursor remains adsorbed on the substrate surface; (c) exposing the substrate surface in a plasma to drive the reaction of the dielectric precursor on the substrate surface to form a portion of the dielectric film; and (d) under conditions allowing the dopant precursor to contact the dielectric film, The dopant precursor is introduced into the reaction chamber and not introduced in (a)-(c). In some embodiments, the method additionally includes flowing an oxidant into the reaction chamber before and during (a)-(c). In some cases, the method further includes reacting the dopant precursor to introduce a dopant into the film.

本发明的又一个方面涉及用于在衬底表面上沉积掺杂膜的装置。所述装置的特征在于以下特征:反应室,其包括用于在所述掺杂的电介质膜的沉积过程中容纳所述衬底的设备;一个或多个工艺气体进口,其耦合到所述反应室;和控制器。所述控制器被设计或配置成使所述装置执行以下操作: (a)在允许第一反应物吸附到所述衬底表面的条件下将所述第一反应物引入所述反应室;(b)在所述第一反应物被吸附在所述衬底表面上的同时,将第二反应物引入所述反应室;(c)将所述衬底表面暴露于等离子体以驱动所述衬底表面上的所述第一和所述第二反应物之间的反应以形成所述膜的一部分; (d)重复(a)-(c)至少一次;(e)在允许包含掺杂剂的材料接触所述膜的暴露表面的条件下,将所述包含掺杂剂的材料引入所述反应室,在(a)- (d)中不引入;和(f)将掺杂剂从所述包含掺杂剂的材料引入所述膜。所述控制器可以被设计或配置成管理诸如根据其它方面讨论的方法等其他的方法的性能。Yet another aspect of the present invention relates to an apparatus for depositing a doped film on a substrate surface. The apparatus is characterized by the following features: a reaction chamber including equipment for containing the substrate during deposition of the doped dielectric film; one or more process gas inlets coupled to the reaction room; and controller. The controller is designed or configured to cause the apparatus to: (a) introduce the first reactant into the reaction chamber under conditions that allow adsorption of the first reactant to the substrate surface; ( b) introducing a second reactant into the reaction chamber while the first reactant is adsorbed on the substrate surface; (c) exposing the substrate surface to a plasma to drive the substrate reaction between said first and said second reactants on the bottom surface to form a portion of said film; (d) repeating (a)-(c) at least once; (e) containing dopants as permitted introducing the dopant-containing material into the reaction chamber under the condition that the material contacts the exposed surface of the film, not in (a)-(d); and (f) introducing the dopant from all the The dopant-containing material is incorporated into the film. The controller may be designed or configured to manage the performance of other methods, such as those discussed in accordance with other aspects.

在某些实施方式中,所述控制器进一步被设计或配置成造成所述装置在(a)-(d)之前和期间使氧化剂流入所述反应室。在某些实施方式中,所述控制器进一步被设计或配置成在(e)或(f)之后重复(a)-(c)。在某些实施方式中,所述控制器进一步被设计或配置成造成将所述掺杂剂从所述膜驱动到所述膜所在的所述衬底表面的特征中。将所述掺杂剂从所述膜驱动可通过对所述膜进行退火处理来实现。在一些实施方式中,所述控制器进一步被设计或配置成造成(e)在(a)-(d)的一次或更多次重复之间的间隔执行,其中在沉积所述膜的过程中所述间隔是变化的。In certain embodiments, the controller is further designed or configured to cause the apparatus to flow oxidant into the reaction chamber before and during (a)-(d). In certain embodiments, the controller is further designed or configured to repeat (a)-(c) after (e) or (f). In certain embodiments, the controller is further designed or configured to cause the dopant to be driven from the film into a feature of the substrate surface where the film is located. Driving the dopant from the film may be accomplished by annealing the film. In some embodiments, the controller is further designed or configured to cause (e) to be performed at intervals between one or more repetitions of (a)-(d), wherein during deposition of the film The interval is varied.

在各种实施方式中,所述控制器进一步被设计或配置成造成在将所述衬底表面暴露于等离子体之前将所述第二反应物从所述反应室清除。在一个示例中,所述清除通过使含有氧化剂的气体在所述控制器的指引下流入所述反应室来实现。In various embodiments, the controller is further designed or configured to cause the second reactant to be purged from the reaction chamber prior to exposing the substrate surface to the plasma. In one example, the purging is accomplished by flowing an oxidant-containing gas into the reaction chamber under the direction of the controller.

具体而言,本发明的一些方面可以阐述如下:In particular, some aspects of the present invention can be set forth as follows:

1.一种在反应室中的非平坦的衬底表面上沉积膜的方法,所述方法包括:1. A method of depositing a film on a non-planar substrate surface in a reaction chamber, the method comprising:

在非等离子体条件下将第一反应物引入所述反应室,使得所述第一反应物吸附在所述非平坦的衬底表面上;introducing a first reactant into the reaction chamber under non-plasma conditions such that the first reactant is adsorbed on the non-planar substrate surface;

在非等离子体条件下将含掺杂剂的材料引入所述反应室;以及introducing a dopant-containing material into the reaction chamber under non-plasma conditions; and

随后将所述非平坦的衬底表面暴露于等离子体以形成与所述非平坦的衬底表面共形的掺杂膜。The uneven substrate surface is then exposed to plasma to form a doped film conformal to the uneven substrate surface.

2.根据条款1所述的方法,其中所述第一反应物是含硅反应物。2. The method of

3.根据条款1所述的方法,其中所述掺杂剂选自硼、磷、砷和镓。3. The method of

4.根据条款1所述的方法,其还包括在将所述非平坦的衬底表面暴露于等离子体之前,将第二反应物引入所述反应室。4. The method of

5.根据条款1所述的方法,其中所述第二反应物是氧化剂。5. The method of

6.根据条款1所述的方法,其中所述第二反应物是含氮反应物。6. The method of

7.根据条款5所述的方法,其中所述掺杂膜是掺杂氧化硅的膜。7. The method of

8.根据条款6所述的方法,其中所述掺杂膜是掺杂氮化硅的膜。8. The method of

9.根据条款1所述的方法,其中所述掺杂膜是掺杂碳化硅的膜。9. The method of

10.根据条款1所述的方法,其还包括在将所述第一反应物吸附到所述非平坦的衬底表面上的同时,将第二反应物引入所述反应室。10. The method of

11.根据条款10所述的方法,其还包括将所述非平坦的衬底表面暴露于等离子体以驱动所述衬底表面上的所述第一反应物和第二反应物之间的反应以形成所述膜的一部分。11. The method of clause 10, further comprising exposing the non-planar substrate surface to a plasma to drive a reaction between the first and second reactants on the substrate surface to form part of the membrane.

这些以及其他的特征将参照相关的附图在下文进行详细描述。These and other features will be described in detail below with reference to the associated drawings.

附图说明Description of drawings

图1根据本公开的实施方式示意性示出了示例的保形膜沉积 (CFD)工艺的时序图。1 schematically illustrates a timing diagram of an example conformal film deposition (CFD) process in accordance with embodiments of the present disclosure.

图2根据本公开的实施方式示意性示出了另一示例的CFD工艺的时序图。FIG. 2 schematically illustrates a timing diagram of another example CFD process according to an embodiment of the present disclosure.

图3根据本公开的实施方式示意性示出了另一示例的CFD工艺的时序图。FIG. 3 schematically illustrates a timing diagram of another example CFD process according to an embodiment of the present disclosure.

图4根据本公开的实施方式示意性示出了一示例的包括等离子体处理循环的CFD工艺的时序图。4 schematically illustrates a timing diagram of an example CFD process including a plasma processing cycle, in accordance with embodiments of the present disclosure.

图5根据本公开的实施方式示出了所沉积的膜的湿法蚀刻速率比和沉积温度之间的示例的相关性。5 illustrates an example correlation between wet etch rate ratio and deposition temperature for a deposited film, according to an embodiment of the present disclosure.

图6根据本公开的实施方式示出了所沉积的膜的湿法蚀刻速率比和应力之间的示例的相关性。6 illustrates an example correlation between wet etch rate ratio and stress for a deposited film, according to an embodiment of the present disclosure.

图7根据本公开的实施方式示出了所沉积的膜的膜污染物浓度和沉积温度之间的示例的相关性。7 illustrates an example correlation between film contaminant concentration and deposition temperature of a deposited film, according to an embodiment of the present disclosure.

图8示意性地示出了包含多个空隙的非平坦的衬底的示例的横截面。FIG. 8 schematically illustrates a cross-section of an example of a non-planar substrate containing a plurality of voids.

图9根据本公开的实施方式示意性地示出了包括到PECVD工艺的过渡的示例的CFD工艺的时序图。9 schematically illustrates a timing diagram of an example CFD process including a transition to a PECVD process in accordance with an embodiment of the present disclosure.

图10示意性地示出了包含锁孔空穴的间隙填充的示例的横截面。Figure 10 schematically shows a cross-section of an example of a gap fill including a keyhole cavity.

图11根据本公开的实施方式示意性地示出了包括原位蚀刻的示例的 CFD工艺的时序图。11 schematically illustrates a timing diagram of an example CFD process including in-situ etching in accordance with an embodiment of the present disclosure.

图12A示意性地示出了重入(re-entrant)的间隙填充轮廓的示例的横截面。Figure 12A schematically shows a cross-section of an example of a re-entrant gap filling profile.

图12B根据本公开的实施方式示意性地示出了在原位蚀刻过程中图 12A的重入的间隙填充轮廓的示例的横截面。12B schematically illustrates a cross-section of an example of the reentrant gap-fill profile of FIG. 12A during an in-situ etch process, in accordance with an embodiment of the present disclosure.

图12C根据本公开的实施方式示意性地示出了在原位蚀刻过程中图 12B的间隙填充轮廓的示例的横截面。12C schematically illustrates a cross-section of an example of the gap-fill profile of FIG. 12B during an in-situ etch process, in accordance with an embodiment of the present disclosure.

图13根据本公开的实施方式示意性地示出了示例的处理站。Figure 13 schematically illustrates an example processing station in accordance with an embodiment of the present disclosure.

图14根据本公开的实施方式示意性地示出了包括多个处理站和控制器的示例性处理工具。14 schematically illustrates an exemplary processing tool including a plurality of processing stations and a controller in accordance with an embodiment of the present disclosure.

图15根据本公开的实施方式示意性地示出了在包括原位蚀刻的 CFD工艺过程中的硅通孔的示例的横截面图。15 schematically illustrates a cross-sectional view of an example of a TSV during a CFD process including in-situ etching, in accordance with an embodiment of the present disclosure.

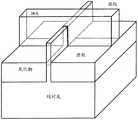

图16示出了具有三维栅结构的晶体管,其中,源极和漏极形成在难以通过传统的离子注入技术掺杂的薄垂直结构中。Figure 16 shows a transistor with a three-dimensional gate structure in which the source and drain are formed in thin vertical structures that are difficult to dope by conventional ion implantation techniques.

图17呈现了随着时间沿x轴推进从左到右的基准CFD操作顺序。Figure 17 presents the baseline CFD sequence of operations advancing from left to right along the x-axis over time.

图18和19描绘了其中掺杂剂沉积在下伏衬底的界面处,随后CFD 循环与掺杂剂输送穿插,且任选地用未掺杂的保护性“加盖(capping)”层可以是CFD氧化膜结束的实施方式。Figures 18 and 19 depict where dopants are deposited at the interface of the underlying substrate, followed by CFD cycles interspersed with dopant delivery, and optionally with an undoped protective "capping" layer which can be Embodiment of CFD oxide film finish.

图20显示了用于合成CFD BSG/PSG膜的典型沉积框图。Figure 20 shows a typical deposition block diagram for synthesizing CFD BSG/PSG films.

图21显示了在致密和隔离的结构上CFD膜的阶梯覆盖性计算为。Figure 21 shows that the step coverage of CFD films on dense and isolated structures is calculated as .

图22呈现了SIMS数据,其示出了在CFD膜中平均硼浓度可在约 0.5-3.5重量%硼的范围中调节。Figure 22 presents SIMS data showing that the average boron concentration in the CFD films can be adjusted in the range of about 0.5-3.5 wt% boron.

具体实施方式Detailed ways

半导体器件的制造通常涉及在集成制造工艺中在非平坦的衬底上沉积一个或多个薄膜。在集成工艺的一些方面,沉积与衬底形貌共形的薄膜可能是有用的。例如,氮化硅膜可以沉积在增高的栅极堆叠(elevated gate stack)的顶部作为间隔层以保护轻掺杂的源极和漏极区域免受随后的离子注入工艺的损坏。The fabrication of semiconductor devices typically involves depositing one or more thin films on a non-planar substrate in an integrated fabrication process. In some aspects of the integration process, it may be useful to deposit thin films that are conformal to the substrate topography. For example, a silicon nitride film can be deposited on top of an elevated gate stack as a spacer layer to protect the lightly doped source and drain regions from damage by subsequent ion implantation processes.

在间隔层沉积工艺中,化学气相沉积(CVD)工艺可用于在非平坦的衬底上形成氮化硅膜,然后对其各向异性蚀刻以形成间隔结构。然而,随着栅堆叠之间的距离减小,CVD气相反应的物质运输限制可能会导致“面包块”(“bread-loafing”)沉积效应。这些效应通常导致在栅堆叠的顶面出现较厚的沉积物并且在栅堆叠的底部角落出现较薄的沉积物。此外,由于一些管芯(die)可以有不同器件密度的区域,因此在整个晶片表面的物质运输效应可能会导致在管芯内和晶片内的膜厚度的变化。这些厚度的变化可能导致在一些区域的过蚀刻和在其他区域的蚀刻不足。这会降低器件的性能和/或管芯产量。Among the spacer layer deposition processes, a chemical vapor deposition (CVD) process can be used to form a silicon nitride film on a non-planar substrate, which is then anisotropically etched to form a spacer structure. However, as the distance between the gate stacks decreases, the species transport limitations of the CVD gas phase reaction may lead to a "bread-loafing" deposition effect. These effects typically result in thicker deposits at the top surface of the gate stack and thinner deposits at the bottom corners of the gate stack. Furthermore, since some dies may have regions of different device densities, species transport effects across the wafer surface may cause variations in film thickness within the die and within the wafer. These thickness variations can result in overetching in some areas and underetching in others. This can reduce device performance and/or die yield.

解决这些问题的一些方法包括原子层沉积(ALD)。相比于使用热激活气相反应以沉积膜的CVD工艺,ALD工艺使用表面介导沉积反应以逐层沉积薄膜。在一个示例的ALD工艺中,包括多个表面活性位点的衬底表面被暴露于气相分布的第一膜前体(P1)。P1的一些分子可以在衬底表面顶部形成凝聚相,其包括P1的化学吸附类物和物理吸附分子。然后将反应器抽空,以除去气相和物理吸附的P1,以便只有化学吸附类物留下。然后引入第二膜前体(P2)到反应器中,使得一些P2的分子吸附到衬底表面。可以再次抽空该反应器,这时去除未被约束的P2。接着,提供于衬底的热能激活P1 和P2的吸附分子之间的表面反应,形成膜层。最后,将该反应器抽空,以去除反应副产物和可能未反应的P1和P2,结束ALD循环。可以包括其他 ALD循环以增加膜的厚度。Some approaches to address these issues include atomic layer deposition (ALD). In contrast to CVD processes that use thermally activated gas phase reactions to deposit films, ALD processes use surface-mediated deposition reactions to deposit thin films layer by layer. In one example ALD process, a substrate surface including a plurality of surface active sites is exposed to a gas phase distributed first film precursor (P1). Some molecules of P1 can form a condensed phase on top of the substrate surface, which includes chemisorbed species and physisorbed molecules of P1. The reactor was then evacuated to remove gas phase and physisorbed P1 so that only chemisorbed species remained. The second membrane precursor (P2) is then introduced into the reactor, so that some of the molecules of P2 are adsorbed to the substrate surface. The reactor can be evacuated again, at which point unconstrained P2 is removed. Next, the thermal energy supplied to the substrate activates the surface reaction between the adsorbed molecules of P1 and P2 to form a film layer. Finally, the reactor is evacuated to remove reaction by-products and possibly unreacted P1 and P2, ending the ALD cycle. Additional ALD cycles can be included to increase the thickness of the film.

在一个示例中,根据投配步骤前体的暴露时间和前体的粘着系数,每个ALD循环可以沉积厚度在0.5和3埃之间的膜层。因此,当沉积超过几纳米厚的膜时,ALD工艺可能是耗时的。此外,一些前体可以具有长的暴露时间,以沉积保形膜,从而也可以降低晶片吞吐的时间。In one example, depending on the exposure time of the precursor in the dosing step and the adhesion coefficient of the precursor, each ALD cycle can deposit a film with a thickness between 0.5 and 3 Angstroms. Therefore, the ALD process can be time consuming when depositing films that are more than a few nanometers thick. Additionally, some precursors can have long exposure times to deposit conformal films, which can also reduce wafer throughput times.

保形膜也可以沉积在平坦的衬底上。例如,由包含不同类型膜的平坦堆叠层可以形成光刻图案化应用中的抗反射层。这样的抗反射层厚度可介于约100至1000埃之间,使得ALD工艺的吸引力不及CVD工艺。然而,相比于许多CVD工艺可能提供的晶片内厚度变化的容差,这样的抗反射层还可以具有晶片内厚度变化的较低的容差。例如,600埃厚的抗反射层可以有小于3埃的厚度范围的容差。Conformal films can also be deposited on flat substrates. For example, antireflection layers in lithographic patterning applications can be formed from flat stacks comprising different types of films. Such antireflection layer thicknesses may be between about 100 to 1000 angstroms, making ALD processes less attractive than CVD processes. However, such an antireflection layer may also have a lower tolerance for intra-wafer thickness variation than many CVD processes may provide. For example, a 600 angstrom thick antireflection layer may have a tolerance in the thickness range of less than 3 angstroms.

相应地,本发明提供了用于在非平坦的和平坦的衬底上提供等离子体激活的保形膜沉积(CFD)的工艺和设备的多个示例。这些示例包括在一些但不是在所有的CFD工艺中采用的多种特征。在这些特征中有:(1)消除或减少从反应室中“清扫”一种或两种反应物所需的时间,(2)提供至少一种反应物的连续流,同时让不同的反应物断续地流入到反应室中,(3)当反应物中的一种以气相存在时,而不是当所有的反应物被清除出反应室时,点燃等离子体,(4)用等离子体处理沉积的CFD膜以修改膜的性能,(5)通过 CFD沉积膜的第一部分后,通常在相同的反应室中,通过PECVD沉积膜的一部分,(6)在CFD的阶段之间蚀刻部分地沉积的膜,以及(7)通过仅对膜的沉积的循环插入杂质输送循环,对CFD膜掺杂。当然,上面所罗列的并不详尽。研究本说明书的其余部分,各种其它CFD特征将是显而易见的。Accordingly, the present invention provides various examples of processes and apparatus for providing plasma-activated conformal film deposition (CFD) on non-planar and planar substrates. These examples include various features employed in some but not all CFD processes. Among these features are: (1) eliminating or reducing the time required to "sweep" one or both reactants from the reaction chamber, (2) providing a continuous flow of at least one reactant while allowing different reactants Intermittent flow into the reaction chamber, (3) ignition of the plasma when one of the reactants is present in the gas phase rather than when all of the reactants have been purged out of the chamber, (4) treatment of the deposition with the plasma The CFD film to modify the properties of the film, (5) after depositing the first part of the film by CFD, usually in the same reaction chamber, depositing part of the film by PECVD, (6) etching the partially deposited film between stages of CFD film, and (7) doping the CFD film by inserting an impurity delivery cycle only for the deposition cycle of the film. Of course, the above list is not exhaustive. Various other CFD features will become apparent upon studying the remainder of this specification.

CFD“循环”的构思与这里所讨论的各种示例有关。一般来说,循环是执行一次表面沉积反应所需的最小组的操作。一个循环的结果是在衬底表面上产生至少部分膜层。通常情况下,CFD循环将只包括那些将每种反应物输送并吸附到衬底表面,且接着使这些吸附的反应物形成部分膜层所必需的步骤。当然,循环可包括若干辅助步骤,如清扫反应物或副产物中的一种,和/或处理所沉积的部分膜。一般情况下,循环包含仅仅一种情形的独特操作序列。作为示例,一个循环可以包括以下操作:(i)输送/吸附反应物A, (ii)输送/吸附反应物B,(ⅲ)将B清扫出反应腔室,以及(iv)施加等离子体以驱动A和B的表面反应,从而在表面上形成部分膜层。The idea of a CFD "cycle" is relevant to the various examples discussed here. In general, a cycle is the smallest set of operations required to perform a surface deposition reaction. The result of one cycle is the creation of at least a partial film on the surface of the substrate. Typically, a CFD cycle will include only those steps necessary to transport and adsorb each reactant to the substrate surface, and then allow these adsorbed reactants to form a partial film. Of course, the cycle may include several auxiliary steps, such as scavenging one of the reactants or by-products, and/or treating a portion of the film deposited. Typically, a loop contains a unique sequence of operations for only one case. As an example, one cycle may include the following operations: (i) deliver/adsorb reactant A, (ii) deliver/adsorb reactant B, (iii) sweep B out of the reaction chamber, and (iv) apply plasma to drive The surfaces of A and B react to form a partial film on the surface.

上述7种特征现在将作进一步讨论。在下面的描述中,考虑CFD反应,在该CFD反应中,一种或多种反应物吸附到衬底表面,然后通过与等离子体的相互作用,发生反应,从而在该表面上形成膜。The above seven characteristics will now be discussed further. In the following description, a CFD reaction is considered in which one or more reactants are adsorbed to a substrate surface and then, through interaction with a plasma, react to form a film on the surface.

特征1(反应物的连续流)-当反应物A在传统的ALD中正常不会流动时,让反应物A在CFD循环的一个或多个部分的过程中连续流到反应室。在传统的ALD中,反应物A流动只为了让该反应物吸附在衬底表面。在ALD循环的其他阶段,反应物A不流动。然而,根据本发明所描述的某些CFD示例,反应物A不仅在与其吸附有关的阶段期间流动,而且在执行吸附A的操作之外的CFD循环的阶段流动。例如,在许多示例中,在反应物A 流动到反应器中的同时,装置正投配第二反应物(本文称作反应物B)。因此,在CFD循环的至少一部分的期间,反应物A和B以气相共存。另外,反应物A可以流动,同时施加等离子体以驱动在衬底表面的反应。注意,可结合载气-如氩气将连续流动的反应物输送到反应室。Feature 1 (Continuous Flow of Reactants) - Let Reactant A flow continuously to the reaction chamber during one or more parts of the CFD cycle when it would not normally flow in conventional ALD. In conventional ALD, reactant A flows only to allow the reactant to be adsorbed on the substrate surface. During other stages of the ALD cycle, reactant A does not flow. However, according to certain CFD examples described herein, reactant A flows not only during the phases associated with its adsorption, but also during phases of the CFD cycle outside of the operation of performing adsorption of A. For example, in many instances, while reactant A is flowing into the reactor, the apparatus is dosing a second reactant (referred to herein as reactant B). Thus, during at least a portion of the CFD cycle, reactants A and B coexist in the gas phase. Alternatively, reactant A can flow while applying plasma to drive the reaction at the substrate surface. Note that a continuous flow of reactants can be delivered to the reaction chamber in combination with a carrier gas such as argon.

连续流的示例的一个优点是,所形成的流避免了由与开启流与关闭流相关的使流瞬态启动并稳定而导致的延迟以及流的变化。One advantage of the continuous flow example is that the resulting flow avoids the delays and changes in flow caused by transiently starting and stabilizing the flow associated with opening and closing the flow.

作为具体的示例,可通过保形膜沉积工艺,使用主要反应物(有时也被称为“固体组分”前体,或在本示例中,简单称作“反应物B”)沉积氧化膜。双(叔-丁基氨基)硅烷(BTBAS)是一种这样的主要反应物。在此示例中,氧化物沉积工艺涉及氧化剂的输送,如氧或一氧化二氮,其在不同的暴露阶段,在主要反应物的输送过程中,初始地并且连续地流动。在不同的等离子体暴露阶段,氧化剂也连续流动。参见例如图1中所示的序列。相比而言,在传统的ALD工艺中,当固体组分前体输送到反应器中时,氧化剂的流将停止。例如,当输送反应物B时,反应物A的流将停止。As a specific example, an oxide film may be deposited by a conformal film deposition process using a primary reactant (also sometimes referred to as a "solid component" precursor, or in this example, simply "reactant B"). Bis(tert-butylamino)silane (BTBAS) is one such primary reactant. In this example, the oxide deposition process involves the delivery of an oxidant, such as oxygen or nitrous oxide, which flows initially and continuously during the delivery of the primary reactants at various exposure stages. The oxidant also flows continuously during different plasma exposure stages. See, for example, the sequence shown in Figure 1 . In contrast, in conventional ALD processes, the flow of oxidant is stopped when the solid component precursor is delivered to the reactor. For example, when reactant B is being delivered, the flow of reactant A will stop.

在一些具体的示例中,连续流动的反应物是“辅助”的反应物。如本文所用,“辅助”的反应物是任何并非主要反应物的反应物。正如上文所述,主要反应物包含在室温下是固体的元素,该元素用于由CFD形成的膜。这样的元素的示例是金属(例如,铝和钛)、半导体(例如,硅和锗)、和非金属或类金属(例如,硼)。辅助的反应物的示例包括氧气、臭氧、氢、一氧化碳、一氧化二氮、氨、烷基胺、和其他类似物。In some specific examples, the continuously flowing reactants are "auxiliary" reactants. As used herein, an "auxiliary" reactant is any reactant that is not a primary reactant. As mentioned above, the primary reactants contain elements that are solid at room temperature, which are used in films formed by CFD. Examples of such elements are metals (eg, aluminum and titanium), semiconductors (eg, silicon and germanium), and non-metals or metalloids (eg, boron). Examples of auxiliary reactants include oxygen, ozone, hydrogen, carbon monoxide, nitrous oxide, ammonia, alkylamines, and the like.

连续流动的反应物可以以恒定的流率或以变动但可控的流率提供。在后者的情况下,作为示例,在输送主要反应物的暴露阶段期间,辅助反应物的流率可能下降。例如,在氧化物沉积过程中,氧化剂(例如,氧或一氧化二氮)在整个沉积序列可以连续流动,但是在输送主要反应物(例如, BTBAS)时,其流率可能下降。这在BTBAS的投配期间,会增加其局部压强,从而减少布满衬底表面所需要的暴露时间。点燃等离子体之前不久,氧化剂的流量可以增加,以减少等离子体暴露阶段期间BTBAS存在的可能性。在一些实施方式中,连续流动的反应物在两个或两个以上的沉积循环的过程中以变动的流率流动。例如,反应物可以在第一CFD循环以第一流率流动,而在第二CFD循环以第二流率流动。The continuously flowing reactants can be provided at a constant flow rate or at a variable but controllable flow rate. In the latter case, as an example, the flow rate of the secondary reactant may drop during the exposure phase in which the primary reactant is delivered. For example, during oxide deposition, the oxidant (eg, oxygen or nitrous oxide) may flow continuously throughout the deposition sequence, but its flow rate may decrease when delivering the primary reactant (eg, BTBAS). This increases the local pressure of the BTBAS during dosing, thereby reducing the exposure time required to fill the substrate surface. Shortly before igniting the plasma, the flow of oxidant can be increased to reduce the likelihood of the presence of BTBAS during the plasma exposure phase. In some embodiments, the continuously flowing reactants flow at varying flow rates during two or more deposition cycles. For example, the reactants may flow at a first flow rate in the first CFD cycle and flow at a second flow rate in the second CFD cycle.

当采用多个反应物且其中之一的流动是连续的时,在CFD循环的一部分的过程中,其中的至少两者将以气相共存。同样,在输送第一反应物后没有执行清除步骤时,两种反应物将共同存在。因此,使用在没有施加激活能量的气相中不会彼此明显发生反应的反应物可能是重要的。通常情况下,反应物应当直到其出现在衬底表面上并暴露于等离子体或另一合适的非热激活条件时才反应。选择这样的反应物涉及考虑至少(1)所希望的反应的热力学适宜度(吉布斯自由能<0),和(2)反应的激活能量,其应该是足够大,以便在所需的沉积温度的反应可以忽略不计。When multiple reactants are employed and the flow of one of them is continuous, at least two of them will coexist in the gas phase during part of the CFD cycle. Likewise, when no clean-up step is performed after delivery of the first reactant, the two reactants will co-exist. Therefore, it may be important to use reactants that do not appreciably react with each other in the gas phase where no activation energy is applied. Typically, the reactant should not react until it is present on the substrate surface and exposed to plasma or another suitable non-thermal activation condition. Selection of such reactants involves consideration of at least (1) the desired thermodynamic fitness of the reaction (Gibbs free energy < 0), and (2) the activation energy of the reaction, which should be large enough to allow deposition at the desired The temperature response is negligible.

特征2(减少或消除清扫步骤)-在某些实施方式中,该工艺省去或减少与清扫步骤相关联的时间,清扫步骤在传统的ALD中通常会执行。在传统的ALD中,在每种反应物输送并吸附到衬底表面后,进行单独的清扫步骤。在传统的ALD清扫步骤中,很少或没有吸附或反应发生。在CFD循环中,在输送至少一种反应物后,减少或消除该清扫步骤。图1示出了去除了清扫步骤的处理序列的示例。没有执行从反应室清扫反应物A的清扫步骤。在某些情况下,在CFD循环输送第一反应物后,没有进行清扫步骤,但是在输送第二反应物或者最后输送的反应物输送后,可以选择地进行清扫步骤。Feature 2 (Reduce or Eliminate Sweeping Steps) - In certain embodiments, the process eliminates or reduces the time associated with sweeping steps that are typically performed in conventional ALD. In conventional ALD, after each reactant is transported and adsorbed to the substrate surface, a separate sweeping step is performed. In traditional ALD sweep steps, little or no adsorption or reaction occurs. In a CFD cycle, this sweep step is reduced or eliminated after the delivery of at least one reactant. Figure 1 shows an example of a processing sequence with the cleaning step removed. The purge step to purge reactant A from the reaction chamber was not performed. In some cases, the cleaning step is not performed after the CFD cycle delivers the first reactant, but may optionally be performed after delivering the second reactant or the last reactant delivered.

CFD的“清扫”步骤或阶段的构思出现在本发明的各种实施方式的讨论中。一般来说,清扫阶段从反应室去除或清除气相反应物中的一种,并且通常仅在该反应物的输送完成后进行。换言之,该反应物在清扫阶段不再输送到反应室。然而,在清扫阶段期间,该反应物保持吸附在衬底表面上。通常情况下,清扫用于在衬底表面吸附该反应物至所需的水平后去除室中的任何残留的气相反应物。清扫阶段也可以从所述衬底表面去除弱吸附的物质(例如,某些前体配位体或反应副产物)。在ALD中,清扫阶段对于防止两种反应物的气相反应或者防止一种反应物与热的、等离子体的相互作用或者用于表面反应的其他的驱动力的相互作用而言,被视为是必要的。在一般情况下,并且除非另有规定,否则,清扫阶段可通过以下步骤完成:(ⅰ)将反应室抽空,和/或(ii)使不包含将被清扫出的物质的气体流动通过该反应室。在情形(ii)中,这样的气体可以是,例如,惰性气体或辅助反应物,如连续流动的辅助反应物。The concept of a "sweep" step or stage of CFD appears in the discussion of various embodiments of the present invention. In general, the purge stage removes or purges one of the gas-phase reactants from the reaction chamber, and usually occurs only after delivery of that reactant is complete. In other words, the reactant is no longer delivered to the reaction chamber during the purge phase. However, during the sweep phase, the reactants remain adsorbed on the substrate surface. Typically, sweeping is used to remove any residual gas-phase reactants in the chamber after the substrate surface has adsorbed the reactants to the desired level. The sweeping stage can also remove weakly adsorbed species (eg, certain precursor ligands or reaction by-products) from the substrate surface. In ALD, the sweeping stage is considered to prevent the gas phase reaction of the two reactants or the interaction of one reactant with heat, plasma, or other driving forces for surface reactions. necessary. In general, and unless otherwise specified, the purge phase may be accomplished by (i) evacuating the reaction chamber, and/or (ii) flowing a gas that does not contain the species to be purged through the reaction room. In case (ii), such gas may be, for example, an inert gas or an auxiliary reactant, such as a continuous flow auxiliary reactant.

消除清扫阶段可以在有或无其它反应物的连续流的情况下完成。在图1中所示的实施方式中,反应物A在其到衬底表面上的吸附完成后,没有被清扫掉,而是继续流入(图中由标号130示出)。The elimination sweep stage can be accomplished with or without continuous flow of other reactants. In the embodiment shown in FIG. 1, the reactant A is not swept away after its adsorption to the substrate surface is complete, but continues to flow in (indicated by the

在使用两个或两个以上的反应物的各种实施方式中,其清扫步骤被消除或减少的反应物是辅助反应物。作为示例,辅助反应物是氧化剂或氮源,而主要反应物是含硅、硼、或锗的前体。当然,主要反应物的清扫也可以被减少或消除。在一些实施方式中,在辅助反应物输送之后,不执行清扫步骤,但在主要反应物输送之后,可选地执行清扫步骤。In various embodiments using two or more reactants, the reactant whose sweep step is eliminated or reduced is a secondary reactant. As an example, the secondary reactant is an oxidant or nitrogen source, and the primary reactant is a silicon, boron, or germanium containing precursor. Of course, sweeping of the primary reactants can also be reduced or eliminated. In some embodiments, a purge step is not performed after the secondary reactant delivery, but optionally a purge step is performed after the primary reactant delivery.

如所提及的,清扫阶段不必完全消除,而只是相比于传统的ALD工艺清扫阶段减少持续时间。例如,在CFD循环过程中,诸如辅助反应物之类的反应物的清扫阶段可进行约0.2秒或更短,例如,介于约0.001至0.1秒之间。As mentioned, the sweep phase does not have to be eliminated completely, but only of reduced duration compared to conventional ALD processes. For example, during a CFD cycle, the purge phase of reactants such as auxiliary reactants may be performed for about 0.2 seconds or less, eg, between about 0.001 to 0.1 seconds.

特征3(当反应物中的一种以气相存在时点燃等离子体)-对于该特征,点燃等离子体,然后将所有的反应物从反应室中清除。这与传统的 ALD工艺相反,在传统的ALD工艺中,只有气相反应物不再存在于反应室中后,才激活等离子体或进行其他反应驱动操作。注意,在如图1所描绘的 CFD循环的等离子体部分的期间反应物A连续流动时,这样的特征必然会发生。然而,本公开的实施方式并不限于这种方式。一种或多种反应物可以在 CFD循环的等离子体阶段流动,但不必在CFD循环过程中连续流动。此外,在等离子体激活过程中处于气相的反应物可以是主要反应物或辅助反应物 (当在CFD循环中采用两种反应物时)。Feature 3 (Ignition of the plasma when one of the reactants is present in the gas phase) - For this feature, the plasma is ignited and then all reactants are purged from the reaction chamber. This is in contrast to conventional ALD processes, where plasma activation or other reaction-driven operations are performed only after gas-phase reactants are no longer present in the reaction chamber. Note that such a feature necessarily occurs when reactant A flows continuously during the plasma portion of the CFD cycle as depicted in Figure 1 . However, embodiments of the present disclosure are not limited in this manner. One or more reactants may flow during the plasma phase of the CFD cycle, but need not flow continuously during the CFD cycle. In addition, the reactants in the gas phase during plasma activation can be the primary reactant or the secondary reactant (when both reactants are employed in the CFD cycle).

例如,序列可以是:(i)引入反应物A,(ii)清除A,(iii)引入反应物B并且当B正在流动时激励等离子体,及(iv)清除。在这样的实施方式中,该工艺采用来源于气相的等离子体激活反应物。这是一个一般的示例,其中CFD不限于序列步骤的序列。For example, the sequence can be: (i) introduce reactant A, (ii) purge A, (iii) introduce reactant B and energize the plasma while B is flowing, and (iv) purge. In such embodiments, the process employs plasma-activated reactants originating from the gas phase. This is a general example where CFD is not limited to a sequence of sequential steps.

如果在向反应器供应固体组分前体(主要反应物)的时间阶段提供激活等离子体,则阶梯覆盖性(step coverage)可能变得不那么保形,但沉积速率通常会增大。但是,如果只有在输送一种辅助反应物的过程中进行等离子体激活,情况并不一定是如此。等离子体可以激活气相辅助成分以使其更易反应,从而增加其在保形膜沉积反应中的反应性。在某些实施方式中,该特征在沉积含硅膜(例如氧化物、氮化物或碳化物)时采用。Step coverage may become less conformal if the activation plasma is provided during the time period during which the solid component precursors (primary reactants) are supplied to the reactor, but deposition rates generally increase. However, this is not necessarily the case if plasma activation occurs only during the delivery of an auxiliary reactant. The plasma can activate gas-phase auxiliary components to make them more reactive, thereby increasing their reactivity in conformal film deposition reactions. In certain embodiments, this feature is employed when depositing silicon-containing films such as oxides, nitrides, or carbides.

特征4(沉积CFD膜的等离子体处理)-在这些实施方式中,等离子体在保形膜沉积过程中可起到两种或两种以上的作用。其作用之一是,在每个CFD循环中激活或驱动膜形成反应。其另一个作用是,在经过一个或多个CFD循环的CFD膜部分或完全沉积之后,处理膜。等离子体处理的目的是改变膜的一种或多种属性。通常情况下,但并不一定,进行等离子体处理阶段的条件与那些用于激活膜形成反应(即,驱动膜形成反应)而采用的条件是不同的。作为一个例子,等离子体处理也可以在还原或氧化环境存在时进行(例如,在氢或氧存在时),而这在CFD循环的激活期间是不必要的。Feature 4 (Plasma Treatment for Deposition of CFD Films) - In these embodiments, the plasma can perform two or more roles in the conformal film deposition process. One of its roles is to activate or drive the membrane formation reaction in each CFD cycle. Another function of this is to process the film after partial or complete deposition of the CFD film over one or more CFD cycles. The purpose of plasma treatment is to alter one or more properties of the film. Typically, but not necessarily, the conditions under which the plasma treatment stage is carried out are different from those employed to activate the film-forming reaction (ie, drive the film-forming reaction). As an example, plasma treatment can also be performed in the presence of a reducing or oxidizing environment (eg, in the presence of hydrogen or oxygen), which is not necessary during activation of a CFD cycle.

可以在CFD工艺的每个循环期间、每隔一个循环期间、或在更少频率的基础上,执行等离子体处理操作。该处理可以是定期进行的、与固定的 CFD循环数相结合的,或者其可以可变地(例如,在CFD循环的不同的间隔)或者甚至是随机地执行。在一个典型的例子中,进行几个CFD循环的膜沉积,以达到适当的膜厚度,然后采用等离子体处理。此后,再次进行没有等离子体处理的几个CFD循环的膜沉积,然后再次进行等离子体处理。这种 x次CFD循环的超序列及紧接着的等离子体处理(膜改性),可以重复进行,直到膜通过CFD完全形成。Plasma processing operations may be performed during every cycle of the CFD process, during every other cycle, or on a less frequent basis. The processing may be performed periodically, in conjunction with a fixed number of CFD cycles, or it may be performed variably (eg, at different intervals of a CFD cycle) or even randomly. In a typical example, several CFD cycles of film deposition are performed to achieve the appropriate film thickness, followed by plasma treatment. Thereafter, film deposition was performed again for several CFD cycles without plasma treatment, followed by plasma treatment again. This supersequence of x CFD cycles followed by plasma treatment (film modification) can be repeated until the film is fully formed by CFD.

在某些实施方式中,所述等离子体处理可在CFD循环开始之前进行,以改变沉积CFD膜的表面的一种或多种属性。在各种实施方式中,表面是由硅(掺杂的或不掺杂的)或含硅物质形成的。改变后的表面能够更好地产生与随后沉积的CFD膜之间的高品质界面。该界面可通过诸如减少故障而提供例如良好的附着力、可靠的电气性能等。In certain embodiments, the plasma treatment may be performed prior to the initiation of a CFD cycle to alter one or more properties of the surface on which the CFD film is deposited. In various embodiments, the surface is formed of silicon (doped or undoped) or a silicon-containing species. The altered surface is better able to produce high-quality interfaces with subsequently deposited CFD films. The interface may provide eg good adhesion, reliable electrical performance, etc. by, for example, reducing failures.

衬底在CFD之前的预处理,并不限于任何特定的等离子体处理。在某些实施方式中,预处理涉及,在氦、氢、氩、氮、氢/氮形成气体、和/或氨的存在下,暴露于氢等离子体、氮等离子体、氮/氢等离子体、氨等离子体、氩等离子体、氦等离子体、氦退火、氢退火、氨退火、和UV-固化。等离子体处理可以用各种等离子体发生器实现,包括但不限于,用微波、ICP-远程、ICP-直接(direct)和本领域技术人员公知的其他手段来实现。The pretreatment of the substrate prior to CFD is not limited to any particular plasma treatment. In certain embodiments, the pretreatment involves exposure to hydrogen plasma, nitrogen plasma, nitrogen/hydrogen plasma, Ammonia plasma, argon plasma, helium plasma, helium anneal, hydrogen anneal, ammonia anneal, and UV-curing. Plasma treatment can be accomplished with a variety of plasma generators, including, but not limited to, microwave, ICP-remote, ICP-direct, and other means known to those skilled in the art.

总体而言,该处理可发生在CFD循环之前、期间和之后。当在 CFD循环期间发生时,可以根据适当的沉积条件选择处理频率。通常情况下,处理发生的频率每个循环不超过一次。In general, the processing can take place before, during and after the CFD cycle. As occurs during a CFD cycle, the treatment frequency can be selected according to appropriate deposition conditions. Typically, processing occurs no more than once per cycle.

作为一个例子,考虑从存在有一些碳的前体形成氮化硅的工艺。这类前体的示例包括BTBAS。作为前体中存在有碳的后果,所沉积的氮化物膜包括一些碳杂质,这可能会降低氮化物的电性能。为了克服这种问题,在使用含碳前体的几个CFD循环后,部分沉积的膜在等离子体的存在下暴露于氢,以减少并最终去除碳杂质。As an example, consider a process for forming silicon nitride from a precursor in which some carbon is present. Examples of such precursors include BTBAS. As a consequence of the presence of carbon in the precursor, the deposited nitride film includes some carbon impurities, which may degrade the electrical properties of the nitride. To overcome this problem, after several CFD cycles using carbon-containing precursors, partially deposited films are exposed to hydrogen in the presence of plasma to reduce and ultimately remove carbon impurities.

可以选择用于修改膜表面的等离子体条件,以实现膜性质和/或组成物的所希望的改变。在各个等离子体条件中,对于所需修改,可以选择和/或修整的是:氧化条件、还原条件、蚀刻条件、用于产生等离子体的功率、用于产生等离子体的频率、用于产生等离子体的两种或更多的频率的使用、等离子体密度、等离子体和衬底之间的距离,等等。CFD膜可以通过等离子体处理进行修改的性能的示例包括:内部膜应力、耐蚀刻性、密度、硬度、光学性质(折射率、反射率、光密度、等等)、介电常数、碳含量、电性能 (Vfb扩散等)、及类似物。The plasma conditions used to modify the film surface can be selected to achieve desired changes in film properties and/or composition. Among the various plasma conditions, what can be selected and/or tailored for the desired modification are: oxidizing conditions, reducing conditions, etching conditions, power used to generate plasma, frequency used to generate plasma, used to generate plasma The use of two or more frequencies of the volume, the plasma density, the distance between the plasma and the substrate, etc. Examples of properties of CFD films that can be modified by plasma treatment include: internal film stress, etch resistance, density, hardness, optical properties (refractive index, reflectivity, optical density, etc.), dielectric constant, carbon content, Electrical properties (Vfb diffusion, etc.), and the like.

在一些实施方式中,使用除等离子体处理以外的处理,以修改沉积膜的属性。这样的处理包括电磁辐射处理、热处理(例如,退火或高温脉冲)、及类似处理。任何这些处理可以单独进行,或者与包括等离子体处理的另一种处理组合进行。任何这样的处理可以用来替代任何上述等离子体处理。在一个特定的实施方式中,该处理涉及把该膜暴露于紫外线辐射。正如下面所描述的,在一个特定的实施方式中,该方法涉及对CFD膜氧化物在原位(即,在形成膜的过程中)应用UV-辐射或对沉积后的氧化物应用UV-辐射。这样的处理可以用来减少或消除结构缺陷,并提供改进的电性能。In some embodiments, treatments other than plasma treatments are used to modify the properties of the deposited films. Such treatments include electromagnetic radiation treatments, thermal treatments (eg, annealing or high temperature pulses), and the like. Any of these treatments can be performed alone or in combination with another treatment including plasma treatment. Any such treatment can be used in place of any of the plasma treatments described above. In a specific embodiment, the treatment involves exposing the film to ultraviolet radiation. As described below, in a specific embodiment, the method involves applying UV-radiation to the CFD film oxide in situ (ie, during film formation) or to the deposited oxide. . Such treatments can be used to reduce or eliminate structural defects and provide improved electrical properties.

在某些特定的实施方式中,UV处理可以和等离子体处理结合使用。这两种操作可以同时执行或顺序执行。在顺序执行选项中,可选地, UV操作首先发生。在同时执行的选项中,这两个处理可以配置不同的源 (例如,RF功率源用于等离子体,灯用于UV),或配置单一的源,例如氦等离子体,其产生紫外线辐射副产物。In certain specific embodiments, UV treatment can be used in conjunction with plasma treatment. Both operations can be performed simultaneously or sequentially. In the sequential execution option, optionally, the UV operation happens first. In a simultaneous option, the two processes can be configured with different sources (eg, RF power source for plasma, lamp for UV), or a single source, such as helium plasma, which produces UV radiation by-products .