サクサク読めて、

アプリ限定の機能も多数!

AMDのコンピューティングおよびグラフィックビジネス部門のシニア・ヴァイス・プレジデントを務め、ジム・ケラー氏が手がけたZenアーキテクチャによるRyzenシリーズの展開を指揮し、倒産寸前だったAMDの復活を影で支えた功労者として知られているジム・アンダーソン氏は、2018年にAMDを退社し、FPGAを中心に開発する半導体企業・ラティスのCEOに就任しました。そんなアンダーソンCEOへのインタビューを、ハードウェア関連ニュースサイトのAnandTechが公開しています。 An AnandTech Interview with Jim Anderson,CEO of Lattice Semiconductor https://www.anandtech.com/show/16879/an-anandtech-interview-with-jim-anderson-ceo-of-lattic

はじめに 現在DNN(Deep NeuralNetwork)の実装において、FPGAの活用はしばし議論の対象になっています。もちろんDNN分野全体からするとニッチな部類に入るとは考えますが、FPGAベンダーはここに非常に力を入れており、作成したネットワークのデプロイ先としてFPGAが選択しやすくなるような各種のソリューションが用意され始めており、日々進化しています。 ここでのFPGAのメリットは、低消費電力であったり、コストであったりします。DNNの実行にはクラウドであっても電力というランニングコストは馬鹿になりませんし、エッジコンピューティング、特にバッテリー駆動のモバイル分野においては電力は極めて重要です。またイニシャルコストの重要性はどちらも同じでしょう。 ここでFPGAベンダーはこぞって、「GPUと同じように開発できます」をキャッチフレーズに、GPUを使って研究開発をしている多く

はじめに 従来のパーセプトロンモデルを使った学習ではなく、回路そのものを微分してFPGAを直接学習してしまおうという当サイトオリジナルのディープラーニングLUT-Networkですが、ここのところ深いネットを学習させるために蒸留(Knowledge Distillation)に取り組んでいました。 その一つの成果として、MNISTデータを使ったセマンティックセグメンテーション(もどき)を試してみたのでブログに記録しておきます。 まずは先に結果 まず先に最新の結果を記載いたします。MNISTベースの画像を入力して、それぞれの数字領域を色塗りするセマンティックセグメンテーション(もどき)を学習させてみました。 入力画像 出力画像 上記の入力画像をもとにVerilog のRTLシミュレーションで得た結果画像が以下です。FPGAリソース 下記が実際にRTLを合成した場合のリソース量です。DNN

~重要イベント一覧 (2019/06/22から)~ 06/22 作成開始 06/29 32bit加算だけ実行する状態機械が完成 07/17 UARTの送信機を作る 07/18 8bit加算ができるようになる 07/19 ModRM, SIB周りのアドレシングを作り込む 07/20 加算命令がIntel x86の仕様を完全に再現 07/25 加算以外の命令を、一気に48個作る 08/13 Hello Worldが動いた (writeシステムコールの作成) 08/21 自作CPU上で自作OSが動いた 08/27 自作CPU上の自作OSにシェルを実装 09/21 自作CPU上の自作OS上でテトリスが動いた

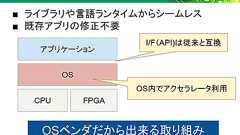

Linux OSからFPGAを透過的に利用する構想。文字列処理をCPUからFPGAへオフロードで10倍速になった研究結果をミラクル・リナックスが発表 プロセッサ内部のロジックをソフトウェアで動的に書き換えることができるFPGAは、アプリケーションごとにロジックを最適化できるため、x86などの汎用プロセッサよりも高速かつ効率的なアプリケーションの実行が可能になると注目されています。 特に、今年の1月にインテルがFPGA大手のアルテラを買収し、XeonにFPGAを統合するという将来計画を発表してから、FPGAへの注目度はさらに高まっています。 しかしいまのところ、FPGAをアプリケーションから利用するには、ロジックを開発ツールなどを用いてFPGAに書き込み、それをデバイスドライバを経由してフレームワークなどを通じて利用するというものになります。 これをもっと簡単にしようという構想を明らかにした

男子たるもの一度は自分でCPUを作ってみたいものだけど、ICでLEDをピカピカさせた程度の経験しかないハード素人な俺だったので、CPUを自作してる東大生などを遠くから見て憧れてるだけだった。しかしおよそ一年前のこと、「MIPSなんて簡単に作れますよ!」とKさん(←FPGAでLispマシンを自作するような人)に言われて、お、おぅ。。そりゃKさんはそうでしょうよ。。あれ、もしかして俺にもできるかな。。? と思った。この一言がなければ32bitのCPUを自作しようなんて考えなかっただろう。 それから一年ちょい、とくに今年の正月休みやFPGA温泉でがっつりがんばって、なんとかMIPS Iサブセットの自作CPUが動いた。これはフィボナッチを計算してるところ。 ちなみに、これはこんな感じのフィボナッチのコードをCで書いて、 void main() { int i, *r = (int *)0x7f00

FPGAベンダー大手の米Alteraは、2014年頃に出荷予定の同社のハイエンドFPGA「Stratix 10 SoC」に、英ARMの64ビットCPUコア「Cortex-A53」を採用すると発表した。CPUコアを搭載する同社の「SoCFPGA」シリーズとして初めて64ビットプロセッサを採用した。 用途としては、データセンターのサーバーにおける検索処理やデータマイニングのアクセラレーション、ネットワーク機器におけるビットレベルでのパケット処理などに向ける。CPUでのソフト処理からFPGAでの論理処理に置き換えることで計算能力を高めるほか、データセンターの電力効率も向上できる。 Stratix 10 SoCは、クアッドコアのCortex-A53、浮動小数点演算向けのDSPコア、ユーザーロジックを搭載するFPGA部から成る。いずれの用途でもサーバーやネットワーク機器本体にホストとなるIAなどの

金融系でFPGAというとHFTへの応用が知られてるけど、この事例はリアルタイムトレードの話ではない。金融業務で必要とされるバッチ処理やHPC(High Performance Computing)でもFPGAが本格的に使われ始めてるという話だ。 元ネタは、2011年にJP Morgan Chaseの人がスタンフォード大学で講演した内容。このビデオを見ていたらとっっっても面白かったので、 #fpgax 第3回で使う資料として要点を訳し、俺のコメントや補足を追加してみた。 http://www.youtube.com/watch?v=9NqX1ETADn0 (スライドはこちら) なお、FPGAも金融も素人なので、勘違いや誤訳があるかもしれない。FPGAとは何かよく知らない人はこちらをどうぞ。 リーマン・ショック対策のスパコン開発 JP Morgan Chaseは、社債やモーゲージ(不動産を担保

A Hardware-BasedFPGAAI for Super Mario Bros. Nintendo Ninja is a final project for ECE5760 (Advanced Microcontroller Design) at Cornell University. The project was developed by JeremyBlum,Sima Mitra, and Jason Wright in the 2013 Spring Semester. This project is Open Source. We built anFPGA-basedAI that uses video input from an NES console to automatically play the game Super Mario Bros. All

●創刊主旨 FPGAが世の中に登場して20数年が経ちました.当初は価格も高くゲート規模も小さかったものが,半導体製造技術の進歩により,低価格化,大容量化,高機能化が進みました. 従来,ASICなどの試作開発やCPU周辺のグルーロジックをまとめる用途で使われていたFPGAは,大容量化により周辺機能をどんどん取り込み,SoC(System on a chip)を実現できるレベルに達しました. そして今日,ARMコアを内蔵したFPGAが登場しました.デュアルコア/800MHzというハイパワー・プロセッサを内蔵し,ユーザの手元でSoCが1個からでも実現できる夢のデバイスとなりました. 2013年は個人レベルで,量産メーカに負けない高性能な機器を設計できる時代になります.FPGAマガジンは,ユニークでオリジナリティのある機器を設計するエンジニアを全面的に支援することを目的に,大容量化,高機能化した

FPGAマガジンNo.20 発売中断のお知らせ 2018年1月25日に発売を予定していたFPGAマガジンNo.20は都合により発売をとり止めることになりました.楽しみにしていただいていた皆さんにご迷惑をおかけしてしまい申し訳ありません. 今後の予定は未定ですが,決まり次第ホームページ等でお知らせいたします.ご質問等がありましたら,CQ出版社までお問合せください.FPGAマガジンでメール・マガジンを始めます! ・弊社のメール・マガジンをすでにご購読のかた(購読の追加)はコチラから… (CQ connectにログインして「会員情報を更新する」でメール・マガジンを追加してください) ・弊社のメール・マガジンを初めて購読されるかた(新規購読の申し込み)はコチラから… (CQ connectへの会員登録をお願いいたします) 抽選で読者プレゼント(各種評価ボード)が当たる!! ・FPGAマガジン N

ここのところ重度のFPGA中二病にかかってしまい、冬休み中もDE0ざんまいな日々。気になっていた金融のHFT(high frequency trading:大手投資銀行等がμ秒単位の超高速で株式等を売り買いしてる恐ろしい市場)におけるFPGA利用状況について、HFT Reviewにこってりしたレポート(HFT業界のベンダー各社にインタビューしたもの)が載っていたので、勢い余って面白かった部分を超訳してしまった。 元ネタはこちら:FPGA & Hardware Accelerated Trading, Part One - Who, What, Where and Why?FPGA & Hardware Accelerated Trading, Part Two - Alternative ApproachesFPGA & Hardware Accelerated Trading, P

第0回 関西FPGA・DE0勉強会を梅田で開催しました。ATND跡地:http://atnd.org/events/23410ATND立てた初日で20人定員がいっぱいに。急遽50人部屋へ変更して最終的に46人となりました。 当日はみなさん楽しんでもらえたようで開催して本当によかったと思います。 みんなどんなところに関心があるのか、なぜこれだけ人が集まったのか というのはボクが知りたいことの一つだったんですが ユーザインタフェース(FPGA設計者の悩みの一つ)の解としてAndroidに注目 オープンソース、ソーシャルコーディングへの関心FPGAコミュニティの希求:単純に言えば同じ事に興味がある人たちと話がしたい、そういう場がほしい そんなかんじです。 さておき、当日の資料をまとめました。 第0回 関西FPGA・DE0勉強会FPGA・DE0でできること : KSK (@ksksue)

同社のFounderでCEOのOskar Mencer氏によれば,HPC(high performance computing)市場で,高速化のためならば,カネを積極的に払ってくれる(例えば,2倍高速にしたら2倍払う)のは,5%の顧客だけだという。その5%の顧客を狙って,事業を始めた。この5%に入り,Maxelerの顧客として名前が公表されている企業には,法人向け金融サービスの米J.P.Morgan(持ち株会社JPMorgan Chase & Co.の傘下の企業)と,石油メジャーの米Chevron Corp.がある。 金融や石油の分野で実績 J.P.Morganは各種金融指標や金融商品の予測システムに,Chevronは油田探索の海底地質調査のシステムに,Maxelerのアクセラレータを利用しているという。汎用のMPUを使ったサーバーをMaxelerのアクセラレータに置き換えたところ,エンド

スタンフォード大学のMichael Flynn教授は、SIMD、MIMDなどのコンピュータの区分を提唱したことなどで有名なコンピュータアーキテクチャ界の重鎮である。Flynn教授は2010年6月1日から筑波で開催されるInternational Conference on Supercomputing(ICS'10)のために来日しており、5月24日に慶応大学で特別講義を行った。今回の特別講義は、ICS'10初日となる6月1日の午後に予定されているFlynn教授を始めとする4人の講師陣によるチュートリアルのあらすじを説明するというものであった。 Flynn教授はFPGAで計算速度を飛躍的に改善するMaxelerTechnologiesという会社を設立しており、すでに、同社は石油探査会社などにFPGAベースのアクセラレータを販売した実績がある。 海底油田の探査では、母船からパルス音を発生させ

http://www.nikkeibp.co.jp/article/news/20110502/268840/?rt=nocnt [nikkeibp.co.jp] 会員サイトなので、興味深いところを抜き出す。 > 価格に関しては,市販のスーパーコンピュータに匹敵する性能で,1/100~1/1000の価格になるとの説明だった。「なぜ,安価にできるのか」と聞くと,Maxelerのアクセラレータはある問題に特化したコンピュータだからだという答えが返ってきた。ある問題とは,基本的に制御が必要でない大規模なデータフロー・グラフに帰着できる問題をいう。ハードウェアとしては,非常に段数の大きなパイプラインになる。J.P.MorganやChevronの適用例では,400~500段のパイプラインが複数のFPGAに実装されているという(なお,規模の小さなパイプラインだと,Maxelerのアクセラレータを導入す

リリース、障害情報などのサービスのお知らせ

最新の人気エントリーの配信

処理を実行中です

j次のブックマーク

k前のブックマーク

lあとで読む

eコメント一覧を開く

oページを開く