DOI:10.1109/JSSC.2007.897148 - Corpus ID: 699469

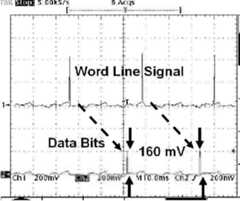

A 160 mV Robust Schmitt Trigger Based Subthreshold SRAM

@article{Kulkarni2007A1M, title={A 160 mV Robust Schmitt Trigger Based Subthreshold SRAM}, author={Jaydeep P. Kulkarni and Keejong Kim and Kaushik Roy}, journal={IEEE Journal of Solid-State Circuits}, year={2007}, volume={42}, pages={2303-2313}, url={https://api.semanticscholar.org/CorpusID:699469}}- J. KulkarniKeejong KimK. Roy

- Published inIEEE Journal of Solid-State…24 September 2007

- Engineering, Materials Science

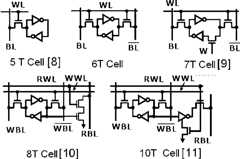

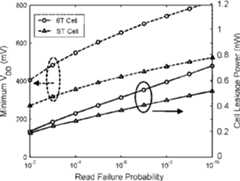

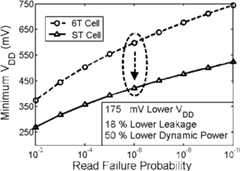

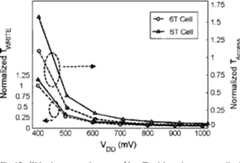

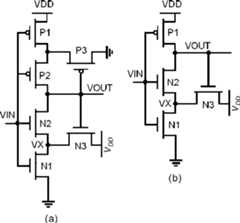

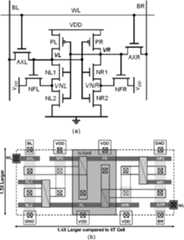

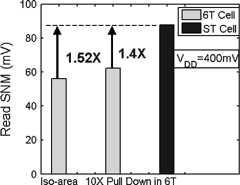

A novel Schmitt trigger (ST) based differential 10-transistor SRAM (static random access memory) bitcell suitable for subthreshold operation and does not require any architectural changes from the present 6T architecture is proposed.

483 Citations

Figures and Tables from this paper

483 Citations

A low power subthreshold Schmitt Trigger based 12T SRAM bit cell with process-variation-tolerant write-ability

- Prakhar SharmaShourya GuptaK. GuptaN. Pandey

- 2020

Engineering, Materials Science

Ultralow-Voltage Process-Variation-Tolerant Schmitt-Trigger-Based SRAM Design

- J. KulkarniK. Roy

- 2012

Engineering, Computer Science

IEEE Transactions on Very Large Scale Integration…

The proposed ST-2 bitcell incorporates a built-in feedback mechanism, achieving process variation tolerance - a must for future nano-scaled technology nodes, and gives better read-stability as well as better write-ability compared to the standard 6T bitcell.

Process variation tolerant SRAM array for ultra low voltage applications

- J. KulkarniKeejong KimS. P. ParkK. Roy

- 2008

Computer Science, Engineering

2008 45th ACM/IEEE Design Automation Conference

The proposed Schmitt Trigger SRAM cell addresses the fundamental conflicting design requirement of read versus write operation of a conventional 6T cell and incorporates a built-in feedback mechanism, achieving process variation tolerance -- a must for future nano-scaled technology nodes.

Variation resilient subthreshold SRAM cell design technique

The proposed bitcell utilises single differential port unlike conventional 10T bitcell which utilises dual differential ports and proves its robustness against process variations by featuring narrower spread in T RA distribution and in T WA distribution at 200 mV.

A Robust High Density 7T Subthreshold SRAM Bitcell with Partial Dynamic Threshold Voltage Connection Scheme

The area penalty of proposed SRAM is the smallest with robustness and functionality of subthreshold SRAM achieved, making the design less vulnerable to process variation.

Design and Analysis of Schmitt Trigger Based 10T SRAM in 32 nm Technology

- A. RajputM. PattanaikR. K. Tiwari

- 2017

Computer Science, Engineering

The results indicate that the proposed cell may be a better substitution of other Schmitt trigger based SRAM cell at scaled technology node.

Single-Ended Schmitt-Trigger-Based Robust Low-Power SRAM Cell

- Sayeed AhmadMohit Kumar GuptaN. AlamM. Hasan

- 2016

Computer Science, Engineering

IEEE Transactions on Very Large Scale Integration…

A Schmitt-trigger-based single-ended 11T SRAM cell is presented, which significantly improves read and write static noise margin (SNM) and consumes low power and achieves the lowest leakage power dissipation among the cells considered for comparison.

Independently-Controlled-Gate FinFET Schmitt Trigger Sub-Threshold SRAMs

- Chien-Yu HsiehM. FanV. HuP. SuC. Chuang

- 2012

Engineering

IEEE Transactions on Very Large Scale Integration…

Results indicate that even at the worst corner, two of the proposed cells can provide sufficient margin of μ/σ ratio, and compared with previously reported 10 T Schmitt Trigger sub-threshold SRAM cells, the proposed Cells exhibit comparable or better RSNM, higher density, and lower Standby leakage current.

A Technique for Designing Variation Resilient Subthreshold Sram Cell

- A. Islam

- 2013

Physics

This paper presents a technique for designing a variability aware subthreshold SRAM cell. The architecture of the proposed cell is similar to the standard read-decoupled 8-transistor (RD8T) SRAM cell…

A 200 mV low leakage current subthreshold SRAM bitcell in a 130 nm CMOS process

- Na 娜 Bai 柏Baitao 白涛 Lü 吕

- 2012

Engineering, Computer Science

A self-adaptive leakage cut off scheme is adopted in the proposed design without any extra dynamic energy dissipation or performance penalty, combined with buffering circuit and reconfigurable operation, which ensures both read and standby stability without deteriorating writability in the subthreshold region.

...

18 References

An Ultra-Low-Power Memory With a Subthreshold Power Supply Voltage

- Jinhui ChenL. ClarkTai-hua Chen

- 2006

Engineering, Materials Science

A 512times13 bit ultra-low-power subth threshold memory is fabricated on a 130-nm process technology, with pseudo-static operation provided via self-timed control of the keeper transistors to mitigate increased variability manifested in subthreshold operation.

Read Stability and Write-Ability Analysis of SRAM Cells for Nanometer Technologies

- E. GrossarM. StucchiK. MaexW. Dehaene

- 2006

Engineering, Computer Science

This paper analyzes the read stability N-curve metrics and compares them with the commonly used static noise margin (SNM) metric defined by Seevinck, and demonstrates that the new metrics provide additional information in terms of current, which allows designing a more robust and stable cell.

SRAM leakage suppression by minimizing standby supply voltage

- H. QinYu CaoD. MarkovicA. VladimirescuJ. Rabaey

- 2004

Engineering, Computer Science

International Symposium on Signals, Circuits and…

This paper explores how low DRV can be in a standard low leakage SRAM module and analyzes how DRV is affected by parameters such as process variations, chip temperature, and transistor sizing, and forms the basis for further design space explorations.

Review and future prospects of low-voltage RAM circuits

- Y. NakagomeM. HoriguchiT. KawaharaK. Itoh

- 2003

Computer Science, Engineering

This paper describes low-voltage random-access memory (RAM) cells and peripheral circuits for standalone and embedded RAMs, focusing on stable operation and reduced subthreshold current in standby…

A feasibility study of subthreshold SRAM across technology generations

- A. RaychowdhuryS. MukhopadhyayK. Roy

- 2005

Computer Science, Engineering

Analysis shows that subthreshold SRAM gives significant reduction of operating and standby power at iso-performance compared to the superthreshold counterpart, however, with increasing intra-die variation owing to technology scaling, the failure probability of subth threshold SRAM increases thereby masking the power benefits.

A high density, low leakage, 5T SRAM for embedded caches

- Ingvar CarlsonS. AndersonS. NatarajanA. Alvandpour

- 2004

Engineering, Computer Science

Proceedings of the 30th European Solid-State…

An embedded high density 128 Kb memory, utilizing a 5-transistor (5T) single bitline SRAM cell in a standard 0.18 /spl mu/m CMOS technology, has 23% smaller area, 75% lower bitline leakage, and a read/write performance comparable to a conventional 6T SRAM.

Static noise margin variation for sub-threshold SRAM in 65-nm CMOS

- B. CalhounA. Chandrakasan

- 2006

Engineering, Computer Science

This paper analyzes SNM for sub-threshold bitcells in a 65-nm process for its dependency on sizing, VDD, temperature, and local and global threshold variation and provides a model that allows estimation of the SNM along the worst-case tail of the distribution.

Stable SRAM cell design for the 32 nm node and beyond

- L. ChangD. FriedW. Haensch

- 2005

Computer Science, Engineering

Digest of Technical Papers. 2005 Symposium on…

This work demonstrates the smallest 6T and full 8T-SRAM cells to date and provides a much greater enhancement in stability by eliminating cell disturbs during a read access, thus facilitating continued technology scaling.

Dynamic leakage cut-off scheme for low-voltage SRAM's

- Hiroshi KawaguchiYasuhito ItakaTakayasu Sakurai

- 1998

Engineering, Computer Science

1998 Symposium on VLSI Circuits. Digest of…

A sub-volt SRAM circuit scheme is presented which speeds up the conventional low-voltage SRAM by more than a factor of two without applying excessive voltage to gate oxide and with maintaining the subthreshold leakage current to a tolerable level.

Self-calibration technique for reduction of hold failures in low-power nano-scaled SRAM

- Swaroop GhoshS. MukhopadhyayKeejong KimK. Roy

- 2006

Engineering, Computer Science

2006 43rd ACM/IEEE Design Automation Conference

This paper proposes a self-calibrating SRAM for aggressively reducing leakage while maintaining the hold failures under control and analyzes the effect of source bias on hold failure under both inter-die and intra-die variations.

Related Papers

Showing 1 through 3 of 0 Related Papers